SiC-Based High Efficiency High Isolation Dual Active Bridge Converter for a Power Electronic Transformer

Abstract

1. Introduction

- Studying the requirements of the devices in each of the PET stages to assess the benefit of integrating SiC and, consequently, identifying the stages making best use of it.

- Selection of the SiC devices for the second PET stage, based on a dual active bridge converter (DAB). As will be explained, this stage presents the most benefits from using SiC devices. Special attention will be paid to the device operation intrinsic to the converter topology. The use of SiC MOSFETs co-packaged with an additional SiC antiparallel diode is also investigated. A loss model is developed to estimate the potential efficiency improvement in this case. Both devices (i.e., with only intrinsic body diode and with additional SiC diode) are experimentally compared at rated power to validate the proposed model.

2. PET Topology

3. Use of WBG for PET

3.1. Device Requirements per PET Stage

3.2. Benefits and Practical Limitations of Using SiC MOSFETs for the DAB Converter

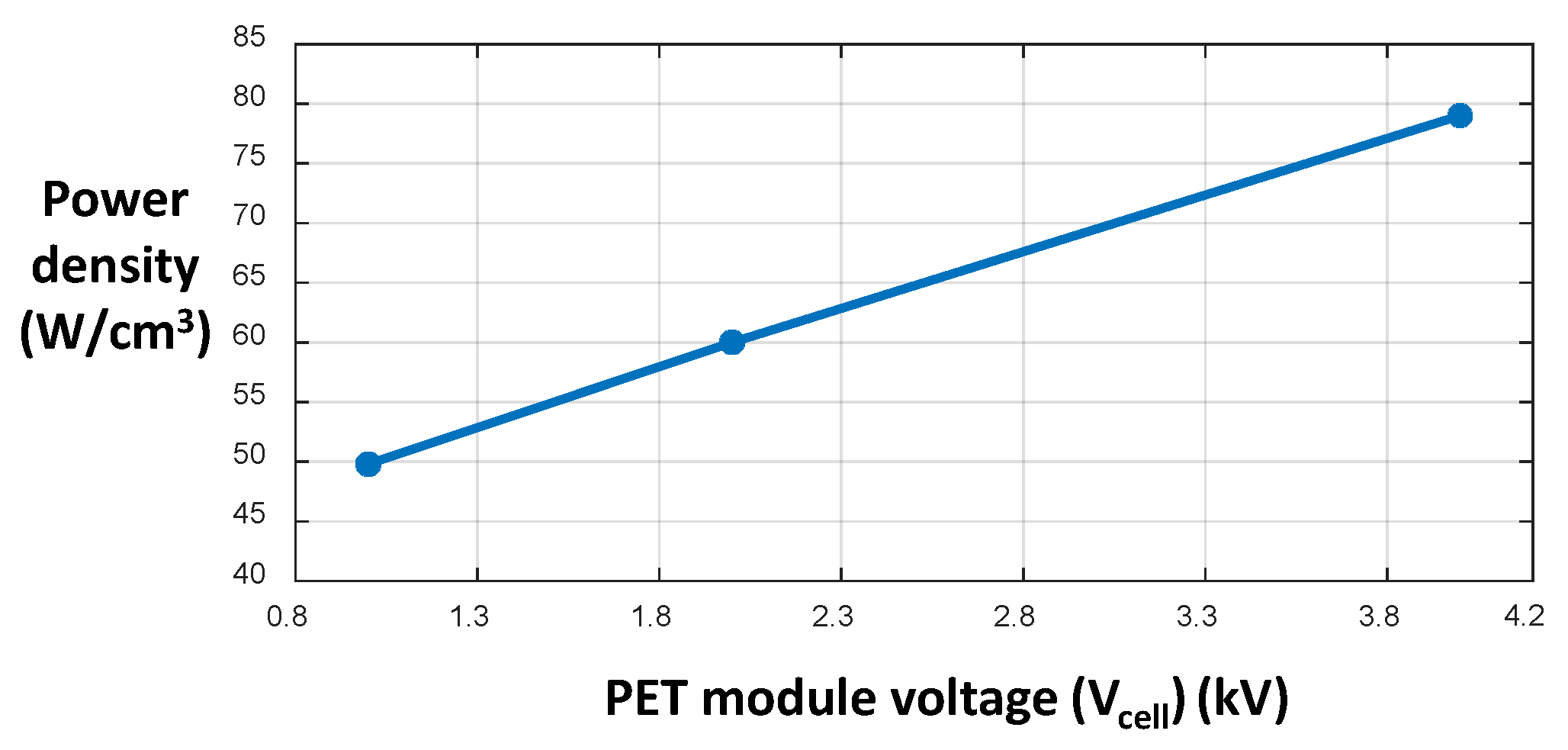

- The high blocking voltages enable increasing Vcell and, therefore, for a given VacHV, the number of stacked PET modules can be reduced (see Figure 1) [7,17]. This is also advantageous for the HFT. Since each module handles more power, this leads to a higher transformer power density. In order to see clearly the effect of this, Figure 2 shows the HFT power density as a function of the cell voltage where the PET total power and VacHV are fixed (i.e., the number of PET modules vary). A comparative analysis regarding this relation is previously presented in [17] showing an improvement in the HFT power density as Vcell increases.

4. SiC-Based DAB Converter

4.1. SiC Device Selection

4.2. Antiparallel SBD for a DAB Converter

4.2.1. Advantages and Disadvantages of an Additional SBD

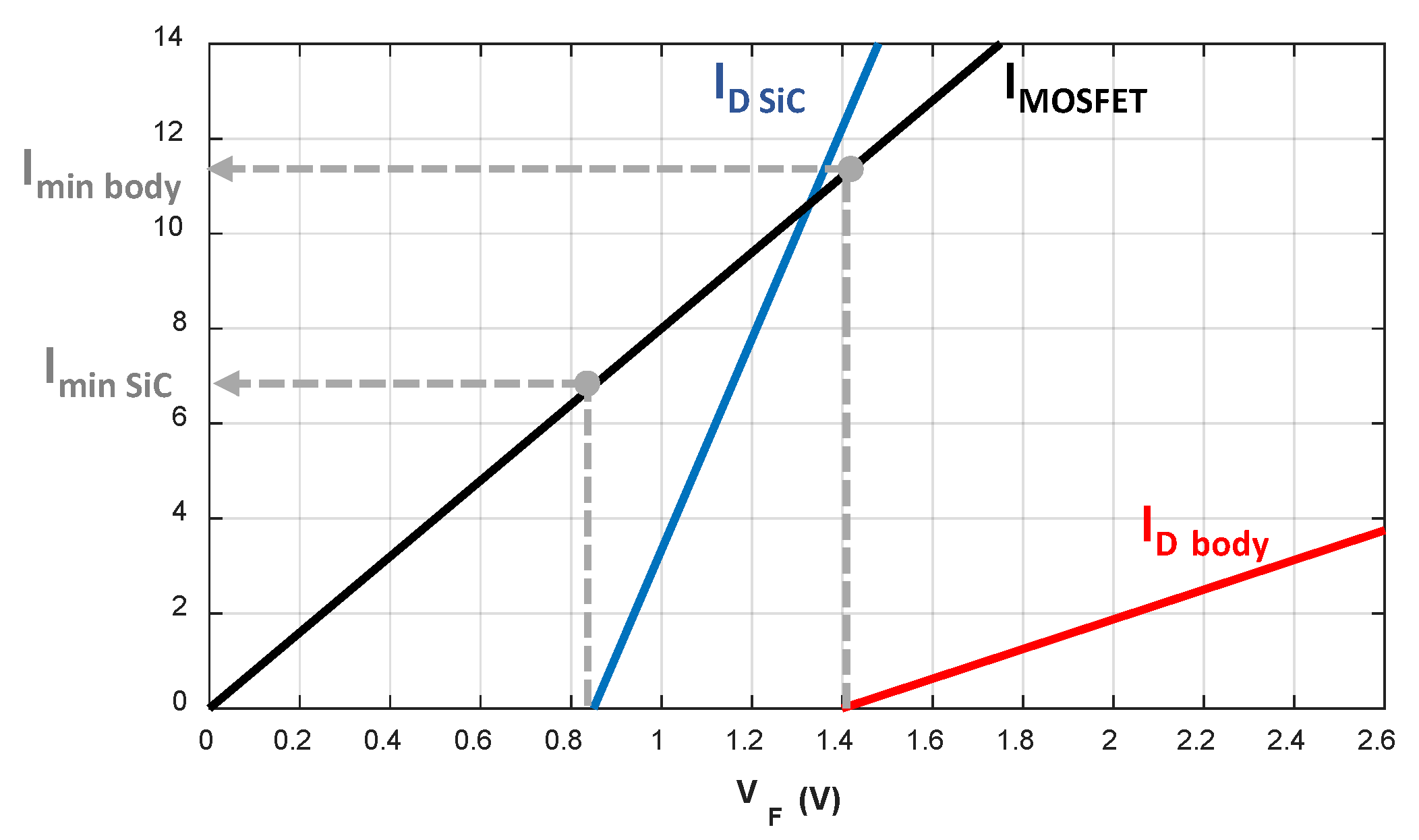

- Since VF-Diode of the additional SiC SBD is more than three times lower than that of the body diode (see Table 3), the power losses due to diode conduction during the dead times are lower using SCH2080KE +SBD.

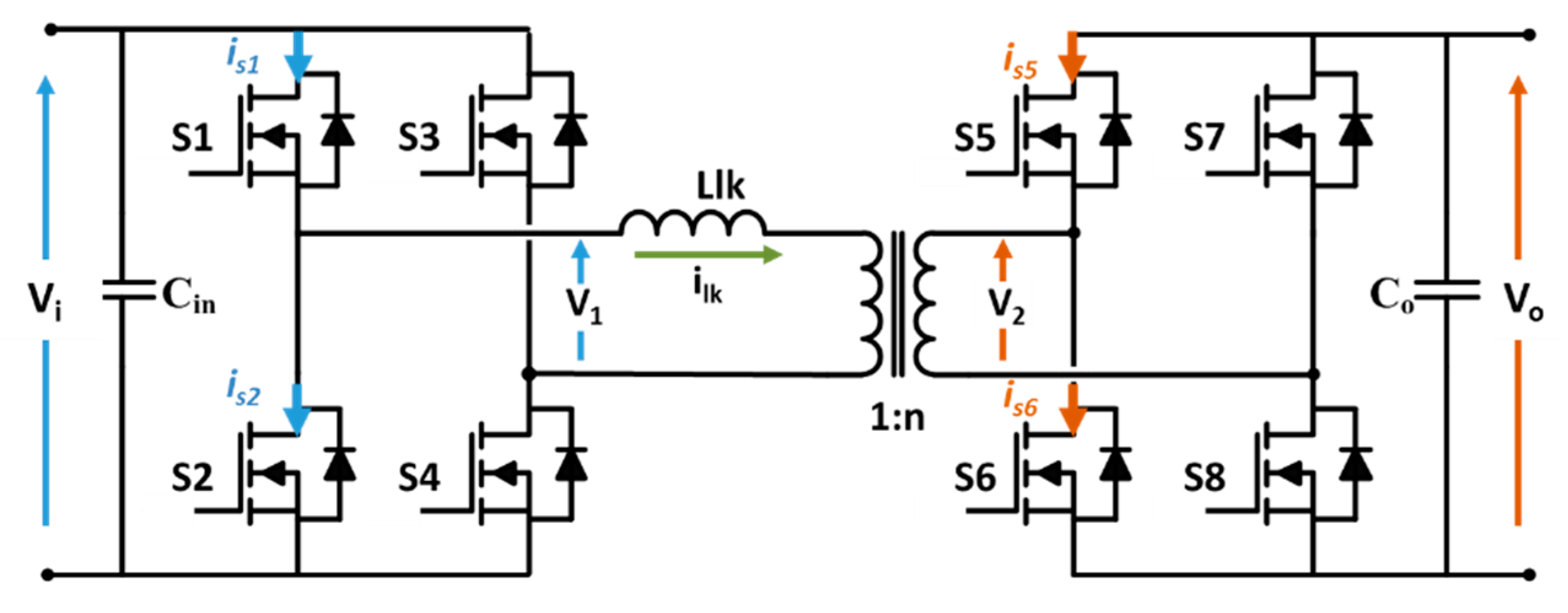

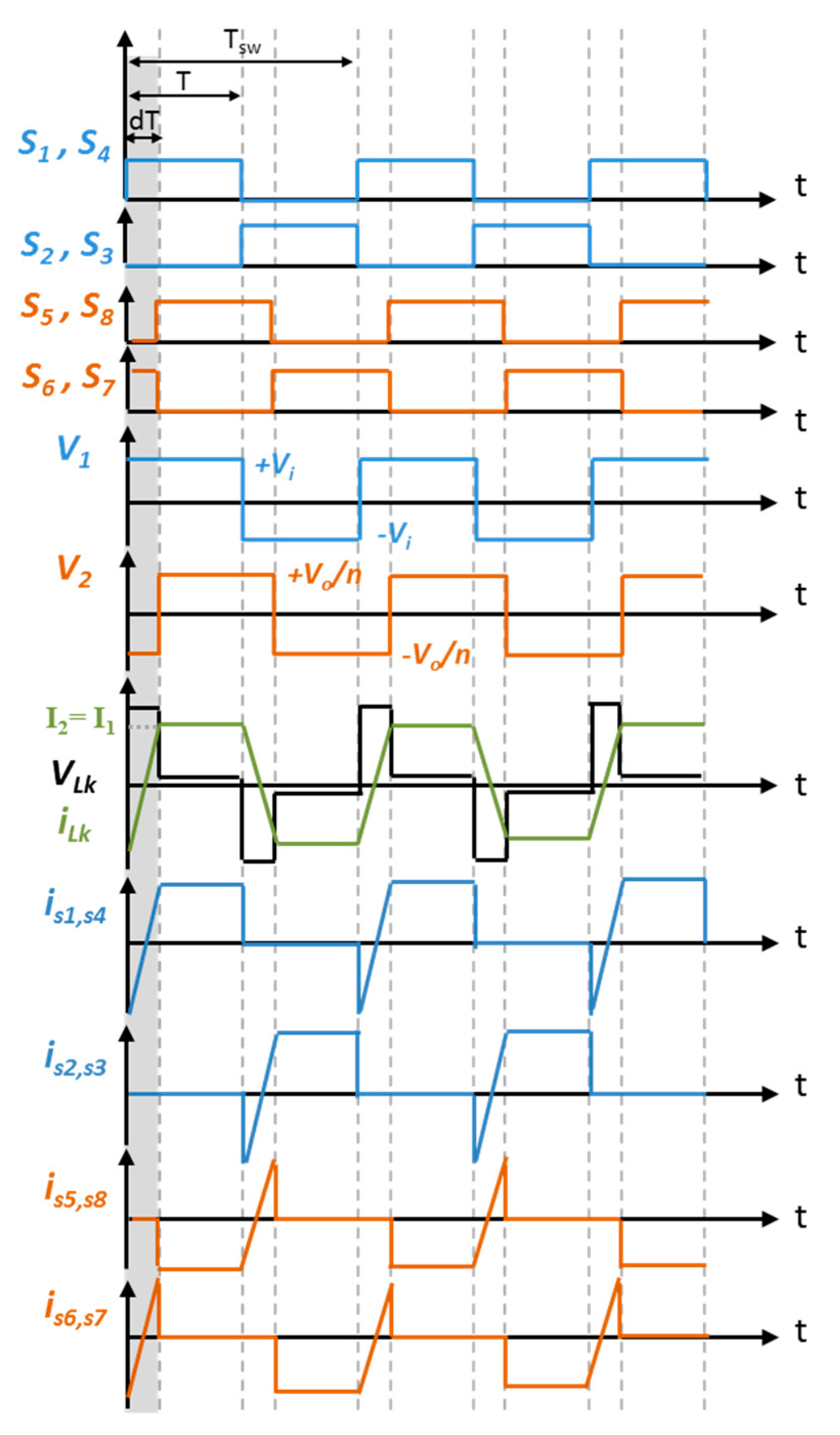

- The diode can enter into conduction while the MOSFET is ON. This can be seen from Figure 5, when the current through the MOSFET is negative (i.e., source to drain), a forward voltage drop, VF-MOSFET, is applied to the diode. If VF-MOSFET is higher than the diode knee voltage (Vknee), then the diode conducts. If this case is true, current is shared between the MOSFET and the diode and, therefore, conduction losses are reduced.

- From Figure 6, diodes do not operate during the whole period of the dead time. During (A), the output parasitic capacitances of the MOSFETs (see Figure 4) in one leg are exchanging the voltage (i.e., one is discharging while the other is charging) and during (B), diodes conduct due to circulating currents. In some cases, (B) can tend to zero depending on the value of the current charging/discharging the parasitic capacitors and on the dead time.

- If the current through the MOSFETs is not high enough to produce a VF-MOSFET > Vknee, then the diode will never conduct during MOSFET ON time.

- The turn OFF switching losses should be analyzed as the enhancement introduced by the SiC SBD in the conduction losses can, in some cases, be compromised by the increase in turn OFF switching losses (due to the extra capacitance).

4.2.2. Model to Assess the Efficiency Improvement Using a SiC Diode

Diode Conduction Intervals

Estimation of the Power Losses

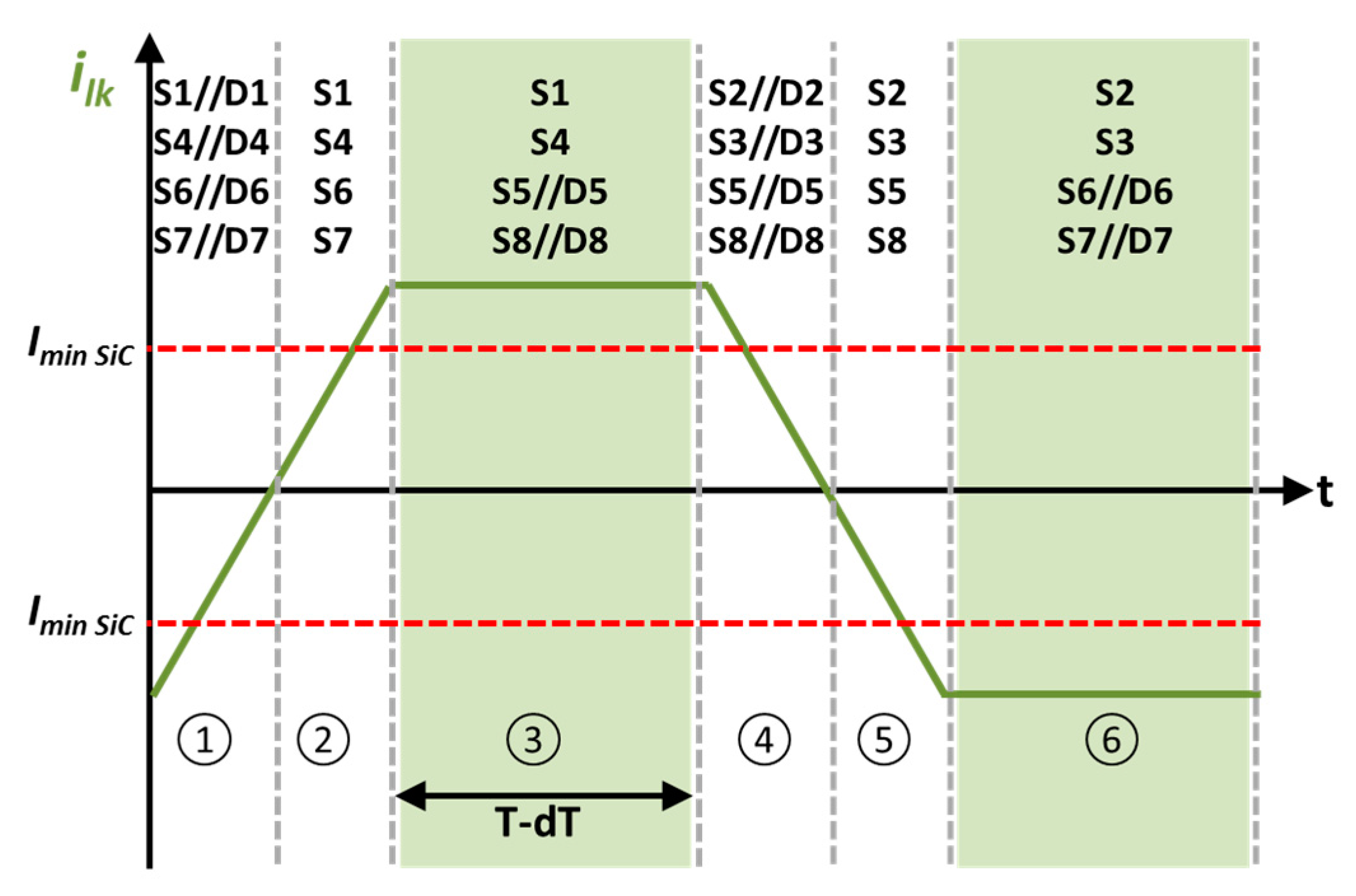

- As Imin SiC is around 75% of Ipk-lk, therefore, it is assumed that the diode operates only during period (3) and (6) when the peak current is passing through the devices (periods (1) and (4) are neglected).

- The power loss estimation is performed only during the periods with different operation for the case of the SiC SBD and the body diode. In other words, only the difference in losses between both cases is considered. These intervals are: (3), (6) and the dead times.

4.2.3. Experimental Validation of the Proposed Loss Model

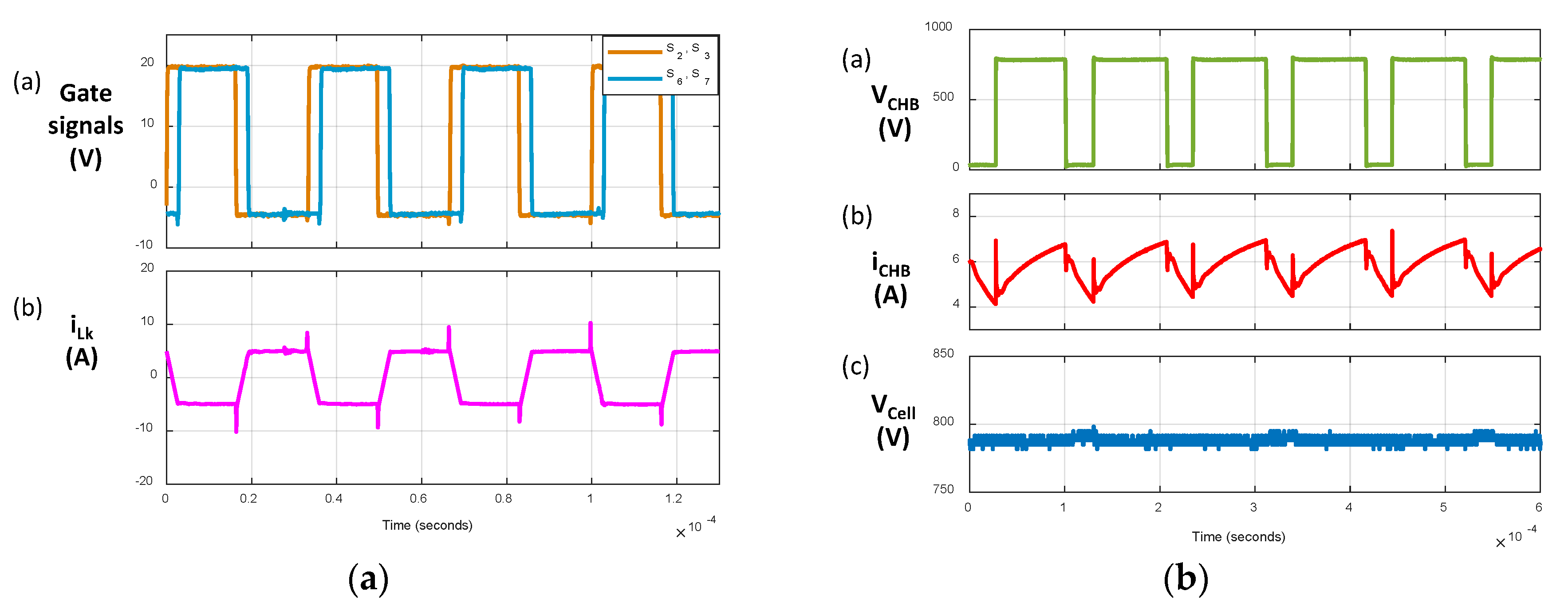

5. Experimental Results of the PET Module

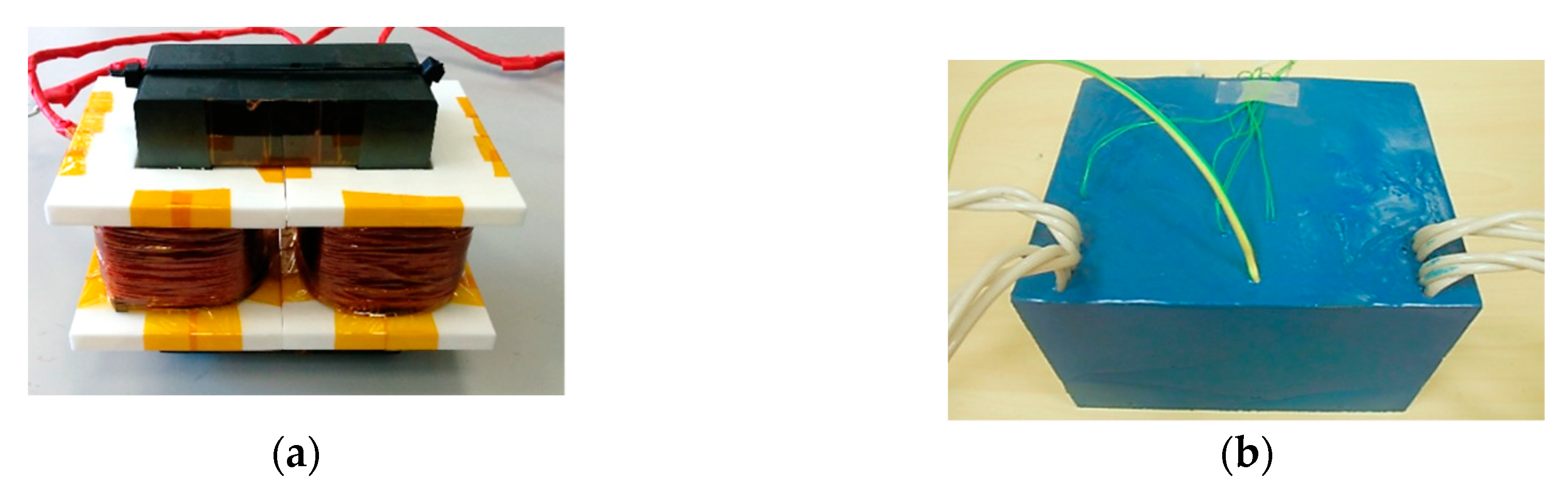

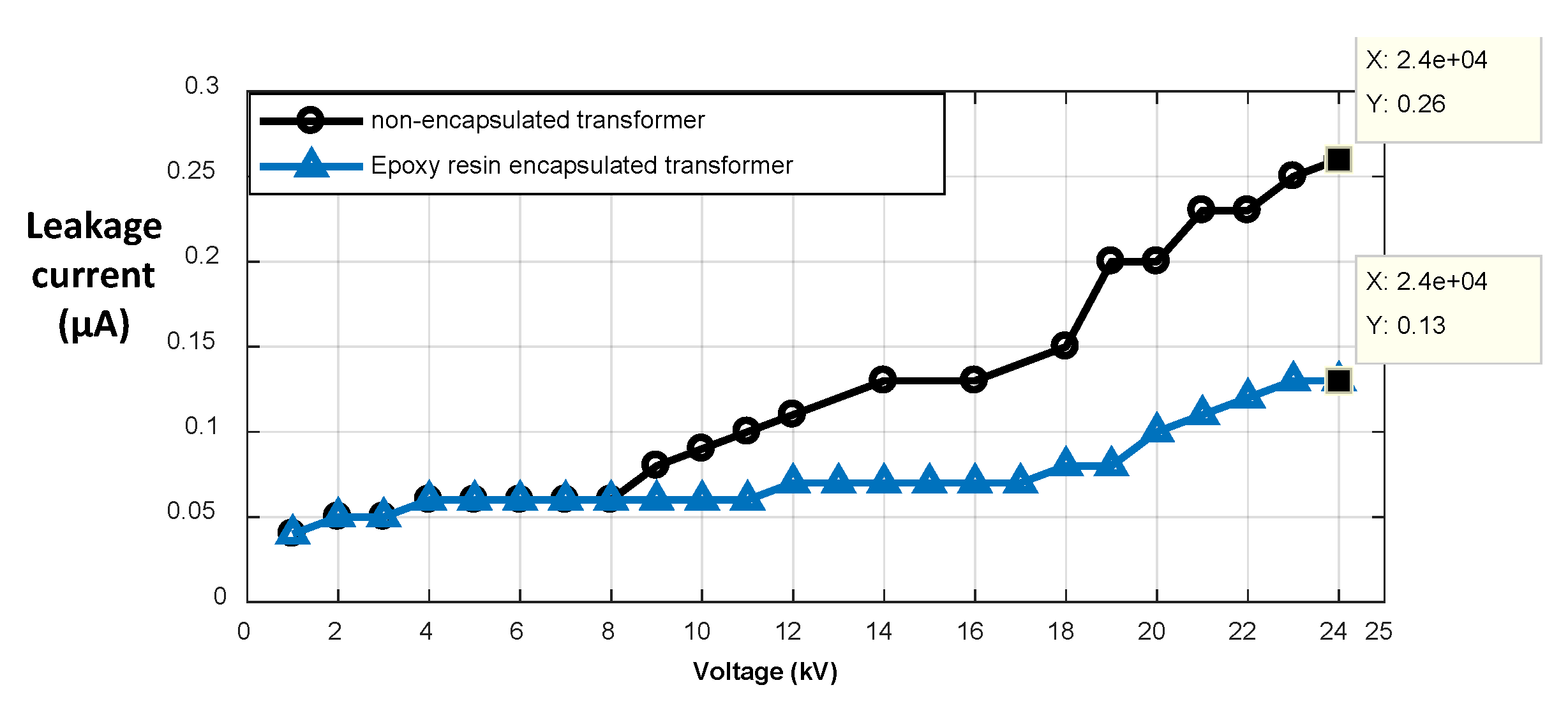

5.1. Developed HFT

5.2. Experimental Validation

6. Conclusions

Author Contributions

Funding

Conflicts of Interest

Nomenclature

| VacHV | HVAC grid voltage |

| VacLV | LVAC grid voltage |

| VdcLV | LVDC link voltage |

| CdcLV | LVDC link capacitor |

| Vcell | Cell capacitor voltage |

| Ccell | Cell capacitor |

| fsw | Switching frequency |

| T | Half the switching period of the DAB |

| d | Phase shift of the DAB represented as a ratio of T |

| Llk | DAB leakage inductance |

| Vknee | Diode knee voltage |

| VF-diode | Diode forward voltage |

| Ipk-lk | Peak current through the leakage inductance |

| RON-MOSFET | MOSFET ON resistance |

| Co(er) | MOSFET effective output capacitance |

References

- van der Merwe, J.W.; Mouton, H.d.T. The solid-state transformer concept: A new era in power distribution. In Proceedings of the AFRICON 2009, Nairobi, Kenya, 23–25 September 2009; pp. 1–6. [Google Scholar]

- McMurray, W. Power Converter Circuits Having a High-Frequency Link. U.S. Patent 3517300, 23 June 1970. [Google Scholar]

- Ronan, E.R.; Sudhoff, S.D.; Glover, S.F.; Galloway, D.L. A power electronic-based distribution transformer. IEEE Trans. Power Del. 2002, 17, 537–543. [Google Scholar] [CrossRef]

- Rothmund, D.; Ortiz, G.; Guillod, T.; Kolar, J.W. 10kV SiC-based isolated DC-DC converter for medium voltage-connected Solid-State Transformers. In Proceedings of the IEEE Applied Power Electronics Conference and Exposition (APEC), Charlotte, NC, USA, 15–19 March 2015; pp. 1096–1103. [Google Scholar]

- Millán, J.; Godignon, P.; Perpiñà, X.; Pérez-Tomás, A.; Rebollo, J. A Survey of Wide Bandgap Power Semiconductor Devices. IEEE Trans. Power Electron. 2014, 29, 2155–2163. [Google Scholar] [CrossRef]

- Millán, J.; Friedrichs, P.; Mihaila, A.; Soler, V.; Rebollo, J.; Banu, V.; Godignon, P. High-voltage SiC devices: Diodes and MOSFETs. In Proceedings of the International Semiconductor Conference (CAS), Sinaia, Romania, 12–14 October 2015; pp. 11–18. [Google Scholar]

- Dong, D.; Agamy, M.; Bebic, J.Z.; Chen, Q.; Mandrusiak, G. A Modular SiC High-Frequency Solid-State Transformer for Medium-Voltage Applications: Design, Implementation, and Testing. IEEE J. Emerg. Sel. Top. Power Electron. 2019, 7, 768–778. [Google Scholar] [CrossRef]

- Raju, R.; Dame, M.; Steigerwald, R. Solid-state transformer using silicon carbide-based modular building blocks. In Proceedings of the IEEE International Conference of Power Electronics and Drive Systems (PEDS), Honolulu, HI, USA, 12–15 December 2017; pp. 1–7. [Google Scholar]

- Yao, R.; Zheng, Z. Design and control of a SiC-based three-stage AC to DC power electronic transformer for electric traction applications. J. Eng. 2019, 2019, 2947–2952. [Google Scholar] [CrossRef]

- Wang, G.; Huang, X.; Wang, J.; Zhao, T.; Bhattacharya, S.; Huang, A.Q. Comparisons of 6.5kV 25A Si IGBT and 10-kV SiC MOSFET in Solid-State Transformer application. In Proceedings of the IEEE Energy Conversion Congress and Exposition (ECCE), Atlanta, GA, USA, 12–16 September 2010; pp. 100–104. [Google Scholar]

- Madhusoodhanan, S.; Tripathi, A.; Patel, D.; Mainali, K.; Kadavelugu, A.; Hazra, S.; Bhattacharya, S.; Hatua, K. Solid-State Transformer and MV Grid Tie Applications Enabled by 15 kV SiC IGBTs and 10 kV SiC MOSFETs Based Multilevel Converters. IEEE Trans. Ind. Appl. 2015, 51, 3343–3360. [Google Scholar] [CrossRef]

- Hatua, K.; Dutta, S.; Tripathi, A.; Baek, S.; Karimi, G.; Bhattacharya, S. Transformerless intelligent power substation design with 15 kV SiC IGBT for grid interconnection. In Proceedings of the IEEE Energy Conversion Congress and Exposition (ECCE), Phoenix, AZ, USA, 17–22 September 2011; pp. 4225–4232. [Google Scholar]

- Abu-Siada, A.; Budiri, J.; Abdou, A.F. Solid State Transformers Topologies, Controllers, and Applications: State-of-the-Art Literature Review. Electronics 2018, 7, 298. [Google Scholar] [CrossRef]

- Evans, N.M.; Lagier, T.; Pereira, A. A preliminary loss comparison of solid-state transformers in a rail application employing silicon carbide (SiC) MOSFET switches. In Proceedings of the 8th IET International Conference on Power Electronics, Machines and Drives (PEMD), Glasgow, UK, 19 April 2016; pp. 1–6. [Google Scholar]

- Lopez, M.; Briz, F.; Zapico, A.; Rodriguez, A.; Diaz-Reigosa, D. Control strategies for MMC using cells with power transfer capability. In Proceedings of the IEEE Energy Conversion Congress and Exposition (ECCE), Montreal, QC, Canada, 20–24 September 2015; pp. 3570–3577. [Google Scholar]

- Cuartas, J.M.; de la Cruz, A.; Briz, F.; Lopez, M. Start-up, functionalities and protection issues for CHB-based solid state transformers. In Proceedings of the IEEE International Conference on Environment and Electrical Engineering and IEEE Industrial and Commercial Power Systems Europe (EEEIC/I&CPS Europe), Milan, Italy, 6–9 June 2017; pp. 1–5. [Google Scholar]

- López, M.; Briz, F.; Saeed, M.; Arias, M.; Rodríguez, A. Comparative analysis of modular multiport power electronic transformer topologies. In Proceedings of the IEEE Energy Conversion Congress and Exposition (ECCE), Milwaukee, WI, USA, 18–22 September 2016; pp. 1–8. [Google Scholar]

- Briz, F.; Lopez, M.; Rodriguez, A.; Arias, M. Modular Power Electronic Transformers: Modular Multilevel Converter versus Cascaded H-Bridge Solutions. IEEE Ind. Electron. Mag. 2016, 10, 6–19. [Google Scholar] [CrossRef]

- Briz, F.; López, M.; Zapico, A.; Rodríguez, A.; Díaz-Reigosa, D. Operation and control of MMCs using cells with power transfer capability. In Proceedings of the IEEE Applied Power Electronics Conference and Exposition (APEC), Charlotte, NC, USA, 15–19 March 2015; pp. 980–987. [Google Scholar]

- European Union. “Silicon Carbide Power Technology for Energy Efficient Devices (SPEED)”, Ref. FP7-NMP3-LA-2013-604057, EU–FP7, Large Scale Integrating Collaborative Research Project. Available online: https://cordis.europa.eu/project/id/604057 (accessed on 4 March 2020).

- Wensong, Y. Wide Band-Gap Devices for Solid State Transformer Applications; Tutorial; FREEDM Systems Center: Raleigh, NC, USA, 2017. [Google Scholar]

- ROHM Semiconductor Electronics Industry Company. Available online: www.rohm.com (accessed on 2 March 2020).

- Wolfspeed, Inc. Available online: www.wolfspeed.com (accessed on 2 March 2020).

- Zhang, L.; Yuan, X.; Wu, X.; Shi, C.; Zhang, J.; Zhang, Y. Performance Evaluation of High-Power SiC MOSFET Modules in Comparison to Si IGBT Modules. IEEE Trans. Power Electron. 2019, 34, 1181–1196. [Google Scholar] [CrossRef]

- Malinowski, M.; Gopakumar, K.; Rodriguez, J.; Perez, M.A. A Survey on Cascaded Multilevel Inverters. IEEE Trans. Ind. Electron. 2010, 57, 2197–2206. [Google Scholar] [CrossRef]

- Rodriguez, J.; Lai, J.-S.; Peng, F.Z. Multilevel inverters: A survey of topologies, controls, and applications. IEEE Trans. Ind. Electron. 2002, 49, 724–738. [Google Scholar] [CrossRef]

- Sahib, A.; Abdulbaqi, I.M.; Ahmed, A.H. Analysis of a Four-Leg Inverter Feeding a Nonlinear Load using SVPWM Technique. In Proceedings of the Second Al-Sadiq International Conference on Multidisciplinary in IT and Communication Science and Applications (AIC-MITCSA), Baghdad, Iraq, 30–31 December 2017; pp. 19–24. [Google Scholar]

- Martin, D.; Killeen, P.; Curbow, W.A.; Sparkman, B.; Kegley, L.E.; McNutt, T. Comparing the switching performance of SiC MOSFET intrinsic body diode to additional SiC schottky diodes in SiC power modules. In Proceedings of the IEEE 4th Workshop on Wide Bandgap Power Devices and Applications (WiPDA), Fayetteville, AR, USA, 7–9 November 2016; pp. 242–246. [Google Scholar]

- Rodriguez, A.; Rogina, M.R.; Saeed, M.; Lamar, D.G.; Arias, M.; Lopez, M.; Briz, F. Auxiliary power supply based on a modular ISOP flyback configuration with very high input voltage. In Proceedings of the IEEE Energy Conversion Congress and Exposition (ECCE), Milwaukee, WI, USA, 18–22 September 2016; pp. 1–7. [Google Scholar]

- Huber, J.E.; Kolar, J.W. Solid-State Transformers: On the Origins and Evolution of Key Concepts. IEEE Ind. Electron. Mag. 2016, 10, 19–28. [Google Scholar] [CrossRef]

- McLyman, C.W.T. High Reliability Magnetic Devices: Design and Fabrication; Marcel Dekker: New York, NY, USA, 2002. [Google Scholar]

- Saeed, M.; Cuartas, J.M.; Rodriguez, A.; Arias, M.; Briz, F. Energization and Start-Up of CHB-Based Modular Three-Stage Solid-State Transformers. IEEE Trans. Ind. Appl. 2018, 54, 5483–5492. [Google Scholar] [CrossRef]

- de Doncker, R.W.; Divan, R.W.; Kheraluwala, M.H. A three-phase soft-switched high power-density dc/dc converter for high-power applications. IEEE Trans. Ind. Appl. 1991, 27, 63–73. [Google Scholar] [CrossRef]

- Kheraluwala, M.H.; Gascoigne, R.W.; Divan, D.M.; Baumann, E.D. Performance characterization of a high-power dual active bridge dc-to-dc converter. IEEE Trans. Ind. Appl. 1992, 28, 1294–1301. [Google Scholar] [CrossRef]

- Rodríguez, A.; Sebastian, J.; Lamar, D.G.; Hernando, M.M.; Vazquez, A. An overall study of a dual active bridge for bidirectional DC/DC conversion. In Proceedings of the IEEE Energy Conversion Congress & Exposition (ECCE), Atlanta, GA, USA, 12–16 September 2010; pp. 1129–1135. [Google Scholar]

- Calderon, C.; Barrado, A.; Rodriguez, A.; Alou, P.; Lazaro, A.; Fernandez, C.; Zumel, P. General Analysis of Switching Modes in a Dual Active Bridge with Triple Phase Shift Modulation. Energies 2018, 11, 2419. [Google Scholar] [CrossRef]

- Wang, G.; Huang, A.Q.; Wang, F.; Song, X.; Ni, X.; Ryu, S.H.; Grider, D.; Schupbach, M.; Palmour, J. Static and dynamic performance characterization and comparison of 15 kV SiC MOSFET and 15 kV SiC n-IGBTs. In Proceedings of the IEEE 27th International Symposium on Power Semiconductor Devices & IC’s (ISPSD), Hong Kong, China, 10–14 May 2015; pp. 229–232. [Google Scholar]

- Kumar, A.; Parashar, S.; Sabri, S.; van Brunt, E.; Bhattacharya, S.; Veliadis, V. Ruggedness of 6.5 kV, 30 a SiC MOSFETs in extreme transient conditions. In Proceedings of the IEEE 30th International Symposium on Power Semiconductor Devices and ICs (ISPSD), Chicago, IL, USA, 13–17 May 2018; pp. 423–426. [Google Scholar]

- Wang, L.; Zhu, Q.; Yu, W.; Huang, A.Q. A medium voltage bidirectional DC-DC converter combining resonant and dual active bridge converters. In Proceedings of the IEEE Applied Power Electronics Conference and Exposition (APEC), Charlotte, NC, USA, 15–19 March 2015; pp. 1104–1111. [Google Scholar]

- Wang, F.; Wang, G.; Huang, A.; Yu, W.; Ni, X. Design and operation of A 3.6kV high performance solid state transformer based on 13kV SiC MOSFET and JBS diode. In Proceedings of the IEEE Energy Conversion Congress and Exposition (ECCE), Pittsburgh, PA, USA, 14–18 September 2014; pp. 4553–4560. [Google Scholar]

- Pala, V.; Brunt, E.V.; Cheng, L.; O’Loughlin, M.; Richmond, J.; Burk, A.; Allen, S.T.; Grider, D.; Palmour, J.W.; Scozzie, C.J. 10 kV and 15 kV silicon carbide power MOSFETs for next-generation energy conversion and transmission systems. In Proceedings of the IEEE Energy Conversion Congress and Exposition (ECCE), Pittsburgh, PA, USA, 14–18 September 2014; pp. 449–454. [Google Scholar]

- Yun, C.-G.; Cho, Y. Active Hybrid Solid State Transformer Based on Multi-Level Converter Using SiC MOSFET. Energies 2019, 12, 66. [Google Scholar] [CrossRef]

- Mu, M.; Xue, L.; Boroyevich, D.; Hughes, B.; Mattavelli, P. Design of integrated transformer and inductor for high frequency dual active bridge GaN Charger for PHEV. In Proceedings of the IEEE Applied Power Electronics Conference and Exposition (APEC), Charlotte, NC, USA, 15–19 March 2015; pp. 579–585. [Google Scholar]

- Hoang, K.D.; Wang, J. Design optimization of high frequency transformer for dual active bridge DC-DC converter. In Proceedings of the XXth International Conference on Electrical Machines (ICEM), Marseille, France, 2–5 September 2012; pp. 2311–2317. [Google Scholar]

- Saeed, M.; Rogina, M.R.; Lopez, M.; Rodriguez, A.; Arias, M.; Briz, F. Design and construction of a DAB using SiC MOSFETs with an isolation of 24 kV for PET applications. In Proceedings of the IEEE 19th European Conference on Power Electronics and Applications (EPE’17 ECCE Europe), Warsaw, Poland, 11–14 September 2017; pp. P.1–P.10. [Google Scholar]

- Ortiz, G.; Biela, J.; Kolar, J.W. Optimized design of medium frequency transformers with high isolation requirements. In Proceedings of the IEEE IECON—36th Annual Conference on Industrial Electronics Society, Glendale, AZ, USA, 7–10 November 2010; pp. 631–638. [Google Scholar]

- Zhao, S.; Li, Q.; Lee, F.C. High frequency transformer design for modular power conversion from medium voltage AC to 400V DC. In Proceedings of the IEEE Applied Power Electronics Conference and Exposition (APEC), Tampa, FL, USA, 26–30 March 2017; pp. 2894–2901. [Google Scholar]

- Chen, Q.; Raju, R.; Dong, D.; Agamy, M. High Frequency Transformer Insulation in Medium Voltage SiC enabled Air-cooled Solid-State Transformers. In Proceedings of the IEEE Energy Conversion Congress and Exposition (ECCE), Portland, OR, USA, 23–27 September 2018; pp. 2436–2443. [Google Scholar]

| Element | Parameter | Value |

|---|---|---|

| PET | Rated power | 105 kW |

| Number of cells | 21 (7 per phase) | |

| HV/LV grid voltage (L-L) | 6 kV/400 V | |

| DAB | Rated power | 5 kW |

| Switching frequency (fsw) | 30 kHz | |

| HFT isolation | 24 kV | |

| Input voltage (Vi = Vcell) | 800 V | |

| Transformer turns ratio (n) | 1:1 | |

| Leakage inductance (Llk) | 423 μH | |

| CHB | Rated power | 5 kW |

| Ccell | 600 µF(film) |

| Manufacturer | Reference | Package | Rated Current @100 °C (A) | RDS (mΩ) | Cout (pF) | Efficiency (%) | Price per Bridge (€) | ||

|---|---|---|---|---|---|---|---|---|---|

| 30 kHz | 50 kHz | 100 kHz | |||||||

| ST | SCT30N120 | TO-247-3 | 34 | 80 | 130 | 97.77 | 98.16 | 97.81 | 100 |

| ROHM | SCH2080KE + SBD | 28 | 80 | 175 | 97.71 | 98.02 | 97.69 | 132 | |

| SCT2080KE | 28 | 80 | 77 | 97.82 | 98.17 | 97.93 | 80 | ||

| CREE | C2M0040120D | 40 | 40 | 150 | 97.76 | 98.10 | 97.84 | 128 | |

| C2M0025120D | 60 | 25 | 220 | 97.56 | 97.88 | 97.42 | 252 | ||

| CAS120M12BM2 + SBD | 6-pack 45 mm | 59 | 25 | 400 | 97.49 | 97.54 | 97.50 | 412 | |

| CCS050M12CM2 + SBD | Half-bridge 62 mm | 138 | 13 | 900 | 96.44 | 95.8 | - | 660 | |

| Characteristics | SCH2080KE +SBD | SCT2080KE | |

|---|---|---|---|

| RON-MOSFET | 125 mΩ | ||

| Eoff (Rg = 10 Ω) | 110 µJ | 120 µJ | |

| Eon (Rg = 10 Ω) | 330 µJ | 275 µJ | |

| Anti-parallel diode | Type | SiC SBD | Body diode |

| RD (Estimated) | 45 mΩ | 320 mΩ | |

| Vknee | 0.85 V | 1.4 V | |

| VF-Diode (@ Ip_lk) | 1.2 V | 4.5 V | |

| Interval | Losses | SCH2080KE +SBD | SCT2080KE | |

|---|---|---|---|---|

| Dead time (600 ns) | Diode conduction (Pdeadtime) | 1.6 W | 6.2 W | |

| (3) & (6) | Switching (Psw) | 26.4 W | 28.8 W | |

| Conduction | PMOSFET-prim | 17.4 W | 17.4 W | |

| PMOSFET-sec | 10.4 W | 17.4 W | ||

| PDiode-sec | 2.8 W | - | ||

| Total losses | 58.6 W | 69.8 W | ||

| Characteristics | SCH2080KE +SBD | SCT2080KE |

|---|---|---|

| Antiparallel diode | SiC SBD | Body diode |

| Efficiency (η) | 98.1% | 97.8% |

| Phase-shift (d) | 0.29 | |

| Dead time | 600 ns | |

| Calculated from Equation (1): 9 A | ||

| Measured (experimental): 9.8 A | ||

| Element | Characteristics | Reference |

|---|---|---|

| DAB | ROHM 1.2 kV, 28 A SiC MOSFET | SCH2080KE |

| CREE 2-channel drivers | CGD15HB62P1 | |

| CHB | Infineon 1.7 kV Si IGBT + SiC diode | Not commercial |

| Infineon two-channel drivers | 2ED300C17-S | |

| Controller | Xilinx FPGA (Spartan 3E) custom board | XC3S250E-4TQG144I |

| Quantity | Value |

|---|---|

| Isolation | 24 kV |

| Core structure | UU100/57/25 |

| Ferrite material | Ferroxcube® 3C90 |

| Encapsulation | Epoxy resin (15 kV/mm) (ROYAPOX 912 THC/2) |

| Bobbins | GPO-3 (20 kV/mm) |

| Number of turns (N) | 35 |

| Temperature rise at NTC 4 | 40˚C |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Saeed, M.; Rogina, M.R.; Rodríguez, A.; Arias, M.; Briz, F. SiC-Based High Efficiency High Isolation Dual Active Bridge Converter for a Power Electronic Transformer. Energies 2020, 13, 1198. https://doi.org/10.3390/en13051198

Saeed M, Rogina MR, Rodríguez A, Arias M, Briz F. SiC-Based High Efficiency High Isolation Dual Active Bridge Converter for a Power Electronic Transformer. Energies. 2020; 13(5):1198. https://doi.org/10.3390/en13051198

Chicago/Turabian StyleSaeed, Mariam, María R. Rogina, Alberto Rodríguez, Manuel Arias, and Fernando Briz. 2020. "SiC-Based High Efficiency High Isolation Dual Active Bridge Converter for a Power Electronic Transformer" Energies 13, no. 5: 1198. https://doi.org/10.3390/en13051198

APA StyleSaeed, M., Rogina, M. R., Rodríguez, A., Arias, M., & Briz, F. (2020). SiC-Based High Efficiency High Isolation Dual Active Bridge Converter for a Power Electronic Transformer. Energies, 13(5), 1198. https://doi.org/10.3390/en13051198