Comprehensive Analysis of a High-Power Density Phase-Shift Full Bridge Converter Highlighting the Effects of the Parasitic Capacitances †

Abstract

1. Introduction

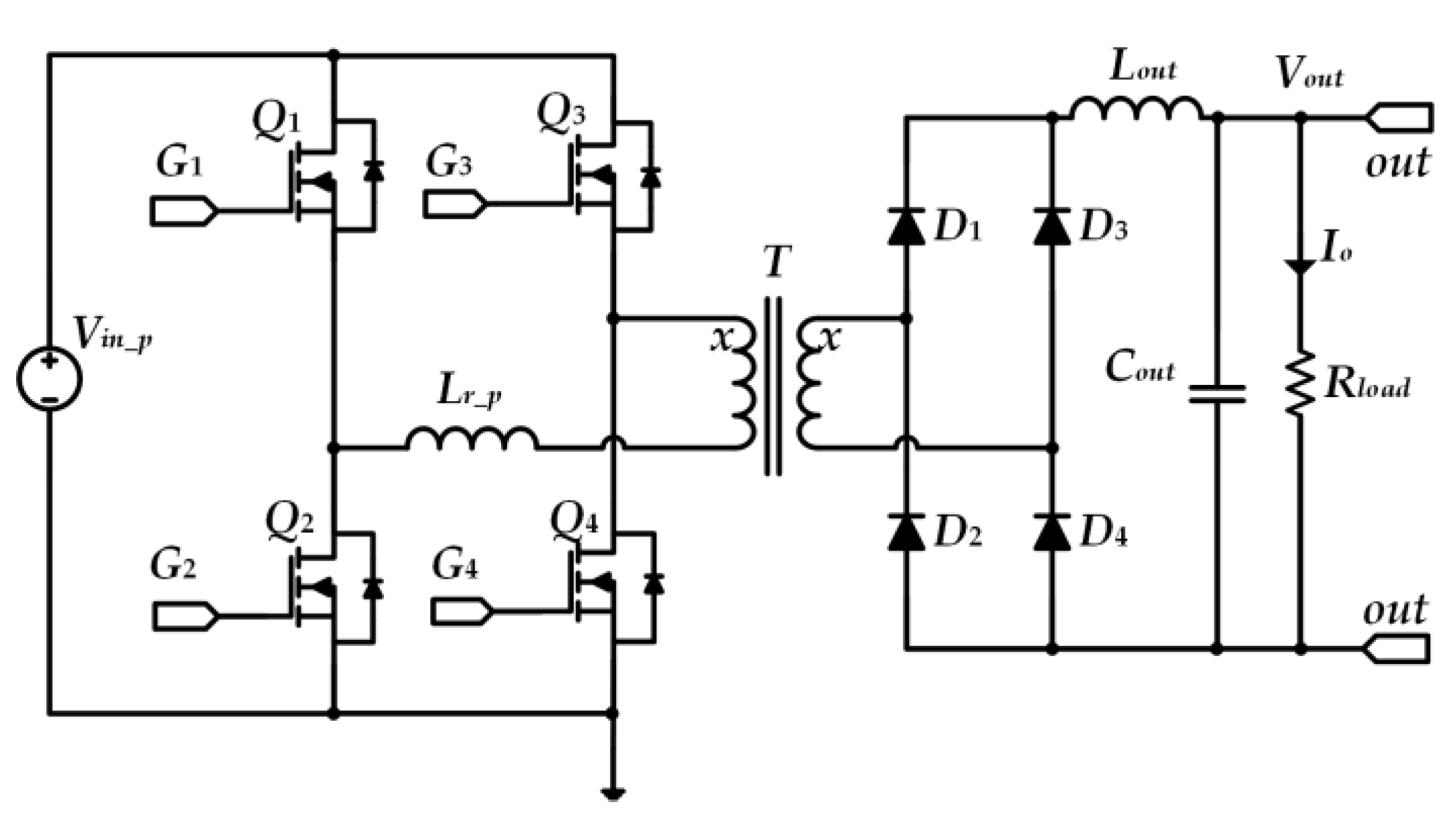

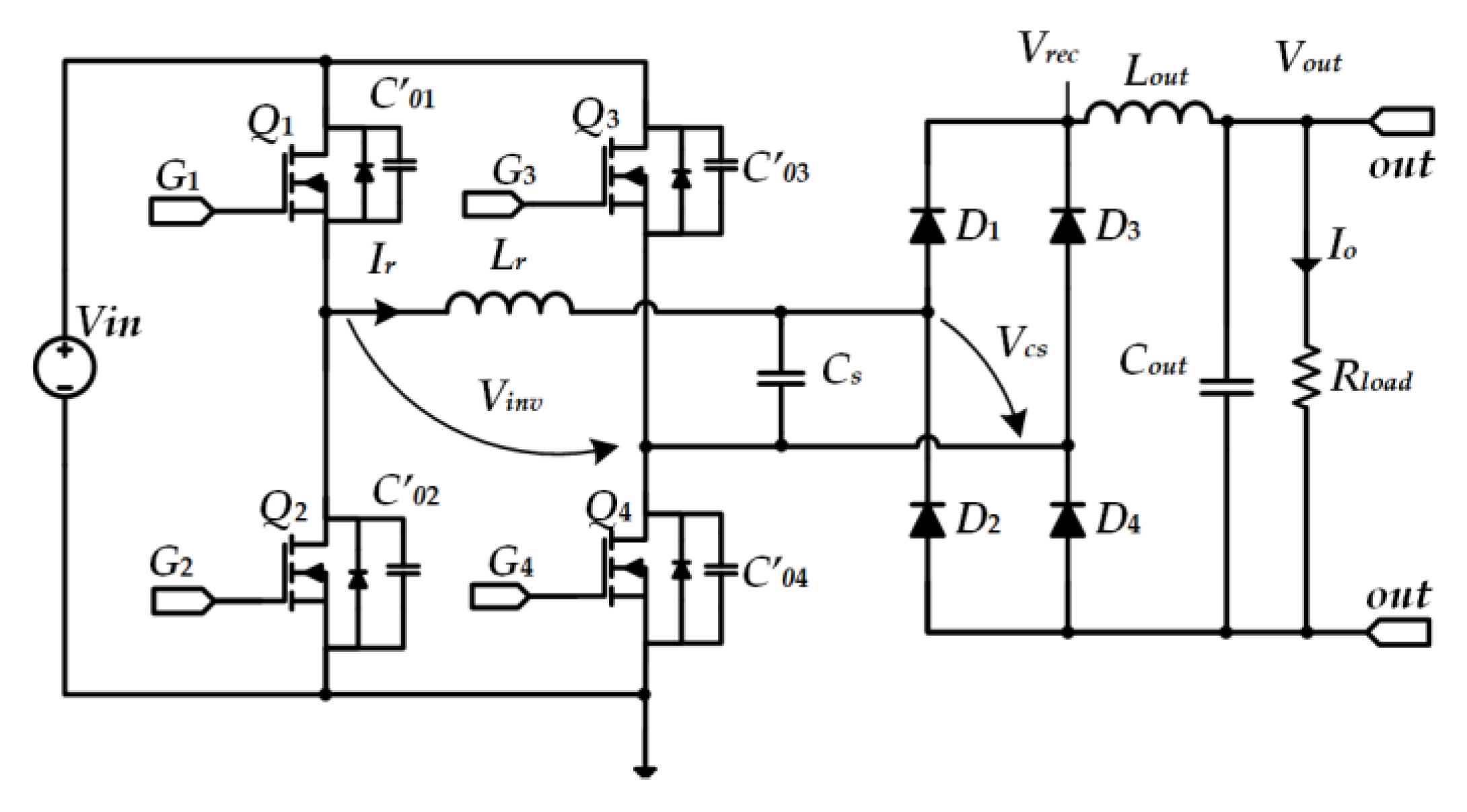

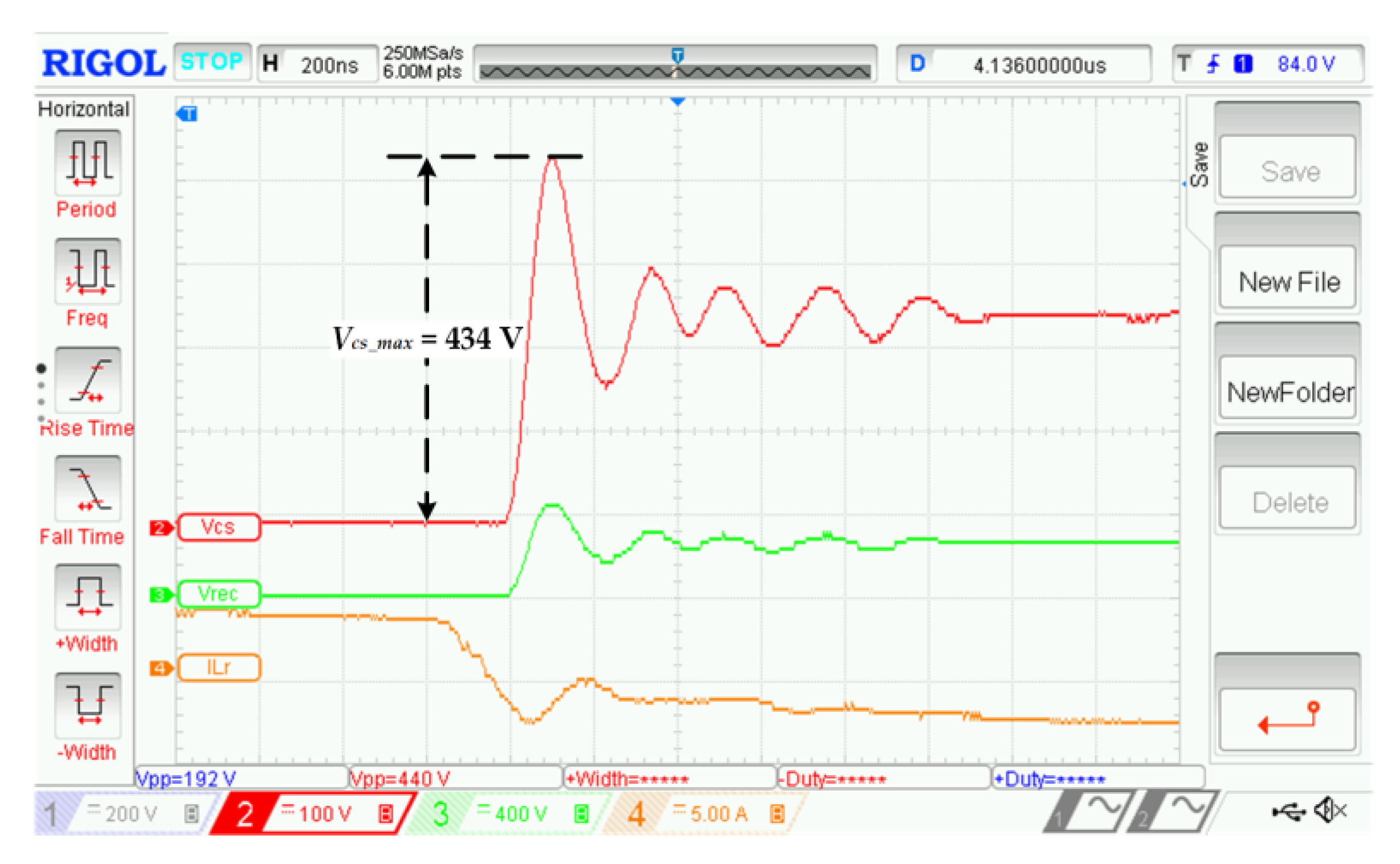

2. Motivation

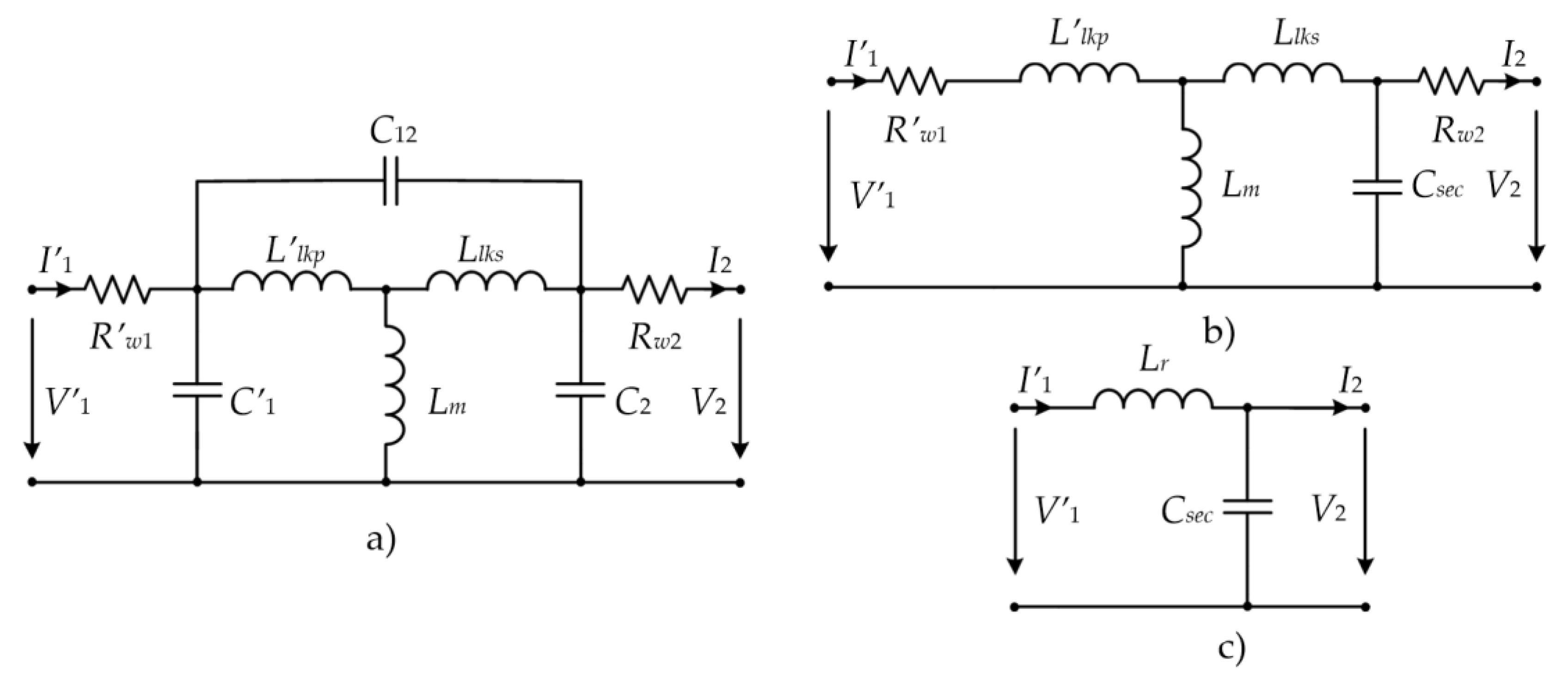

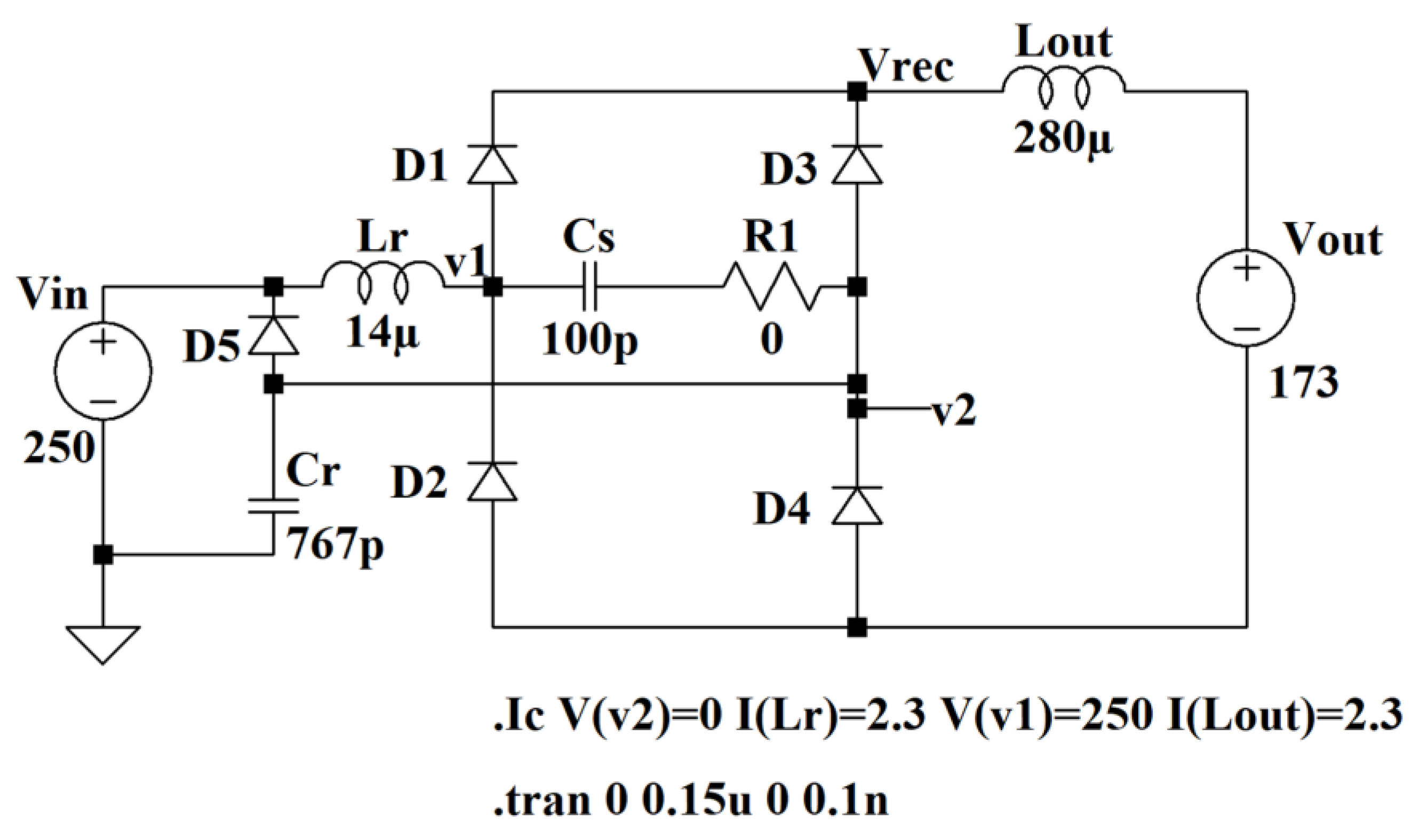

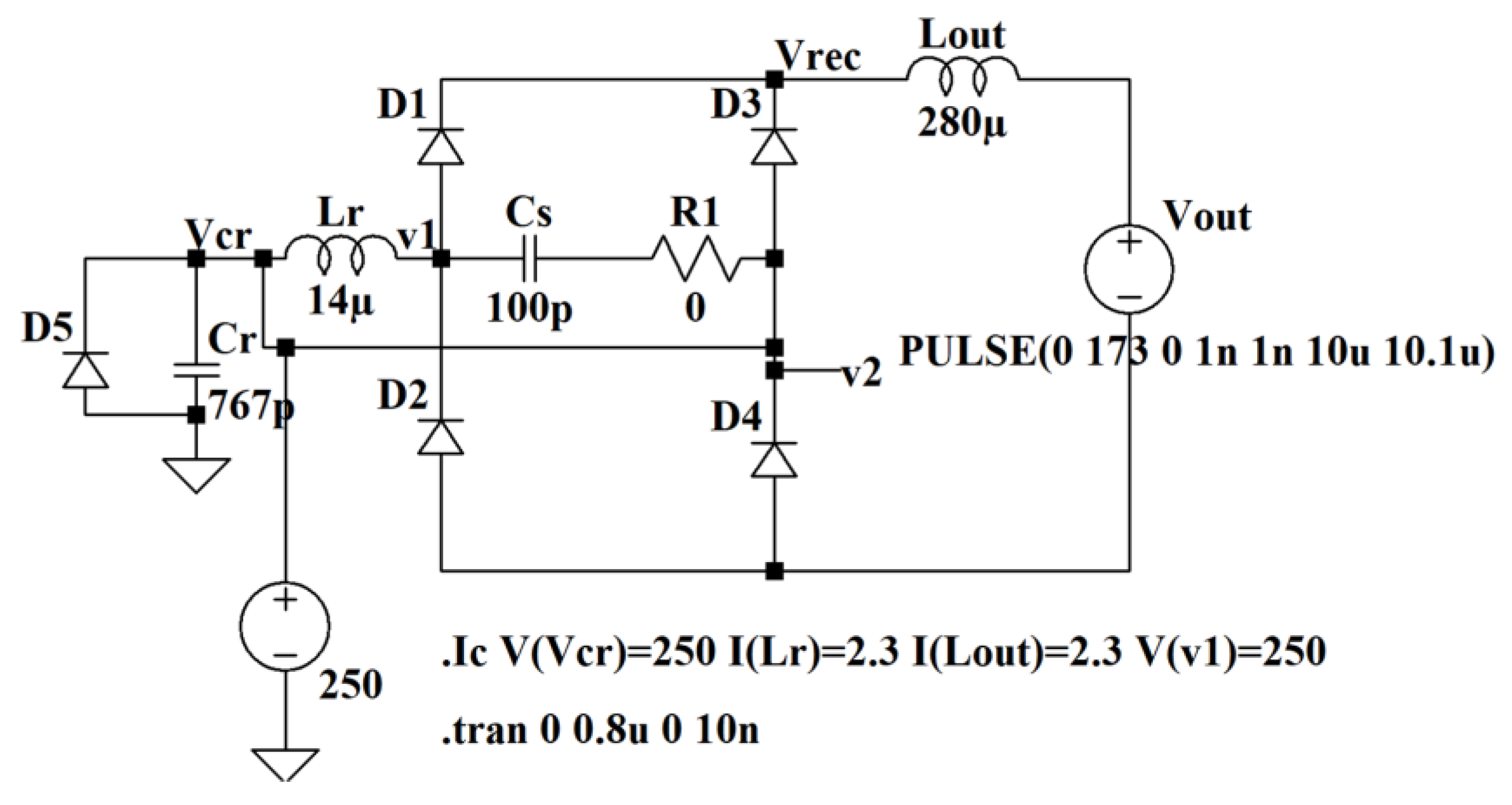

3. The Model of the Converter

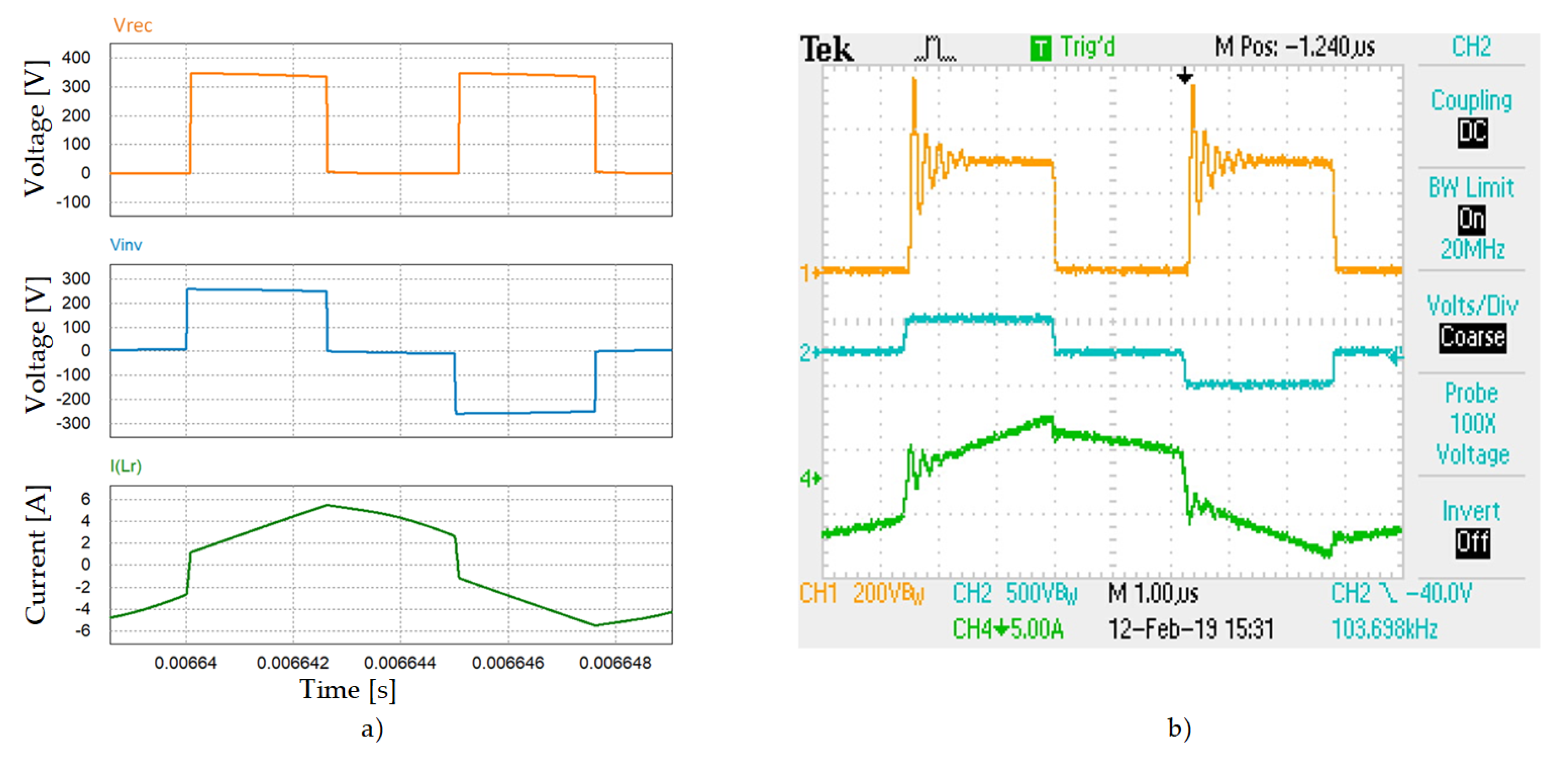

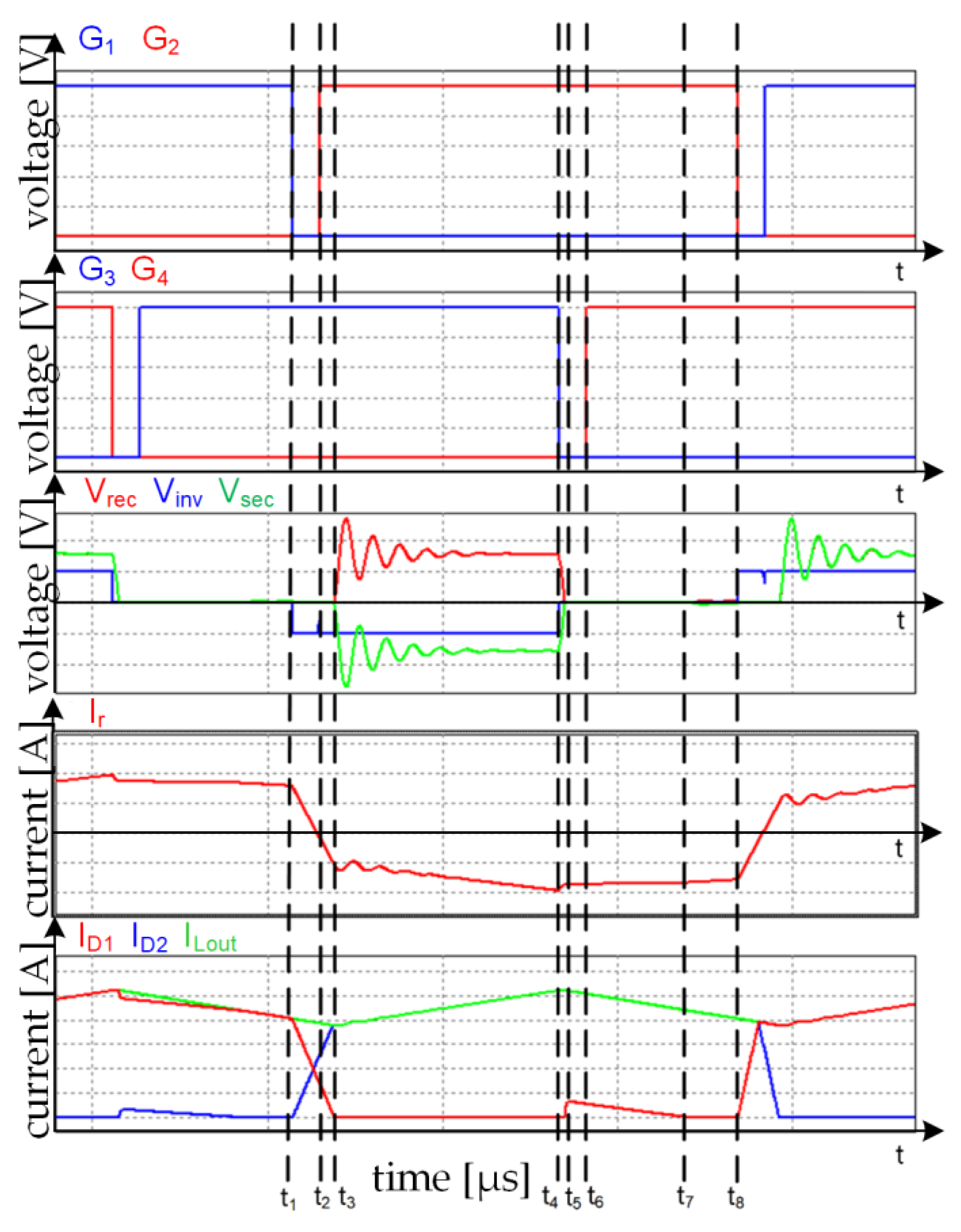

4. Converter Operation

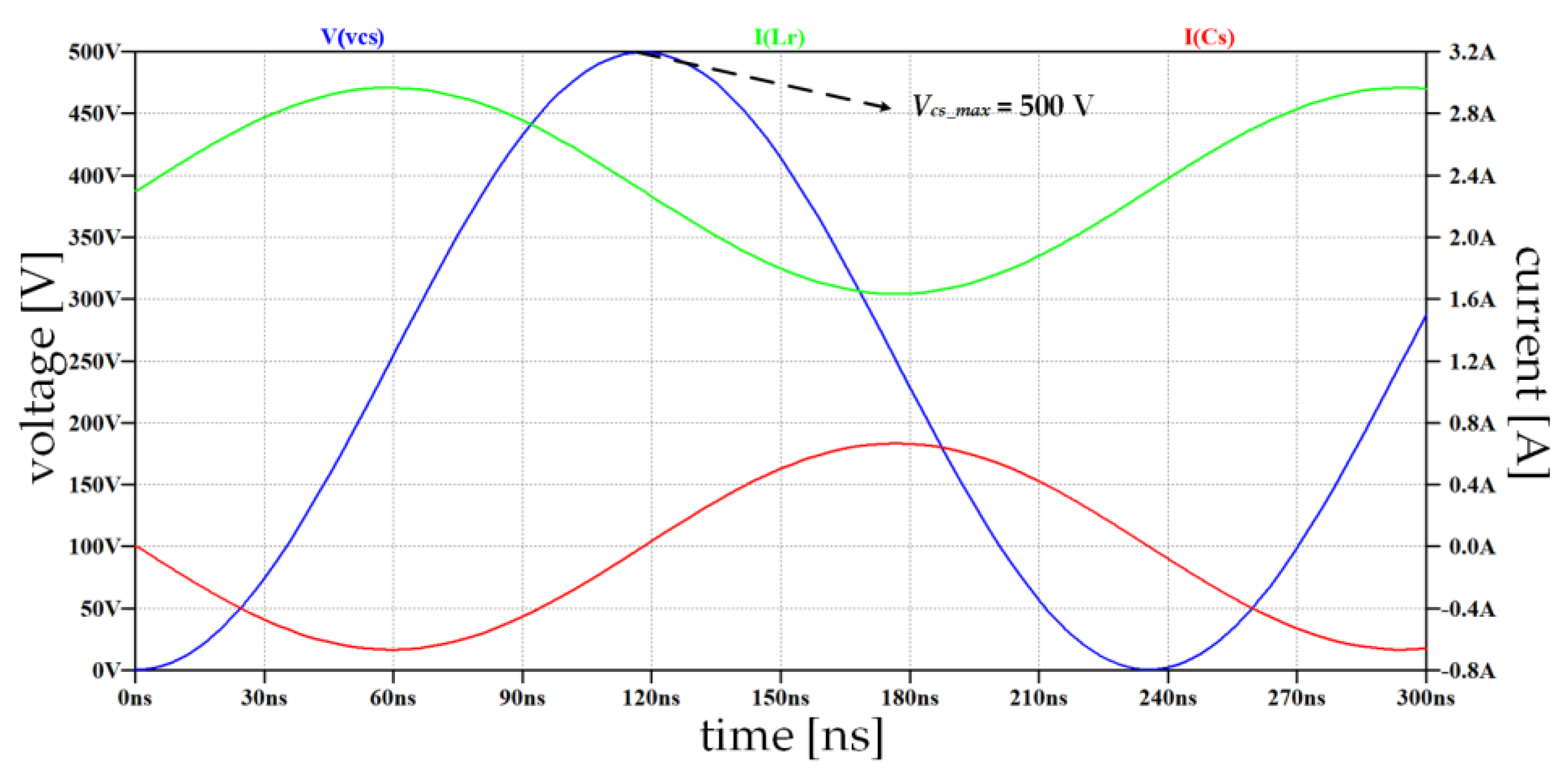

4.1. Operation during [t1-t3]

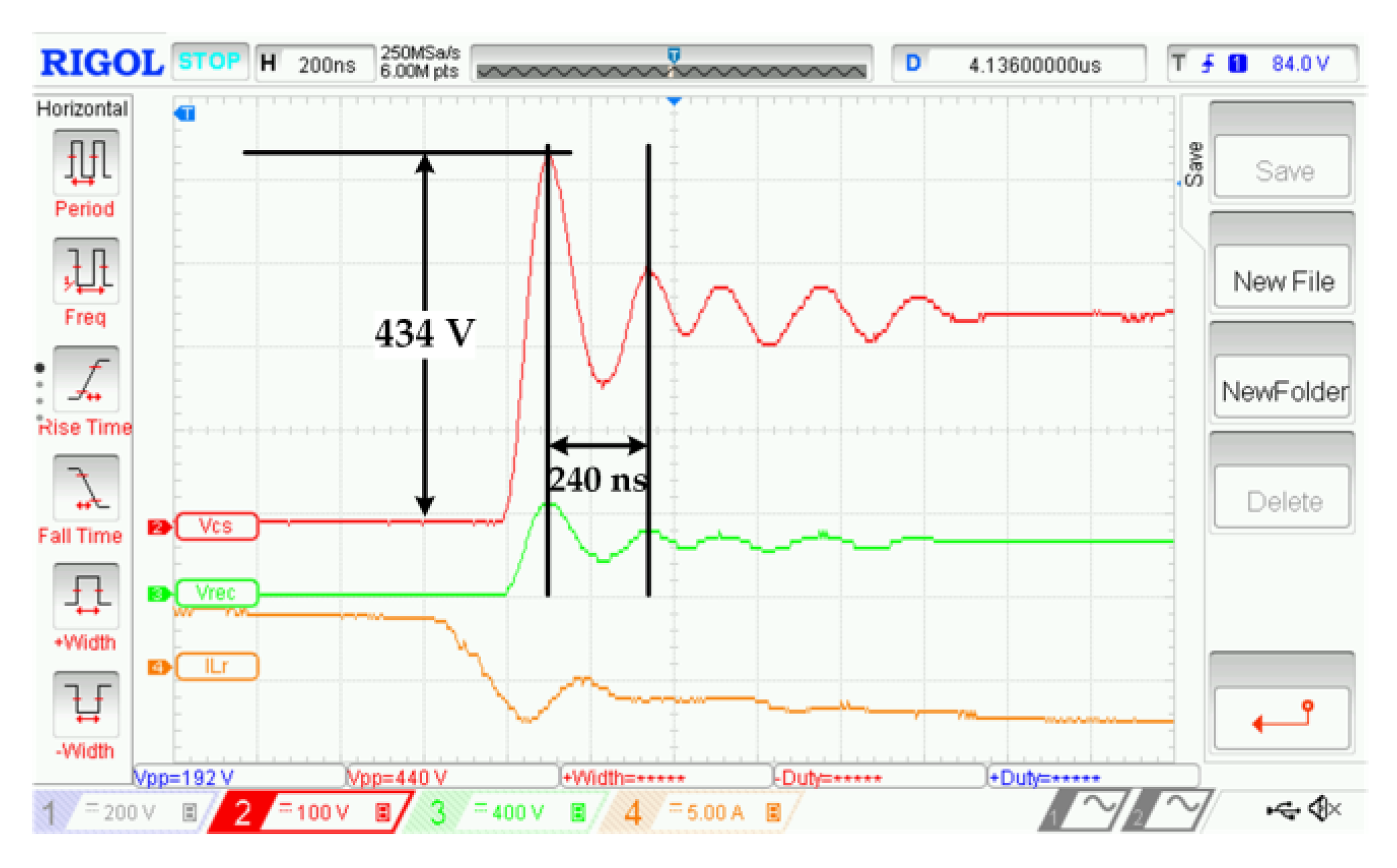

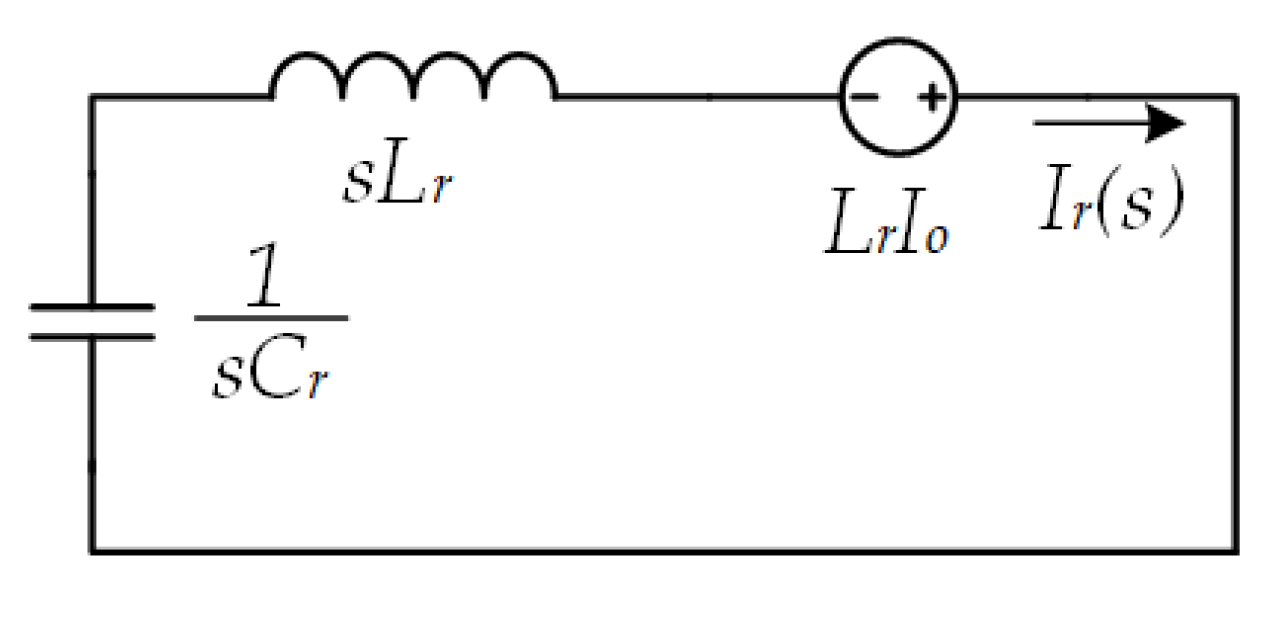

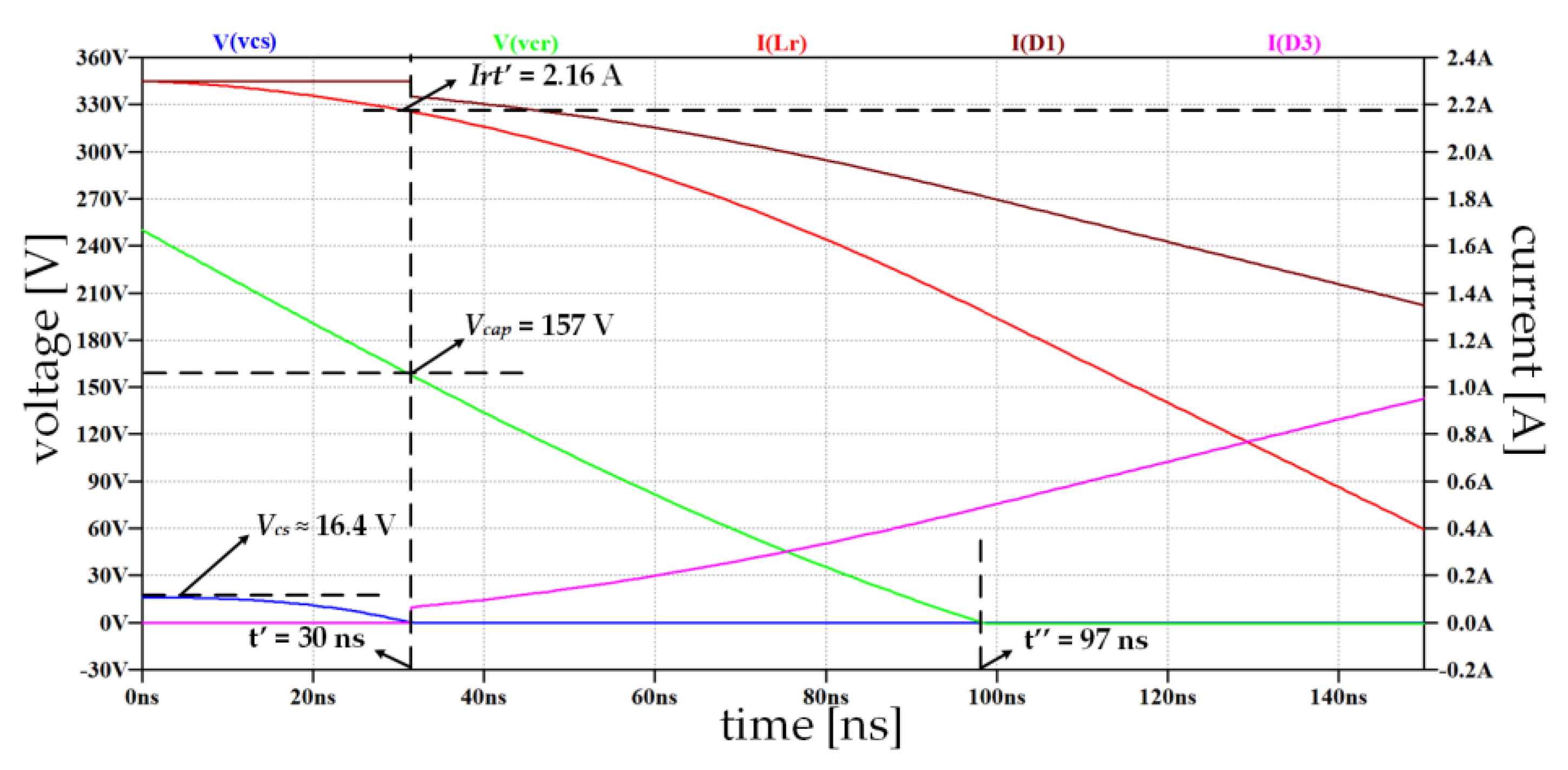

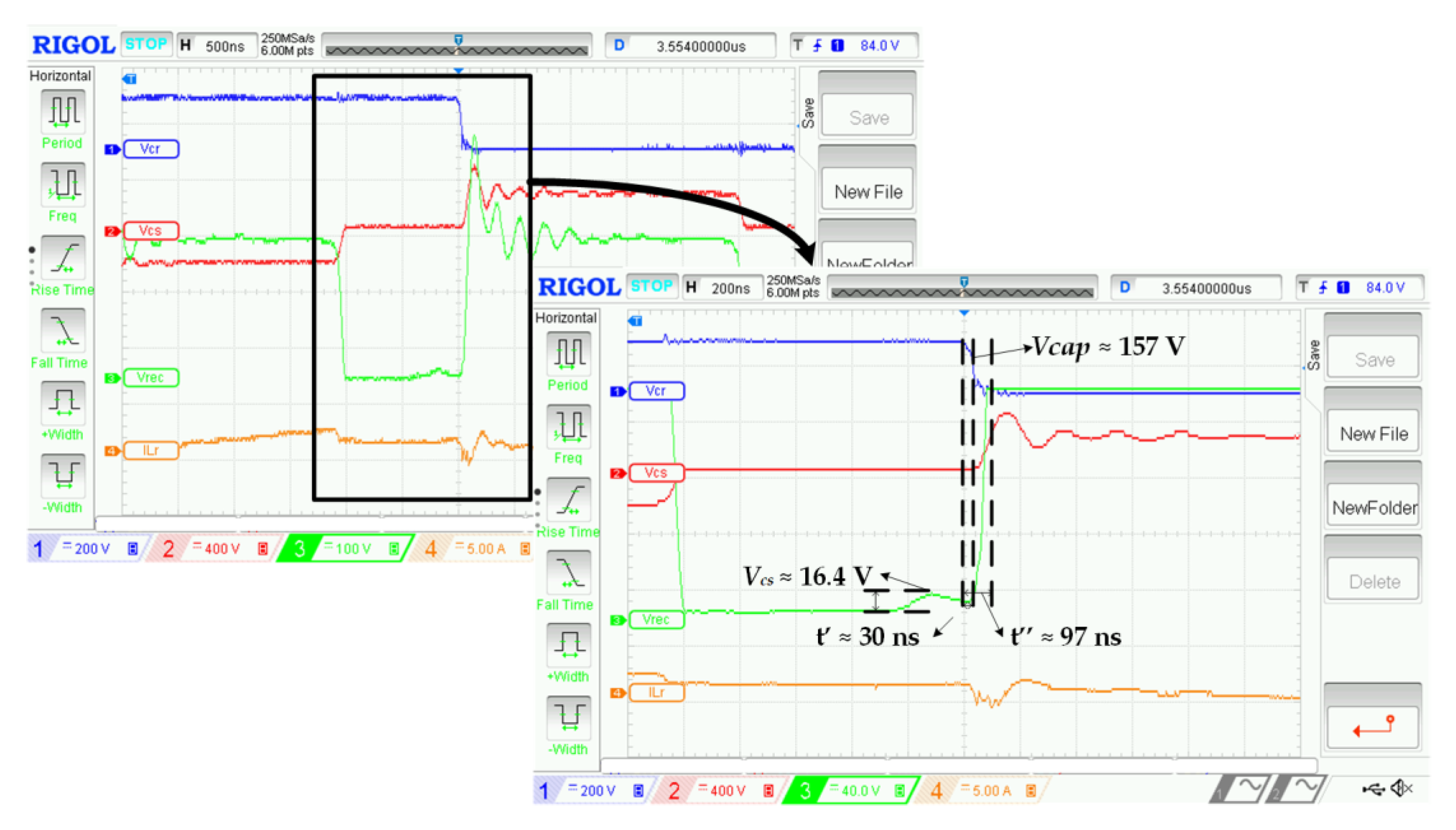

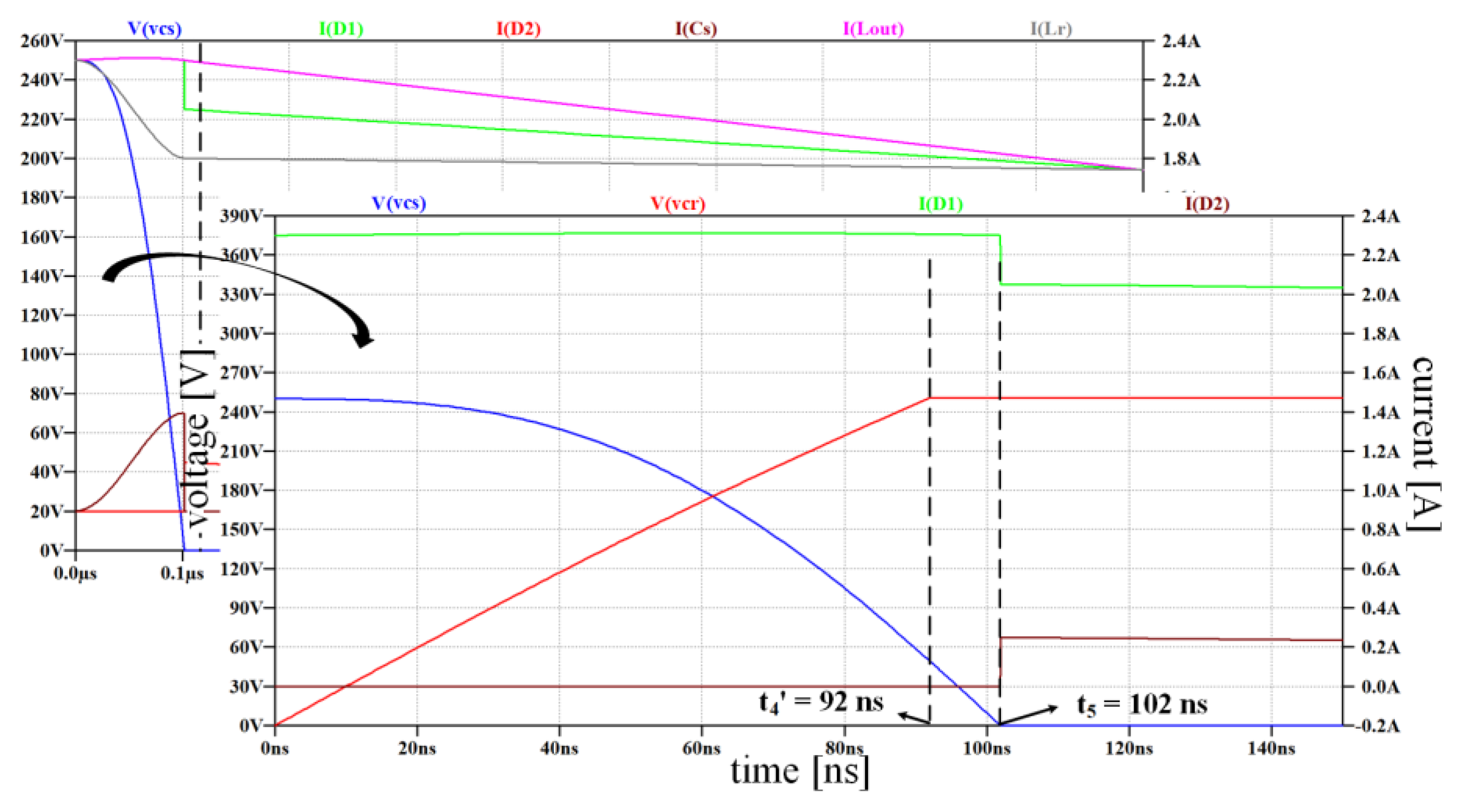

4.2. Operation during [t3-t4], immediately after t3

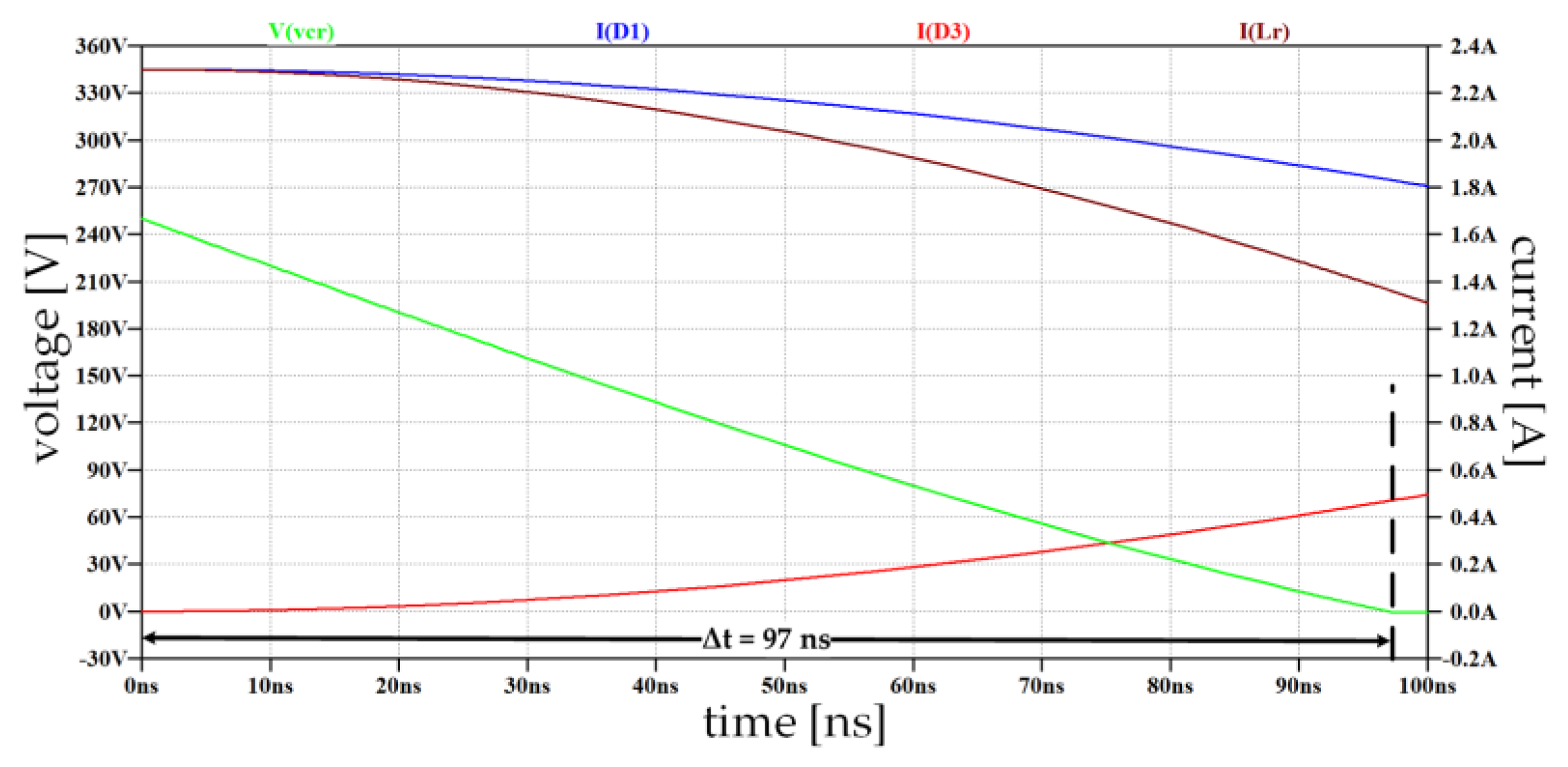

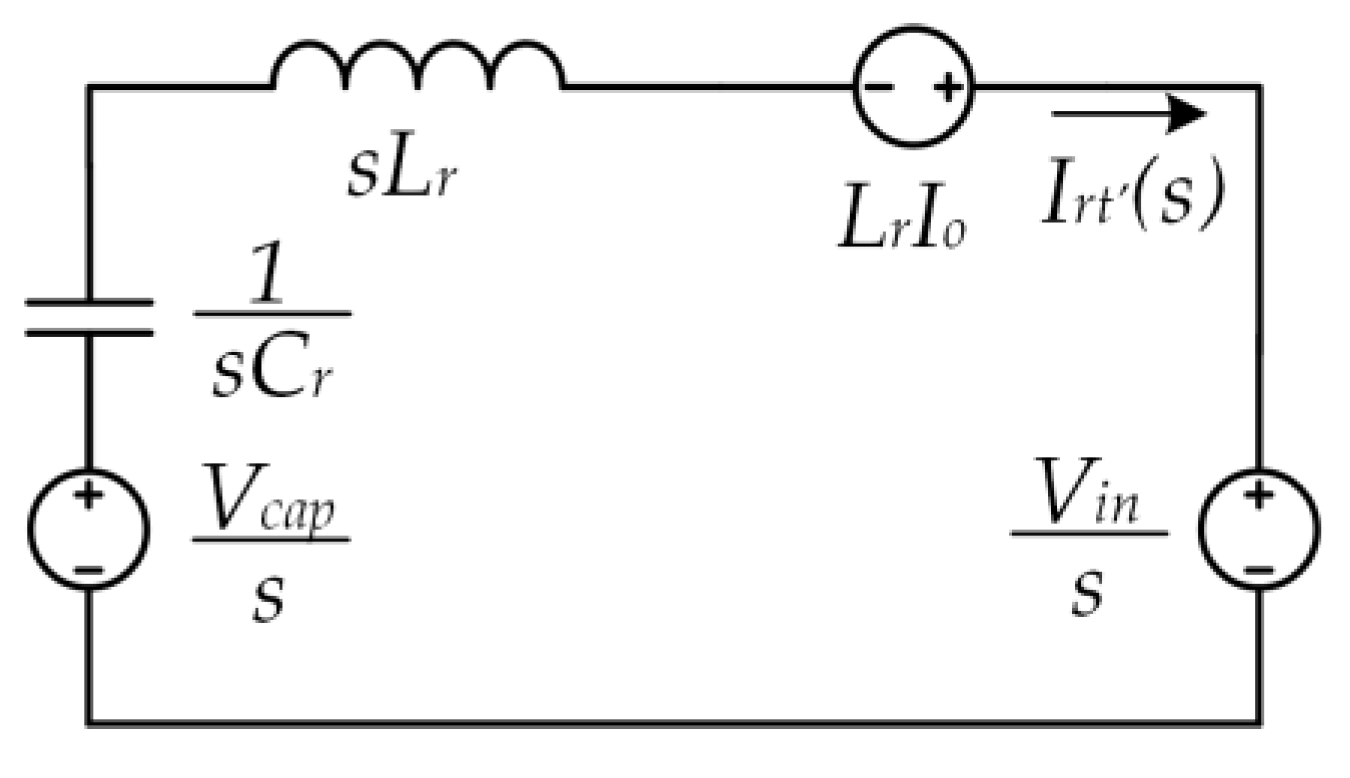

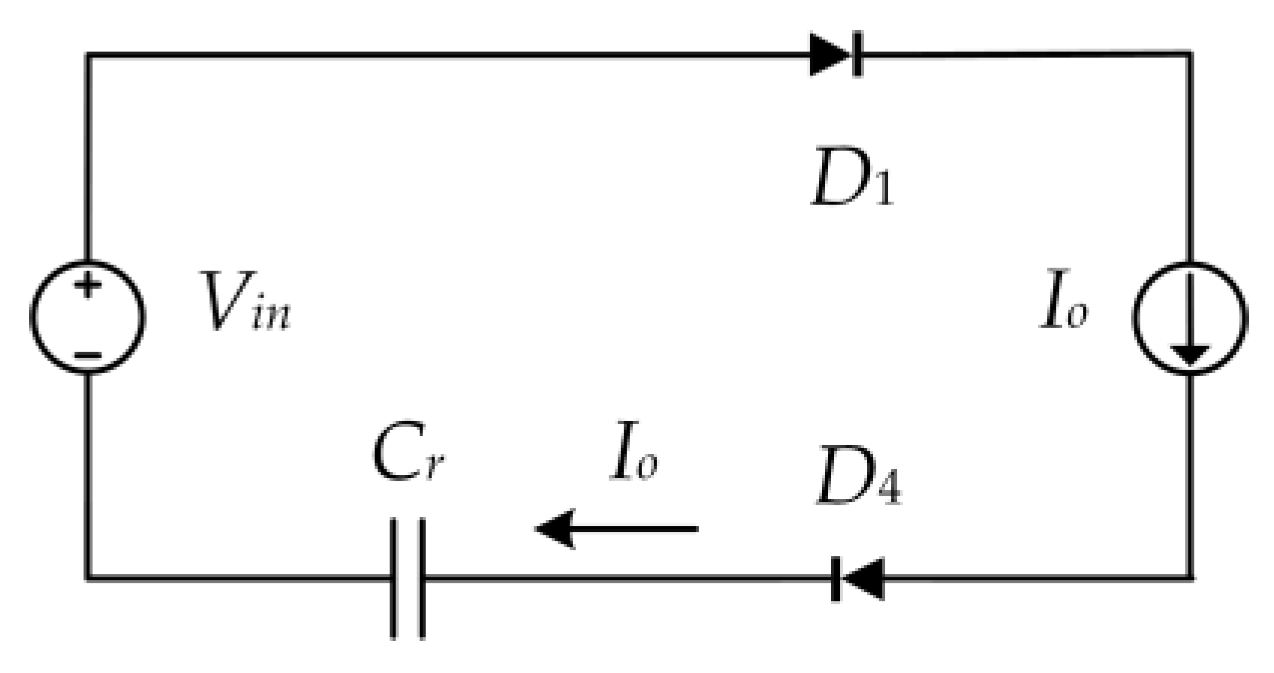

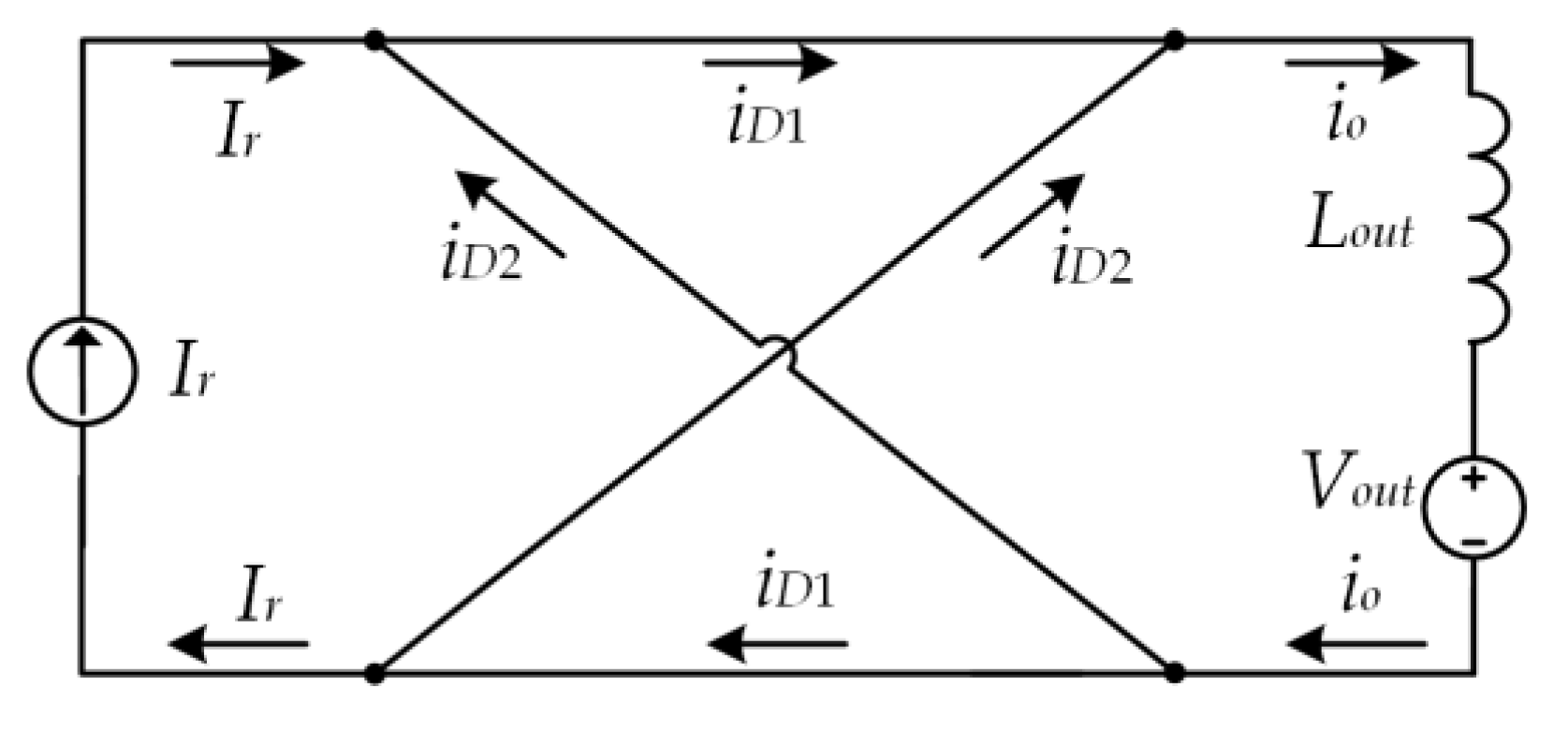

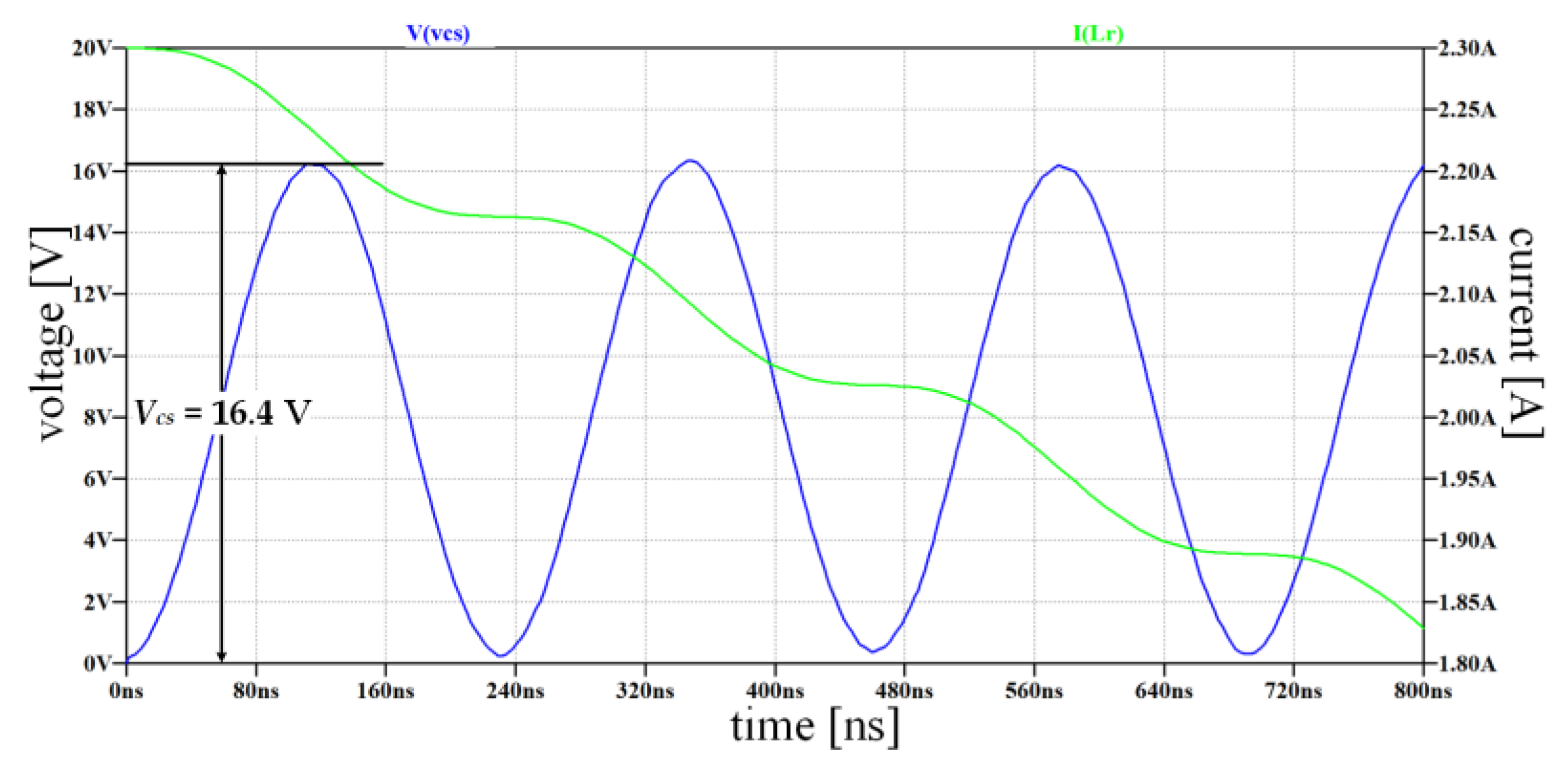

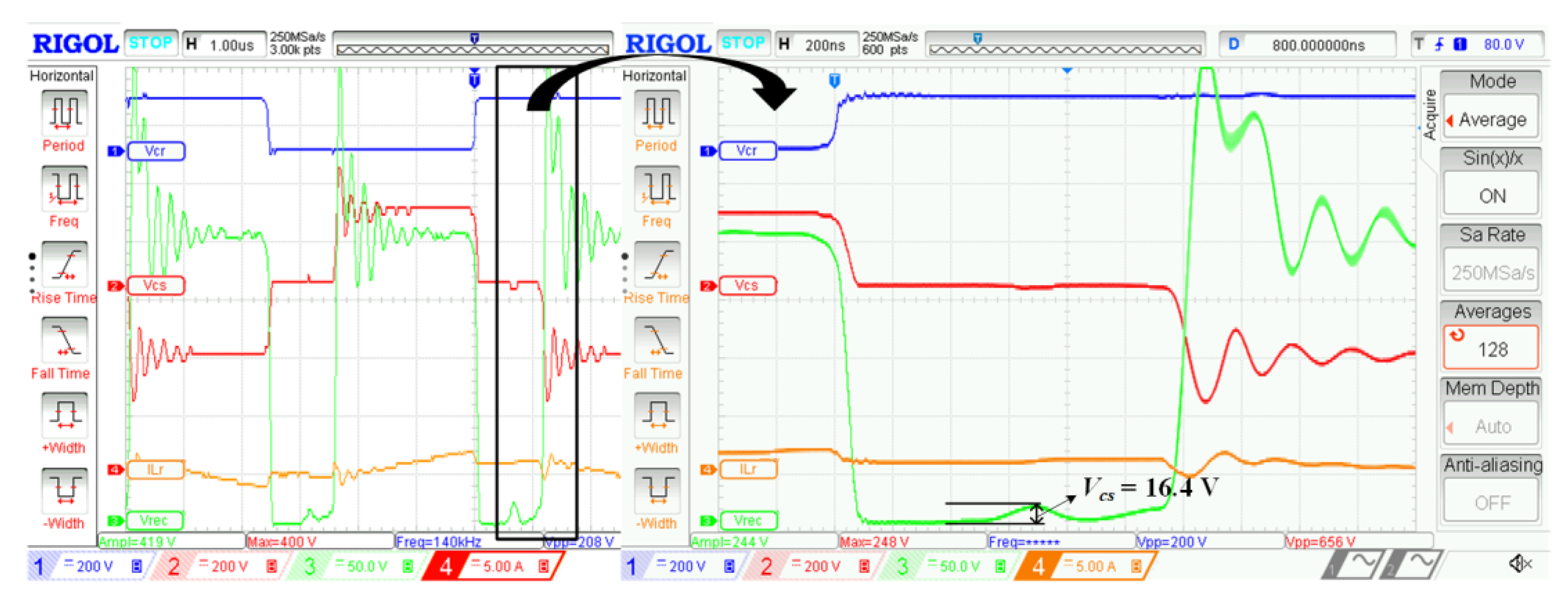

4.3. Operation during [t4-t5]

4.4. Operation during [t5-t7]

4.5. Operation during [t7-t8]

5. Conclusions

6. Discussion

Author Contributions

Funding

Conflicts of Interest

References

- Zhao, L.; Li, H.; Yu, Y.; Wang, Y. A Novel Choice Procedure of Magnetic Component Values for Phase Shifted Full Bridge Converters with a Variable Dead-Time Control Method. Energies 2015, 8, 9655–9669. [Google Scholar] [CrossRef]

- Hossain, M.Z.; Rahim, N.A. Recent progress and development on power DC-DC converter topology, control, design and applications: A review. Renew. Sustain. Energy Rev. 2018, 81, 205–230. [Google Scholar] [CrossRef]

- Aghaei, M.; Karimi, Y.; Kaboli, S. Analysis of Phase-Shifted Full-Bridge Based dc-dc Converter Considering Transformer Parasitic Elements in Discontinuous Current Mode. In Proceedings of the 5th Annual International Power Electronics, Drive Systems and Technologies Conference (PEDSTC 2014), Tehran, Iran, 5–6 February 2014. [Google Scholar]

- Tie, S.F.; Tan, C.W. A review of energy sources and energy management system in electric vehicles. Renew. Sustain. Energy Rev. 2013, 20, 82–102. [Google Scholar] [CrossRef]

- Un-Noor, F.; Padmanaban, S.; Mihet-Popa, L.; Mollah, M.N.; Hossain, E. A Comprehensive Study of Key Electric Vehicle (EV) Components, Technologies, Challenges, Impacts, and Future Direction of Development. Energies 2017, 10, 1217. [Google Scholar] [CrossRef]

- Gautam, D.S.; Musavi, F.; Edington, M.; Eberle, W.; Dunford, W.G. An Automotive On-Board 3.3 kW Battery Charger for PHEV Application. In Proceedings of the 2011 IEEE Vehicle Power and Propulsion Conference, Chicago, IL, USA, 6–9 September 2011; pp. 1–6. [Google Scholar] [CrossRef]

- Sabate, J.A.; Vlatkovic, V.; Ridley, R.B.; Lee, F.C.; Cho, B.H. Design Considerations for High-Voltage High-Power Full-Bridge Zero-Voltage-Switched PWM Converter. In Proceedings of the IEEE APEC, Los Angeles, CA, USA, 11–16 March 1990. [Google Scholar]

- Han, J.K.; Moon, G.W. Circulating Current-less Phase-Shifted Full-Bridge Converter with New Rectifier Structure. In Proceedings of the 2018 International Power Electronics Conference (IPEC-Niigata 2018-ECCE Asia), Niigata, Japan, 20–24 May 2018; pp. 4054–4058. [Google Scholar] [CrossRef]

- Lin, S.Y.; Chen, C.L. On the leading leg transition of phase-shifted ZVS-FB converters. IEEE Trans. Ind. Electron. 1998, 45, 677–679. [Google Scholar] [CrossRef]

- Kim, D.Y.; Kim, C.E.; Moon, G.W. Variable delay time method in the phase-shifted full-bridge converter for reduced power consumption under light load conditions. IEEE Trans. Power Electron. 2013, 28, 5120–5127. [Google Scholar] [CrossRef]

- Kim, J.W.; Kim, D.K.; Kim, C.E.; Moon, G.W. A simple switching control technique for improving light load efficiency in a phase-shifted full-bridge converter with a server power system. IEEE Trans. Power Electron. 2014, 29, 1562–1566. [Google Scholar] [CrossRef]

- Xu, W.; Chan, N.H.; Or, S.W.; Ho, S.L.; Chan, K.W. A New Control Method for a Bi-Directional Phase-Shift-Controlled DC-DC Converter with an Extended Load Range. Energies 2017, 10, 1532. [Google Scholar] [CrossRef]

- Lai, Y.S.; Su, Z.J.; Chang, Y.T. Novel Phase-Shift Control Technique for Full-Bridge Converter to Reduce Thermal Imbalance under Light-Load Condition. IEEE Trans. Ind. Appl. 2015, 51, 1651–1659. [Google Scholar] [CrossRef]

- Kim, J.H.; Kim, C.E.; Kim, J.K.; Lee, J.B.; Moon, G.W. Analysis on Load-Adaptive Phase-Shift Control for High Efficiency Full-Bridge LLC Resonant Converter under Light-Load Conditions. IEEE Trans. Power Electron. 2016, 31, 4942–4955. [Google Scholar]

- Chen, B.-Y.; Lai, Y. Switching control technique of phase-shift-controlled full-bridge converter to improve efficiency under light-load and standby conditions without additional auxiliary components. IEEE Trans. Power Electron. 2010, 25, 1001–1012. [Google Scholar] [CrossRef]

- Zhao, L.; Xu, C.; Zheng, X.; Li, H. A Dual Half-Bridge Converter with Adaptive Energy Storage to Achieve ZVS over Full Range of Operation Conditions. Energies 2017, 10, 444. [Google Scholar] [CrossRef]

- Pandey, R.; Tripathi, R.N.; Hanamoto, T. Comprehensive Analysis of LCL Filter Interfaced Cascaded H-Bridge Multilevel Inverter-Based DSTATCOM. Energies 2017, 10, 346. [Google Scholar] [CrossRef]

- Lai, Y.-S.; Su, Z. New Integrated Control Technique for Two-Stage Server Power to Improve Efficiency under the Light-Load Condition. IEEE Trans. Ind. Electron. 2015, 62, 6944–6954. [Google Scholar] [CrossRef]

- Wang, C.S.; Li, W.; Wang, Y.F.; Han, F.Q.; Meng, Z.; Li, G.D. An Isolated Three-Port Bidirectional DC-DC Converter with Enlarged ZVS Region for HESS Applications in DC Microgrids. Energies 2017, 10, 446. [Google Scholar] [CrossRef]

- Ruan, X. Soft-Switching PWM Full-Bridge Converters: Topologies, Control, and Design; John Wiley & Sons: Singapore, 2014; pp. 122–123. [Google Scholar]

- Kummari, N.; Chakraborty, S.; Chattopadhyay, S. An isolated high-frequency link microinverter operated with secondary-side modulation for efficiency improvement. IEEE Trans. Power Electron. 2018, 33, 2187–2200. [Google Scholar] [CrossRef]

- Escudero, M.; Kutschak, M.A.; Meneses, D.; Rodriguez, N.; Morales, D.P. A Practical Approach to the Design of a Highly Efficient PSFB DC-DC Converter for Server Applications. Energies 2019, 12, 3723. [Google Scholar] [CrossRef]

- Petreus, D.; Ciocan, I.; Patarau, T.; Etz, R.; Orban, Z. The Effect of Parasitic Capacitances on the Phase-Shift Full Bridge Converter. In Proceedings of the IECON—IEEE Industrial Electronics Society Conference, Lisbon, Portugal, 14–17 October 2019. [Google Scholar]

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Petreus, D.; Etz, R.; Patarau, T.; Ciocan, I. Comprehensive Analysis of a High-Power Density Phase-Shift Full Bridge Converter Highlighting the Effects of the Parasitic Capacitances. Energies 2020, 13, 1439. https://doi.org/10.3390/en13061439

Petreus D, Etz R, Patarau T, Ciocan I. Comprehensive Analysis of a High-Power Density Phase-Shift Full Bridge Converter Highlighting the Effects of the Parasitic Capacitances. Energies. 2020; 13(6):1439. https://doi.org/10.3390/en13061439

Chicago/Turabian StylePetreus, Dorin, Radu Etz, Toma Patarau, and Ionut Ciocan. 2020. "Comprehensive Analysis of a High-Power Density Phase-Shift Full Bridge Converter Highlighting the Effects of the Parasitic Capacitances" Energies 13, no. 6: 1439. https://doi.org/10.3390/en13061439

APA StylePetreus, D., Etz, R., Patarau, T., & Ciocan, I. (2020). Comprehensive Analysis of a High-Power Density Phase-Shift Full Bridge Converter Highlighting the Effects of the Parasitic Capacitances. Energies, 13(6), 1439. https://doi.org/10.3390/en13061439