± 180° Discontinuous PWM for Single-Phase PWM Converter of High-Speed Railway Propulsion System

Abstract

:1. Introduction

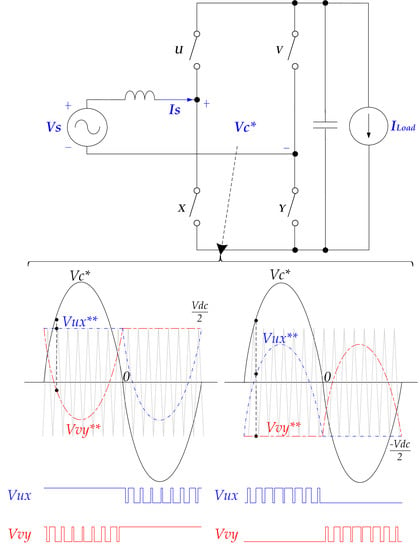

2. Conventional Carrier-Based Sinusoidal Pulse-Width Modulation (CB-SPWM) for Single-Phase PWM Converter of High-Speed Railway (HSR) Propulsion System

3. Proposed Discontinuous Pulse-Width Modulation (DPWM) for Single-Phase PWM Converter

3.1. Basic Idea for Proposed DPWM

3.2. Implementation Method I: Direct Time Calculation

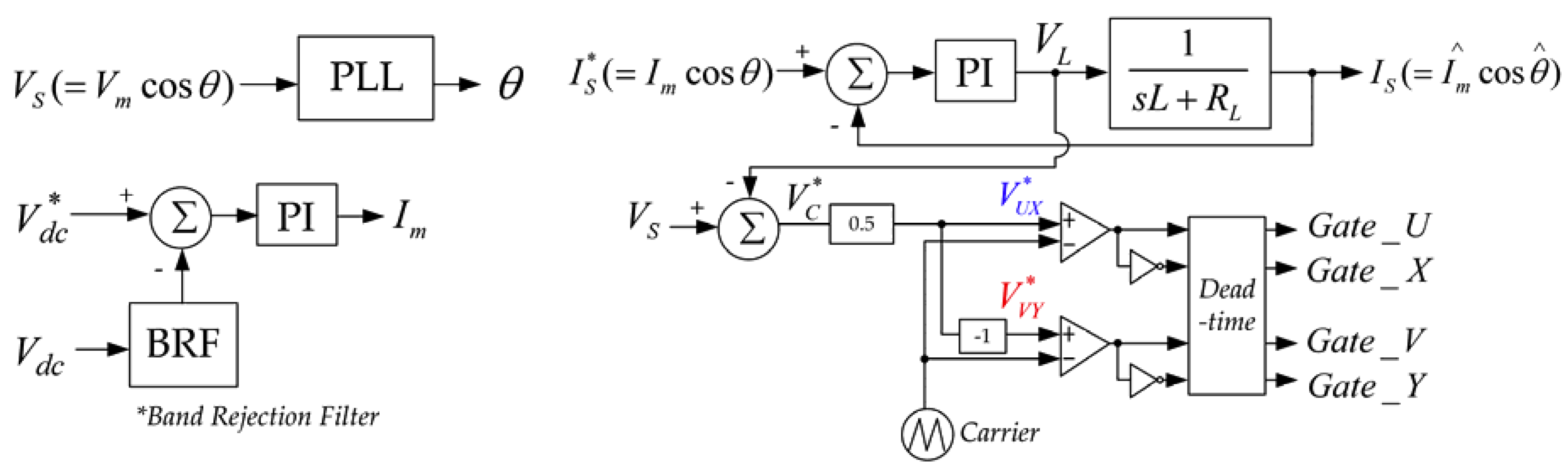

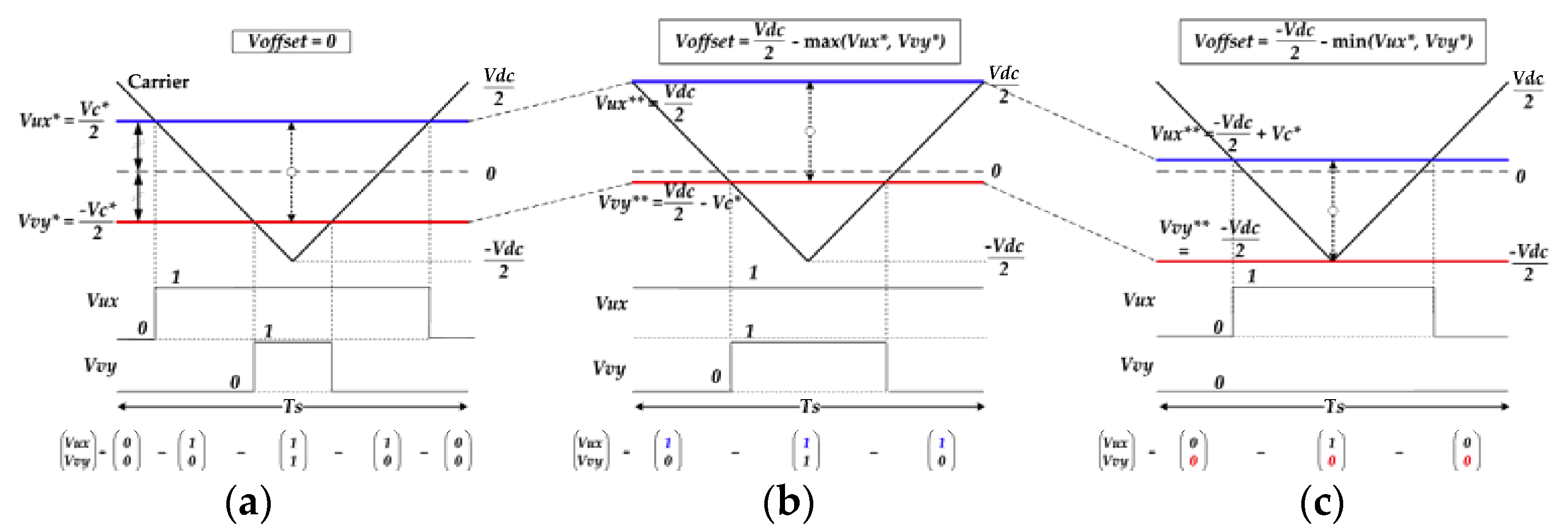

3.3. Implementation Method II: Offset Voltage Addition

3.4. Mode Analysis

3.5. Controller Design for Proposed DPWM

4. Simulation

4.1. Operation and Performance Verification

4.2. Ability to Reduce Temperature Deviations between Power Stacks

5. Experiment

6. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Ronanki, D.; Singh, S.A.; Williamson, S.S. Comprehensive Topological overview of rolling stock architectures and recent trends in electric railway traction systems. IEEE Trans. Transp. Electr. 2017, 3, 724–738. [Google Scholar] [CrossRef]

- Lin, Y. Travel costs and urban specialization patterns: Evidence from China’s high speed railway system. J. Urban Econ. 2017, 98, 98–123. [Google Scholar] [CrossRef]

- Shao, Z.-Z.; Ma, Z.-J.; Sheu, J.-B.; Gao, H.O. Evaluation of large-scale transnational high-speed railway construction priority in the belt and road region. Transp. Res. Part E Logist. Transp. Rev. 2018, 117, 40–57. [Google Scholar] [CrossRef]

- Norrga, S. A soft-switched bi-directional isolated AC/DC converter for AC-fed railway propulsion applications. In Proceedings of the 2002 International Conference on Power Electronics, Machines and Drives (Conf. Publ. No. 487), Sante Fe, NM, USA, 4–7 June 2002. [Google Scholar]

- Uno, M.; Inoue, M.; Sato, Y.; Nagata, H. Bidirectional Interleaved PWM Converter with High Voltage-Conversion Ratio and Automatic Current Balancing Capability for Single-Cell Battery Power System in Small Scientific Satellites. Energies 2018, 11, 2702. [Google Scholar] [CrossRef] [Green Version]

- Kono, Y.; Ito, K.; Okawara, H.; Fukuma, T. Power electronics technologies for railway traction systems. Hitachi Rev. 2012, 61, 306–311. [Google Scholar]

- Feloups, C.E.S.; Ali, A.I.M.; Mohamed, E.E.M. Single-phase seven-level PWM inverter for PV systems employing multi-level boost converter. In Proceedings of the International Conference on Innovative Trends in Computer Engineering (ITCE), Aswan, Egypt, 19–21 March 2018. [Google Scholar]

- Akagi, H. Multilevel converters: Fundamental circuits and systems. Proc. IEEE 2017, 105, 2048–2065. [Google Scholar] [CrossRef]

- Akagi, H. Classification, terminology, and application of the modular multilevel cascade converter (MMCC). IEEE Trans. Power Electron. 2011, 26, 3119–3130. [Google Scholar] [CrossRef]

- Choudhury, A.; Pillay, P.; Williamson, S.S. Comparative analysis between two-level and three-level DC/AC electric vehicle traction inverters using a novel DC-link voltage balancing algorithm. IEEE J. Emerg. Sel. Top. Power Electron. 2014, 2, 529–540. [Google Scholar] [CrossRef]

- Ishikawa, K.; Yukutake, S.; Kono, Y.; Ogawa, K.; Kameshiro, N. Traction inverter that applies compact 3.3 kV/1200 A SiC hybrid module. In Proceedings of the 2014 International Power Electronics Conference (IPEC-Hiroshima 2014—ECCE ASIA), Hiroshima, Japan, 18–21 May 2014. [Google Scholar]

- Zhang, H.; Tolbert, L.M.; Ozpineci, B. Impact of SiC devices on hybrid electric and plug-in hybrid electric vehicles. IEEE Trans. Ind. Appl. 2011, 47, 912–921. [Google Scholar] [CrossRef]

- Holtz, J. Pulsewidth modulation—A survey. IEEE Trans. Ind. Electron. 1992, 39, 410–420. [Google Scholar] [CrossRef]

- Ojo, O. The generalized discontinuous PWM scheme for three-phase voltage source inverter. IEEE Trans. Ind. Electron. 2004, 51, 1280–1289. [Google Scholar] [CrossRef]

- Chung, D.W.; Kim, J.S.; Sul, S.K. Unified voltage modulation technique for real-time three-phase power conversion. IEEE Trans. Ind. Appl. 1998, 34, 374–380. [Google Scholar] [CrossRef]

- Hren, A.; Mihalic, F. An improved SPWM-based control with over-modulation strategy of the third harmonic elimination for a single-phase inverter. Energies 2018, 11, 881. [Google Scholar] [CrossRef] [Green Version]

- Blasko, V. Analysis of a hybrid PWM based on modified space-vector and triangle-comparison methods. IEEE Trans. Ind. Appl. 1997, 33, 756–764. [Google Scholar] [CrossRef]

- Hava, A.; Kerkman, R.; Lipo, T. A high performance generalized discontinuous PWM algorithm. IEEE Trans. Ind. Appl. 1998, 34, 1059–1071. [Google Scholar] [CrossRef]

- Holmes, D.G.; Lipo, T. Pulse Width Modulation for Power Converter: Principles and Practice, 1st ed.; John Wiley & Sons: New York, NY, USA, 2003; pp. 186–207. [Google Scholar]

- Yang, X.-J.; Qu, H.; Tang, H.J.; Yao, C.; Zhang, N.-Y.; Blaabjerg, F. Research on discontinuous pulse width modulation algorithm for single-phase voltage source rectifier. J. Int. Conf. Electr. Mach. Syst. 2014, 3, 433–445. [Google Scholar] [CrossRef] [Green Version]

- Mohan, N.; Undeland, T.M.; Robbins, W.P. Power Electronics-Converters, Applicaitons and Design; John Wiley & Sons: New York, NY, USA, 2003; pp. 243–244. [Google Scholar]

- Teodorescu, R.; Blaabjerg, F.; Liserre, M.; Loh, P.C. Proportional-resonant controllers and filters for grid-connected voltage-source converters. IEEE Proc. Electr. Power Appl. 2006, 153, 750–762. [Google Scholar] [CrossRef] [Green Version]

- Leon, J.I.; Portillo, R.; Franquelo, L.G.; Vazquez, S.; Carrasco, J.M.; Dominguez, E. New space vector modulation techniques for single-phase multilevel converters. In Proceedings of the 2007 IEEE International Symposium on Industrial Electronics, Vigo, Spain, 4–7 June 2007. [Google Scholar]

- Song, M.-S. Single-phase PWM converter for high-speed railway propulsion system using discontinuous PWM. J. Korean Soc. Railw. 2017, 20, 448–457. [Google Scholar] [CrossRef]

- The Simulation Platform for Power Electronic Systems. Available online: https://www.plexim.com/plecs (accessed on 30 January 2020).

- Thermal Simulation. Available online: https://www.plexim.com/plecs/thermal (accessed on 30 January 2020).

- Isidori, A.; Rossi, F.M.; Blaabjerg, F.; Ma, K. Thermal loading and reliability of 10-MW multilevel wind power converter at different wind roughness classes. IEEE Trans. Ind. Appl. 2014, 50, 484–494. [Google Scholar] [CrossRef]

| Regions | ① | ② | ||

|---|---|---|---|---|

| Adjacent Vectors | Left: V1 Right: V2 | 0 Vdc | −Vdc 0 | |

| Dwelling Time | T1 T2 | (Vdc − VC*)/Vdc·TS VC*/Vdc·TS | −VC*/Vdc·TS (Vdc + VC*)/Vdc·TS | |

| PWM duration time for U PWM duration time for V (0 ~ TS) | CB-SPWM | T1/2 + T2 T1/2 | T2/2 T1 + T2/2 | |

| DPWM | Upper clamping | TS T1 | T2 TS | |

| Lower clamping | T2 0 | 0 T1 | ||

| Main Parameters | |||

|---|---|---|---|

| Input voltage, Vs | 1400 V ac(rms)/60 Hz | Output voltage, Vdc | 2800 V |

| Input inductance, L | 2 mH | DC-link capacitance, Cdc | 6.26 mF |

| Output power, Po | 1 MW | Switching frequency, fsw | 1.08 kHz |

| DPWM | CB-SPWM | |

|---|---|---|

| Psw_igbt [kW] | 6.37 | 12.88 |

| Psw_diode [kW] | 2.04 | 4.51 |

| Pcond_igbt [kW] | 0.64 | 0.68 |

| Pcond_diode [kW] | 2.15 | 2.12 |

| Total loss [kW] | 11.01 | 19.76 |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Song, M.-S.; Cho, I.-H.; Lee, J.-B. ± 180° Discontinuous PWM for Single-Phase PWM Converter of High-Speed Railway Propulsion System. Energies 2020, 13, 1550. https://doi.org/10.3390/en13071550

Song M-S, Cho I-H, Lee J-B. ± 180° Discontinuous PWM for Single-Phase PWM Converter of High-Speed Railway Propulsion System. Energies. 2020; 13(7):1550. https://doi.org/10.3390/en13071550

Chicago/Turabian StyleSong, Min-Sup, In-Ho Cho, and Jae-Bum Lee. 2020. "± 180° Discontinuous PWM for Single-Phase PWM Converter of High-Speed Railway Propulsion System" Energies 13, no. 7: 1550. https://doi.org/10.3390/en13071550