Parallel PV Configuration with Magnetic-Free Switched Capacitor Module-Level Converters for Partial Shading Conditions

Abstract

1. Introduction

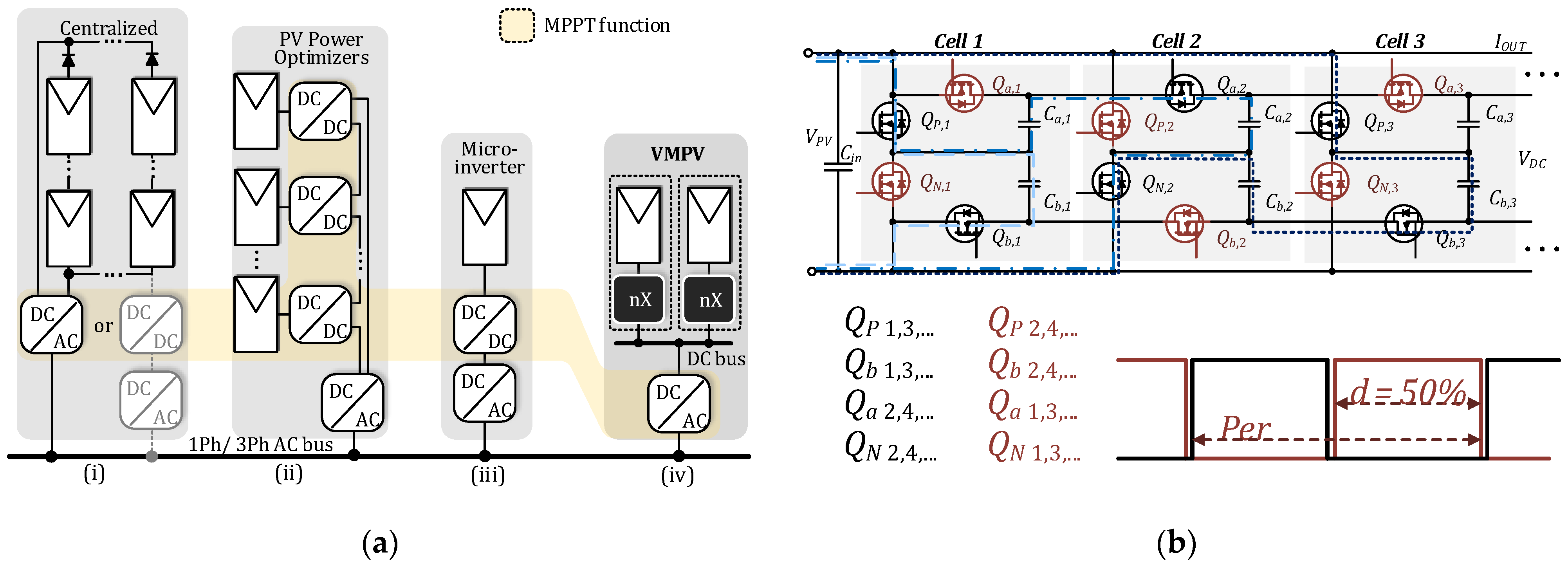

2. Proposed Module-Level PV Architecture

2.1. PV-Side Voltage Multiplier

- the input voltage source is directly connected across Cb1 (dashed blue line),

- the source is connected in series with Ca1 to charge capacitor Ca2 (dash–dot blue line), and

- the source is connected in series with Cb2 to charge capacitor Cb3 (dotted blue line).

2.2. Grid-Side Inverter

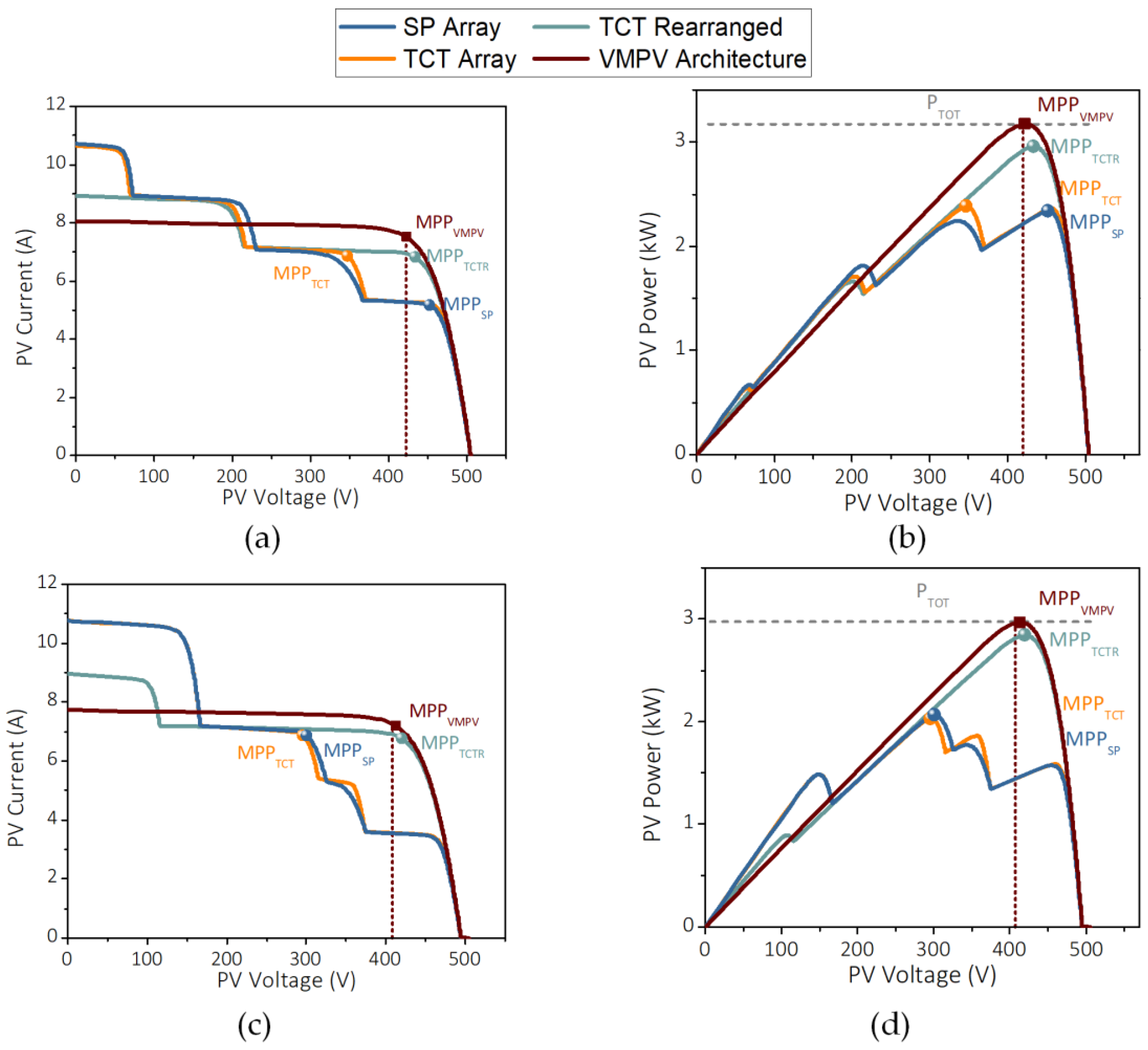

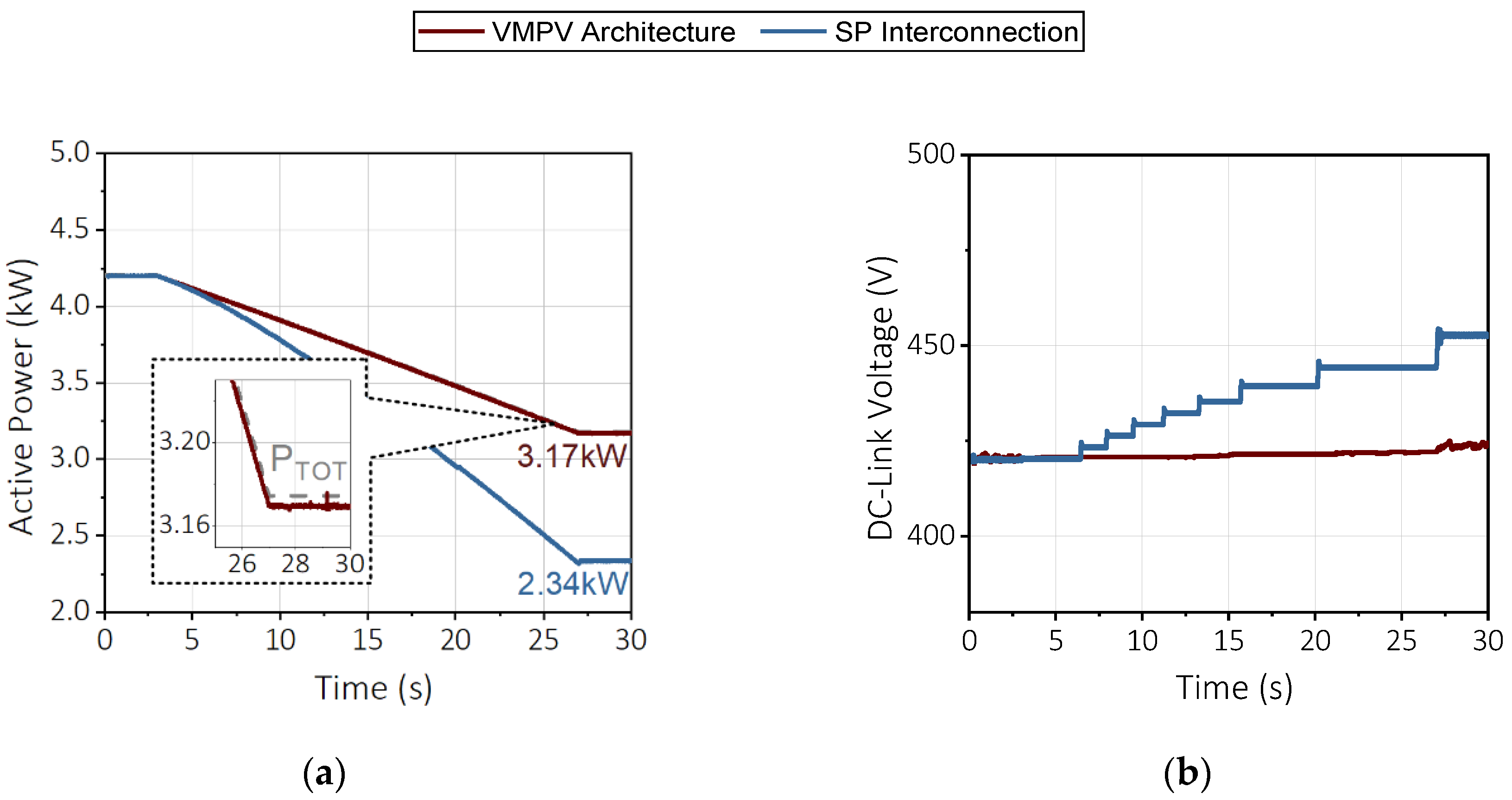

- The entire PV system always has a single MPP, even under mismatched irradiance and temperature conditions, due to the parallel connection of the VMPVs. As a result, no PV module is bypassed and the MPP is always successfully tracked, as opposed to the multi-peak P-V curves in centralized architectures, leading to almost 100% power extraction efficiency under any partial shading conditions.

- The DC-link voltage variation is limited due to the inherently small deviation of VMP with the environmental conditions. This makes it easy for the inverter to extract the maximum power while meeting the input voltage requirements, in contrast to single-stage systems under PS.

- Having a single grid-side inverter permits the implementation of sophisticated control functions, such as ancillary services to the grid (e.g., fault ride through, reactive power injection, frequency regulation), as opposed to the micro-inverters that cannot afford such complexity.

3. Modeling and Simulation

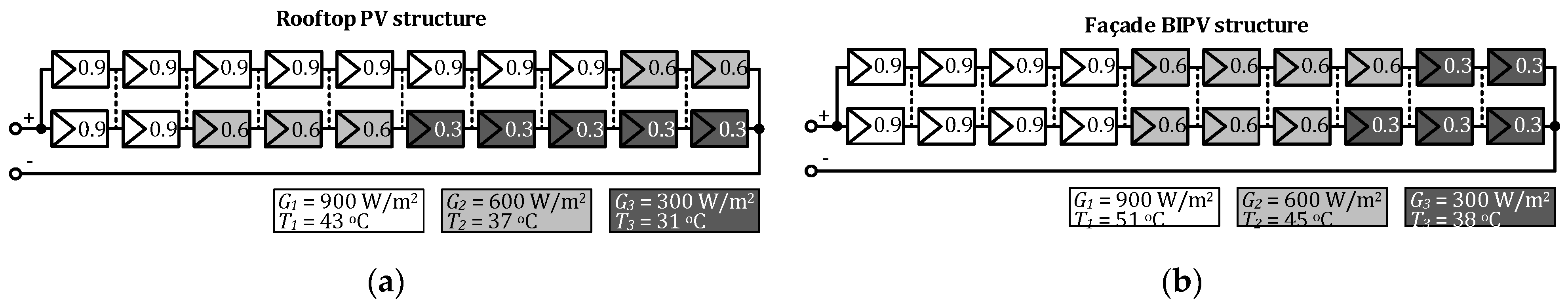

3.1. PV Generator Configuration Comparison

3.1.1. Shading Pattern A: Long–Narrow

3.1.2. Shading Pattern B: Short–Wide

3.2. Grid-Connected VMPV System

4. Experimental Validation

4.1. Experimental Setup

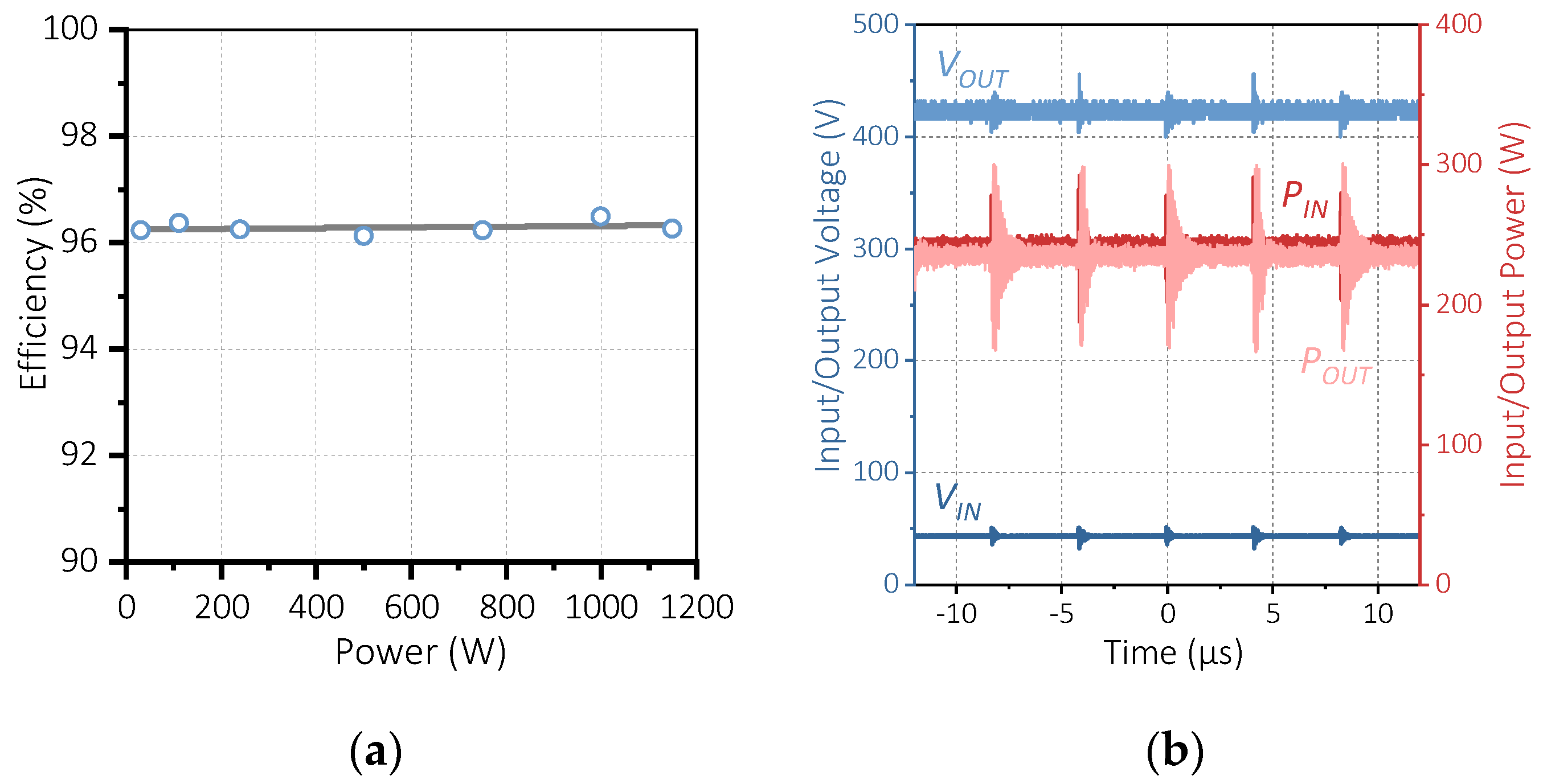

4.2. PV-Side nX Converter

4.3. Output Characteristics of the VMPV System

4.4. Real-Time MPPT of the VMPV Architecture

5. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

Abbreviations

| BIPV | Building-integrated photovoltaic |

| BL | Bridge-link interconnection scheme |

| DER | Distributed energy resources |

| ESR | Capacitor’s internal series resistance |

| GMPP | Global maximum power point |

| HC | Honey-comb interconnection scheme |

| HEMT | High electron mobility transistor |

| IC | Integrated circuit |

| LMPP | Local maximum power point |

| LPF | Low-pass filter |

| MLCC | Multi-layer ceramic capacitors |

| MLPE | Module-level power electronics |

| MPPT | Maximum power point |

| NOCT | Nominal operation cell temperature |

| P&O | Perturb and observe algorithm |

| PCB | Printed circuit board |

| PLL | Phase locked loop |

| PR | Proportional resonant controller |

| PS | Partial shading |

| PV | Photovoltaic |

| PVPO | Photovoltaic power optimizer |

| PWM | Pulse width modulation |

| SC | Switched capacitor |

| SOGI | Second order generalized integrator |

| SP | Series-parallel interconnection scheme |

| STC | Standard test conditions |

| TCT | Total-cross-tied interconnection scheme |

| TCTR | Electrically rearranged TCT array |

| VMPV | Voltage-multiplied photovoltaic system |

| ZCS | Zero current switching |

References

- Eftekharnejad, S.; Vittal, V.; Heydt, G.T.; Keel, B.; Loehr, J. Impact of Increased Penetration of Photovoltaic Generation on Power Systems. IEEE Trans. Power Syst. 2013, 28, 893–901. [Google Scholar] [CrossRef]

- Batzelis, E.I.; Georgilakis, P.S.; Papathanassiou, S.A. Energy Models for Photovoltaic Systems under Partial Shading Conditions: A Comprehensive Review. IET Renew. Power Gener. 2015, 9, 340–349. [Google Scholar] [CrossRef]

- Atmaja, T.D. Façade and Rooftop PV Installation Strategy for Building Integrated Photo Voltaic Application. Energy Procedia 2013, 32, 105–114. [Google Scholar] [CrossRef][Green Version]

- Karatepe, E.; Boztepe, M.; Çolak, M. Development of a Suitable Model for Characterizing Photovoltaic Arrays with Shaded Solar Cells. Solar Energy 2007, 81, 977–992. [Google Scholar] [CrossRef]

- Strache, S.; Wunderlich, R.; Heinen, S. A Comprehensive, Quantitative Comparison of Inverter Architectures for Various PV Systems, PV Cells, and Irradiance Profiles. IEEE Trans. Sustain. Energy 2014, 5, 813–822. [Google Scholar] [CrossRef]

- Hanson, A.J.; Deline, C.A.; MacAlpine, S.M.; Stauth, J.T.; Sullivan, C.R. Partial-Shading Assessment of Photovoltaic Installations via Module-Level Monitoring. IEEE J. Photovolt. 2014, 4, 1618–1624. [Google Scholar] [CrossRef]

- Drif, M.; Pérez, P.J.; Aguilera, J.; Aguilar, J.D. A New Estimation Method of Irradiance on a Partially Shaded PV Generator in Grid-Connected Photovoltaic Systems. Renew. Energy 2008, 33, 2048–2056. [Google Scholar] [CrossRef]

- Li, H.; Yang, D.; Su, W.; Lu, J.; Yu, X. An Overall Distribution Particle Swarm Optimization MPPT Algorithm for Photovoltaic System Under Partial Shading. IEEE Trans. Ind. Electron. 2019, 66, 265–275. [Google Scholar] [CrossRef]

- Sundareswaran, K.; Sankar, P.; Nayak, P.S.R.; Simon, S.P.; Palani, S. Enhanced Energy Output From a PV System Under Partial Shaded Conditions Through Artificial Bee Colony. IEEE Trans. Sustain. Energy 2015, 6, 198–209. [Google Scholar] [CrossRef]

- Batzelis, E.I.; Kampitsis, G.E.; Papathanassiou, S.A.; Manias, S.N. Direct MPP Calculation in Terms of the Single-Diode PV Model Parameters. IEEE Trans. Energy Convers. 2015, 30, 226–236. [Google Scholar] [CrossRef]

- Moballegh, S.; Jiang, J. Modeling, Prediction, and Experimental Validations of Power Peaks of PV Arrays Under Partial Shading Conditions. IEEE Trans. Sustain. Energy 2014, 5, 293–300. [Google Scholar] [CrossRef]

- Jeyaprabha, S.B.; Selvakumar, A.I. Model-Based MPPT for Shaded and Mismatched Modules of Photovoltaic Farm. IEEE Trans. Sustain. Energy 2017, 8, 1763–1771. [Google Scholar] [CrossRef]

- Shams El-Dein, M.Z.; Kazerani, M.; Salama, M.M.A. An Optimal Total Cross Tied Interconnection for Reducing Mismatch Losses in Photovoltaic Arrays. IEEE Trans. Sustain. Energy 2013, 4, 99–107. [Google Scholar] [CrossRef]

- Babu, T.S.; Ram, J.P.; Dragicevic, T.; Miyatake, M.; Blaabjerg, F.; Rajasekar, N. Particle Swarm Optimization Based Solar PV Array Reconfiguration of the Maximum Power Extraction Under Partial Shading Conditions. IEEE Trans. Sustain. Energy 2018, 9, 74–85. [Google Scholar] [CrossRef]

- Shams El-Dein, M.Z.; Kazerani, M.; Salama, M.M.A. Optimal Photovoltaic Array Reconfiguration to Reduce Partial Shading Losses. IEEE Trans. Sustain. Energy 2013, 4, 145–153. [Google Scholar] [CrossRef]

- Kjaer, S.B.; Pedersen, J.K.; Blaabjerg, F. A Review of Single-Phase Grid-Connected Inverters for Photovoltaic Modules. IEEE Trans. Ind. Appl. 2005, 41, 1292–1306. [Google Scholar] [CrossRef]

- Meneses, D.; Blaabjerg, F.; García, Ó.; Cobos, J.A. Review and Comparison of Step-Up Transformerless Topologies for Photovoltaic AC-Module Application. IEEE Trans. Power Electron. 2013, 28, 2649–2663. [Google Scholar] [CrossRef]

- Batzelis, E.I.; Kampitsis, G.E.; Papathanassiou, S.A. Power Reserves Control for PV Systems With Real-Time MPP Estimation via Curve Fitting. IEEE Trans. Sustain. Energy 2017, 8, 1269–1280. [Google Scholar] [CrossRef]

- Chen, S.-M.; Liang, T.-J.; Hu, K.-R. Design, Analysis, and Implementation of Solar Power Optimizer for DC Distribution System. IEEE Trans. Power Electron. 2013, 28, 1764–1772. [Google Scholar] [CrossRef]

- Vinnikov, D.; Chub, A.; Liivik, E.; Kosenko, R.; Korkh, O. Solar Optiverter—A Novel Hybrid Approach to the Photovoltaic Module Level Power Electronics. IEEE Trans. Ind. Electron. 2019, 66, 3869–3880. [Google Scholar] [CrossRef]

- Stauth, J.T.; Seeman, M.D.; Kesarwani, K. Resonant Switched-Capacitor Converters for Sub-Module Distributed Photovoltaic Power Management. IEEE Trans. Power Electron. 2013, 28, 1189–1198. [Google Scholar] [CrossRef]

- Tahmasbi-Fard, M.; Tarafdar-Hagh, M.; Pourpayam, S.; Haghrah, A.-A. A Voltage Equalizer Circuit to Reduce Partial Shading Effect in Photovoltaic String. IEEE J. Photovolt. 2018, 8, 1102–1109. [Google Scholar] [CrossRef]

- Li, W.; He, X. Review of Nonisolated High-Step-Up DC/DC Converters in Photovoltaic Grid-Connected Applications. IEEE Trans. Ind. Electron. 2011, 58, 1239–1250. [Google Scholar] [CrossRef]

- Gao, L.; Dougal, R.A.; Liu, S.; Iotova, A.P. Parallel-Connected Solar PV System to Address Partial and Rapidly Fluctuating Shadow Conditions. IEEE Trans. Ind. Electron. 2009, 56, 1548–1556. [Google Scholar] [CrossRef]

- Tseng, K.-C.; Huang, C.-C.; Shih, W.-Y. A High Step-Up Converter With a Voltage Multiplier Module for a Photovoltaic System. IEEE Trans. Power Electron. 2013, 28, 3047–3057. [Google Scholar] [CrossRef]

- Ahmed, M.E.; Mousa, M.; Orabi, M. Development of High Gain and Efficiency Photovoltaic System Using Multilevel Boost Converter Topology. In Proceedings of the IEEE 2nd International Symposium on Power Electronics for Distributed Generation Systems (PEDG), Hefei, China, 16–18 June 2010; pp. 898–903. [Google Scholar]

- Molavi, N.; Farzanehfard, H.; Adib, E. Soft-Switched Non-Isolated High Step-up DC–DC Converter with Reduced Voltage Stress. IET Power Electron. 2016, 9, 1711–1718. [Google Scholar] [CrossRef]

- Revathi, B.S.; Prabhakar, M. High Gain High Power DC-DC Converter for Photovoltaic Application. In Proceedings of the 2013 Annual International Conference on Emerging Research Areas and 2013 International Conference on Microelectronics, Communications and Renewable Energy, Kanjirapally, India, 4–6 June 2013; pp. 1–6. [Google Scholar]

- Gu, B.; Dominic, J.; Lai, J.-S.; Zhao, Z.; Liu, C. High Boost Ratio Hybrid Transformer DC–DC Converter for Photovoltaic Module Applications. IEEE Trans. Power Electron. 2013, 28, 2048–2058. [Google Scholar] [CrossRef]

- Nanakos, A.C.; Christidis, G.C.; Tatakis, E.C. Weighted Efficiency Optimization of Flyback Microinverter Under Improved Boundary Conduction Mode (i-BCM). IEEE Trans. Power Electron. 2015, 30, 5548–5564. [Google Scholar] [CrossRef]

- Qian, W.; Cao, D.; Cintron-Rivera, J.G.; Gebben, M.; Wey, D.; Peng, F.Z. A Switched-Capacitor DC–DC Converter With High Voltage Gain and Reduced Component Rating and Count. IEEE Trans. Ind. Appl. 2012, 48, 1397–1406. [Google Scholar] [CrossRef]

- Kampitsis, G.; Chevron, M.; van Erp, R.; Perera, N.; Papathanassiou, S.; Matioli, E. Mixed Simulation-Experimental Optimization of a Modular Multilevel Switched Capacitors Converter Cell. In Proceedings of the 2020 IEEE 21st Workshop on Control and Modeling for Power Electronics (COMPEL), Aalborg, Denmark, 9 November 2020; pp. 1–6. [Google Scholar]

- Cao, D.; Peng, F.Z. A Family of Zero Current Switching Switched-Capacitor Dc-Dc Converters. In Proceedings of the Twenty-Fifth Annual IEEE Applied Power Electronics Conference and Exposition (APEC), Palm Springs, CA, USA, 21–25 February 2010; pp. 1365–1372. [Google Scholar]

- Uemoto, Y.; Morita, T.; Ikoshi, A.; Umeda, H.; Matsuo, H.; Shimizu, J.; Hikita, M.; Yanagihara, M.; Ueda, T.; Tanaka, T.; et al. GaN Monolithic Inverter IC Using Normally-off Gate Injection Transistors with Planar Isolation on Si Substrate. In Proceedings of the 2009 IEEE International Electron Devices Meeting (IEDM), Baltimore, MD, USA, 7–9 December 2009; pp. 1–4. [Google Scholar]

- Kampitsis, G.; van Erp, R.; Matioli, E. Ultra-High Power Density Magnetic-Less DC/DC Converter Utilizing GaN Transistors. In Proceedings of the 2019 IEEE Applied Power Electronics Conference and Exposition (APEC), Anaheim, CA, USA, 17–21 March 2019; pp. 1609–1615. [Google Scholar]

- Zhang, Z.; Xiao, T.; Shen, Y.; Wang, L.; Jia, P.; Yu, J. A Method to Test Operating Cell Temperature for BIPV Modules. IEEE J. Photovolt. 2016, 6, 272–277. [Google Scholar] [CrossRef]

- Kampitsis, G.; Batzelis, E.; Papathanassiou, S. Power Balance Control for a Two-Stage Solar Inverter with Low Voltage Ride through Capability. Eur. Photovolt. Solar Energy Conf. Exhib. 2016, 32, 1646–1650. [Google Scholar] [CrossRef]

| Component | Parameter | Value |

|---|---|---|

| PV modules | Part Type | VBHN245SJ25 |

| VMP | 44.3 V | |

| IMP | 5.53 A | |

| VOC | 53 V | |

| ISC | 5.86 A | |

| Module-level nX converter | Transistors in QP/N position | GS61008T |

| Transistors in Qa/b position | GS66508T | |

| Switching capacitors | 4 × 2.2 μF, X6S | |

| Gate driver | LM5114 | |

| Digital/Power isolator | ISOW7842F | |

| 2nd-stage DC-DC converter | Series diodes | S10KC |

| LDC-DC | 1.5 mH | |

| CDC-DC | 50 μF | |

| Transistor | IPB65R190CFD | |

| Switching diode | C3D08065E | |

| Micro-controller | TMS320F28379D | |

| Switching frequency (FSW-B) | 20 kHz | |

| MPPT period (TMPPT) | 250 ms | |

| Voltage/Current sampling rate | 4 k samples/s | |

| LPF cutoff frequency (F0) | 100 Hz | |

| Output Resistor | Rout | 0–240 Ω |

| Test Conditions | PV Module/PV System | VPV (V) | IPV (A) | PPV (W) | Extraction eff. (%) |

|---|---|---|---|---|---|

| Pattern A: Uniform Conditions | Module 1 (MPP1) | 41.25 | 4.705 | 194.1 | - |

| Module 2 (MPP2) | 40.08 | 4.757 | 190.7 | - | |

| VMPV Architecture (MPPVMPV) | 40.52 | 9.475 | 384.4 | 99.9 | |

| Module 1 (@MPPVMPV) | 40.52 | 4.785 | 193.9 | 99.9 | |

| Module 2 (@MPPVMPV) | 40.52 | 4.702 | 190.5 | 99.9 | |

| Pattern B: PS Conditions | Module 1 (MPP1) | 42.5 | 1.145 | 48.7 | - |

| Module 2 (MPP2) | 41.05 | 4.26 | 174.9 | - | |

| VMPV Architecture (MPPVMPV) | 41.6 | 5.36 | 223 | 99.74 | |

| Module 1 (@MPPVMPV) | 41.6 | 1.161 | 48.3 | 99.18 | |

| Module 2 (@MPPVMPV) | 41.6 | 4.20 | 174.7 | 99.89 | |

| Series Connection (GMPPS) | 39.65 | 4.38 | 174 | 77.8 | |

| Series Connection (LMPPS) | 91.3 | 1.255 | 113 | 50.5 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Kampitsis, G.; Batzelis, E.; van Erp, R.; Matioli, E. Parallel PV Configuration with Magnetic-Free Switched Capacitor Module-Level Converters for Partial Shading Conditions. Energies 2021, 14, 456. https://doi.org/10.3390/en14020456

Kampitsis G, Batzelis E, van Erp R, Matioli E. Parallel PV Configuration with Magnetic-Free Switched Capacitor Module-Level Converters for Partial Shading Conditions. Energies. 2021; 14(2):456. https://doi.org/10.3390/en14020456

Chicago/Turabian StyleKampitsis, Georgios, Efstratios Batzelis, Remco van Erp, and Elison Matioli. 2021. "Parallel PV Configuration with Magnetic-Free Switched Capacitor Module-Level Converters for Partial Shading Conditions" Energies 14, no. 2: 456. https://doi.org/10.3390/en14020456

APA StyleKampitsis, G., Batzelis, E., van Erp, R., & Matioli, E. (2021). Parallel PV Configuration with Magnetic-Free Switched Capacitor Module-Level Converters for Partial Shading Conditions. Energies, 14(2), 456. https://doi.org/10.3390/en14020456