Variable Speed Drive DC-Bus Voltage Dip Proofing

Abstract

1. Introduction

2. Variable Speed Drive under Short-Term Power Interruption (STPI)

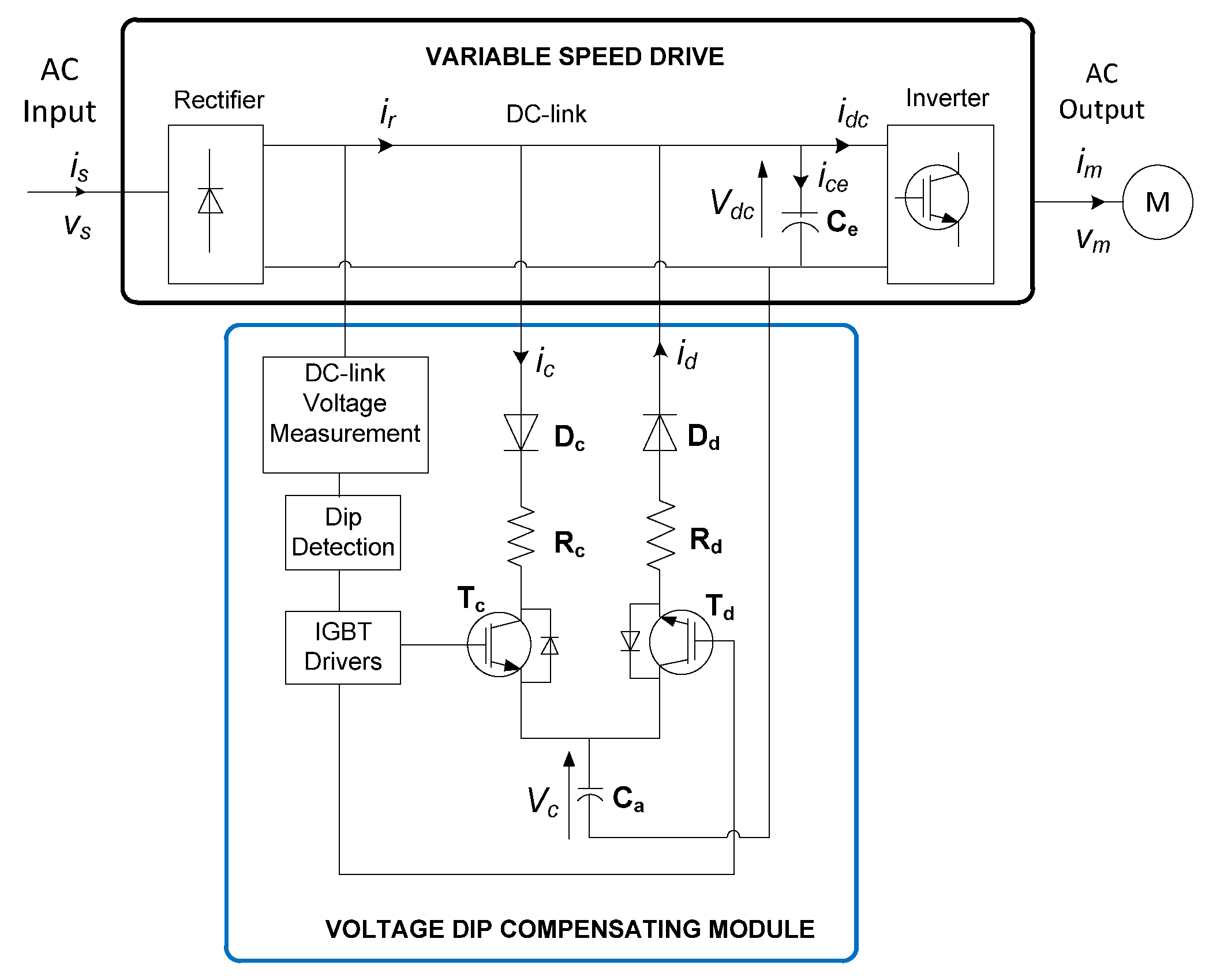

3. Proposed DC-Link Voltage Dip Compensation

3.1. DC-Link during Compensation

3.2. DC-Link during Charging

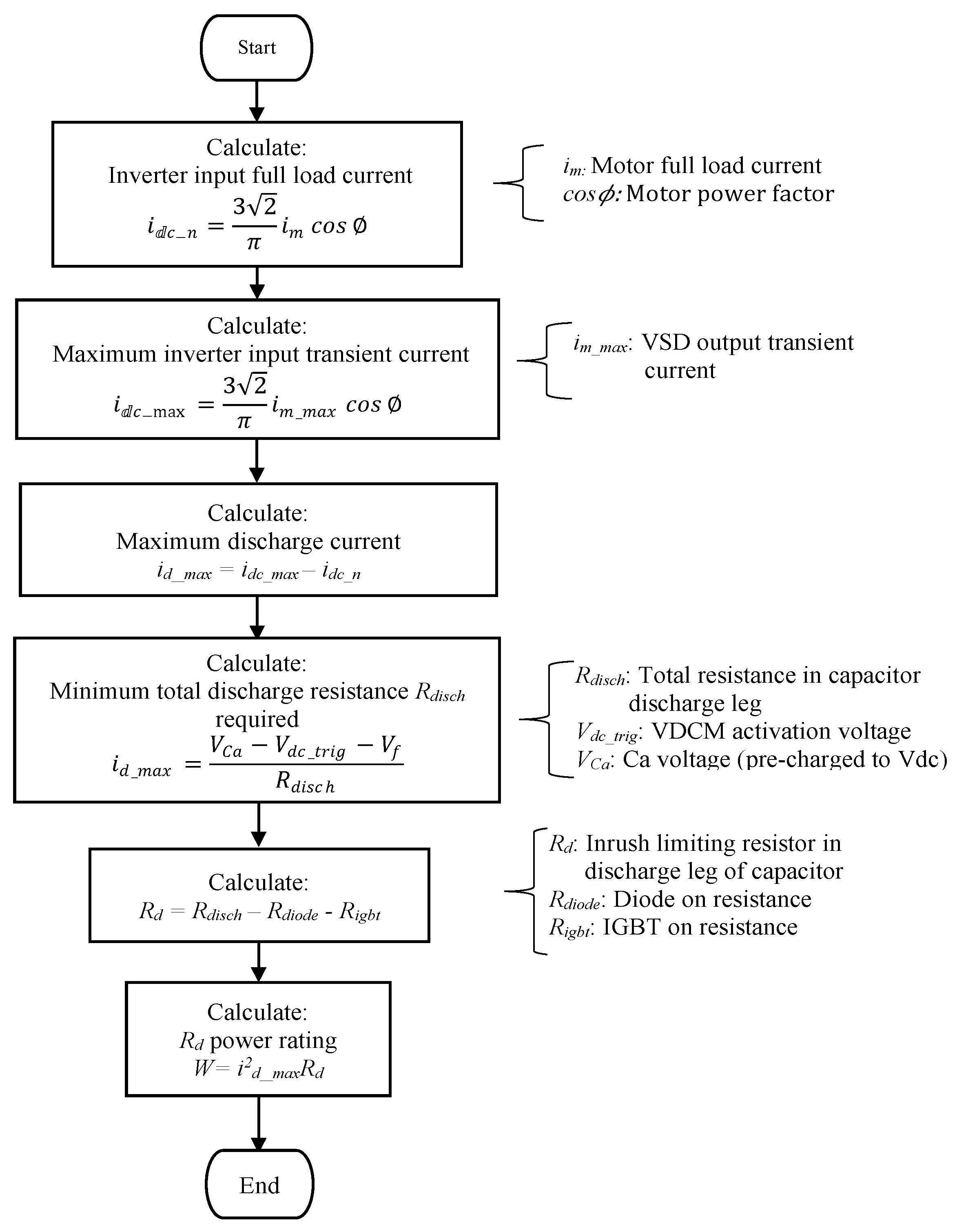

4. Sizing Methodology: Voltage Dip Compensating Module

5. Simulation Results and Analysis

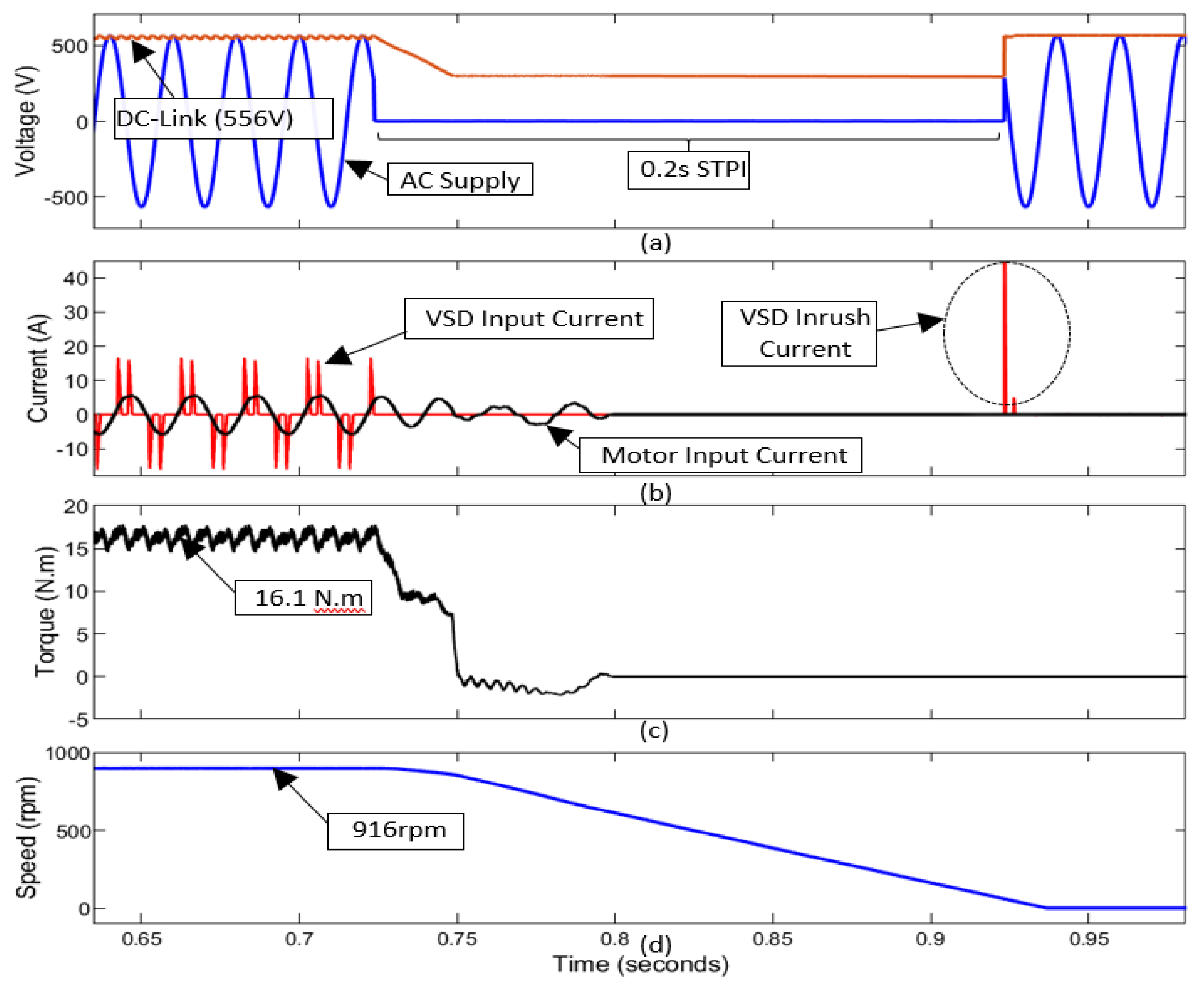

5.1. Simulation Results without DC-Link Voltage Compensation

5.2. Simulation Results with DC-Link Voltage Compensation

6. Experimental Set-Up and Results

6.1. Experimental Test Conditions

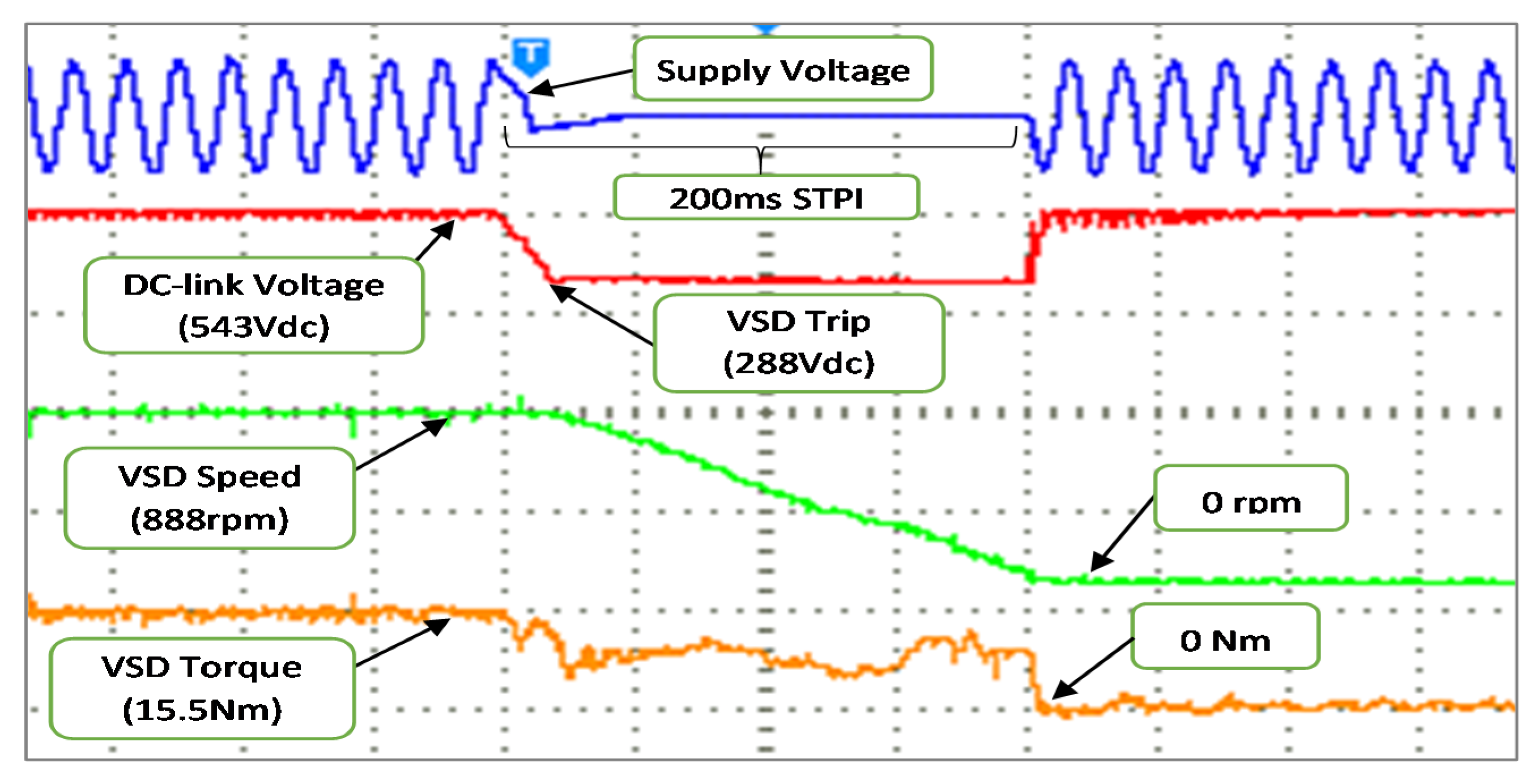

6.2. Results without “DC-Link Voltage” Compensation

6.3. With “DC-Link Voltage” Compensation

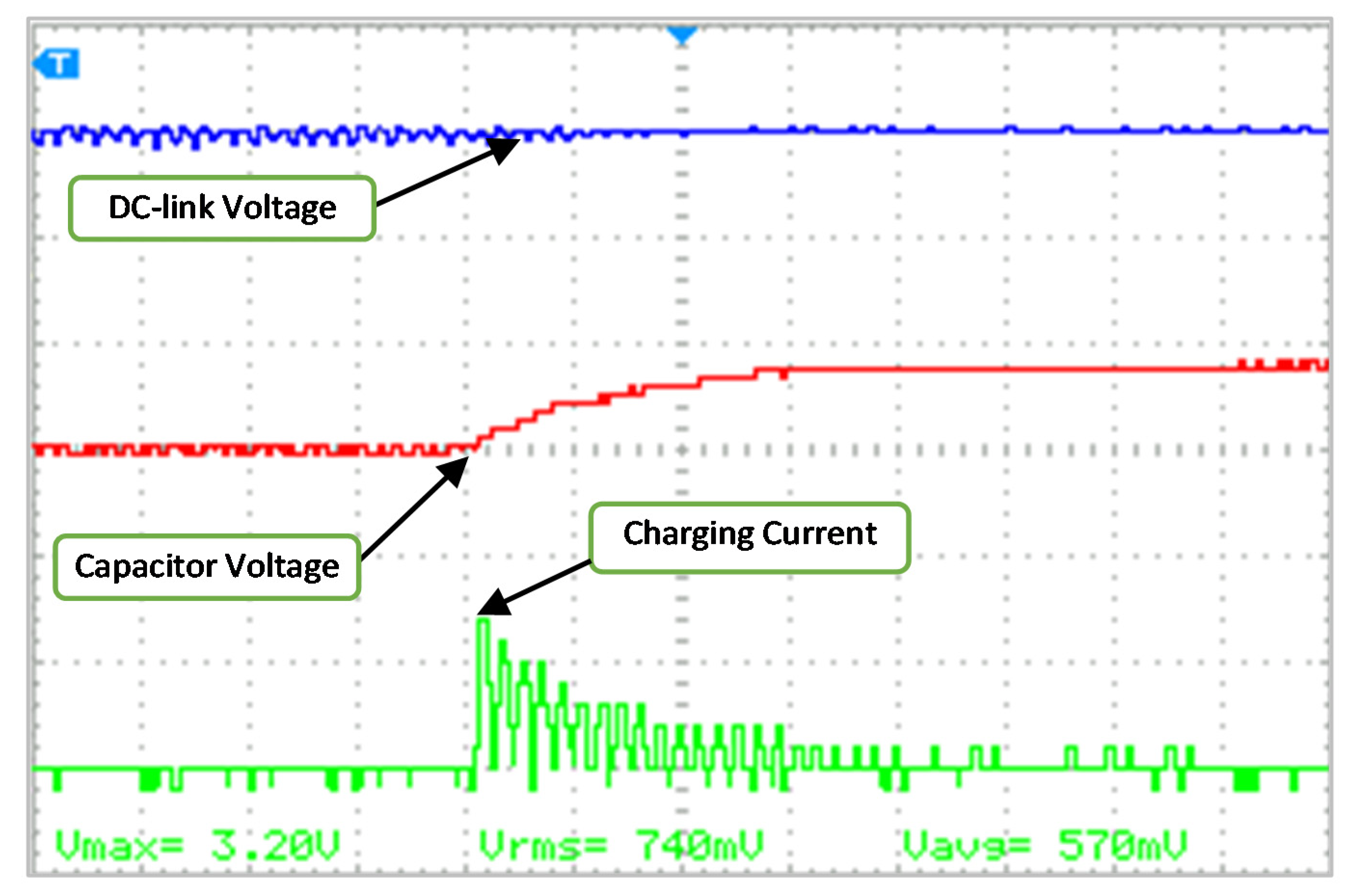

6.4. Compensation of Capacitor Charging from DC-Link

7. Analysis of Results

8. Conclusions

- A switched capacitor can be used to improve voltage ride through for a dc bus voltage;

- There was a torque pulsation of 12.8 and 14.3% at the start and end of dc-link voltage compensation respectively;

- During voltage dip ride through (compensation) there was a 2.5% drop in the speed and 10.3% drop in the motor torque;

- A sizing methodology for the additional capacitor and discharge limiting resistor has been tested and validated. This methodology uses readily available motor and VSD nameplate information;

- The voltage ride through module was able to retain up to 82% of the dc bus voltage during 0.2 s STPI which avoided a trip on the VSD;

- There was good agreement between simulations and experimental results and, when comparing the two, there was a 2.4% voltage difference on the dc link voltage drop and 2% difference on the switched capacitor voltage drop during compensation. There was a 2.4% difference between simulations and experimental work on the amount of the discharge current;

- The proposed method whilst effective in improving ride-through capability of VSD resulted in an unwanted voltage drop and energy losses due to the inrush current limiting resistor, which led to reduced overall module efficiency;

- The observed behaviour of the VSD was based on a STPI which presents the worst-case scenario. Improved behaviour is expected for less severe voltage dips;

- The voltage compensation module can be added to existing VSDs that are based on V/f control in order to avoid operational breakdowns.

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

Nomenclature/Abbreviations

| EL | Total load energy (Wh) |

| EC | Energy supplied by capacitor (Wh) |

| Ekin | Kinetic energy in the rotating mass (Wh) |

| TL | Load torque (N.m) |

| ω | Speed of rotating assembly (rad/s) |

| Jl | Inertia (kg·m2) |

| Vc | Capacitor voltage (V) |

| Ca | Switched capacitor (F) |

| Ce | Invereter dc bus capacitance (F) |

| Vdc | dc bus voltage (V) |

| Idc | dc link current (A) |

| IS | Variable speed drive supply current (A) |

| Vs | Variable speed drive supply voltage (V) |

| Rca | Internal resistance of the switched capacitor (Ω) |

| RTd | The switch internal resistance (Ω) |

| RDd | The resistance of the diode during conduction (Ω) |

| Rd | The discharge current limtting resistor (Ω) |

| Rce | The internal resistance of the VSD capacitor (Ω) |

| Pinv | The VSD inverter input power (W) |

| VCa | Initial capacitor voltage |

| VCa_min | Capacitor voltage at end of compensation |

| id_max | The initial inrush current (A) |

| ic | Inrush charging current (A) |

| Rd, Rc | Inrush current limiting resistors (Ω) |

| Rdisch | Total resistance in discharge led (Ω) |

| Idc_n | Norminal dc bust current under full load condition (A) |

| im | Motor full load current (A) |

| Im_max | VSD peack out transient current (A) |

| Pm | Motor shaft power (W) |

| Δt | Required ride through duration (s) |

| Cu | Standard capcitance value (F) |

| Vcu | Standard voltage (V) |

| ESR | Equivalent serries resistance (V) |

| Vf | Diode forward voltage (V) |

| Vac_min | Capacitor voltage after compensation (V) |

| Rcharg | Resistance during charging (Ω) |

| STPI | Short term power interuption |

| PWM | Pulse width modulation |

| VSD | Variable speed drive |

| VDCM | Voltage dischage compensation module |

Appendix A

| Motor Rating | 1.5 kW, 400 V, 50 Hz, 3.84 A, 920 rpm, Cos ϕ: 0.75, η: 75.2% |

| Stator resistance | 4.38 Ω |

| Stator leakage inductance | 17.1 mH |

| Rotor resistance | 4.11 Ω |

| Rotor leakage inductance | 16.5 mH |

| Magnetizing inductance | 476 mH |

| Rotor inertia | 0.0014 kg·m2 |

| Input Rating | 380–500 V, 50 Hz, 6.4 A, Inrush: 10 A, Power loss: 61 W |

| Output Rating | 380–500 V, 0.5–500 Hz, 4.1 A, Transient 6.2 A for 60 s |

| Rectifier | 3-arm Diode Bridge |

| Inverter | 3-arm IGBT/Diode Bridge |

| Inverter Control | V/f, 2-level PWM |

| Switching Frequency | 4 kHz |

| Modulation Index | 0.9 |

| Sample Time | 10 µs |

| DC-link Capacitor | 250 µF |

| Power | 7.5 kW |

| Efficiency | 89.3% |

| Power Factor | 0.81 |

| Pole Pairs | 2 |

| Rotor Speed | 1450 rpm |

References

- Majodina, M.; Botai, J.O.; Rautenbach, H. The vulnerability of the South African electricity transmission network infrastructure to weather and climate: A review. J. Energy South. Afr. 2018, 29, 51–59. [Google Scholar] [CrossRef]

- Pillot, B.; Muselli, M.; Poggi, P.; Dias, J.B. Historical trends in global energy policy and renewable power system issues in Sub-Saharan Africa: The case of solar PV. Energy Policy 2019, 127, 113–124. [Google Scholar] [CrossRef]

- Minnaar, U.J.; Gaunt, C.T.; Nicolls, F. Characterisation of power system events on South African transmission power lines. Electr. Power Syst. Res. 2012, 88, 25–32. [Google Scholar] [CrossRef]

- Buraimoh, E.; Davidson, I.E.; Martinez-Rodrigo, F. Fault Ride-Through Enhancement of Grid Supporting Inverter-Based Microgrid Using Delayed Signal Cancellation Algorithm Secondary Control. Energies 2019, 12, 3994. [Google Scholar] [CrossRef]

- B Magoro The South African Grid Code-The Network Code-Version 9. Eskom Transmission Division, July 2014. Available online: http://www.nersa.org.za (accessed on 1 March 2021).

- Hansen, A.D.; Das, K.; Sørensen, P.; Singh, P.; Gavrilovic, A. European and Indian Grid Codes for Utility Scale Hybrid Power Plants. Energies 2021, 14, 4335. [Google Scholar] [CrossRef]

- Duran-Gomez, J.L.; Enjeti, P.N.; von Jouanne, A. An approach to achieve ride-through of an adjustable-speed drive with flyback converter modules powered by super capacitors. IEEE Trans. Ind. Appl. 2002, 38, 514–522. [Google Scholar] [CrossRef]

- Bollen, M.H.J.; Zhang, L.D. Analysis of voltage tolerance of AC adjustable-speed drives for three-phase balanced and unbalanced sags. IEEE Trans. Ind. Appl. 2000, 36, 904–910. [Google Scholar] [CrossRef]

- Zyl, A.V.; Spee, R.; Faveluke, A.; Bhowmik, S. Voltage sag ride-through for adjustable-speed drives with active rectifiers. IEEE Trans. Ind. Appl. 1998, 34, 1270–1277. [Google Scholar]

- Narayanan, R.; Platt, D.; Perera, S. Improvements to Voltage Sag-Ride Through Perfomance of AC Variable Speed Drives. Int. J. Eng. Sci. Technol. 2010, 2, 7. [Google Scholar]

- Enjeti, P.N. Method and System for Ride Through of an Adjustable Speed Drive for Voltage Sags and Short Term Power Interruption. U.S. Patent 6,005,362, 21 December 1999. [Google Scholar]

- Pires, V.F.; Monteiro, J.; Silva, J.F. Dual 3-Phase Bridge Multilevel Inverters for AC Drives with Voltage Sag Ride-through Capability. Energies 2019, 12, 2324. [Google Scholar] [CrossRef]

- Afridi, K.K.; Chen, M.; Perreault, D.J. Enhanced Bipolar Stacked Switched Capacitor Energy Buffers. IEEE Trans. Ind. Appl. 2014, 50, 1141–1149. [Google Scholar] [CrossRef]

- von Jouanne, A.; Enjeti, P.N.; Banerjee, B. Assessment of ride-through alternatives for adjustable-speed drives. IEEE Trans. Ind. Appl. 1999, 35, 908–916. [Google Scholar] [CrossRef]

- Stockman, K.; D’hulster, F.; Verhaege, K.; Didden, M.; Belmans, R. Ride-through of adjustable speed drives during voltage dips. Electr. Power Syst. Res. 2003, 66, 49–58. [Google Scholar] [CrossRef]

- Klumpner, C.; Blaabjerg, F. Experimental evaluation of ride-through capabilities for a matrix converter under short power interruptions. IEEE Trans. Ind. Electron. 2002, 49, 315–324. [Google Scholar] [CrossRef]

- Deswal, S.S.; Dahiya, R.; Jain, D.K. Enhance Ride-Through Capability of Adjustable Speed Drives by Maintaining DC-Link voltage. Int. J. Comput. Electr. Eng. 2009, 1, 142–148. [Google Scholar] [CrossRef]

- Carnovale, D.J.; Biternas, J.; Dionise, T.J.; Shipp, D.D. Design, Development and Testing of a Voltage Ride-Thru Solution for Variable Speed Drives in Oil Field Applications. In Proceedings of the 2007 IEEE Petroleum and Chemical Industry Technical Conference, Calgary, AB, Canada, 17–19 September 2007; pp. 1–7. [Google Scholar]

- Kavitha, V.; Subramanian, K. Review on DC link capacitor issues in variable frequency drives. In Proceedings of the 2017 International Conference on Innovations in Electrical, Electronics, Instrumentation and Media Technology (ICEEIMT), Coimbatore, India, 3–4 February 2017; pp. 216–218. [Google Scholar]

- Kim, U.-J.; Oh, S.-G. New Sub-Module with Reverse Blocking IGBT for DC Fault Ride-Through in MMC-HVDC System. Energies 2021, 14, 1551. [Google Scholar] [CrossRef]

- Wymann, T.; Jorg, P. Power loss ride-through in a variable speed drive system. In Proceedings of the 2014 Petroleum and Chemical Industry Conference Europe, Valparaíso, Chile, 22–26 March 2021; pp. 1–9. [Google Scholar]

- Undeland, T.M.; Mohan, N. Overmodulation and loss considerations in high-frequency modulated transistorized induction motor drives. IEEE Trans. Power Electron. 1988, 3, 447–452. [Google Scholar] [CrossRef]

| Ride-through duration | 0.2 s |

| Voltage dip | STPI |

| Minimum acceptable dc-link voltage | 0.85 Vdc |

| Maximum permissible discharge current 1 | 4.1 A |

| Maximum permissible charging current 2 | 8.4 A |

| Parameter | At Start of Short Term Power Interruption(STPI) | At End of Short Term Power Interruption (STPI) | % Change 1 |

|---|---|---|---|

| DC-link voltage | 556 V | 471 V | −15.3% |

| Capacitor voltage | 544 V | 500 V | −8.1% |

| Speed | 916 rpm | 871 rpm | −4.5% |

| Torque | 16.1 Nm | 15.8 Nm | −1.9% |

| Parameter | at Start of STPI | at End of STPI | % Change 1 |

|---|---|---|---|

| DC-link voltage | 556 V | 456 V | −18.0% |

| Capacitor Voltage | 544 V | 488 V | −10.3% |

| Parameter | at Start of STPI | at End of STPI | % Change 1 |

|---|---|---|---|

| Speed | 882 rpm | 860 rpm | −2.5% |

| Torque | 15.7 Nm | 14.0 Nm | −10.3% |

| Parameter | Change in Value as Per * | ||

|---|---|---|---|

| Sizing Methodology | Simulation | Experiment | |

| DC-link voltage drop | 15.0% | 15.6% | 18.0% |

| Cap voltage drop | 7.7% | 8.3% | 10.3% |

| Parameter | Value Obtained as Per | ||

|---|---|---|---|

| Sizing Methodology | Simulation | Experiment | |

| Discharge current (A) | 4.2 A | 4.2 A | 4.1 A |

| Charging current (A) | 8.4 A | 8.3 A | 9.5 A |

| Parameter | Value Obtained as Per | % Variance | |

|---|---|---|---|

| Sizing Methodology | Simulation | ||

| DC-link voltage drop | 83.4 V | 82.8 V | 0.7% |

| Cap voltage drop | 54.0 V | 51.2 V | 5.3% |

| Parameter | Value Obtained as Per | % Variance | |

|---|---|---|---|

| Sizing Methodology | Simulation | ||

| Discharge current (A) | 27.89 A | 28.17 A | 1.0% |

| Charging current (A) | 20.88 A | 19.79 A | 5.4% |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Chiranga, F.; Masisi, L. Variable Speed Drive DC-Bus Voltage Dip Proofing. Energies 2021, 14, 8257. https://doi.org/10.3390/en14248257

Chiranga F, Masisi L. Variable Speed Drive DC-Bus Voltage Dip Proofing. Energies. 2021; 14(24):8257. https://doi.org/10.3390/en14248257

Chicago/Turabian StyleChiranga, Freeman, and Lesedi Masisi. 2021. "Variable Speed Drive DC-Bus Voltage Dip Proofing" Energies 14, no. 24: 8257. https://doi.org/10.3390/en14248257

APA StyleChiranga, F., & Masisi, L. (2021). Variable Speed Drive DC-Bus Voltage Dip Proofing. Energies, 14(24), 8257. https://doi.org/10.3390/en14248257