T-NPC Soft-Commutated Inverter Based on Reverse Blocking IGBTs with the Novel Concept of a DESAT Control Circuit in the Gate Driver

Abstract

:1. Introduction

2. T-NPC Inverter Cases of Implementation for Power Loss Reduction and DESAT Control Circuit in Gate Driver

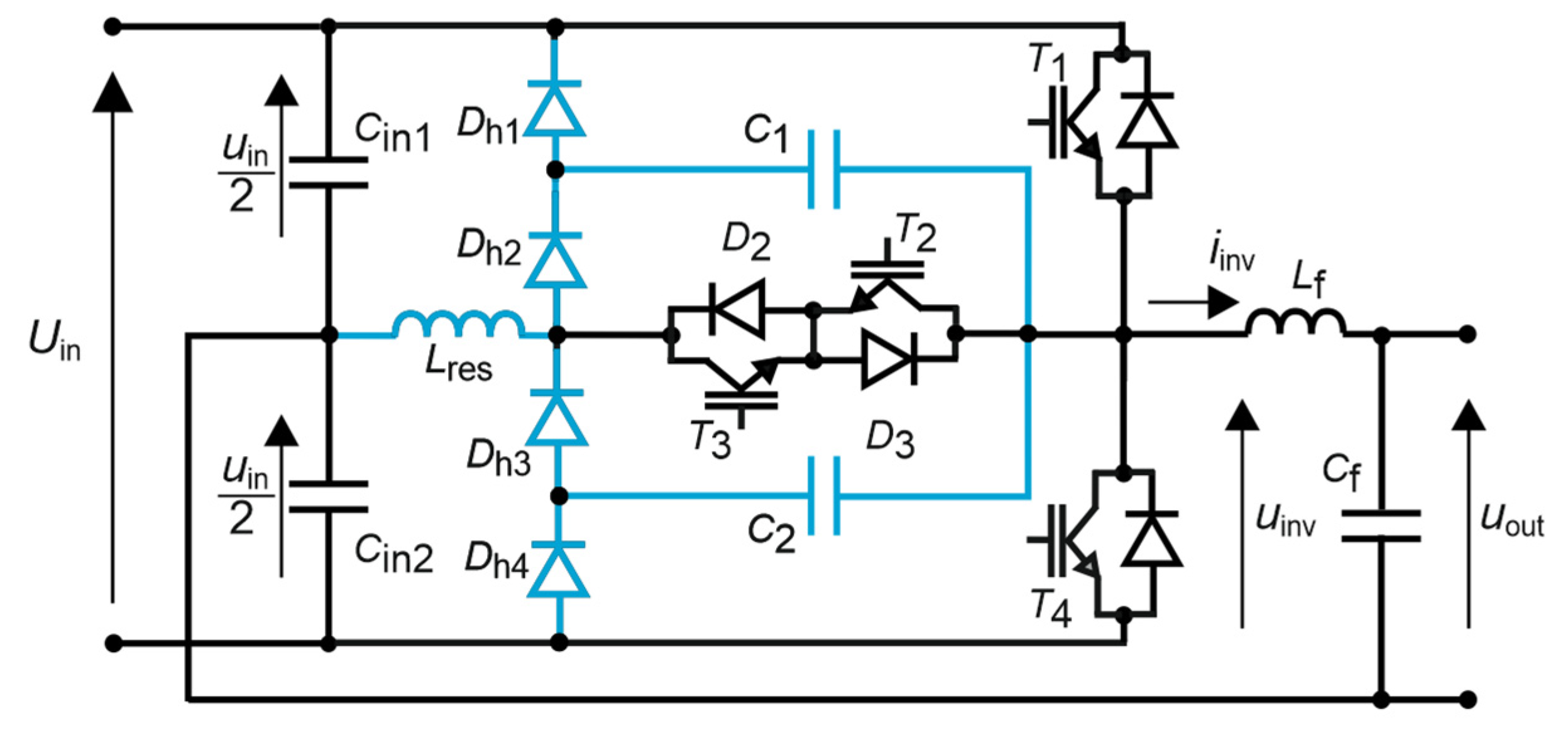

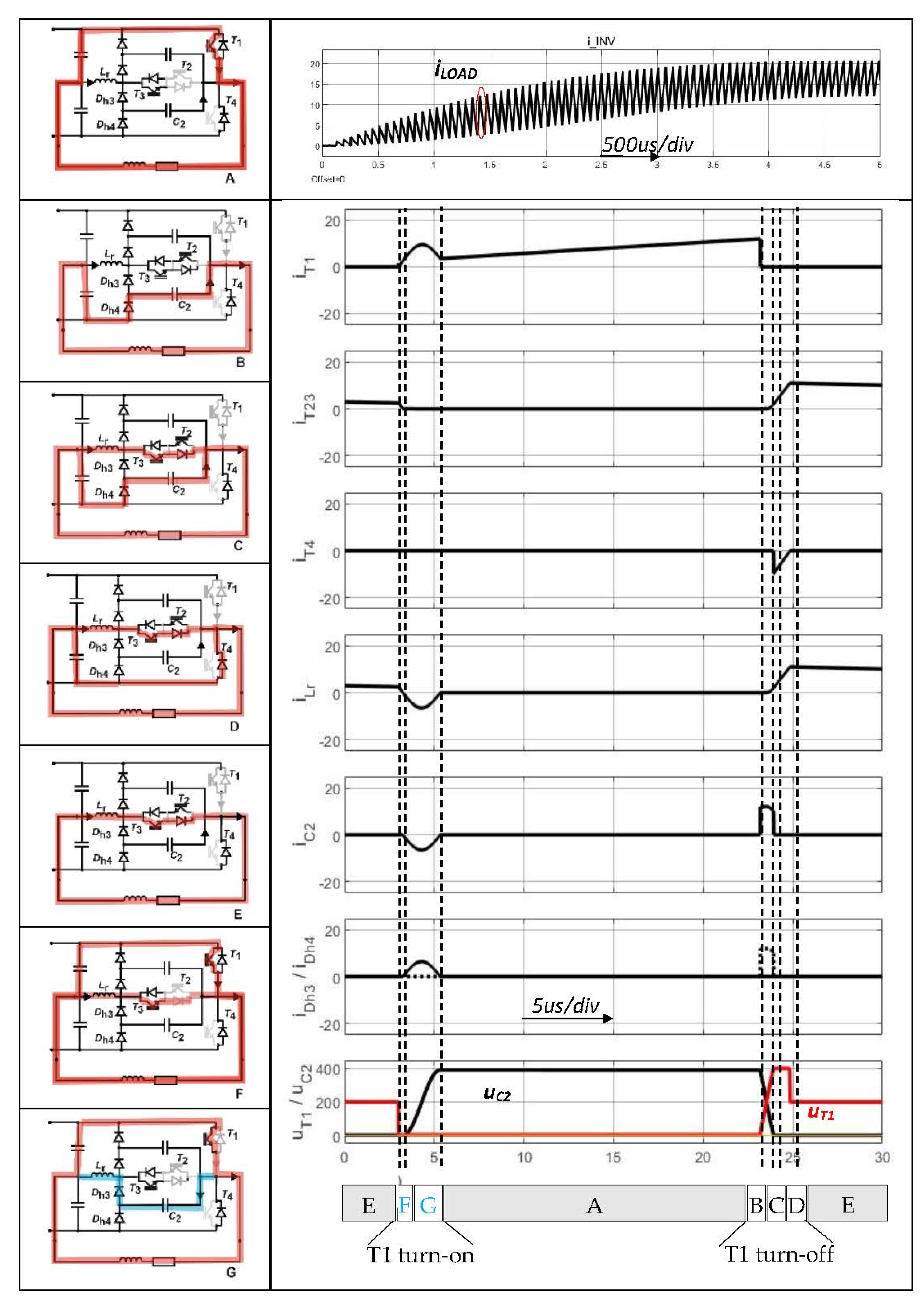

2.1. T-NPC Inverter in Soft Switching Configuration for the Reduction of Switching Losses

Analytical Consideration and Selection of the S3L Parameters

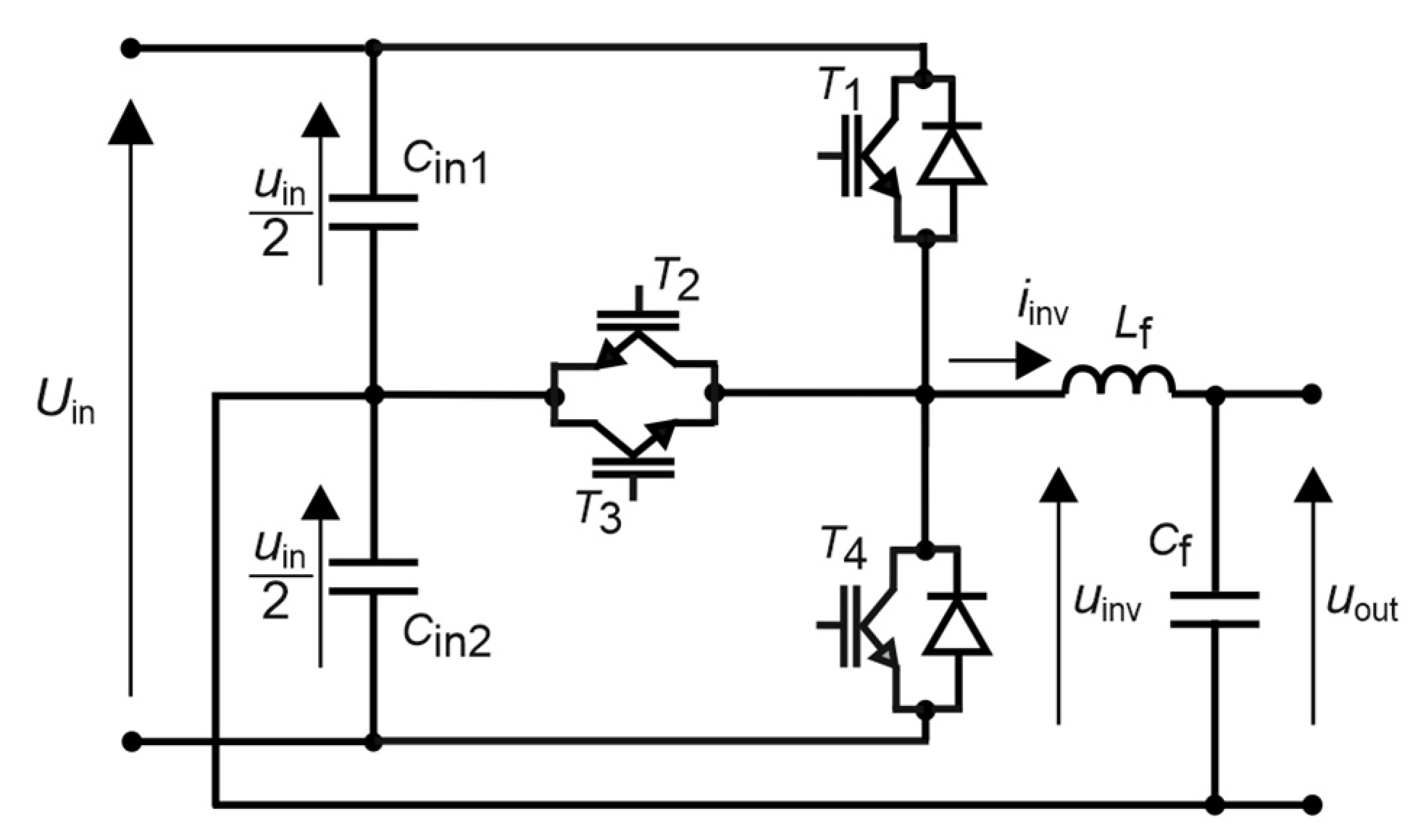

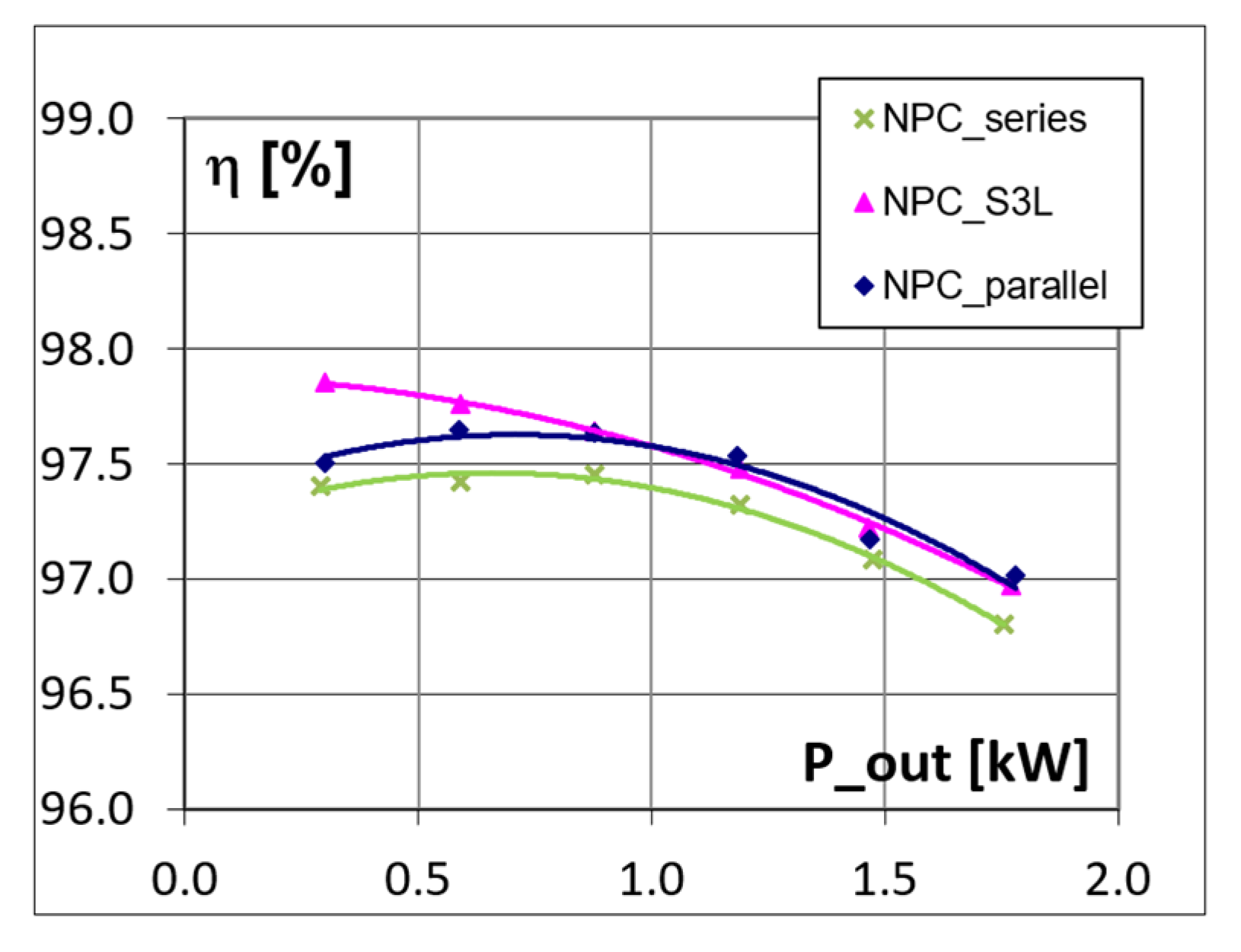

2.2. Reduction of the Conducted Losses in a T-NPC Inverter

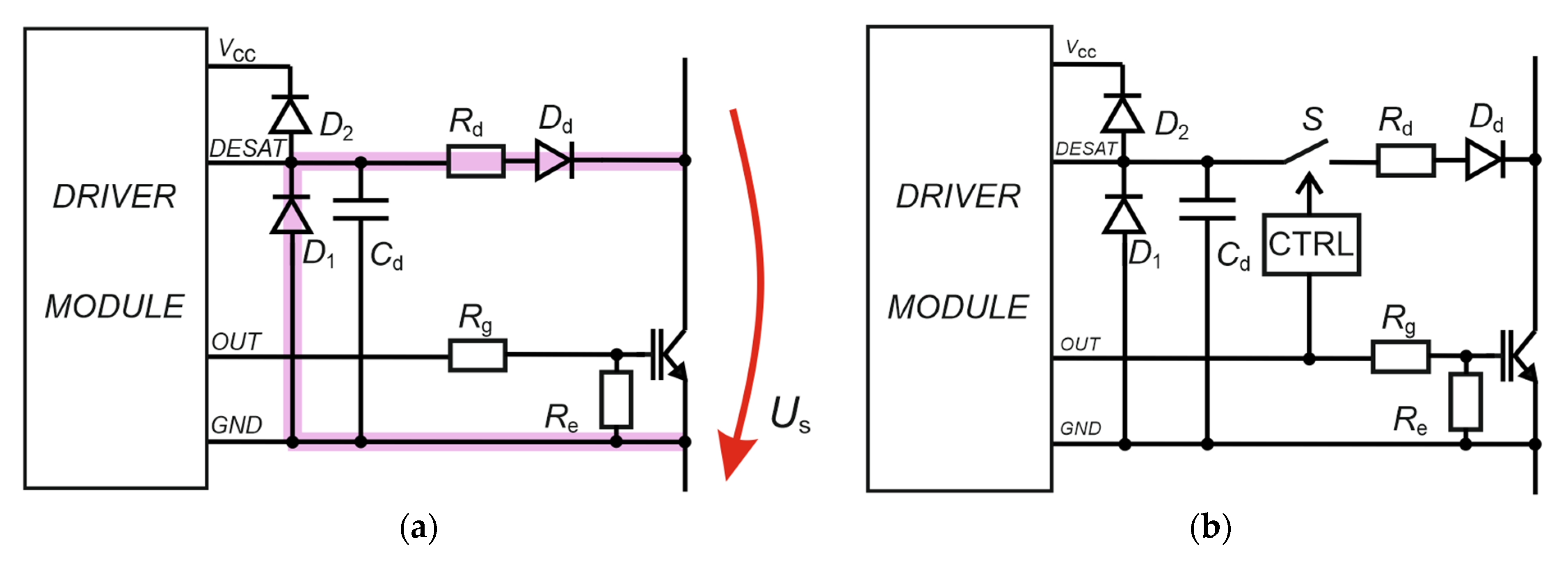

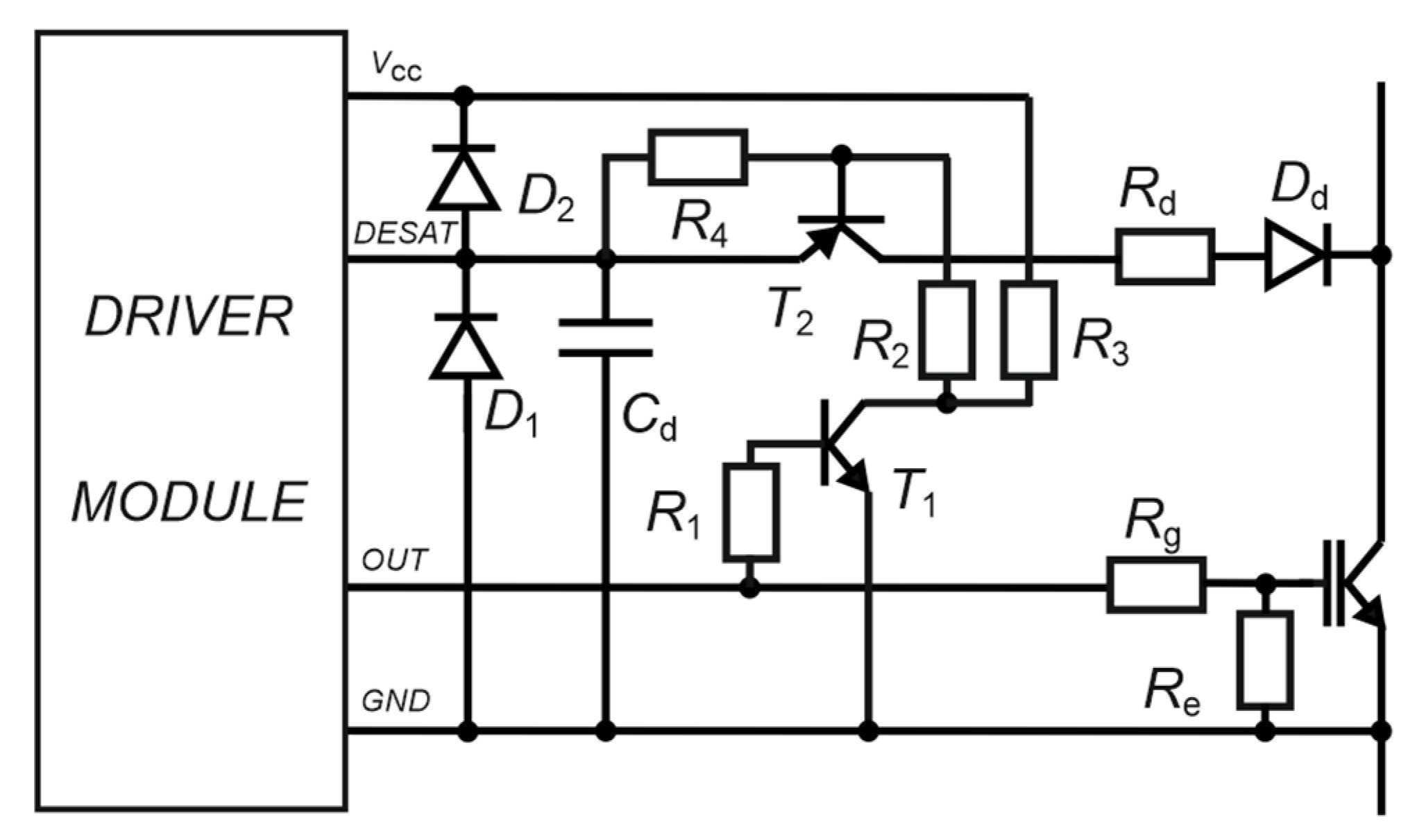

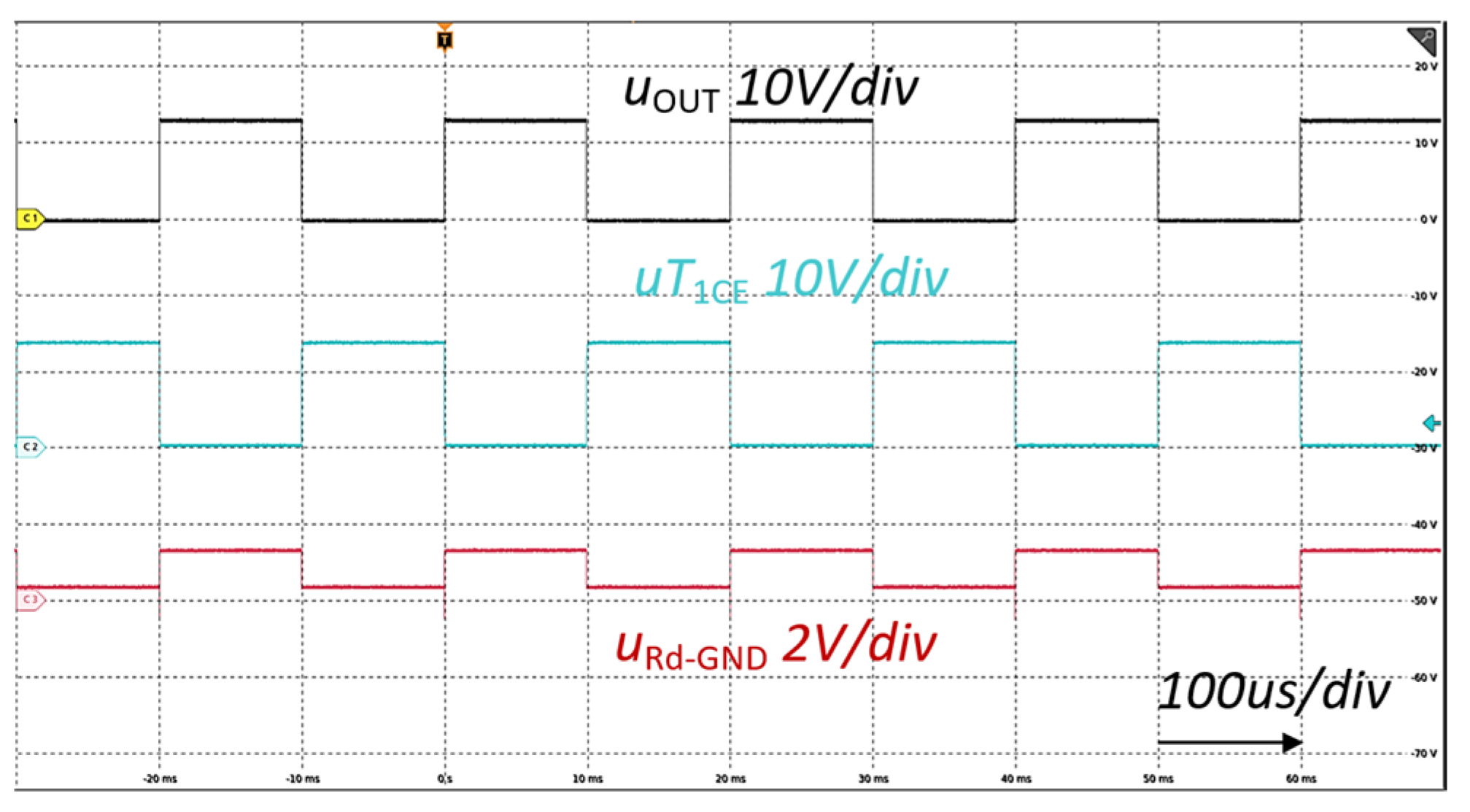

Driver with DESAT Control for Anti-Parallel Connected Reverse Blocking Transistors

3. Experimental Results

3.1. The Laboratory Setup

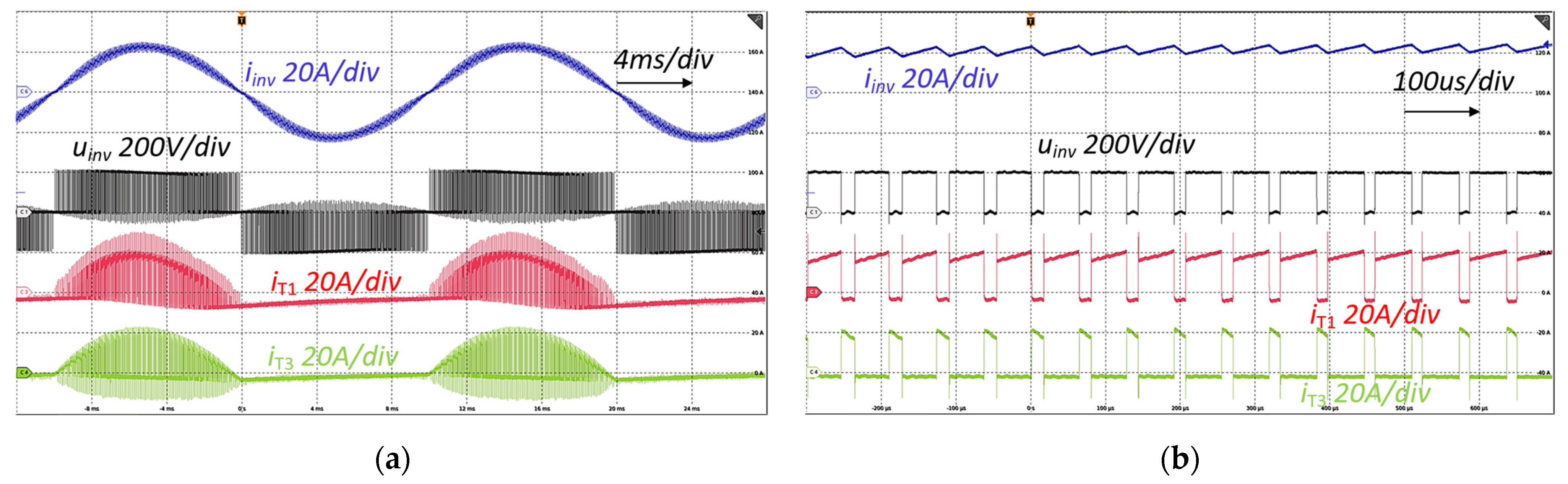

3.2. Result of Measurements

4. Discussion

Funding

Data Availability Statement

Conflicts of Interest

References

- Rodriguez, J.; Bernet, S.; Steimer, P.K.; Lizama, I.E. A Survey on Neutral-Point-Clamped Inverters. IEEE Trans. Ind. Electron. 2010, 57, 2219–2230. [Google Scholar] [CrossRef]

- Nabae, A.; Takahashi, I.; Akagi, H. A new neutral-point-clamped PWM inverter. IEEE Trans. Ind. Appl. 1981, IA–17, 518–523. [Google Scholar] [CrossRef]

- Salem, A.; Abido, M.A. T-Type Multilevel Converter Topologies: A Comprehensive Review. Arab. J. Sci. Eng. 2019, 44, 1713–1735. [Google Scholar] [CrossRef]

- Wang, Y.; Shi, W.W.; Xie, N.; Wang, C.M. Diode-Free T-type three-level neutral-point-clamped inverter for low-voltage renewable energy system. IEEE Trans. Ind. Electron. 2014, 61, 6168–6174. [Google Scholar] [CrossRef]

- Aly, M.; Ahmed, E.M.; Shoyama, M. Modulation Method for Improving Reliability of Multilevel T-Type Inverter in PV Systems. IEEE J. Emerg. Sel. Top. Power Electron. 2020, 8, 1298–1309. [Google Scholar] [CrossRef]

- Bhattacharya, S.; Mascarella, D.; Joos, G.; Cyr, J.-M.; Xu, J. A dual three-level T-NPC inverter for high-power traction applications. IEEE J. Emerg. Sel. Top. Power Electron. 2016, 4, 668–678. [Google Scholar] [CrossRef]

- Lee, J.-S.; Choi, U.-M.; Lee, K.-B. Comparison of tolerance controls for open-switch fault in a grid-connected T-type rectifier. IEEE Trans. Power Electron. 2015, 30, 5810–5820. [Google Scholar] [CrossRef]

- Lee, J.-S.; Lee, K.-B. An open-switch fault detection method and tolerance controls based on SVM in a grid-connected t-type rectifier with unity power factor. IEEE Trans. Ind. Electron. 2014, 61, 7092–7104. [Google Scholar] [CrossRef]

- Motto, E.; Donlon, J.; Tabata, M.; Takahashi, H.; Yu, Y.; Majumdar, G. Application characteristics of an experimental RB-IGBT (reverse blocking IGBT) module. In Proceedings of the Conference Record of the 2004 IEEE Industry Applications Conference, 2004. 39th IAS Annual Meeting, Seattle, WA, USA, 3–7 October 2004; Volume 3. [Google Scholar]

- Vaidya, M.; Naugarhiya, A.; Verma, S.; Mishra, G.P. Collector Engineered Bidirectional Insulated Gate Bipolar Transistor with Low Loss. IEEE Trans. Electron Dev. 2022, 69, 1604–1607. [Google Scholar] [CrossRef]

- Xu, X.; Chen, W.; Wang, F.; Sun, R.; Liu, C.; Xia, Y.; Xin, Y.; Zhou, Q.; Li, Z.; Zhang, B. An Ultralow Loss N-channel RB-IGBT with P-drift Region. In Proceedings of the 2020 32nd International Symposium on Power Semiconductor Devices and ICs (ISPSD), Vienna, Austria, 13–18 September 2020; pp. 455–458. [Google Scholar] [CrossRef]

- Kim, U.-J.; Oh, S.-G. New Sub-Module with Reverse Blocking IGBT for DC Fault Ride-Through in MMC-HVDC System. Energies 2021, 14, 1551. [Google Scholar] [CrossRef]

- Yang, X.; Xue, Y.; Chen, B.; Mu, Y.; Lin, Z.; Zheng, T.Q.; Igarashi, S. Reverse-blocking modular multilevel converter for battery energy storage systems. J. Mod. Power Syst. Clean Energy 2017, 5, 652–662. [Google Scholar] [CrossRef] [Green Version]

- Yang, X.; Xue, Y.; Chen, B.; Lin, Z.; Mu, Y.; Zheng, T.Q.; Igarshi, S. Reverse blocking sub-module based modular multilevel converter with DC fault ride-through capability. In Proceedings of the 2016 IEEE Energy Conversion Congress and Exposition (ECCE), Milwaukee, WI, USA, 18–22 September 2016. [Google Scholar] [CrossRef]

- Liu, Y.; Duan, Z.; Chen, Q.; Li, B.; Ban, M.; Li, Z. MMC-modified sub-module structure with double reverse blocking IGBTs. J. Power Electron. 2023, 23, 434–444. [Google Scholar] [CrossRef]

- Singh, A.K.; Jeyasankar, E.; Das, P.; Panda, S.K. A matrix-based nonisolated three-phase AC–DC rectifier with large step-down voltage gain. IEEE Trans. Power Electron. 2017, 32, 4796–4811. [Google Scholar] [CrossRef]

- Tuan, D.A.; Vu, P.; Lien, N.V. Design and Control of a Three-Phase T-Type Inverter using Reverse-Blocking IGBTs. Eng. Technol. Appl. Sci. Res. 2021, 11, 6614–6619. [Google Scholar] [CrossRef]

- di Benedetto, M.; Lidozzi, A.; Solero, L.; Crescimbini, F.; Grbovic, P.J. Reliability and Real-Time Failure Protection of the Three-Phase Five-Level E-Type Converter. IEEE Trans. Ind. Appl. 2020, 56, 6630–6641. [Google Scholar] [CrossRef]

- Kolar, J.W.; Ertl, H.; Erhartt, L.L.; Zach, F.C. Analysis of turn-off behavior and switching losses of a 1200 V/50 A zero-voltage or zero-current switched IGBT. In Proceedings of the Conference Record of the 1991 IEEE Industry Applications Society Annual Meeting, Dearborn, MI, USA, 28 September–4 October 1991; Volume 2, pp. 1508–1514. [Google Scholar]

- Gekeler, M.W. Soft switching three level inverter with passive snubber circuit (S3L inverter). In Proceedings of the 2011-14th European Conference on Power Electronics and Applications (EPE 2011), Birmingham, UK, 30 August–1 September 2011; pp. 1–10. [Google Scholar]

- Gekeler, M.W.; Schreitmueller, S.; Voigt, G. Comparison of the EMC and efficiency characteristics of hard and soft switching three-level inverters. In Proceedings of the International Exhibition and Conference for Power Electronics Intelligent Motion Renewable Energy and Energy Management, PCIM Europe, Nuremberg, Germany, 10–12 May 2016; pp. 1–8. [Google Scholar]

- Mondzik, A.; Stala, R.; Penczek, A.; Piróg, S.; Szot, S.; Ryłko, M. Operation Improvement of the Three-Level T-NPC Soft Switching Inverter with Passive Snubber, In Proceedings of the 2020 IEEE 19th International Power Electronics and Motion Control Conference (PEMC), Gliwice, Poland, 25-29 April 2021.

- Penczek, A.; Mondzik, A.; Piróg, S.; Twaróg, M.; Stala, R. New Three-Level Soft Turn-off T-type NPC Inverter. In Proceedings of the 21st International Symposium on Power Electronics (Ee), Novi Sad, Serbia, 27–30 October 2021; pp. 1–5. [Google Scholar]

- Mazgaj, W.; Szular, Z.; Rozegnal, B. Soft-Switching System with Safe Connections of Capacitors and Inductors in Three-phase Two-level Voltage Source Inverter. IEEE Trans. Power Electron. 2021, 36, 6443–6456. [Google Scholar] [CrossRef]

- Grbovic, P.J.; Gruson, F.; Idir, N.; Le Moigne, P. Turn-on Performance of Reverse Blocking IGBT (RB IGBT) and Optimization Using Advanced Gate Driver. IEEE Trans. Power Electron. 2010, 25, 970–980. [Google Scholar] [CrossRef]

- Zhou, D.; Sun, K.; Liu, Z.; Huang, L.; Matsuse, K.; Sasagawa, K. A Novel Driving and Protection Circuit for Reverse-Blocking IGBT Used in Matrix Converter. IEEE Trans. Ind. Appl. 2007, 43, 3–13. [Google Scholar] [CrossRef]

- Zhou, D.; Liu, Z.; Kong, P.; Sun, K.; Huang, L.; Sasagawa, K. An improved driving and protection circuit for reverse blocking IGBT. In Proceedings of the 2004 IEEE 35th Annual Power Electronics Specialists Conference (IEEE Cat. No.04CH37551), Aachen, Germany, 20–25 June 2004. [Google Scholar] [CrossRef]

- Dustert, C.; Volke, A. Implement Gate Drivers for 3-Level NPC2 Modules with Reverse-Blocking IGBTs. Electronic Design, 6 April 2015. [Google Scholar]

- Wang, X.; Li, Q.; Wang, S.; Wang, X.; Fu, Y. Design of Driving and protection circuit for Submodule based on cascaded H-bridge STATCOM. IOP Conf. Ser. Mater. Sci. Eng. 2018, 366, 012074. [Google Scholar] [CrossRef] [Green Version]

- Mondzik, A.; Penczek, A.; Ryłko, M.; Szot, S.; Szarek, M.; Stala, R. Driver Circuit, Circuit Arrangement Comprising a Driver Circuit, and Inverter Comprising a Circuit Arrangement. U.S. Patent US2018026517-B2, 13 October 2020. [Google Scholar]

- Morris, G.K.; Phillips, M.G.; Wei, L.; Lukaszewski, R.A. Operating IGBTs above Rated Junction Temperature Limits: Impacts to Reliability and Electrical Performance. In Proceedings of the 2016 Annual Reliability and Maintainability Symposium (RAMS), Tucson, AZ, USA, 25–28 January 2016; pp. 1–7. [Google Scholar] [CrossRef]

- Morozumi, A.; Yamada, K.; Miyasaka, T.; Sumi, S.; Seki, Y. Reliability of Power Cycling for IGBT Power Semiconductor Modules. IEEE Trans. Ind. Appl. 2003, 39, 665–671. [Google Scholar] [CrossRef]

- Liu, J.; Zhang, K.; Xiao, H.; Zhu, G.; Mao, X.; Zhang, W.; Chen, F.; Guo, X.; Liu, H. The analysis of IGBT module based on thermal simulation technology. In Proceedings of the 23rd International Conference on Electronic Packaging Technology (ICEPT), Dalian, China, 10–13 August 2022; pp. 1–3. [Google Scholar] [CrossRef]

- Chao, F.; Tong, A.; Fei, Q.; Jingyi, Z.; Xuequan, Y. Temperature and stress distribution of IGBT module in DC power cycling test with different switching frequencies. In Proceedings of the 2018 19th International Conference on Electronic Packaging Technology (ICEPT), Shanghai, China, 8–11 August 2018. [Google Scholar] [CrossRef]

- Abuelnaga, A.; Narimani, M.; Bahman, A.S. A Review on IGBT Module Failure Modes and Lifetime Testing. IEEE Access 2021, 9, 9643–9663. [Google Scholar] [CrossRef]

| Component | Parameters |

|---|---|

| T1, T4 | IKW40N120 |

| T2, T3 (classic T-NPC and Figure 1) | IKW40N120 |

| T2, T3 (Figure 3) | IXRH50N120 |

| Passives (Figure 1) | C1 = C2 = 22 nF, Lres = 20 uH |

| Diodes (Figure 1) | Dh1, Dh4: C4D20120, Dh2, Dh3: IDP15E60 |

| Input capacitance | Cin1 = Cin2 = 4.23 mF |

| Output filter | Lf = 150 uH, Cf = 2 × 4, 7 uF |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the author. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Mondzik, A. T-NPC Soft-Commutated Inverter Based on Reverse Blocking IGBTs with the Novel Concept of a DESAT Control Circuit in the Gate Driver. Energies 2023, 16, 4642. https://doi.org/10.3390/en16124642

Mondzik A. T-NPC Soft-Commutated Inverter Based on Reverse Blocking IGBTs with the Novel Concept of a DESAT Control Circuit in the Gate Driver. Energies. 2023; 16(12):4642. https://doi.org/10.3390/en16124642

Chicago/Turabian StyleMondzik, Andrzej. 2023. "T-NPC Soft-Commutated Inverter Based on Reverse Blocking IGBTs with the Novel Concept of a DESAT Control Circuit in the Gate Driver" Energies 16, no. 12: 4642. https://doi.org/10.3390/en16124642