Implementation of Phasor Measurement Unit Based on Phase-Locked Loop Techniques: A Comprehensive Review

Abstract

:1. Introduction

2. Synchrophasor Concepts

- Frequency step change test: A cosine signal with a frequency deviation of ±2 Hz for P class and ±5 Hz for M class of the nominal frequency.

- Magnitude deviation test: A cosine signal with an amplitude of 80% to 120% and 10% to 120% of the rated amplitude for P class and M class, respectively.

- Phase angle variation test: A cosine signal running at a frequency of for both PMU classes.

- Harmonic distortion test: A signal containing 1% and 10% of each harmonic up to 50th for P class and M class, respectively.

- Out-of-band interference test: The frequency of the signal varies between nominal frequency and ±10% of half the frequency of the reporting rate. This test is applicable only for P-class PMU.

- Amplitude modulation test: A cosine signal with a modulation amplitude of 10% of the rated amplitude value and modulation frequency of 2 Hz and 5 Hz for P class and M class, respectively.

- Phase angle modulation test: A cosine signal with a modulation angle of 0.1 radians and modulation frequency of 2 Hz and 5 Hz for P class and M class, respectively.

- Linear frequency ramp test: A cosine signal running at the nominal frequency by adding a frequency ramp of ±2 Hz/s and ±5 Hz/s for P class and M class, respectively.

- Magnitude step change test: A cosine signal with a 5% and 10% of the nominal magnitude step change for P class and M class, respectively.

- Phase angle step change test: A cosine signal with a 10° step change for both PMU classes.

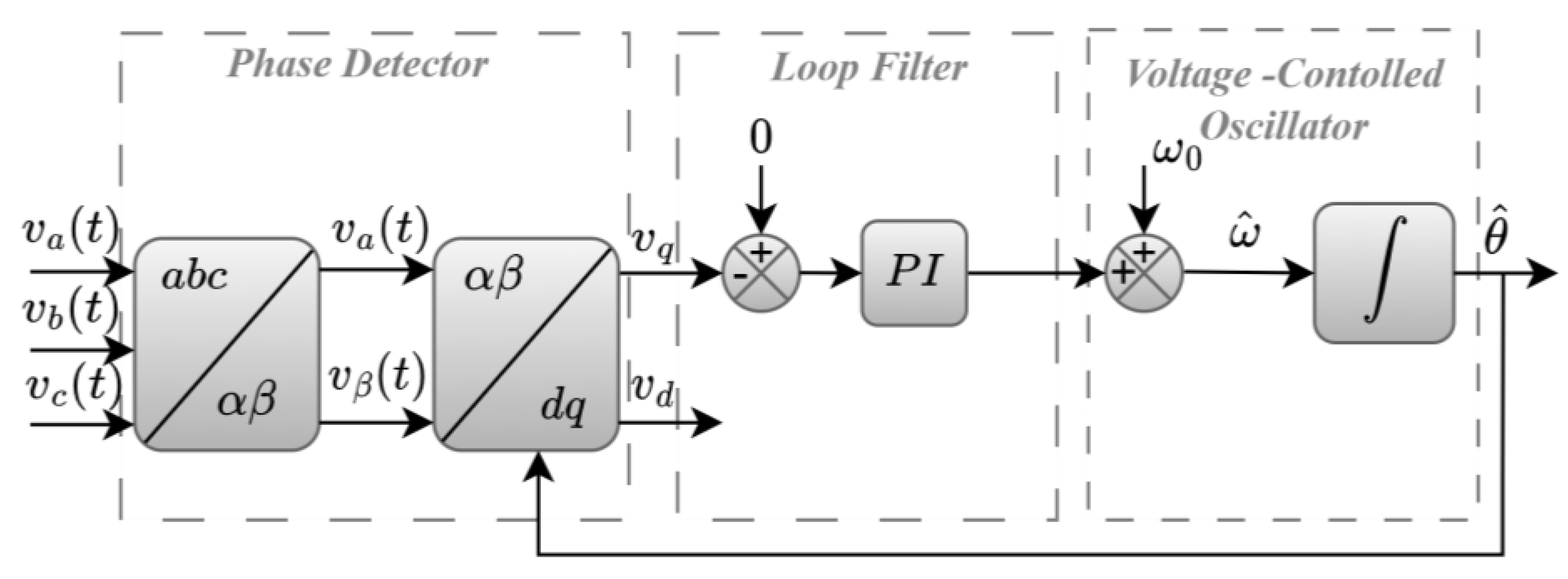

3. Basic Concepts of the Three-Phase PLL

4. PLL-Based Algorithm for the Estimation of the Synchrophasor

4.1. PID SRF-PLL-Based Algorithm for Positive-Sequence Synchrophasor Estimation

4.1.1. Experimental Results under Steady-State Conditions

4.1.2. Experimental Results under Dynamic Conditions

- Amplitude modulation test: The TVE is almost proportional to the value of the modulation frequency. Consequently, the TVE is considerably smaller for P class compared to M class since the required modulation frequency for P class is smaller than the corresponding M-class modulation frequency. Nevertheless, the proposed algorithm meets the requirement for both P and M classes.

- Phase angle modulation test: In this test, the proposed algorithm performs satisfactorily in terms of error values required by the standard making it compatible with both P and M classes.

- Linear frequency ramp test: The linear frequency ramp test results depict that the proposed algorithm fulfils all requirements for both PMU classes P and M.

- Amplitude step change test: The test results show that the TVE, FE and RFE narrowed very fast within the acceptable limits of the IEEE standard. Consequently, the proposed algorithm fulfils the requirements.

- Phase step change test: During the transient period, a small overshoot in the estimated signal amplitude occurred, causing phase and frequency errors that did not exceed the acceptable range for P and M classes.

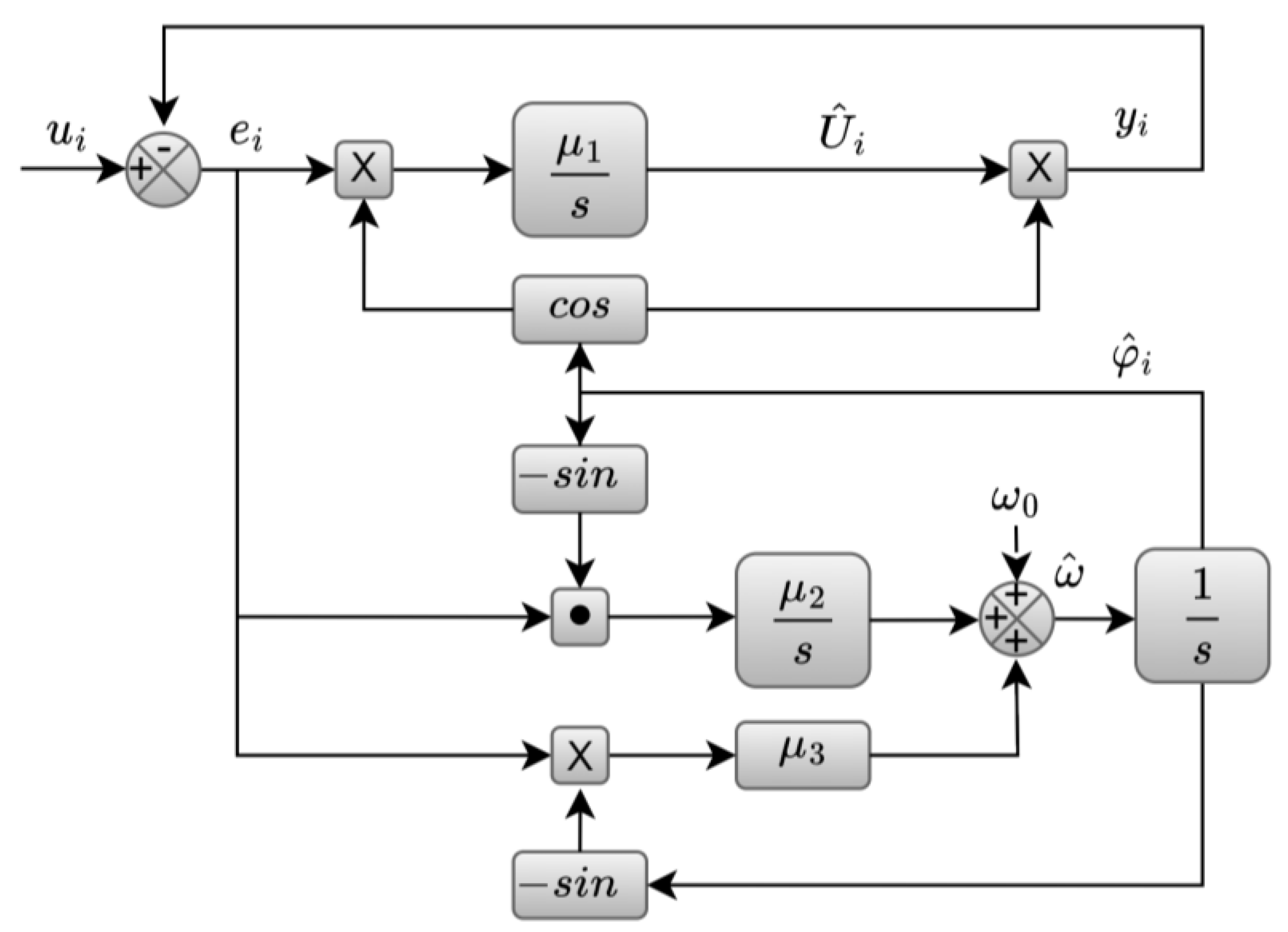

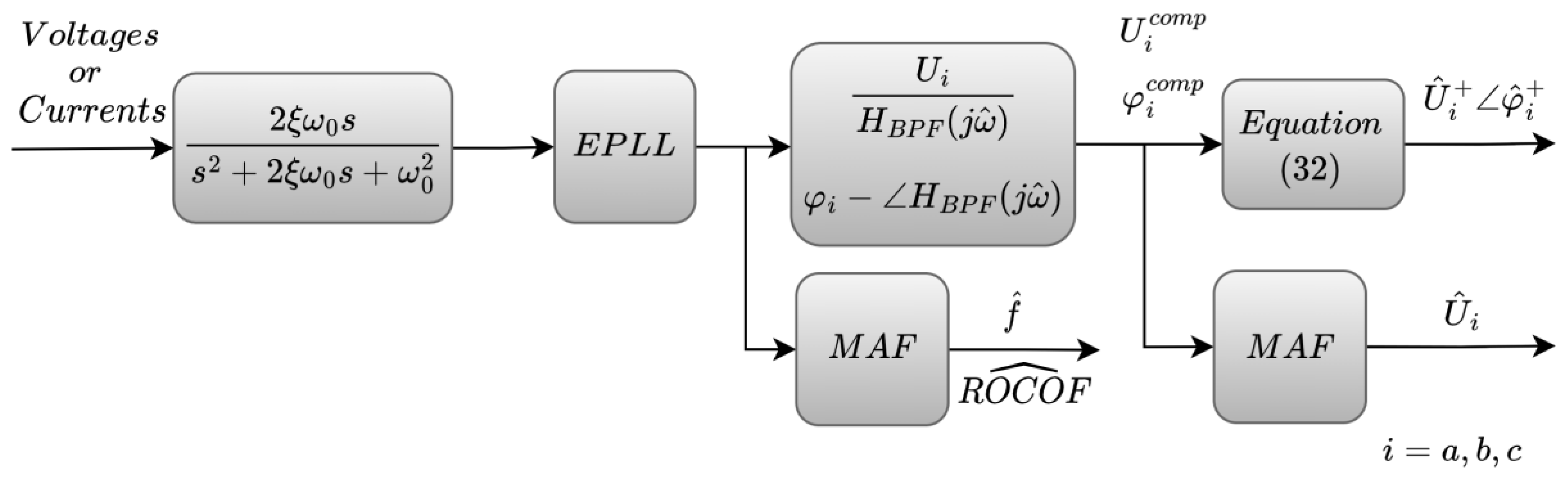

4.2. Three-Phase Enhanced PLL (EPLL)-Based Algorithm for Synchrophasor Estimation

4.2.1. Simulation Results

- Amplitude step change test: The initial three-phase balanced grid voltages undergo a step change of 10% of the fundamental amplitude. In steady-state conditions, the TVE value is below 1%. During the transient, the FE reaches 25 mHz, ROCOF reaches 4 Hz/s and the phase angle error reaches 1.25°.

- Phase angle step change test: The initial three-phase balanced grid voltages undergo a phase angle step change of 10°. In steady-state conditions, the TVE value is below 1%. During the transient, the FE reaches 100 MHz and ROCOF reaches 6 Hz/s. The phase angle is accurately detected.

- Frequency step change test: The initial three-phase balanced grid voltages undergo a frequency step change of 0.1 Hz. In steady-state and dynamic conditions, the TVE value is below 1%. During the transient, the ROCOF reaches 5 Hz/s and the phase angle error reaches 0.25°. The frequency step change is accurately detected.

- Linear frequency ramp test: The frequency of the grid voltages increases with a ramp function of 1 Hz/s. Under this dynamic behavior, the TVE is about 0.1%, the phase angle presents an error of 0.1°, and the frequency is tracked with a steady-state error of 20 MHz. It is worth mentioning that the ROCOF is accurately detected.

- Unbalanced Signal test: Negative- and zero-sequence components with a magnitude of 10% are induced in the three-phase balanced voltages. The PLL rejects the undesired components providing TVE less than 2% during transients and less than 1% in steady state.

- Harmonic distortion test: A signal containing 1% of each harmonic up to the 15th is induced in the three-phase balanced voltages. The TVE value is below 0.8%, the phase angle error is less than 0.5°, and no steady-state error has been observed in terms of frequency and ROCOF.

- Amplitude and Phase Modulation test: The modulation amplitude with a frequency of 2 Hz and a magnitude of 10% is applied to the PLL. The phase angle provides a peak error of about 0.25°, the FE is about 60 MHz, the peak value of RFE reaches 0.5 Hz/s and the TVE is almost 1%.

4.2.2. Experimental Results

- Initially, the grid voltages are in normal condition when at time t = 0.5 s the following harmonics are injected into the grid: 5th, 7th, 11th and 13th, with the corresponding amplitude of 8%, 5%, 3% and 1% of the fundamental component. Under steady-state abnormal conditions, the TVE value is below 1%, FE is ±0.002 Hz and ROCOF is 40 Hz/s. The ROCOF value reaches 60 Hz/s during the transient period.

- Initially, the grid voltages are in normal condition when at the time t = 0.5 s a source voltage is connected to the network that bears an imbalance factor of 10% of the negative sequence. Under steady-state abnormal conditions, the TVE value is below 1%, FE is negligible and ROCOF is 0 Hz/s. The ROCOF value reaches 80 Hz/s during the transient period.

- In this test case, harmonics (from the first case) and low-frequency oscillations (of 1 Hz) are injected into the grid voltages. Under steady-state abnormal conditions, the TVE value is below 1%, while the ROCOF value reaches 40 Hz/s.

- In this final test case, all the above abnormal conditions are considered (harmonics, sequence unbalance and low-frequency oscillations). Under steady-state abnormal conditions, the TVE value is below 1%, while the ROCOF value reaches 30 Hz/s.

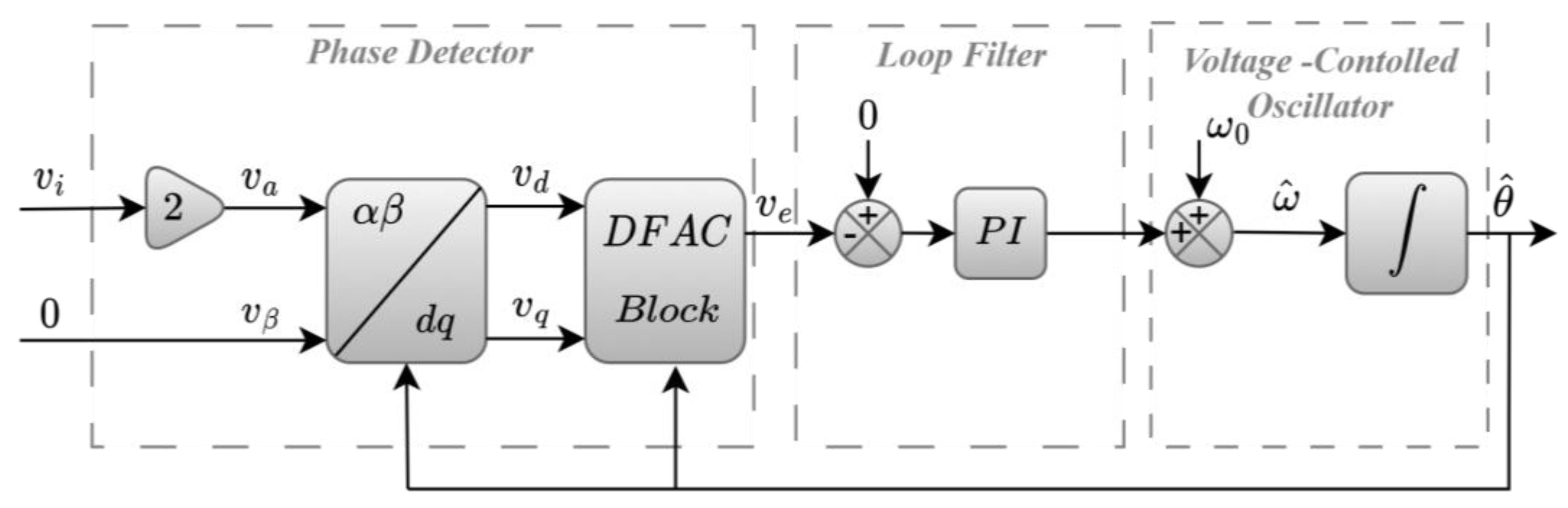

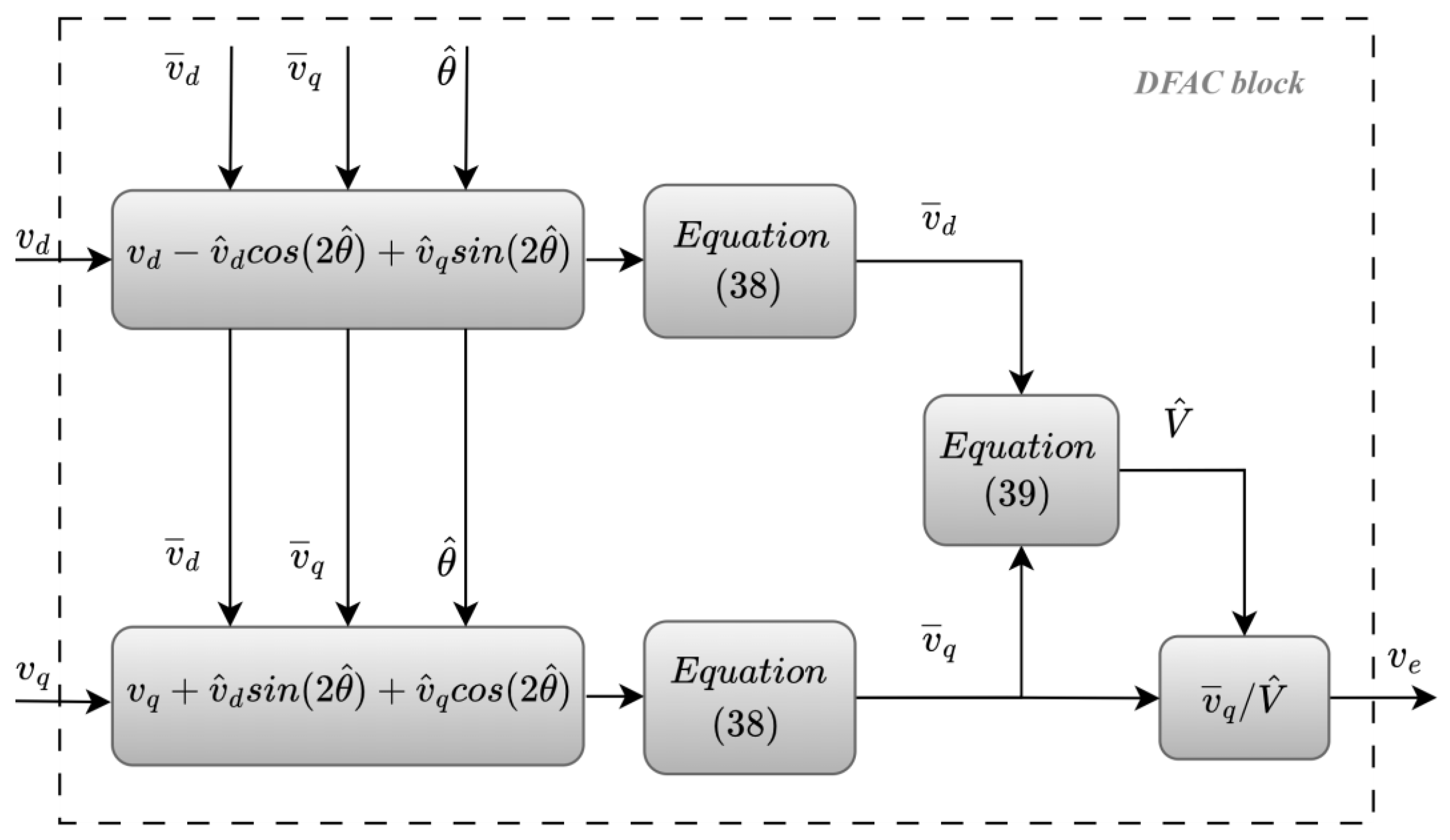

4.3. Double Frequency and Amplitude Compensation (DFAC)-PLL-Based Algorithm for Single-Phase Synchrophasor Estimation

4.3.1. Simulation Results under Steady-State Conditions

- Amplitude step change test: The amplitude of the input signal applied to the PLL varies from 10% to 120% in steps of 10% of the nominal amplitude. The limits for FE, RFE and TVE defined in IEEE standard [4,7] are 0.005 Hz, 0.1 Hz/s and 1%, respectively. The corresponding estimated values provided by the PLL meet the requirements.

- Frequency step change test: The frequency of the input signal applied to the PLL varies from 45 to 55 Hz. The limits for FE, RFE and TVE are the same as the amplitude step test. The corresponding estimated values, provided by the PLL, meet the requirements.

- Harmonics distortion test: Different sinusoidal signals containing harmonics (from 2nd to 50th) one at a time with an amplitude of 10% are applied to the PLL. The limits for FE and TVE defined in IEEE standard [4,7] are 0.025 Hz and 1%, respectively. The PLL provides TVE and FE within limits for harmonic orders greater than 10th and 39th, respectively.

4.3.2. Simulation Results under Dynamic Conditions

- Amplitude and phase angle modulation test: A sinusoidal modulation in the amplitude (with modulation frequency varying from 0.1 to 5 Hz) with a magnitude of 10% is applied to the PLL. According to the IEEE standard [4,7], the limits for FE, RFE and TVE are 0.3 Hz, 14 Hz/s and 3%, respectively. The proposed PLL succeeds in complying with the Standard for the FE and TVE but violates the RFE limit.

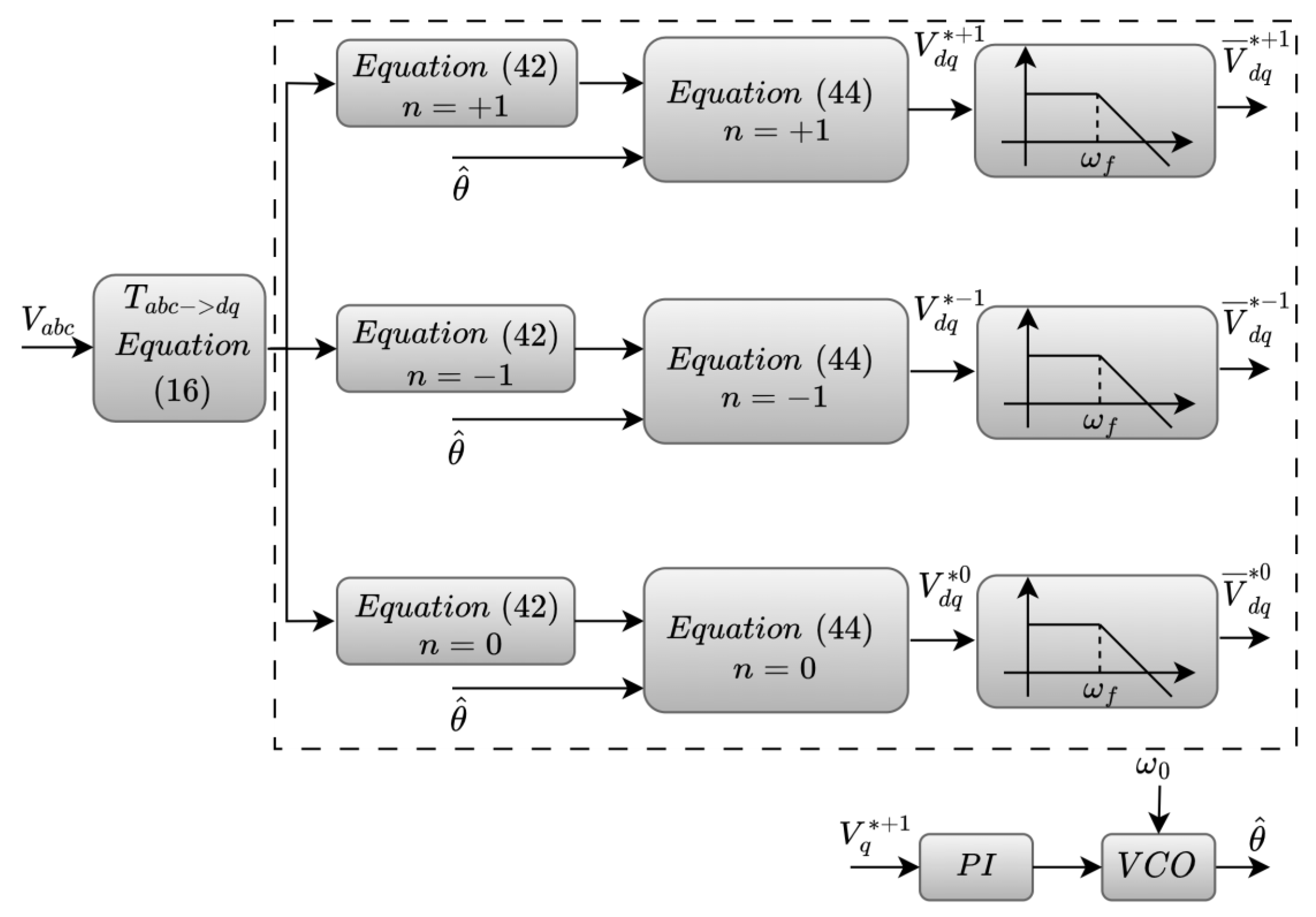

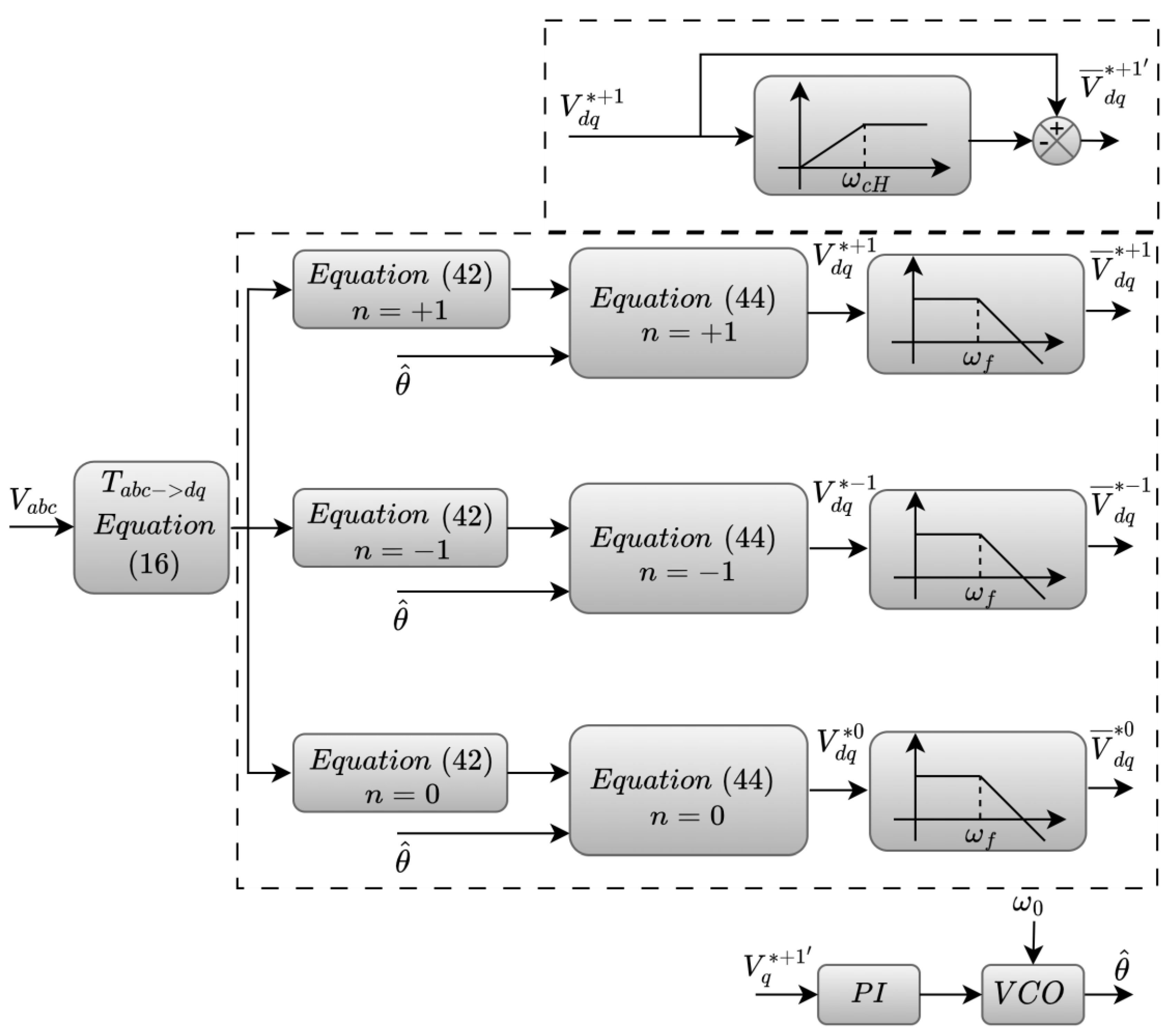

4.4. Harmonic Inter-Harmonic and DC Offset (HIHDO)-PLL-Based Algorithm for Three-Phase System Synchrophasor Estimation

4.4.1. Simulation Results of the HIHDO PLL-Based PMU Algorithm

4.4.2. Experimental Results of the HIHDO PLL-Based PMU Algorithm

- Phase angle step change test: The three-phase input signals undergo a phase angle jump of +30°. The PMU managed to track the phase angle step change while it obtained the value of +30° in 70 ms. During transients, slight overshoots occurred in the waveforms of the estimated signal amplitude and frequency with a settling time of 80 ms. Under this condition, the frequency reached 2.1 Hz and the amplitude 0.1 per unit at the time the phase angle step change occurred.

- Harmonic distortion test: In the grid voltages, the following harmonics were injected: 5th and 7th with the corresponding amplitude of 6% and 5% of the fundamental component. Furthermore, a phase angle step of −20° was introduced. The PMU succeeded in rejecting the high-frequency components while accurately estimating the signal amplitude, angle and frequency. During the transients, the voltage amplitude and frequency overshot were 1.6 Hz and 0.05 per unit, respectively. The settling times for the frequency, magnitude and phase estimations were 80 ms, 66 ms and 65 ms, respectively.

- Inter-harmonics and DC-offset rejection test: The PMU succeeded in rejecting the inter-harmonic and DC-offset components while accurately estimating the voltage amplitude, phase angle and frequency.

- Harmonics and voltage sag injection, and frequency step test: A combined set of test signals were applied to the proposed PLL-based PMU, comprising of 5% 7th, 3.5% 11th, 3% 15th and 2% 17th harmonics, voltage sag of 37% and frequency step change of −2 Hz. The harmonics were effectively compensated, resulting in an accurate estimation of voltage amplitude, phase angle and frequency. The proposed algorithm managed to detect the voltage sag within 10 ms while the settling time for the estimated frequency and phase angle were 80 ms and 140 ms, respectively. Furthermore, the PMU tracked the step change of the frequency within 100 ms.

5. Discussion

- The PID SRF-PLL-based PMU algorithm provides satisfactory experimental results in the estimation of positive-sequence amplitude, phase angle, frequency and ROCOF. In addition, the implementation of the algorithm presents a low computational burden, making it capable of being developed on a general-purpose microcontroller with DSP features. The experimental results showed that the proposed PLL-based PMU algorithm for the synchrophasor estimation complies with all the IEEE standard requirements [4,7] for both PMU classes P and M, while in conjunction with the low computational cost, makes it attractive for implementation of low-cost PMUs in order to be used in distribution networks [35], although it provides a low reporting rate.

- The EPLL-based PMU algorithm provides good experimental and simulation results in estimating positive-sequence amplitude, phase angle, frequency and ROCOF for a P-class PMU. It is worth noting that the estimated frequency and ROCOF are derived from the processing of the information obtained from all three signal components, making these estimated measurements more reliable and stable. In terms of amplitude and phase angle modulation tests, the proposed method meets TVE requirements but failed in estimating accurately the frequency as well as the ramp frequency test [21]. The proposed PMU algorithm addresses the abnormal grid conditions such as imbalances and harmonics, while also providing a fast dynamic response and acceptable steady-state accuracy which make it a potential candidate algorithm for a P-class phasor measurement unit [39]. It can be observed from [39] that the computational complexity of the proposed algorithm is low; therefore, it can be implemented on a low-cost microprocessor.

- The DFAC-PLL is a single-phase PLL that can estimate the phase amplitude, angle and frequency of the input signal [42]. Although the compliance testing of the PLL in accordance with the IEEE standard [4,7] is performed without the pre- and post-filtering stages, it shows that it can meet the requirements of the steady-state condition tests, while exceeding the acceptable limits in the harmonic distortion and out-of-band interference tests. In terms of dynamic condition tests, the proposed PLL meets the requirements for the synchrophasor estimation when subjected to the amplitude modulation test but exceeded the limitations in the phase angle modulation test. In case the DFAC-PLL is to be used for synchrophasor estimation algorithm, the filtering and compensation stages are required.

- The HIHDO-PLL-based PMU successfully faces the normal and abnormal grid conditions, while presenting excellent simulation results in the estimation of the positive-sequence component of phase magnitude and angle of the power grid. Moreover, it provides fast dynamic response and slight overshoots without sacrificing the required accuracy under harmonically polluted and faulty network conditions which is also the case for the estimation of the synchrophasor in a more realistic power grid. The proposed PLL presents a lower computational burden compared with existing PLL algorithms in the recent literature for addressing both the imbalances and harmonic distortion due to abnormal grid conditions, but its execution requires 106 mathematical operations, which is an important burden if its implementation is performed by a general-purpose microcontroller with DSP features. With the exception of the computational burden, the mathematical analysis and simulation results on network faults showed that the HIHDO-PLL has the potential to be used for synchrophasor estimation algorithms [43].

6. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Monti, A.; Muscas, C.; Ponci, F. (Eds.) Phasor Measurement Units and Wide Area Monitoring Systems: From the Sensors to the System; Elsevier: Amsterdam, The Netherlands, 2016; ISBN 978-0-12-804569-5. [Google Scholar]

- Karimi-Ghartemani, M.; Ooi, B.-T.; Bakhshai, A. Application of Enhanced Phase-Locked Loop System to the Computation of Synchrophasors. IEEE Trans. Power Deliv. 2011, 26, 22–32. [Google Scholar] [CrossRef]

- Talukder, Z.; Nishat Tasnim, K.; Reza, M.S. A Comparative Study of Various Methods of Phasor Measurement Unit Algorithms. In Proceedings of the 2019 1st International Conference on Advances in Science, Engineering and Robotics Technology (ICASERT), Dhaka, Bangladesh, 3–5 May 2019; pp. 1–6. [Google Scholar]

- IEEE Std C37.118.1-2011; IEEE Standard for Synchrophasor Measurements for Power Systems. IEEE: Piscateville, NJ, USA, 2011.

- IEEE Std C37.118-2005 (Revision of IEEE Std 1344-1995); IEEE Standard for Synchrophasors for Power Systems. IEEE: Piscateville, NJ, USA, 2006; pp. 1–65.

- IEEE Std C37.118.1a-2014 (Amendment to IEEE Std C37.118.1-2011); IEEE Standard for Synchrophasor Measurements for Power Systems Amendment 1: Modification of Selected Performance Requirements. IEEE: Piscataway, NJ, USA, 2014.

- IEEE Std C37.118.2-2011; IEEE Standard for Synchrophasor Data Transfer for Power Systems. IEEE: Piscataway, NJ, USA, 2011.

- Karimi-Ghartemani, M.; Ooi, B.-T.; Bakhshai, A. Investigation of DFT-Based Phasor Measurement Algorithm. In Proceedings of the IEEE PES General Meeting, Providence, RI, USA, 25–29 July 2010; pp. 1–6. [Google Scholar]

- Zhan, L.; Liu, Y.; Liu, Y. A Clarke Transformation-Based DFT Phasor and Frequency Algorithm for Wide Frequency Range. IEEE Trans. Smart Grid 2018, 9, 67–77. [Google Scholar] [CrossRef]

- Derviškadić, A.; Romano, P.; Paolone, M. Iterative-Interpolated DFT for Synchrophasor Estimation in M-Class Compliant PMUs. In Proceedings of the 2017 IEEE Manchester PowerTech, Manchester, UK, 18–22 June 2017; pp. 1–6. [Google Scholar]

- Romano, P.; Paolone, M. Enhanced Interpolated-DFT for Synchrophasor Estimation in FPGAs: Theory, Implementation, and Validation of a PMU Prototype. IEEE Trans. Instrum. Meas. 2014, 63, 2824–2836. [Google Scholar] [CrossRef]

- Romano, P.; Paolone, M. An Enhanced Interpolated-Modulated Sliding DFT for High Reporting Rate PMUs. In Proceedings of the 2014 IEEE International Workshop on Applied Measurements for Power Systems Proceedings (AMPS), Aachen, Germany, 24–26 September 2014; pp. 1–6. [Google Scholar]

- De la O Serna, J.A.; Rodriguez-Maldonado, J. Instantaneous Oscillating Phasor Estimates with TaylorK-Kalman Filters. IEEE Trans. Power Syst. 2011, 26, 2336–2344. [Google Scholar] [CrossRef]

- Dash, P.K.; Hasan, S. A Fast Recursive Algorithm for the Estimation of Frequency, Amplitude, and Phase of Noisy Sinusoid. IEEE Trans. Ind. Electron. 2011, 58, 4847–4856. [Google Scholar] [CrossRef]

- Platas-Garza, M.A.; de La O Serna, J.A. Dynamic Phasor and Frequency Estimates through Maximally Flat Differentiators. IEEE Trans. Instrum. Meas. 2010, 59, 1803–1811. [Google Scholar] [CrossRef]

- Roscoe, A.J.; Abdulhadi, I.F.; Burt, G.M. P and M Class Phasor Measurement Unit Algorithms Using Adaptive Cascaded Filters. IEEE Trans. Power Deliv. 2013, 28, 1447–1459. [Google Scholar] [CrossRef] [Green Version]

- De La O Serna, J.A. Synchrophasor Measurement with Polynomial Phase-Locked-Loop Taylor–Fourier Filters. IEEE Trans. Instrum. Meas. 2015, 64, 328–337. [Google Scholar] [CrossRef]

- Castello, P.; Liu, J.; Muscas, C.; Pegoraro, P.A.; Ponci, F.; Monti, A. A Fast and Accurate PMU Algorithm for P+M Class Measurement of Synchrophasor and Frequency. IEEE Trans. Instrum. Meas. 2014, 63, 2837–2845. [Google Scholar] [CrossRef]

- Toscani, S.; Muscas, C.; Pegoraro, P.A. Design and Performance Prediction of Space Vector-Based PMU Algorithms. IEEE Trans. Instrum. Meas. 2017, 66, 394–404. [Google Scholar] [CrossRef]

- Toscani, S.; Muscas, A. Space Vector Based Approach for Synchrophasor Measurement. In Proceedings of the 2014 IEEE International Instrumentation and Measurement Technology Conference (I2MTC) Proceedings, Montevideo, Uruguay, 12–15 May 2014; pp. 257–261. [Google Scholar]

- Karimi-Ghartemani, M.; Mojiri, M.; Bakhshai, A.; Jain, P. A Phasor Measurement Algorithm Based on Phase-Locked Loop. In Proceedings of the PES T&D 2012, Orlando, FL, USA, 7–10 May 2012; pp. 1–6. [Google Scholar]

- Sun, K.; Zhou, Q.; Liu, Y. A Phase Locked Loop-Based Approach to Real-Time Modal Analysis on Synchrophasor Measurements. IEEE Trans. Smart Grid 2014, 5, 260–269. [Google Scholar] [CrossRef]

- Messina, F.; Marchi, P.; Rey Vega, L.; Galarza, G.; Laiz, H. A Novel Modular Positive-Sequence Synchrophasor Estimation Algorithm for PMUs. IEEE Trans. Instrum. Meas. 2017, 66, 1164–1175. [Google Scholar] [CrossRef]

- Ferrero, R.; Pegoraro, P.A.; Toscani, S. A Space Vector Phase-Locked-Loop Approach to Synchrophasor, Frequency and Rocof Estimation. In Proceedings of the 2019 IEEE International Instrumentation and Measurement Technology Conference (I2MTC), Auckland, New Zealand, 20–23 May 2019; pp. 1–6. [Google Scholar]

- Ferrero, R.; Pegoraro, P.A.; Toscani, S. Proposals and Analysis of Space Vector-Based Phase-Locked-Loop Techniques for Synchrophasor, Frequency, and ROCOF Measurements. IEEE Trans. Instrum. Meas. 2020, 69, 2345–2354. [Google Scholar] [CrossRef]

- Trento, B.; Wang, B.; Sun, K.; Tolbert, L.M. Integration of Phase-Locked Loop Based Real-Time Oscillation Tracking in Grid Synchronized Systems. In Proceedings of the 2014 IEEE PES General Meeting|Conference & Exposition, Washington, DC, USA, 27–31 July 2014; pp. 1–5. [Google Scholar]

- De Carvalho, G.U.; Weber Denardin, G.; Cardoso, R.; Moraes, F. Design and Test of a SRF-PLL Based Algorithm for Positive-Sequence Synchrophasor Measurements. In Proceedings of the 2019 IEEE 15th Brazilian Power Electronics Conference and 5th IEEE Southern Power Electronics Conference (COBEP/SPEC), Santos, Brazil, 1–4 December 2019; pp. 1–6. [Google Scholar]

- Golestan, S.; Guerrero, J.M.; Vasquez, J. Three-Phase PLLs: A Review of Recent Advances. IEEE Trans. Power Electron. 2017, 32, 1894–1907. [Google Scholar] [CrossRef] [Green Version]

- Santos Filho, M.; Seixas, P.F.; Cortizo, P.; Torres, L.A.B.; Souza, A.F. Comparison of Three Single-Phase PLL Algorithms for UPS Applications. IEEE Trans. Ind. Electron. 2008, 55, 2923–2932. [Google Scholar] [CrossRef]

- Karimi-Ghartemani, M.; Iravani, M. A Method for Synchronization of Power Electronic Converters in Polluted and Variable-Frequency Environments. IEEE Trans. Power Syst. 2004, 19, 1263–1270. [Google Scholar] [CrossRef]

- Chung, S.-K. A Phase Tracking System for Three Phase Utility Interface Inverters. IEEE Trans. Power Electron. 2000, 15, 431–438. [Google Scholar] [CrossRef] [Green Version]

- Velasco, D.; Trujillo, C.; Garcera, G.; Figueres, E. An Active Anti-Islanding Method Based on Phase-PLL Perturbation. IEEE Trans. Power Electron. 2011, 26, 1056–1066. [Google Scholar] [CrossRef] [Green Version]

- Kaura, V.; Blasko, V. Operation of a Phase Locked Loop System under Distorted Utility Conditions. IEEE Trans. Ind. Appl. 1997, 33, 58–63. [Google Scholar] [CrossRef]

- Liu, B.; Zhuo, F.; Zhu, Y.; Yi, H.; Wang, F. A Three-Phase PLL Algorithm Based on Signal Reforming Under Distorted Grid Conditions. IEEE Trans. Power Electron. 2015, 30, 5272–5283. [Google Scholar] [CrossRef]

- De Carvalho, G.U.; Denardin, G.W.; Cardoso, R.; Grando, F.L. A PID SRF-PLL Based Algorithm for Positive-sequence Synchrophasor Measurements. Int. Trans. Electr. Energy Syst. 2021, 31, e12777. [Google Scholar] [CrossRef]

- Fortescue, L. Method of Symmetrical Co-Ordinates Applied to the Solution of Polyphase Networks. Trans. Am. Inst. Electr. Eng. 1918, XXXVII, 1027–1140. [Google Scholar] [CrossRef]

- Rodriguez, P.; Pou, J.; Bergas, J.; Candela, J.I.; Burgos, P.; Boroyevich, D. Decoupled Double Synchronous Reference Frame PLL for Power Converters Control. IEEE Trans. Power Electron. 2007, 22, 584–592. [Google Scholar] [CrossRef]

- Karimi-Ghartemani, M.; Mojiri, M.; Safaee, A.; Walseth, J.A.; Khajehoddin, S.A.; Jain, P.; Bakhshai, A. A New Phase-Locked Loop System for Three-Phase Applications. IEEE Trans. Power Electron. 2013, 28, 1208–1218. [Google Scholar] [CrossRef]

- Costa, T.B.; Berriel, O.; Lima, A.S.; Dias, F.S. Evaluation of a Phase-Locked Loop Phasor Measurement Algorithm on a Harmonic Polluted Environment in Applications Such as PMU. J. Control Autom. Electr. Syst. 2019, 30, 424–433. [Google Scholar] [CrossRef]

- Kundur, P. Power System Stability and Control; McGraw-Hill Professional: New York, NY, USA, 1994. [Google Scholar]

- Kumar, P.; Gurrala, G. IEEE C37.118.1a-2014 Compliance Testing of EPLL and DFAC-PLL for Synchrophasors. In Proceedings of the 2018 North American Power Symposium (NAPS), Fargo, ND, USA, 9–11 September 2018; pp. 1–6. [Google Scholar]

- Golestan, S.; Monfared, M.; Freijedo, F.D.; Guerrero, J.M. Design and Tuning of a Modified Power-Based PLL for Single-Phase Grid-Connected Power Conditioning Systems. IEEE Trans. Power Electron. 2012, 27, 3639–3650. [Google Scholar] [CrossRef] [Green Version]

- Ali, Z.; Saleem, K.; Brown, R.; Christofides, N.; Dudley, S. Performance Analysis and Benchmarking of PLL-Driven Phasor Measurement Units for Renewable Energy Systems. Energies 2022, 15, 1867. [Google Scholar] [CrossRef]

- Ali, Z.; Christofides, N.; Hadjidemetriou, L.; Kyriakides, E. Design of an Advanced PLL for Accurate Phase Angle Extraction under Grid Voltage HIHs and DC Offset. IET Power Electron. 2018, 11, 995–1008. [Google Scholar] [CrossRef]

| PLL-Based PMU Approach | ||||

|---|---|---|---|---|

| PID SRF-PLL | EPLL | DFAC-PLL | HIHDO-PLL | |

| Harmonic rejection | Good | Good | Poor | Very good |

| Dynamic response | Faster | Fast | Slow | Fast |

| Computational burden | Low | Medium | Medium | High |

| Compliant with IEEE Std. | Yes, for P and M classes | Yes, for P class. Minor deviations | No | Should be investigated |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Giotopoulos, V.; Korres, G. Implementation of Phasor Measurement Unit Based on Phase-Locked Loop Techniques: A Comprehensive Review. Energies 2023, 16, 5465. https://doi.org/10.3390/en16145465

Giotopoulos V, Korres G. Implementation of Phasor Measurement Unit Based on Phase-Locked Loop Techniques: A Comprehensive Review. Energies. 2023; 16(14):5465. https://doi.org/10.3390/en16145465

Chicago/Turabian StyleGiotopoulos, Vasilis, and Georgios Korres. 2023. "Implementation of Phasor Measurement Unit Based on Phase-Locked Loop Techniques: A Comprehensive Review" Energies 16, no. 14: 5465. https://doi.org/10.3390/en16145465