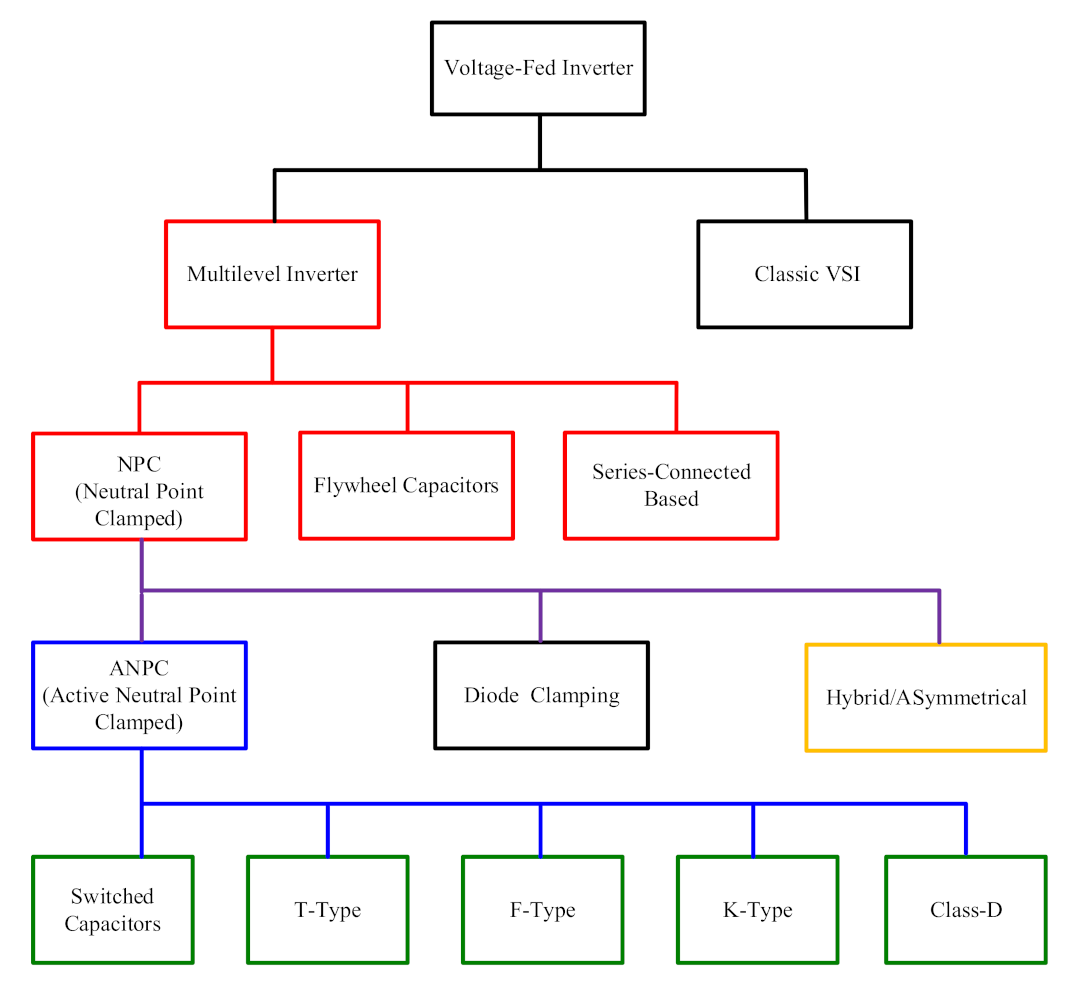

Perspective of Voltage-Fed Single-Phase Multilevel DC-AC Inverters

Abstract

:1. Introduction

2. Analysis of Basic Topologies of Systematic MLIs

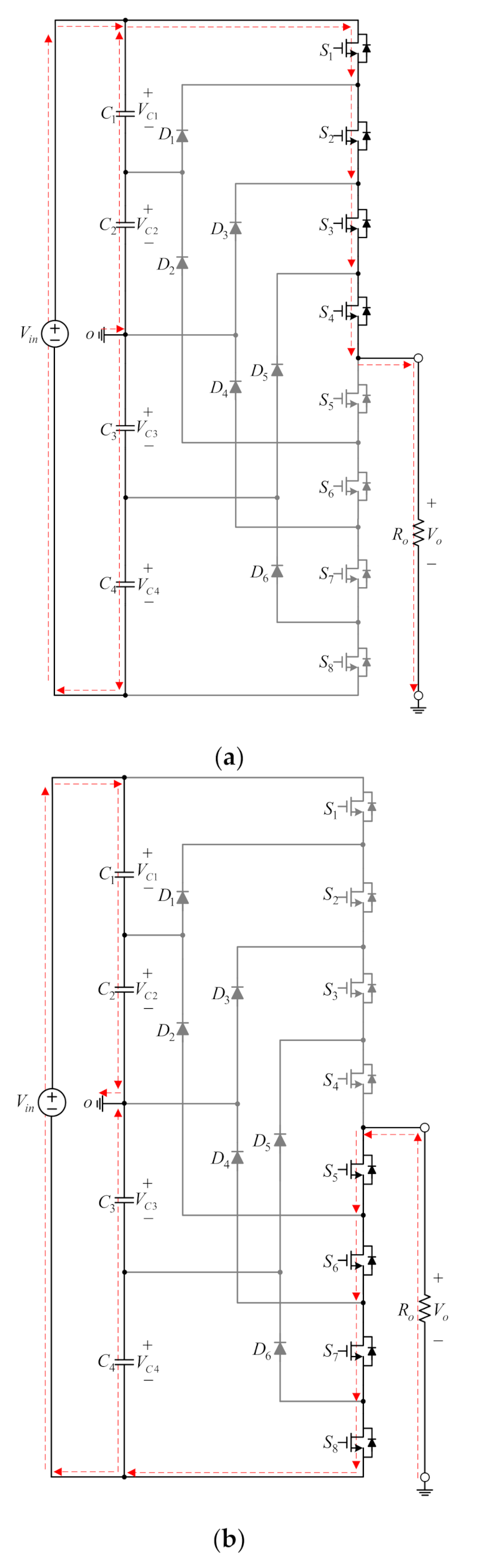

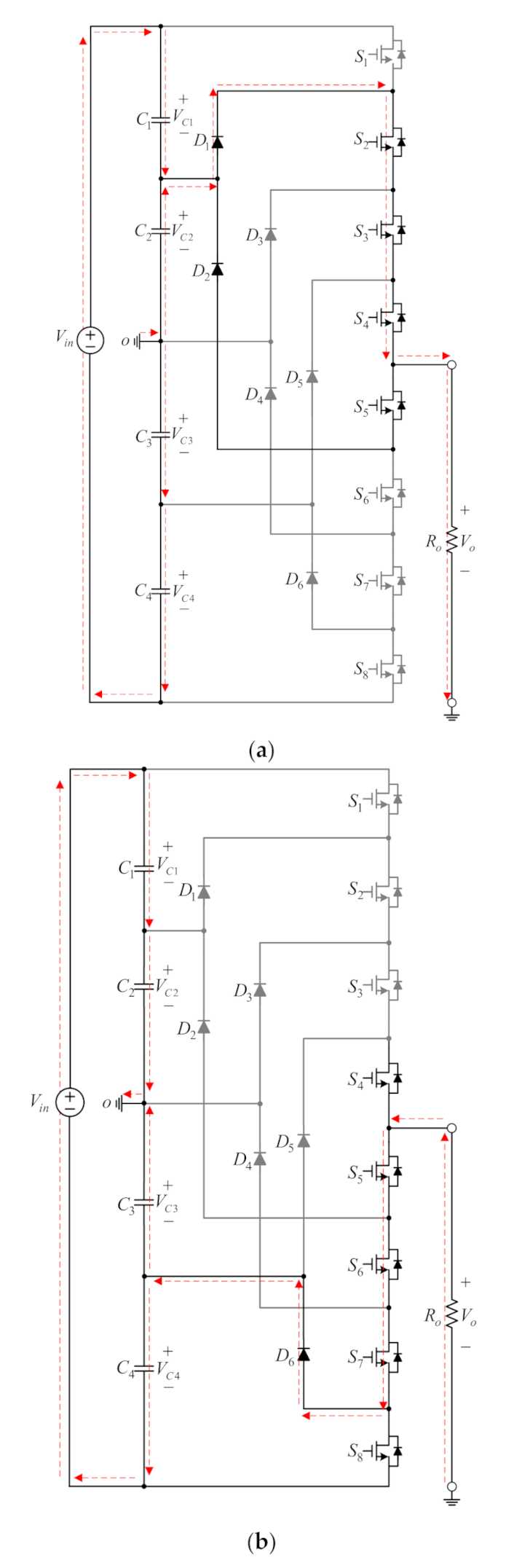

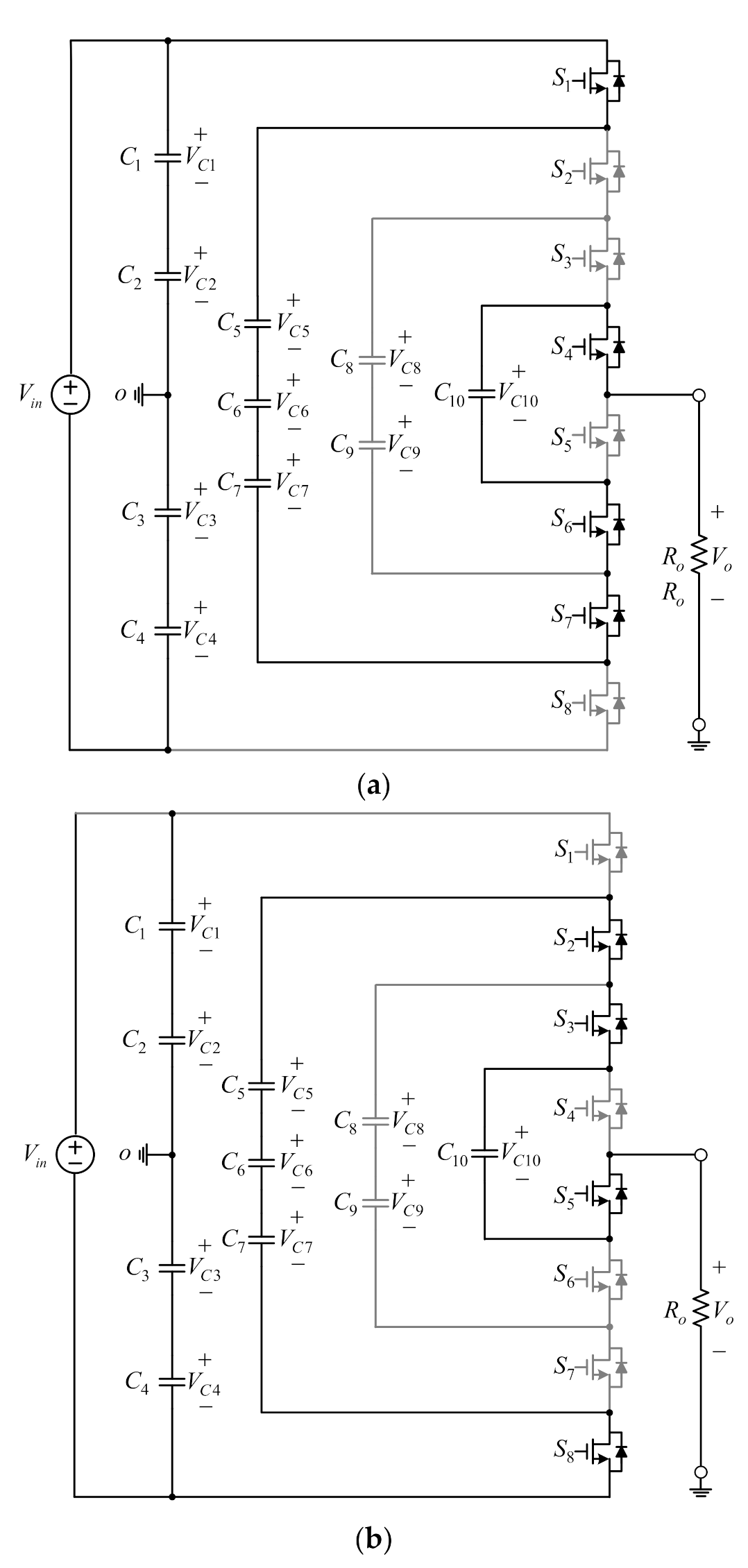

2.1. Neutral Point Clamped Inverter

2.2. Flywheel Capacitor Inverter

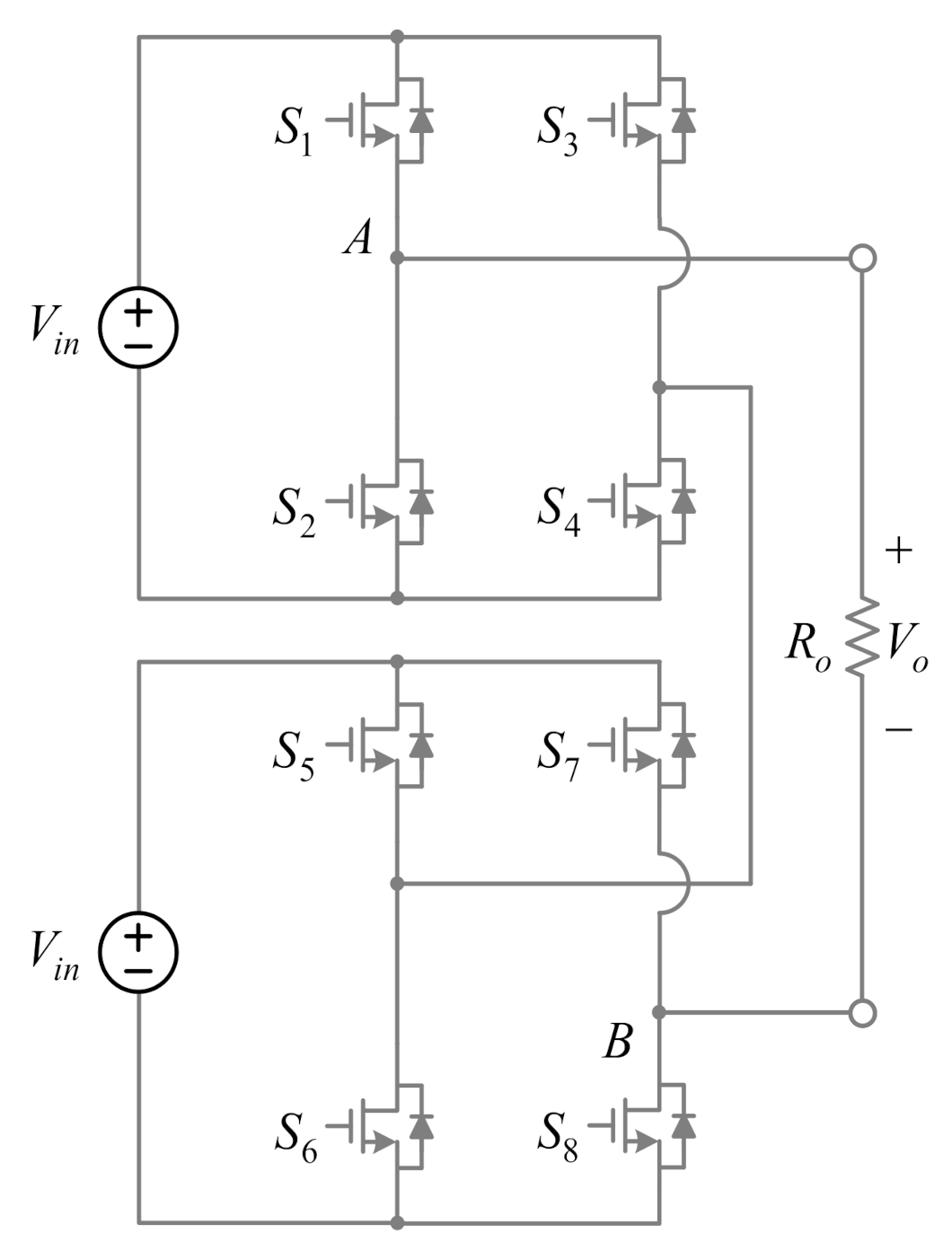

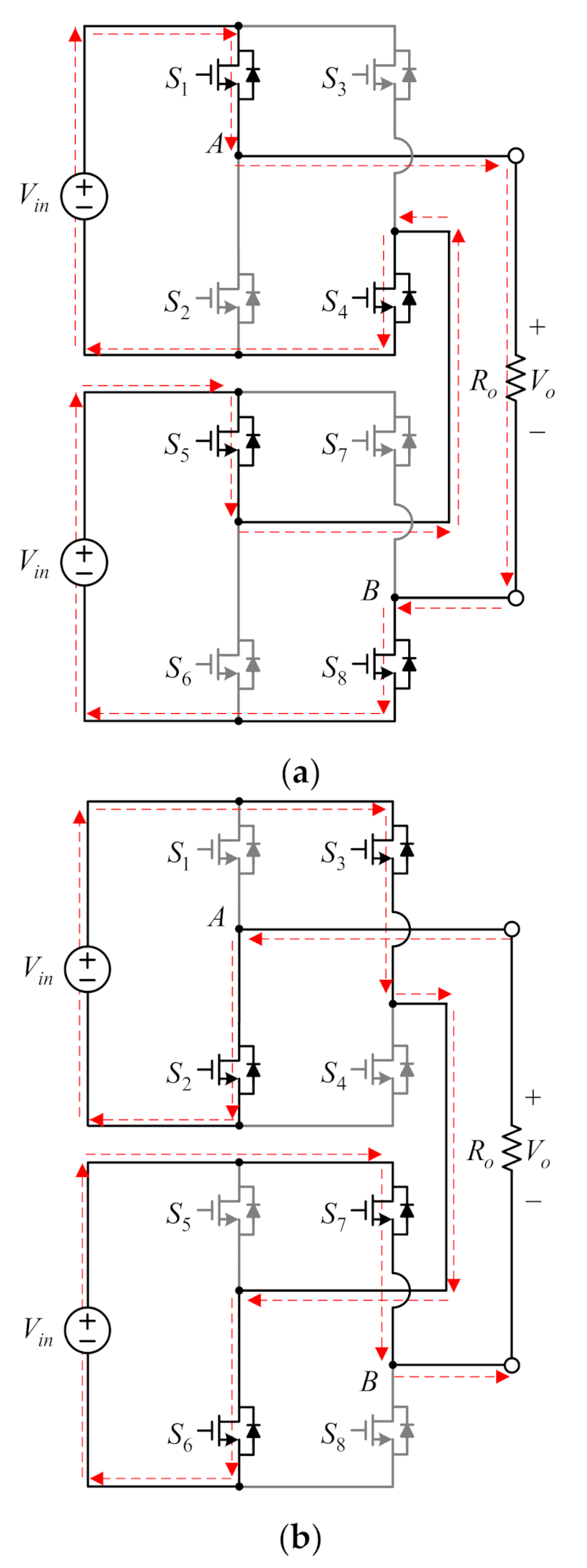

2.3. Series-Connected-Based Inverter

3. State of Recent Works

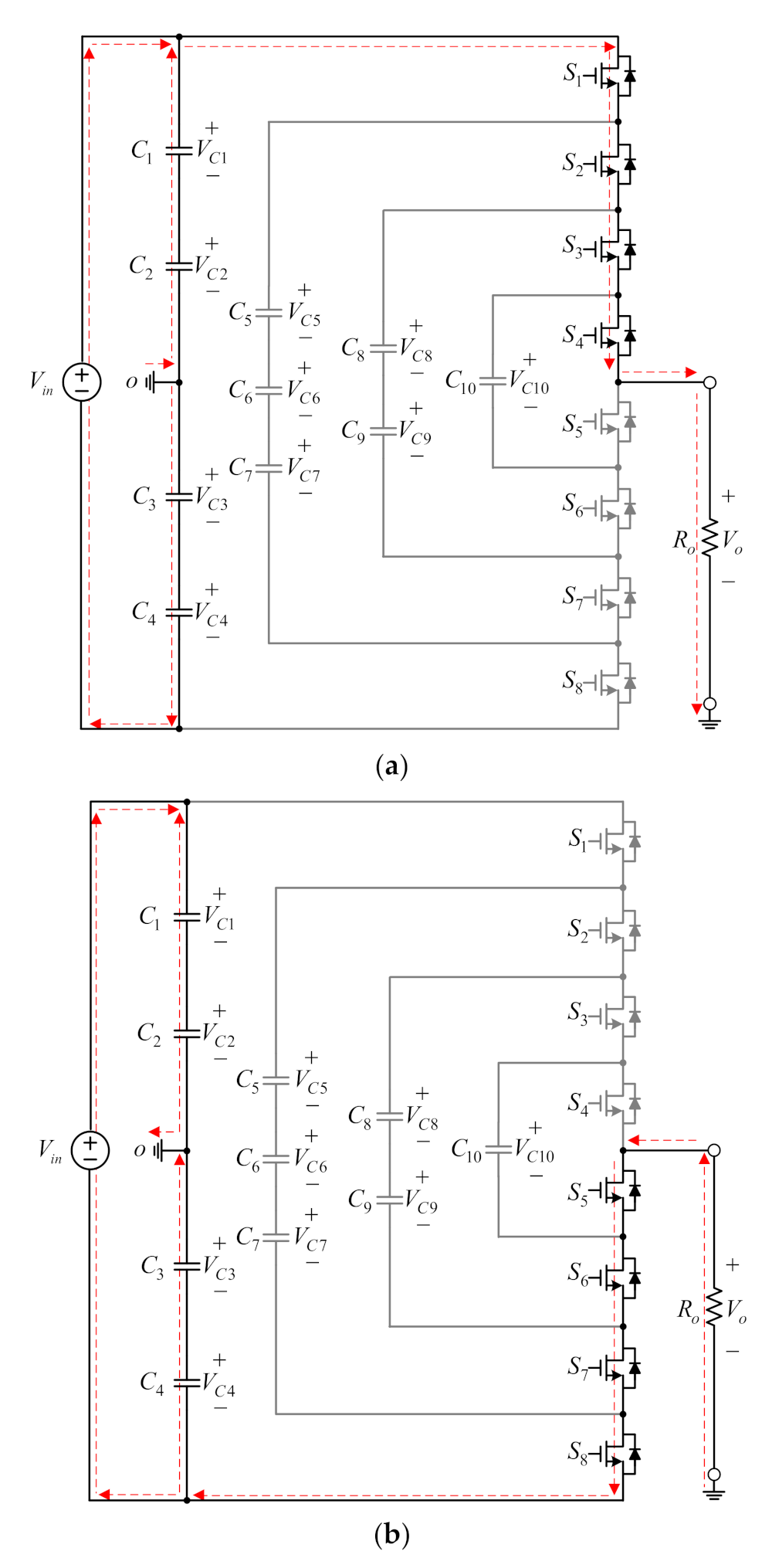

3.1. Series-Connected-Based MLIs

3.2. Flywheel-Capacitor-Based MLIs

3.3. ANPC-Based MLIs

3.3.1. Switched-Capacitor-Based MLIs

3.3.2. T-Type

3.3.3. F-Type

3.3.4. K-Type

3.3.5. Class-D-Type

3.4. Diode-Clamped

3.5. Comparison of the Recent Proposed MLIs

4. Puzzles

- (1)

- THD reduction and circuit symmetry, along with two-end output and self-balancing ability, should be investigated simultaneously. As a result, not only the interchangeability of mass production but also linear control can be easily achieved. Two-end output exhibits improved linearity, as the even harmonics of the switching frequency are very effectively suppressed in a perfectly symmetrical structure. Another advantage of a balanced configuration is that the supply voltage can be halved [53].

- (2)

- At present, there is no standard of the input voltage. Therefore, by taking 12 V as a base, a multiple of this base to obtain 24 V, 48 V, and 96 V, depending on customer needs.

- (3)

- Some special structures can reduce the number of switches, but they cannot be extended to the N-level.

- (4)

- Modeling and advanced control should be developed. To control the switching power converter, modeling is quite important, although there are numerous variations in analysis and measurement from the perspective of theory and implementation, respectively [54]. There are many strategies presented for modeling of the DC-DC converter, for example, the well-known state-space averaging method. However, very few examples of modeling of the multilevel DC-AC inverter can be found in the literature, and only open-loop waveforms are demonstrated in many studies. That is to say, transient responses are not taken into account. Consequently, modeling of the multilevel inverter and design of the closed-loop controller should be investigated.

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Sen, P.; Jha, V.; Sahoo, A.K. Inrush current minimization in reduced device count multilevel inverter interfacing PV system. In Proceedings of the IEEE International Conference on Energy, Power and Environment: Towards Clean Energy Technologies, Shillong, Meghalaya, India, 5–7 March 2021; pp. 1–6. [Google Scholar]

- Wang, Y.; Shi, W.W.; Xie, N.; Wang, C.M. Diode-free T-type three-level neutral-point-clamped inverter for low-voltage renewable energy system. IEEE Trans. Ind. Electron. 2014, 61, 6168–6174. [Google Scholar] [CrossRef]

- Dhanamjayulu, C.; Khasim, S.R.; Padmanaban, S.; Arunkumar, G.; Holm-Nielsen, J.B.; Blaabjerg, F. Design and implementation of multilevel inverters for fuel cell energy conversion system. IEEE Access 2020, 8, 183690–183707. [Google Scholar] [CrossRef]

- Benedetti, D.; Agnelli, J.; Gagliardi, A.; Dini, P.; Saponara, S. Design of an off-grid photovoltaic carport for a full electric vehicle recharging. In Proceedings of the IEEE EEEIC/I&CPS Europe’20, Madrid, Spain, 9–12 June 2020; pp. 1–6. [Google Scholar]

- Dini, P.; Saponara, S. Electro-thermal model-based design of bidirectional on-board chargers in hybrid and full electric vehicles. Electronics 2022, 11, 112. [Google Scholar] [CrossRef]

- Rasool, H.; Verbrugge, B.; Zhaksylyk, A.; Tran, T.M.; El Baghdadi, M.; Geury, T.; Hegazy, O. Design optimization and electrothermal modeling of an off-board charging system for electric bus applications. IEEE Access 2021, 9, 84501–84519. [Google Scholar] [CrossRef]

- Vratislav, M. Three-level PWM floating H-bridge sinewave power inverter for high-voltage and high-efficiency applications. IEEE Trans. Power Electron. 2016, 31, 4065–4074. [Google Scholar]

- Maki, K.; Sbragio, R.; Vlahopoulos, N. System design of a wind turbine using a multi-level optimization approach. Renew. Energy 2012, 43, 101–110. [Google Scholar] [CrossRef]

- Wu, F.; Li, X.; Feng, F.; Gooi, H.B. Modified cascaded multilevel grid-connected inverter to enhance European efficiency and several extended topologies. IEEE Trans. Ind. Inform. 2015, 11, 1358–1365. [Google Scholar] [CrossRef]

- Choi, U.-M.; Lee, J.-S. Single-phase five-level IT-type NPC inverter with improved efficiency and reliability in photovoltaic systems. IEEE J. Emerg. Sel. Top. Power Electron. 2022, 10, 5226–5239. [Google Scholar] [CrossRef]

- Anjali Krishna, R.; Suresh, L.P. A brief review on multilevel inverter topologies. In Proceedings of the International Conference on Circuit, Power and Computing Technologies [ICCPCT], Nagercoil, India, 18–19 March 2016; pp. 1–6. [Google Scholar]

- Arbune, P.A.; Gaikwad, A. Comparative study of three level and five level inverter. Int. J. Adv. Res. Electr. Electron. Instrum. Eng. 2016, 5, 681–686. [Google Scholar]

- Rodriguez, J.; Lai, J.-S.; Peng, F.Z. Multilevel inverters: A survey of topologies, controls, and applications. IEEE Trans. Ind. Electron. 2002, 49, 724–738. [Google Scholar] [CrossRef] [Green Version]

- Wang, K.; Zheng, Z.; Li, Y.; Liu, K.; Shang, J. Neutral-point potential balancing of a five-level active neutral-point-clamped inverter. IEEE Trans. Ind. Electron. 2013, 60, 1907–1918. [Google Scholar] [CrossRef]

- Nabae, A.; Takahashi, I.; Akagi, H. A new neutral-point-clamped PWM inverter. IEEE Trans. Ind. Appl. 1981, IA-17, 518–523. [Google Scholar] [CrossRef]

- Sato, Y.; Natori, K. Design consideration of flying capacitor multilevel inverters using SiC MOSFETs. In Proceedings of the International Power Electronics Conference, Niigata, Japan, 20–24 May 2018; pp. 1860–1865. [Google Scholar]

- Naderi, R.; Sadigh, A.K.; Smedley, K.M. Dual flying capacitor active-neutral-point-clamped multilevel converter. IEEE Trans. Power Electron. 2016, 31, 6476–6484. [Google Scholar] [CrossRef]

- Rabinovici, R.; Baimel, D.; Tomasik, J.; Zuckerberger, A. Generic phase shifted PWM algorithm for thirteen level cascaded H-bridge NPC inverter. In Proceedings of the IEEE 26th Convention of Electrical and Electronics Engineers, Eilat, Israel, 17–20 November 2010; pp. 315–319. [Google Scholar]

- Babaei, E.; Laali, S.; Alilu, S. Cascaded multilevel inverter with series connection of novel H-bridge basic units. IEEE Trans. Ind. Electron. 2014, 61, 6664–6671. [Google Scholar] [CrossRef]

- Rao, B.N.; Suresh, Y. A novel single source multilevel inverter with hybrid switching technique. Int. J. Circuit Theory Appl. 2021, 50, 794–811. [Google Scholar]

- Barah, S.S.; Behera, S. An optimize configuration of H-bridge multilevel inverter. In Proceedings of the 1st International Conference on Power Electronics and Energy (ICPEE), Bhubaneswar, India, 2–3 January 2021; pp. 1–4. [Google Scholar]

- Kumar, N.K.; Muthyala, U.R.; Dhabale, A. Optimized multilevel inverters derived from generalized asymmetrical topology. In Proceedings of the IEEE 4th International Future Energy Electronics Conference (IFEEC), Singapore, 25–28 November 2019; pp. 1–6. [Google Scholar]

- Ye, M.; Wei, Q.; Li, S.; Ren, W.; Song, G. Research on balance control strategy of single capacitor clamped. IET Power Electron. 2021, 14, 280–289. [Google Scholar] [CrossRef]

- Missula, J.V.; Adda, R.; Tripathy, P. Averaged modeling and SRF-based closed-loop control of single-phase ANPC inverter. IEEE Trans. Power Electron. 2021, 36, 13839–13854. [Google Scholar] [CrossRef]

- Sun, R.; Wang, X.; Ye, Y. Seventeen-level inverter based on switched-capacitor and flying-capacitor-fed T-type unit. IEEE Access 2022, 10, 33561–33570. [Google Scholar] [CrossRef]

- Chen, S.; Ye, Y.; Wang, X. Hybrid 17-level inverters based on T-type flying-capacitor and switched-capacitor. Int. J. Circuit Theory Appl. 2021, 50, 886–903. [Google Scholar] [CrossRef]

- Lee, S.S.; Yang, Y.; Siwakoti, Y.P. A novel single-stage five-level common-ground-boost-type active neutral-point-clamped 5L-CGBT-ANPC inverter. IEEE Trans. Power Electron. 2021, 36, 6192–6196. [Google Scholar] [CrossRef]

- Zhang, L.; Lou, X.; Li, C.; Wu, F.; Gu, Y.; Chen, G.; Xu, D. Evaluation of different Si SiC hybrid three-level active NPC inverters for high power density. IEEE Trans. Power Electron. 2020, 35, 8224–8236. [Google Scholar] [CrossRef]

- Lee, S.S.; Lim, C.S.; Lee, K.-B. Novel active-neutral-point-clamped inverters with improved voltage-boosting capability. IEEE Trans. Power Electron. 2020, 35, 5978–5986. [Google Scholar] [CrossRef]

- Yarlagadda, A.K.; Verma, V. Seven-level triple boost self-balanced switched-capacitor inverter. Int. J. Circuit Theory Appl. 2022, 1–17. [Google Scholar] [CrossRef]

- Naik, B.S.; Suresh, Y.; Venkataramanaiah, J. Experimental verification of a hybrid multilevel inverter with voltage-boosting ability. Int. J. Circuit Theory Appl. 2020, 48, 420–434. [Google Scholar] [CrossRef]

- Ye, Y.; Zhangm, G.; Wangm, X.; Yi, Y.; Cheng, K.W.E. Self-balanced switched-capacitor thirteen-level inverters with reduced capacitors count. IEEE Trans. Ind. Electron. 2022, 69, 14827–14837. [Google Scholar] [CrossRef]

- Meraj; Tanzim, S.; Kamrul, H.; Ammar, M. A novel configuration of cross-switched T-type CT-type multilevel inverter. IEEE Trans. On. Power Electron. 2020, 35, 3688–3696. [Google Scholar] [CrossRef]

- Prem, P.; Sugavanam, V.; Abubakar, A.I.; Ali, J.S.M.; Sengodan, B.C.; Krishnasamy, V.; Padmanaban, S. A novel cross-connected multilevel inverter topology for higher number of voltage levels with reduced switch count. Int. Trans. Electr. Energy Syst. 2020, 30, e12381. [Google Scholar] [CrossRef]

- Lee, S.S.; Lee, K.-B. Dual-T-type seven-level boost active-neutral-point-camped inverter. IEEE Trans. Power Electron. 2019, 34, 6031–6035. [Google Scholar] [CrossRef]

- Bogineni, J.; Nakka, J. A novel reduced switch single-phase five-level inverter. Int. J. Circuit Theory Appl. 2022, 50, 2793–2809. [Google Scholar] [CrossRef]

- Sathik, M.J.; Sandeep, N.; Almakhles, D.; Blaabjerg, F. Improved “K” type seven-level switched capacitor inverter topology with self-voltage balancing. Int. J. Circuit Theory Appl. 2020, 48, 1800–1819. [Google Scholar] [CrossRef]

- Zeng, J.; Lin, W.; Cen, D.; Liu, J. Novel K-type multilevel inverter with reduced components and self-balance. IEEE J. Emerg. Sel. Top. Power Electron. 2020, 8, 4343–4354. [Google Scholar] [CrossRef]

- Shieh, J.-J.; Hwu, K.-I.; Li, Y.-Y. A single-voltage-source class-D boost multi-level inverter with self-balanced capacitors. Energies 2022, 15, 4082. [Google Scholar] [CrossRef]

- Shieh, J.-J.; Hwu, K.-I.; Li, Y.-Y. Analysis and modeling of a single-power-source T-Type 7-level single-phase DC-AC inverter with voltage gain of 3. Energies 2022, 15, 7894. [Google Scholar] [CrossRef]

- Stala, R. Natural DC-link voltage balance in a single-phase NPC inverter with four-level legs and novel modulation method. IET Power Electron. 2020, 13, 3764–3776. [Google Scholar] [CrossRef]

- Martinez-Garcia, M.F.; Vazquez-Guzman, G.; Martinez-Rodriguez, P.R.; Escobar, G.; Valdez-Fernandez, A.A.; Sosa-Zuniga, J.M. Step-Up seven-level neutral-point-clamped inverter based topology for TL-PVS. IET Power Electron. 2020, 13, 2847–2853. [Google Scholar]

- Odeh, C.I.; Lewicki, A.; Morawiec, M.; Kondratenko, D. Three-level F-type inverter. IEEE Trans. Power Electron. 2021, 36, 11265–11275. [Google Scholar] [CrossRef]

- Tolbert, L.M.; Habetler, T.G. Novel multi-level inverter carrier based PWM methods. IEEE Trans. Ind. Appl. 1999, 35, 1424–1431. [Google Scholar] [CrossRef] [Green Version]

- Chitra, U.C.; Arun, R. Bus clamping PWM for three level neutral point clamped inverters. In Proceedings of the International Conference on Technological Advancements in Power and Energy (TAP Energy), Kollam, India, 24–26 June 2015; pp. 322–326. [Google Scholar]

- Khluabwannarat, P.; Thammarat, C.; Tadsuan, S.; Bunjongjit, S. An analysis of iron loss supplied by sinusoidal square wave bipolar PWM inverter and unipolar PWM inverter. In Proceedings of the International Power Engineering Conference (IPEC), Singapore, 3–6 December 2007; pp. 1185–1190. [Google Scholar]

- Sarker, R. Phase disposition PWM (PD-PWM) technique to minimize THD from a three-phase NPC multilevel voltage source inverter. In Proceedings of the IEEE International Conference for Convergence in Engineering, Kolkata, India, 5–6 September 2020; pp. 220–224. [Google Scholar]

- Wang, G.; Li, Y.W. Parabolic PWM for current control of voltage-source converters (VSCs). IEEE Trans. Ind. Electron. 2010, 57, 3491–3496. [Google Scholar] [CrossRef]

- Sarkar, I.; Fernandes, B.G. Modified hybrid multi-carrier PWM technique for cascaded H-bridge multilevel inverter. In Proceedings of the 40th Annual Conference of the IEEE Industrial Electronics Society (IECON), Dallas, TX, USA, 29 October–1 November 2014; pp. 4318–4324. [Google Scholar]

- Babkrani, Y.; Naddam, A.; Hayani, S.; Hilal, M.; Fahli, A. Simulation of cascaded H-bridge multilevel inverter with several multicarrier waveforms and implemented with PD, POD and APOD Techniques. In Proceedings of the International Renewable and Sustainable Energy Conference (IRSEC), Tangier, Morocco, 4–7 December 2017; pp. 1–6. [Google Scholar]

- Carrara, G.; Gardella, S.; Marchesoni, M.; Salutar, R.; Sciutto, G. A new multilevel PWM method: A theoretical analysis. IEEE Trans. Power Electron. 1992, 7, 497–505. [Google Scholar] [CrossRef]

- Rai, S.K.; Chaturvedi, P.; Shimi, S.L. SHE-PWM based multilevel T-type inverter topology for single-phase photovoltaic applications. In Proceedings of the IEEE International Conference on Power Electronics, Drives and Energy Systems (PEDES), Trivandrum, India, 14–17 December 2016; pp. 1–4. [Google Scholar]

- Doutreloigne, J. A new mlti-level switching amplifier architecture with improved power efficiency. In Proceedings of the World Congress on Engineering and Computer Science (WCECS), San Francisco, CA, USA, 21–23 October 2015; pp. 1–5. [Google Scholar]

- Erickson, R.W.; Maksimovic, D. Fundamental Power Electronics, 2nd ed.; Electronic Services: Boulder, CO, USA, 2001. [Google Scholar]

| Inverter Type | Level Voltage | S1 | S2 | S3 | S4 | S5 | S6 | S7 | S8 |

|---|---|---|---|---|---|---|---|---|---|

| Diode Clamped | 0.5 Vin | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 |

| 0.25 Vin | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | |

| 0 Vin | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | |

| −0.25 Vin | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | |

| −0.5 Vin | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | |

| Flywheel Capacitor | 0.5 Vin | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 |

| 0.25 Vin | 1 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | |

| 0 Vin | 0 | 1 | 1 | 0 | 1 | 0 | 0 | 1 | |

| 0 Vin | 1 | 0 | 0 | 1 | 0 | 1 | 1 | 0 | |

| −0.25 Vin | 0 | 0 | 1 | 0 | 1 | 0 | 1 | 1 | |

| −0.5 Vin | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | |

| Series-Connected | 2 Vin | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 1 |

| Vin | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |

| −Vin | 0 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | |

| −2 Vin | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 0 |

| [10] | [20] | [21] | [22] | [23] | [24] | |

| Number of Levels | 5 | 9 | 5 | 9 | 5 | 5 |

| Number of Switches | 8 | 10 | 6 | 10 | 6 | 8 |

| Number of Diodes | 2 | 0 | 0 | 0 | 0 | 0 |

| Number of Capacitors | 2 | 4 | 0 | 0 | 1 | 3 |

| Number of Transformers | 0 | 2 | 0 | 0 | 0 | 0 |

| Voltage Gain | 0.78 | 2 | 2 | 4 | 1 | 0.5 |

| Number of DC Power Sources | 1 | 1 | 2 | 4 | 1 | 1 |

| End of Output | two | two | two | two | two | two |

| Rated Load Power (W) | 1000 | --- | --- | --- | 25 | 300 |

| Input Voltage (V) | 400 | 50 | --- | --- | 24 | 128 |

| Peak Output Voltage (V) | 311 | 100 | --- | --- | 21.6 | 64 |

| Rated Load THD (%) | --- | 12.50 | 17.66 | 8.90 | 33.27 | 3.86 |

| Peak Efficiency (%) | 97.09 | 95.77 | --- | --- | 95.21 | --- |

| Control Strategy | UP-PWM/ OLC-PWM | PD-PWM/ TPCS | PD-PWM | PD-PWM | PS-PWM | PS-PWM/ PD-PWM |

| Modeling | x | x | x | x | x | v |

| Feedback Controller Design | x | x | x | x | x | v |

| [25] | [26] | [27] | [28] | [30] | [31] | |

| Number of Levels | 17 | 17 | 5 | 11 | 7 | 9 |

| Number of Switches | 9 | 11 | 7 | 12 | 10 | 11 |

| Number of Diodes | 2 | 0 | 0 | 0 | 1 | 0 |

| Number of Capacitors | 4 | 2 | 2 | 3 | 3 | 2 |

| Number of Transformers | 0 | 0 | 0 | 0 | 0 | 0 |

| Voltage Gain | 2 | 2 | 10 | 2.5 | 3 | 2 |

| Number of DC Power Sources | 1 | 1 | 1 | 1 | 1 | 1 |

| End of Output | two | two | single | single | two | two |

| Rated Load Power (W) | 480 | 480 | 400 | 500 | 60 | 330 |

| Input Voltage (V) | 160 | 160 | 40 | 100 | 30 | 50 |

| Peak Output Voltage (V) | 320 | 320 | 400 | 250 | 84.5 | 100 |

| Rated Load THD (%) | --- | 6.96 | 35.11 | --- | 5.30 | 13.51 |

| Peak Efficiency (%) | 98.36 | 97.80 | 97.50 | 96.67 | 97.61 | 97.30 |

| Control Strategy | APOD-PWM | AOD-PWM | SPWM | SPWM | LS-PWM | PD-PWM |

| Modeling | x | x | x | x | x | x |

| Feedback Controller Design | x | x | x | x | x | x |

| [32] | [33] | [34] | [35] | [36] | [37] | |

| Number of Levels | 13 | 9 | 25 | 7 | 5 | 7 |

| Number of Switches | 10 | 10 | 12 | 10 | 6 | 8 |

| Number of Diodes | 2 | 0 | 0 | 0 | 0 | 5 |

| Number of Capacitors | 4 | 4 | 4 | 4 | 2 | 3 |

| Number of Transformers | 0 | 0 | 0 | 0 | 0 | 0 |

| Voltage Gain | 6 | 2 | --- | 1.5 | 1 | 1.5 |

| Number of DC Power Sources | 1 | 2 | 2 | 1 | 1 | 1 |

| End of Output | two | two | two | single | two | two |

| Rated Load Power (W) | 500 | --- | 370 | 130 | 1250 | 1500 |

| Input Voltage (V) | 60 | 60 | 10 V + 50 V | 100 | 350 | 200 |

| Peak Output Voltage (V) | 360 | 120 | 60 | 150 | 350 | 300 |

| Rated Load THD (%) | --- | 9.36 | 3.26 | --- | 1.55 | --- |

| Peak Efficiency (%) | 97.32 | 98.94 | --- | 98.20 | 98.70 | 96.60 |

| Control Strategy | PD-PWM/ | SHE-PWM | PD-PWM | SHE-PWM | PD-PWM | PD-PWM |

| Modeling | x | x | x | x | x | x |

| Feedback Controller Design | x | x | x | x | x | x |

| [38] | [39] | [40] | [41] | [42] | ||

| Number of Levels | 13 | 7 | 7 | 7 | 7 | |

| Number of Switches | 14 | 12 | 10 | 12 | 8 | |

| Number of Diodes | 0 | 8 | 6 | 8 | 6 | |

| Number of Capacitors | 3 | 4 | 4 | 3 | 4 | |

| Number of Transformers | 0 | 0 | 0 | 0 | 0 | |

| Voltage Gain | 1.5 | 3 | 3 | 1 | 1.5 | |

| Number of DC Power Sources | 1 | 1 | 1 | 1 | 1 | |

| End of Output | two | two | two | two | one | |

| Rated-load Power (W) | 1000 | 300 | 300 | 1200 | 100 | |

| Input Voltage (V) | 260 | 56 | 56 | 400 | 180 | |

| Peak Output Voltage (V) | 390 | 168 | 168 | 400 | 270 | |

| Rated Load THD (%) | 5.30 | 2.75 | 3.36 | --- | 21.09 | |

| Peak Efficiency (%) | 96.80 | 97.90 | 97.42 | 96.80 | 95.39 | |

| Control Strategy | PD-PWM | LS-SPWM | LS-SPWM | SPWM | LS-PWM | |

| Modeling | x | x | v | x | x | |

| Feedback Controller Design | x | x | v | x | x | |

| Number | Abbreviation | Full Name |

|---|---|---|

| 1 | SPWM | Sinusoidal Pulse Width Modulation [44] |

| 2 | OLC-PWM | One-Leg Clamping-PWM [45] |

| 3 | UP-PWM | Unipolar-PWM [46] |

| 4 | PD-PWM | Phase Disposition-PWM [47] |

| 5 | TPCS | Triangle and Parabolic Carrier Signals [48] |

| 6 | PS-PWM | Phase-Shifted-PWM [49] |

| 7 | APOD-PWM | Alternate Opposition Disposition-PWM [50] |

| 8 | LS-PWM | Level-Shifted-PWM [51] |

| 9 | SHE-PWM | Selected Harmonic Elimination-PWM [52] |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Shieh, J.-J.; Hwu, K.-I.; Chen, S.-J. Perspective of Voltage-Fed Single-Phase Multilevel DC-AC Inverters. Energies 2023, 16, 898. https://doi.org/10.3390/en16020898

Shieh J-J, Hwu K-I, Chen S-J. Perspective of Voltage-Fed Single-Phase Multilevel DC-AC Inverters. Energies. 2023; 16(2):898. https://doi.org/10.3390/en16020898

Chicago/Turabian StyleShieh, Jenn-Jong, Kuo-Ing Hwu, and Sheng-Ju Chen. 2023. "Perspective of Voltage-Fed Single-Phase Multilevel DC-AC Inverters" Energies 16, no. 2: 898. https://doi.org/10.3390/en16020898