A Design and Validation of 400 W PV Emulator Using Simple Equivalent Circuit for PV Power System Test

Abstract

:1. Introduction

2. Characteristics and Equivalent Circuit of a PV Cell

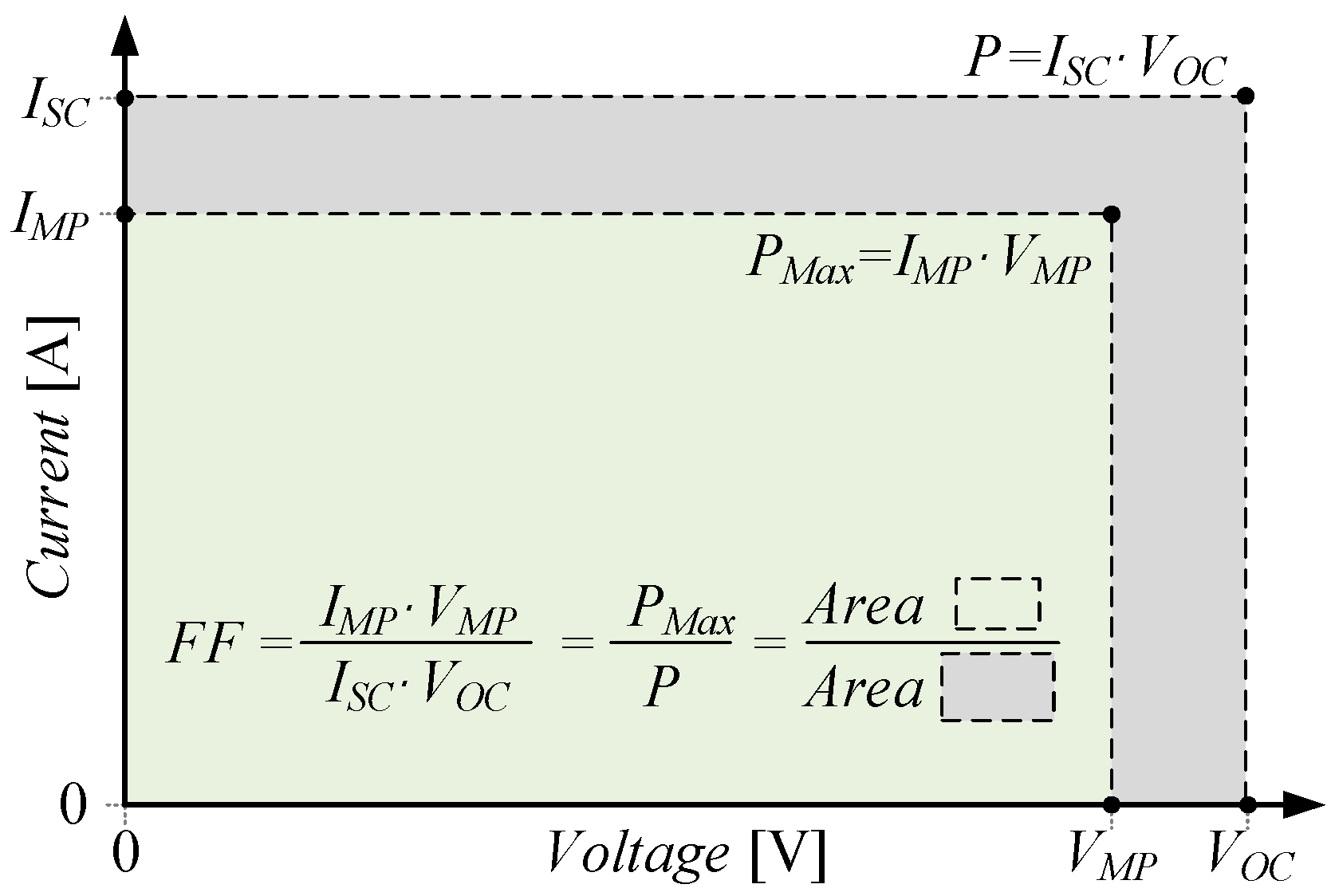

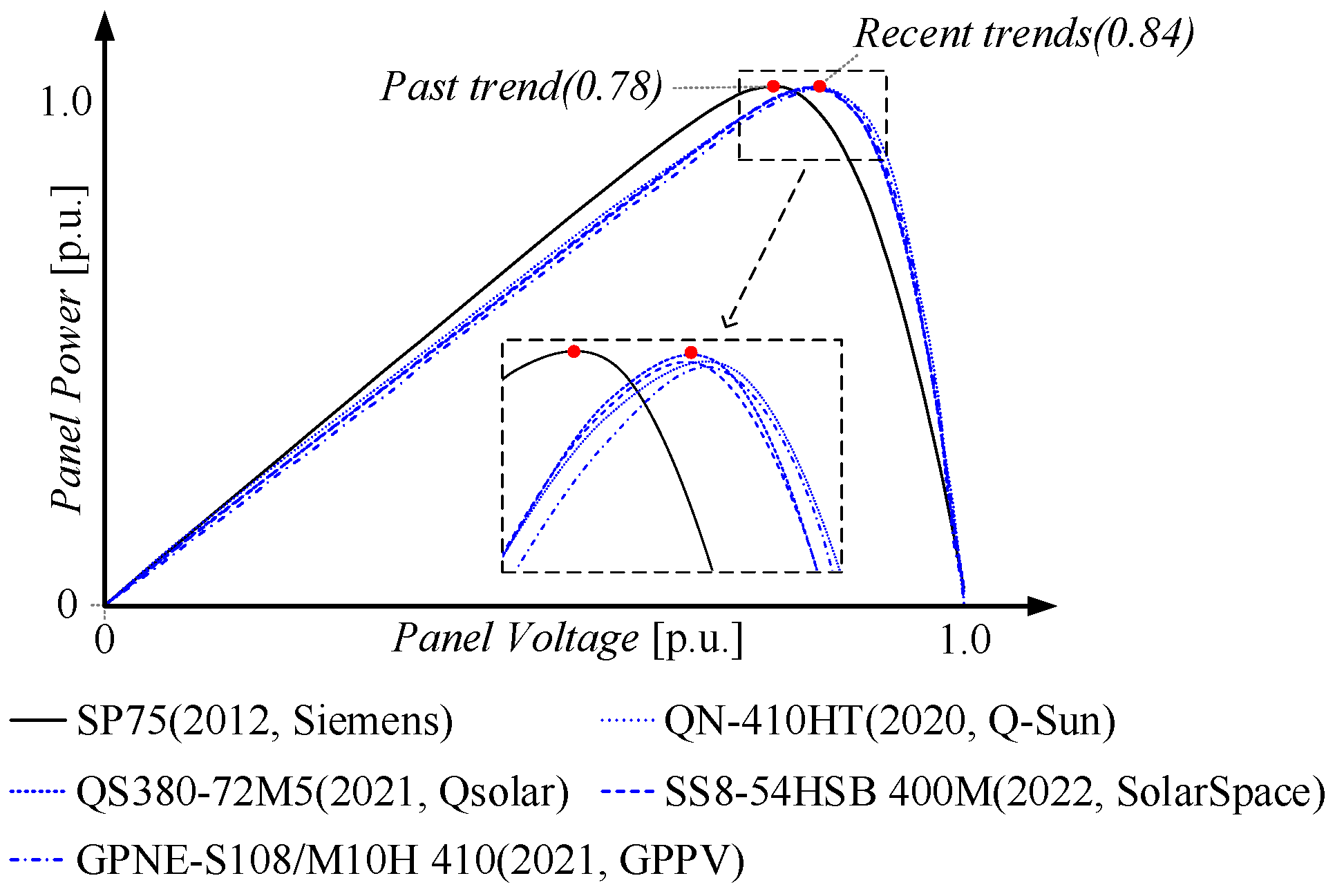

2.1. Characteristics of a PV Cell

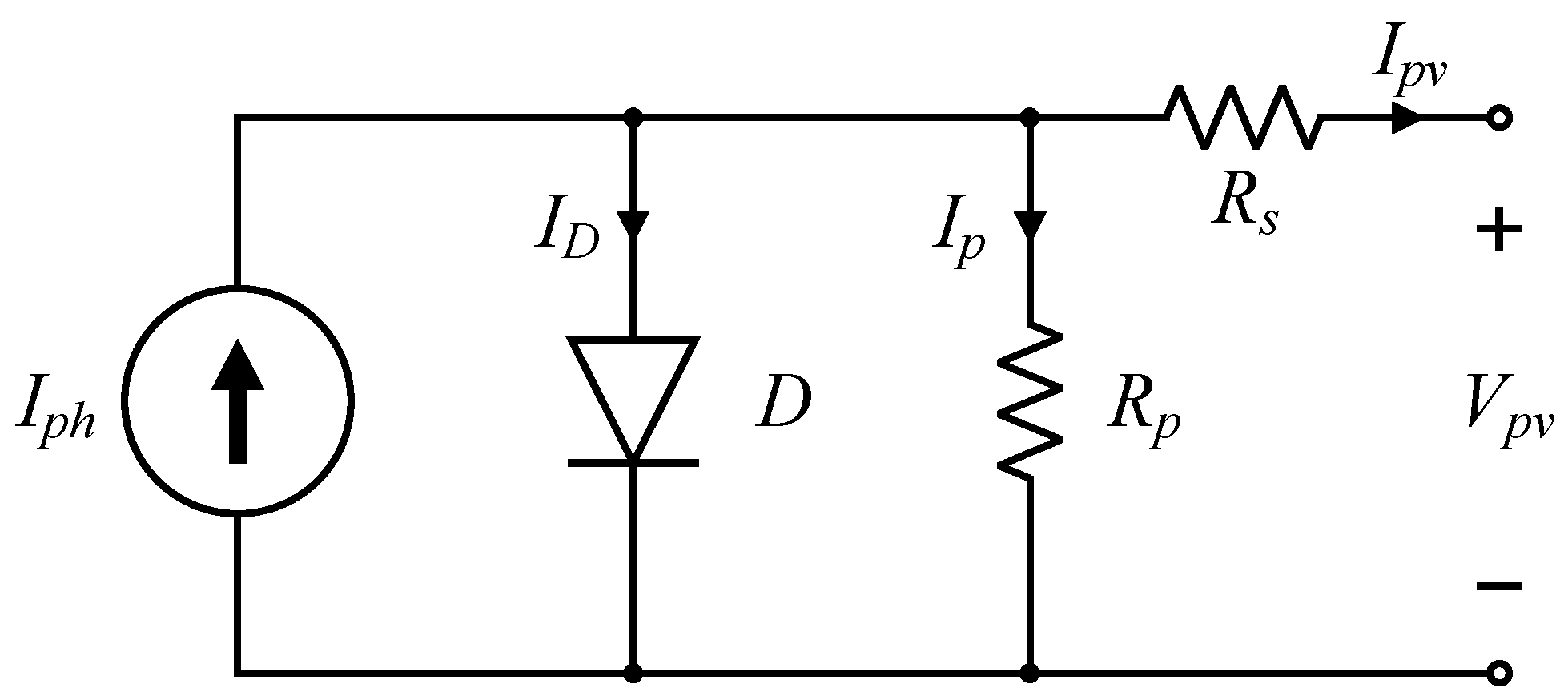

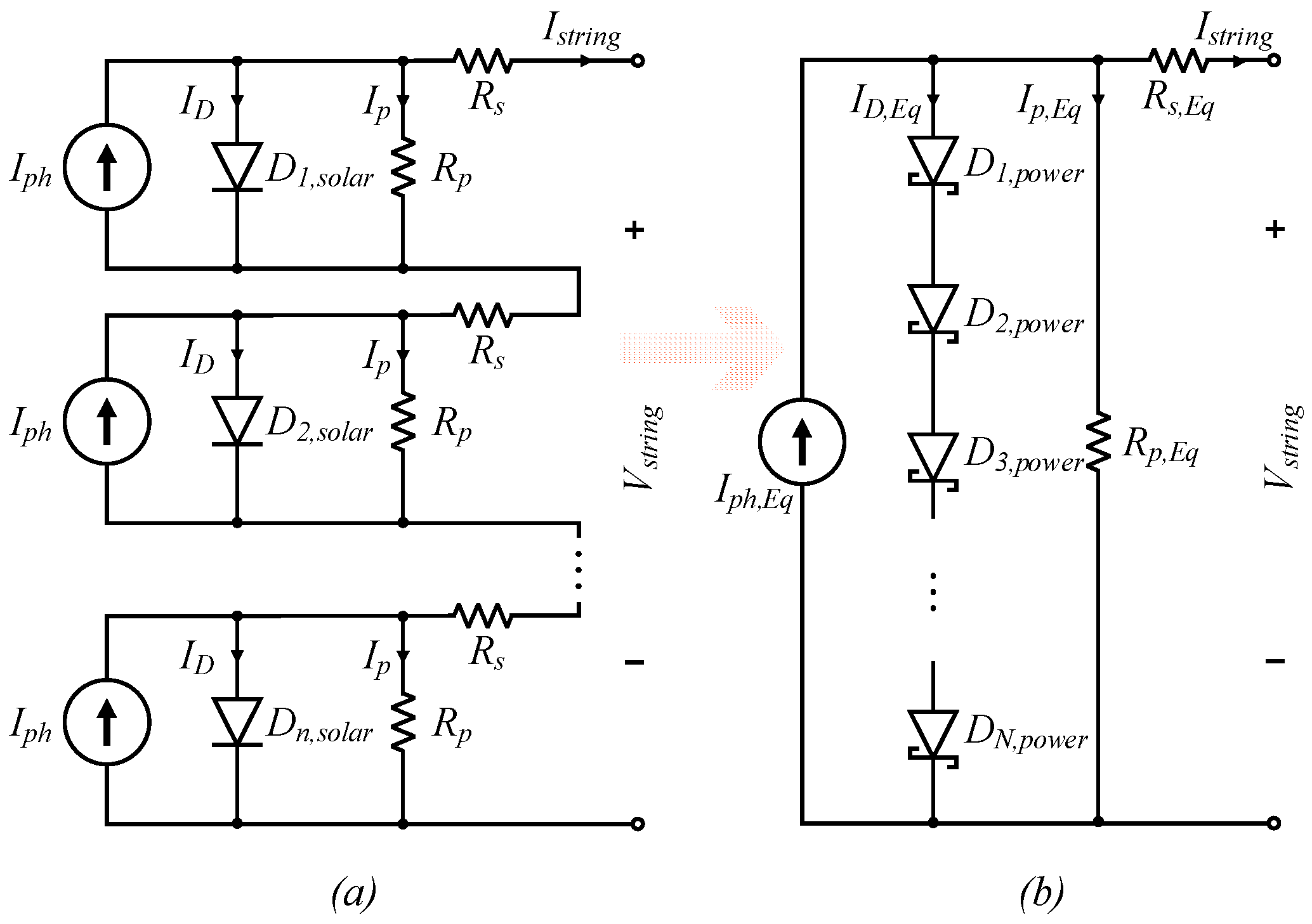

2.2. Equivalent Circuit Model of a PV Cell

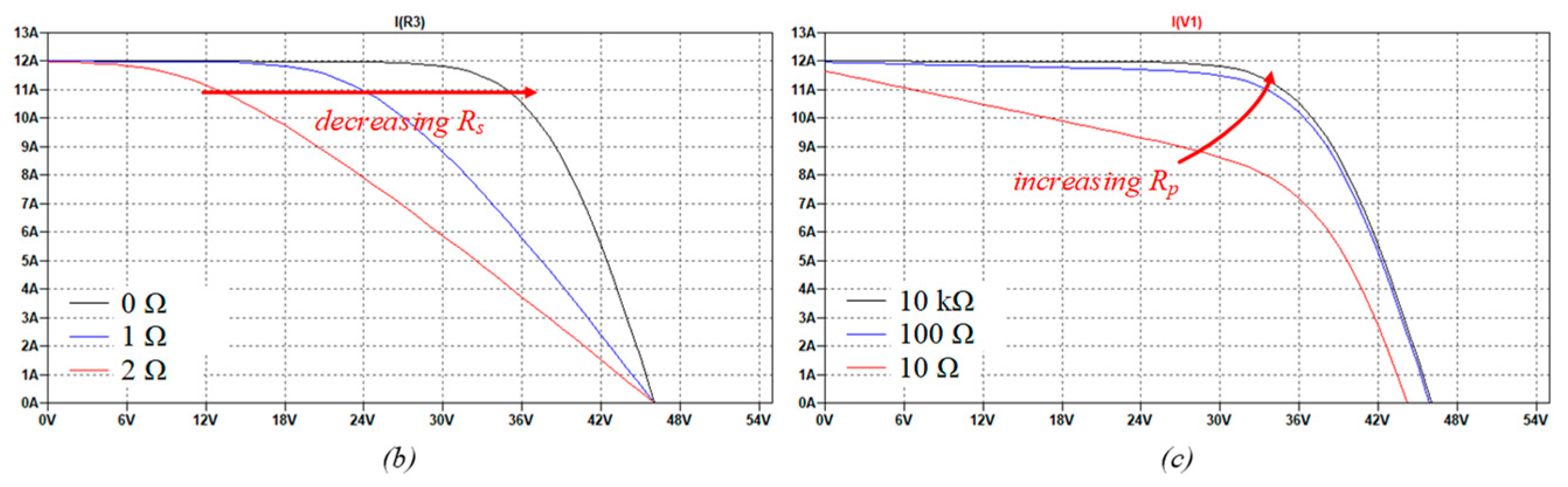

2.3. Impact of Rs and Rp on PVE

3. Hardware Design of PVE

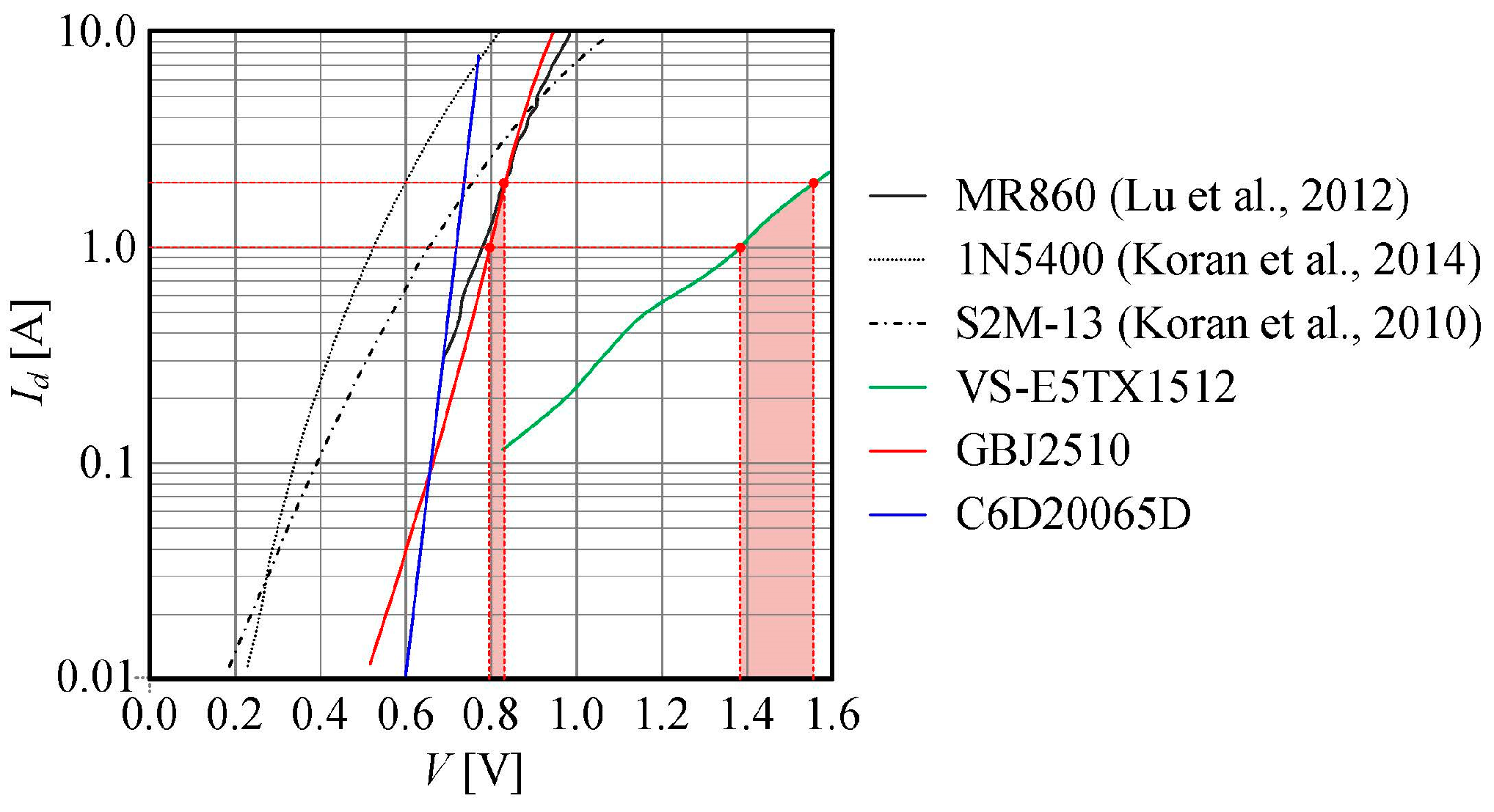

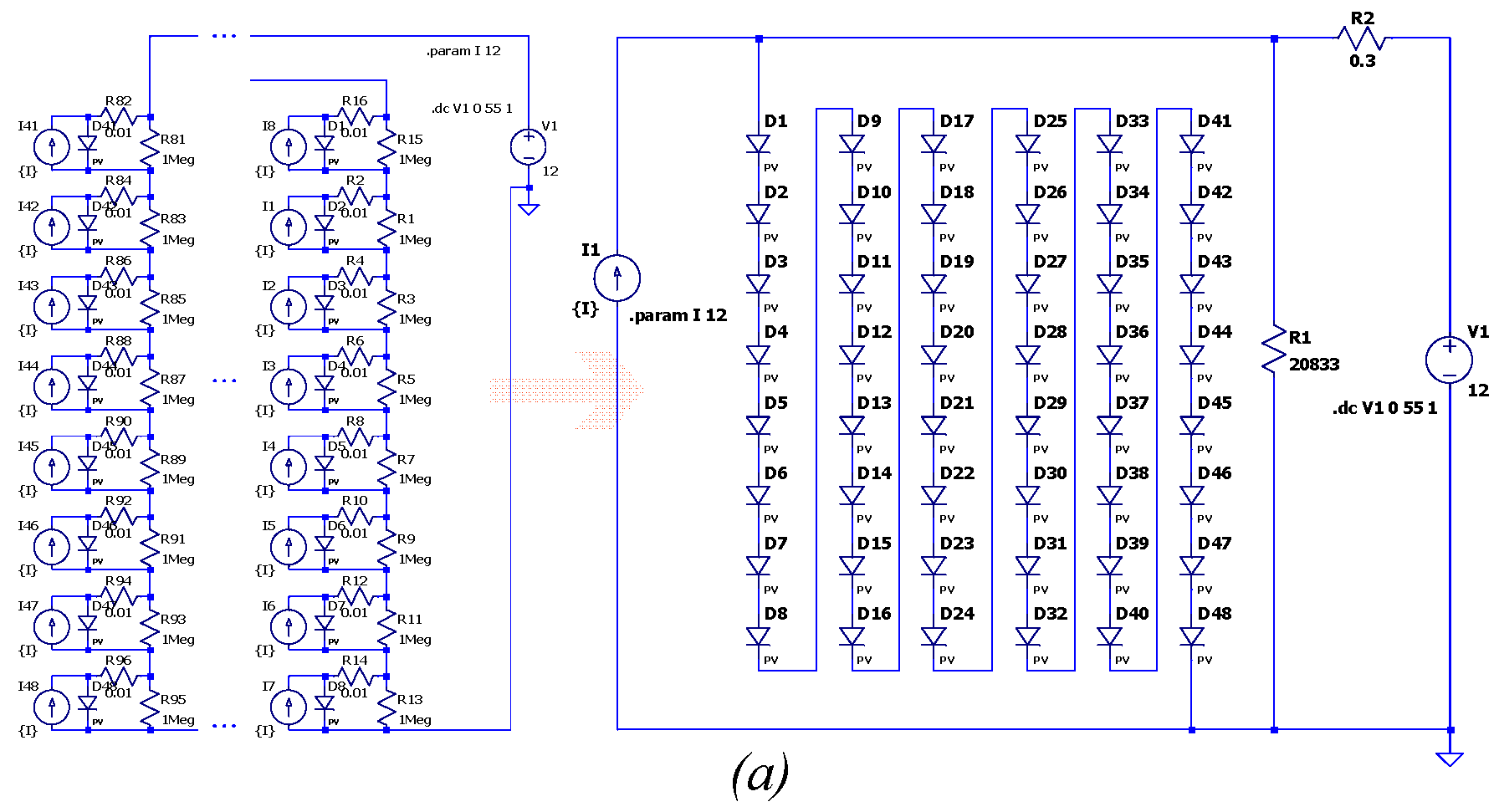

3.1. Diode Selection for PVE

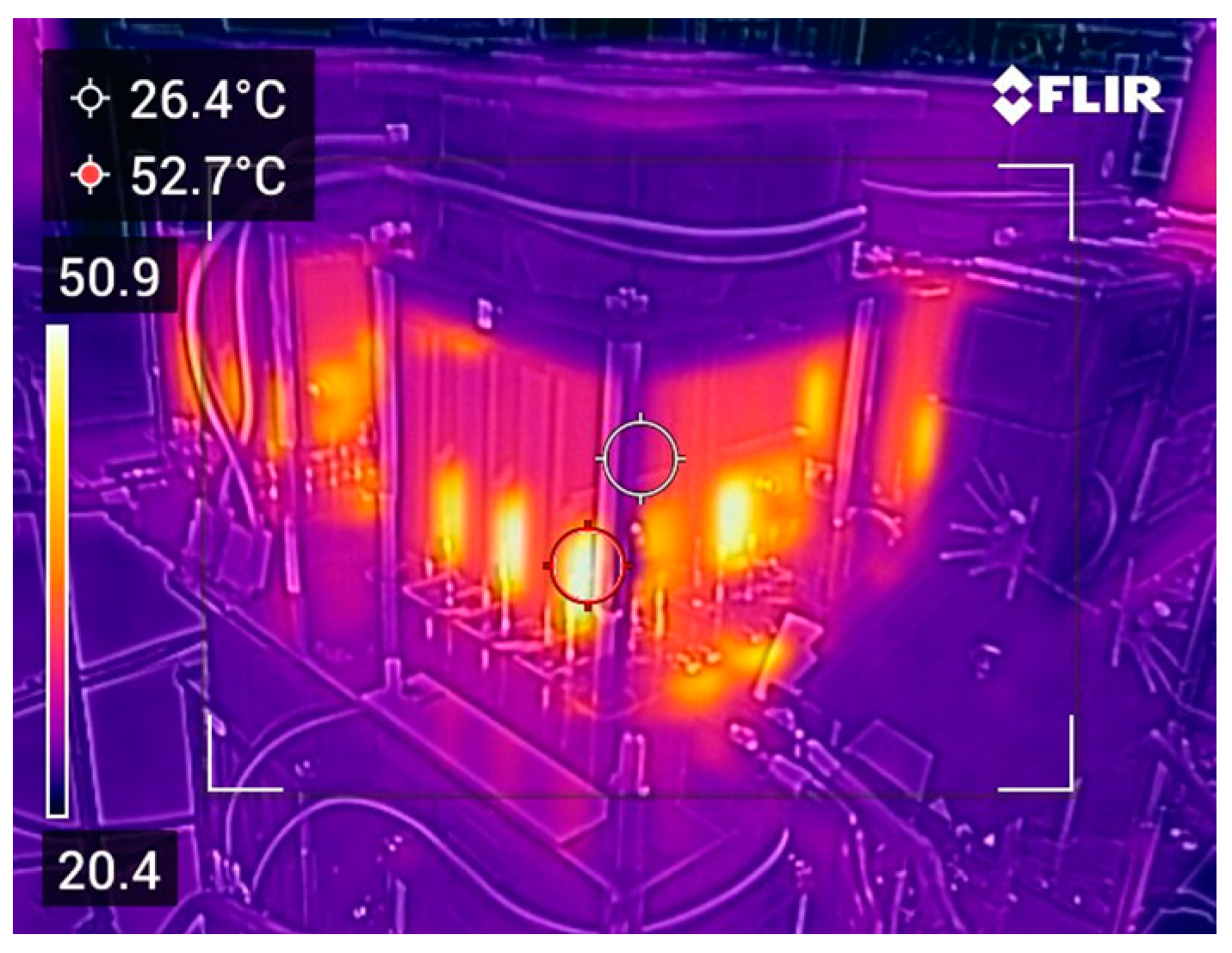

3.2. Thermal Design

3.3. Simulation Configuration and Results

3.4. Hardware Implementation of the 400 W PVE

4. Experiment Results

4.1. Experiment Configuration of Proposed PVE

4.2. Effect of Additional Rs on I–V and P–V Curves

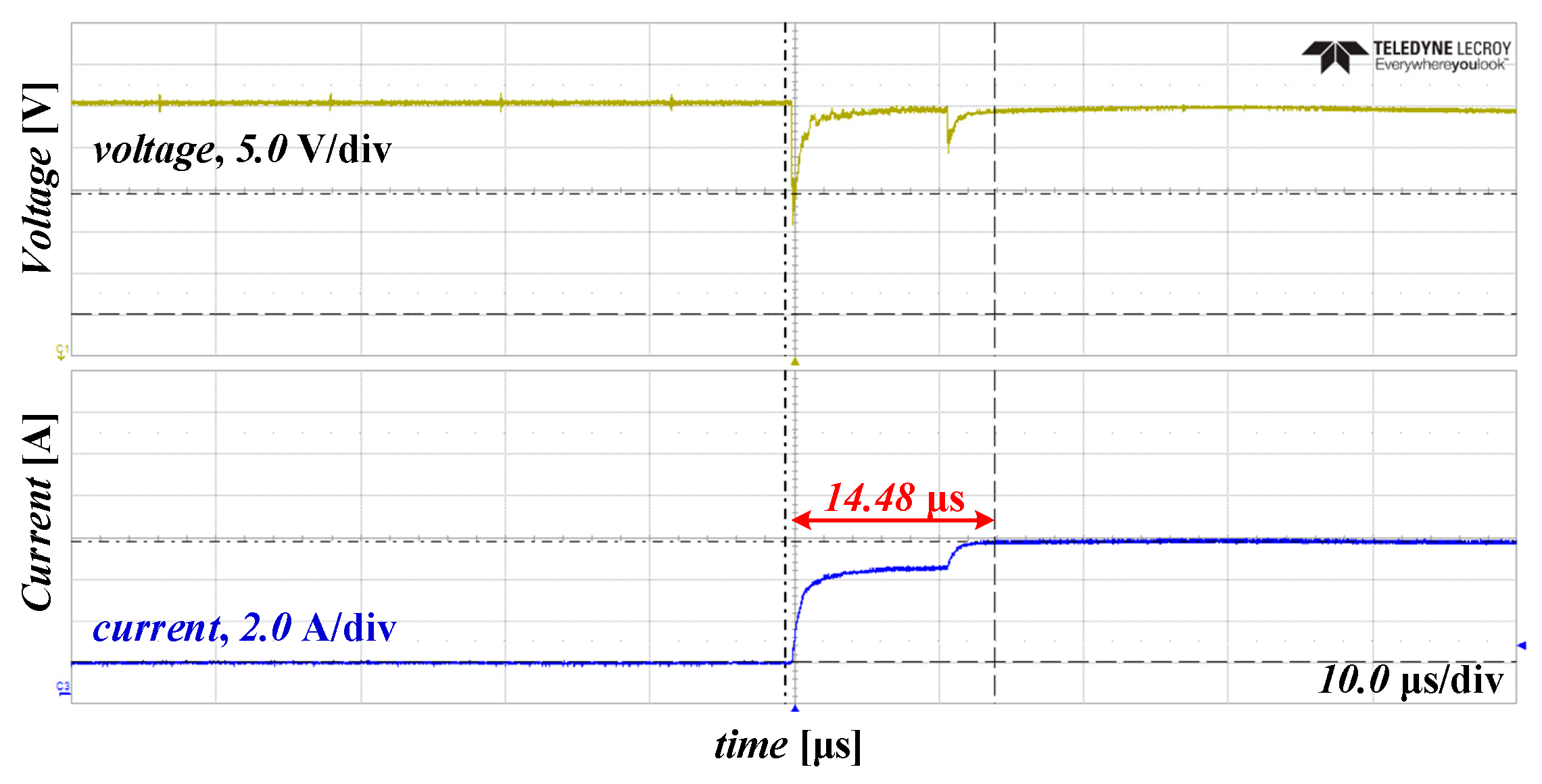

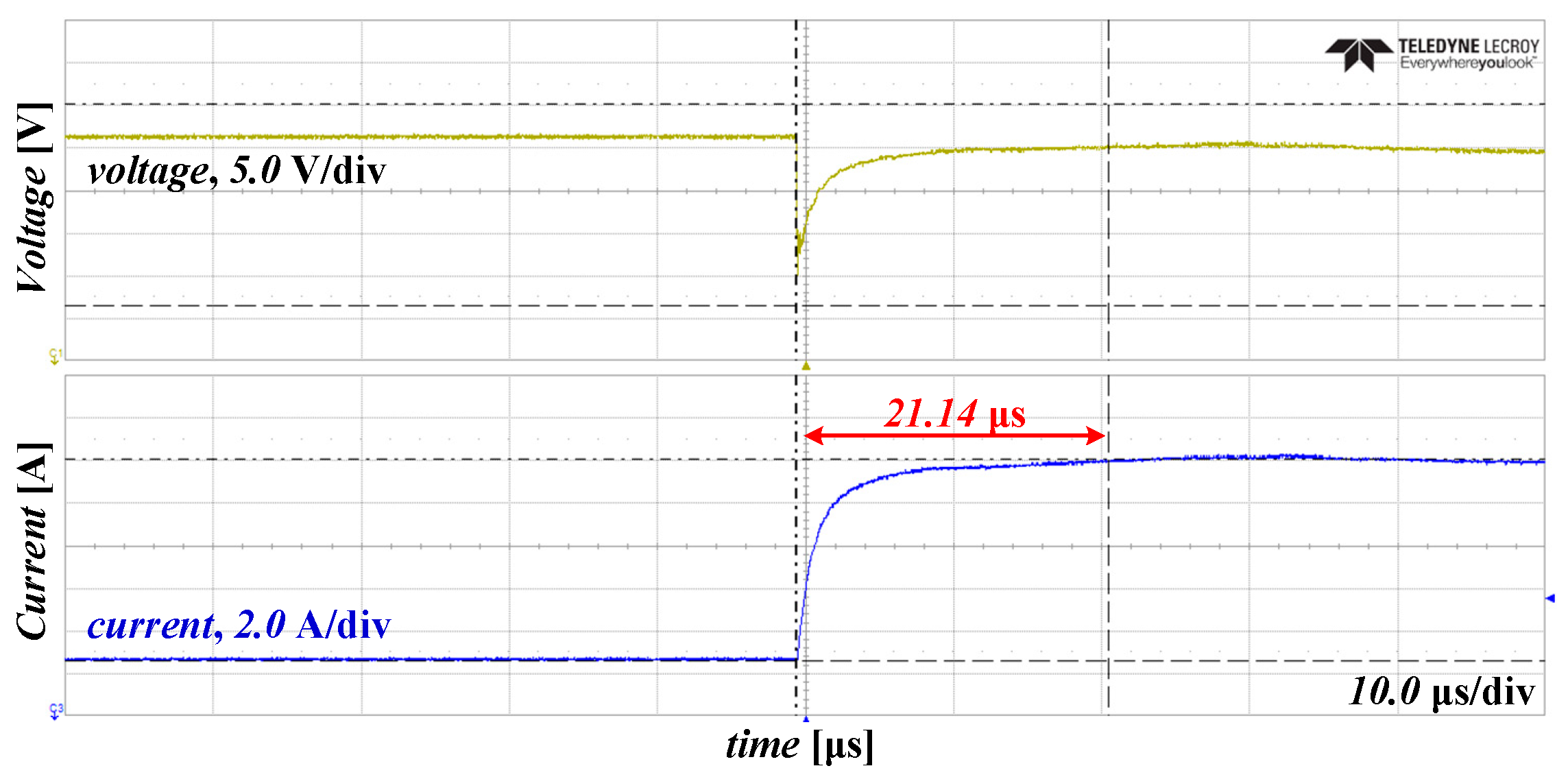

4.3. Dynamic Response

4.3.1. Experiment Results of Step Changes in the Resistive Load

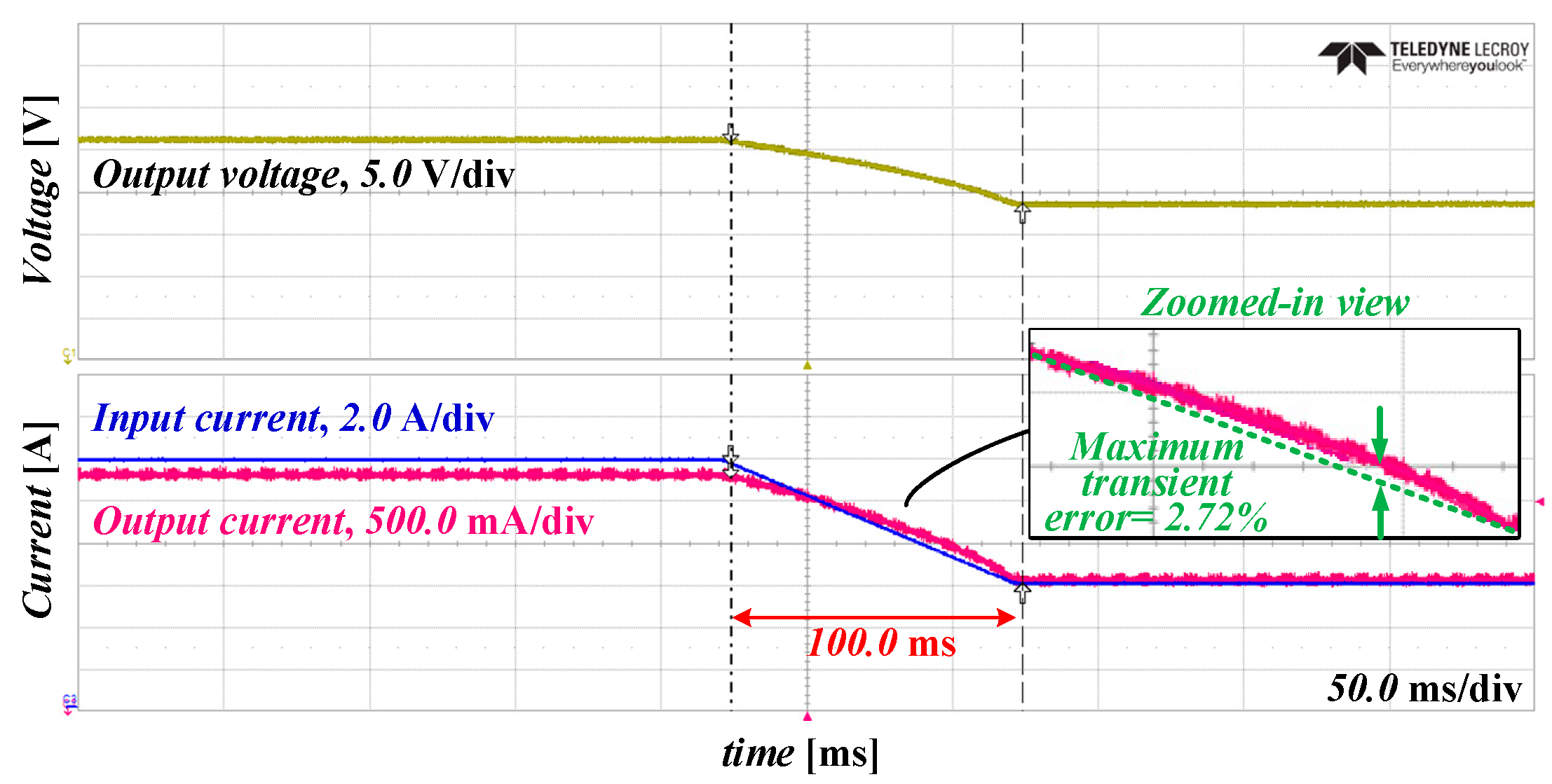

4.3.2. Experiment Results of Dynamic Response in Input Current

4.4. Efficiency of PVE

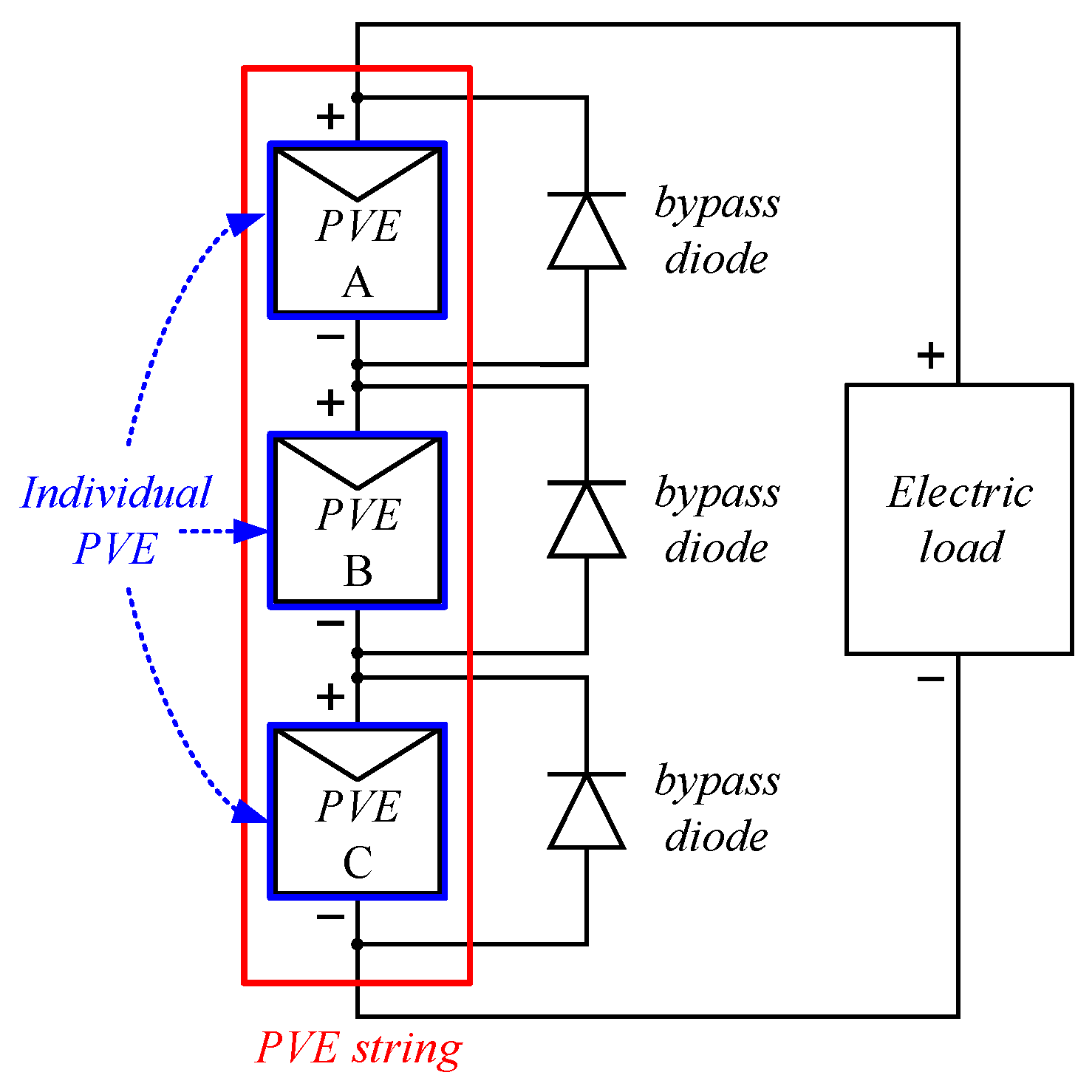

4.5. Verification of Partial Shading Operation through Multiple Series Connections

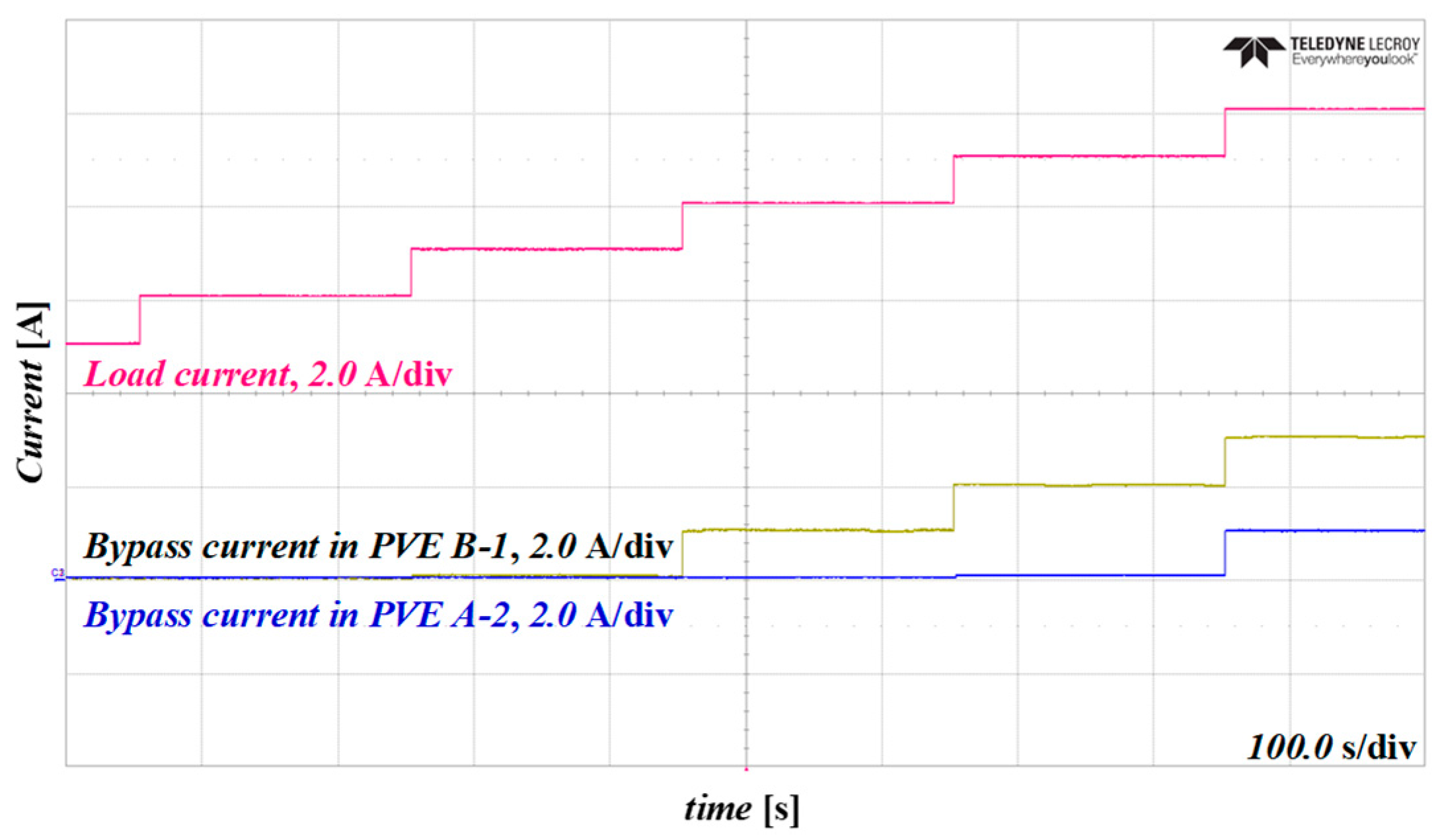

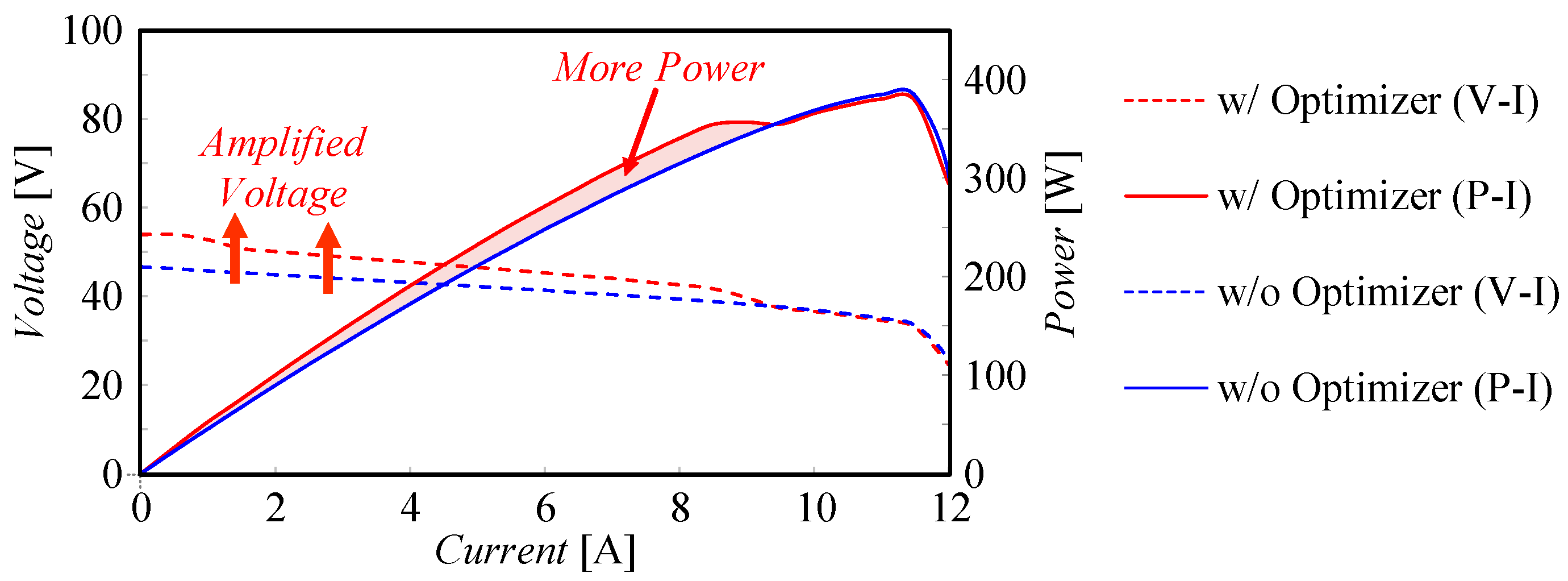

4.6. Integrated Operation with the Power Optimizer

4.7. Comparative Investigation with Commercial PVEs

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Koran, A.; Sano, K.; Kim, R.-Y.; Lai, J.-S. Design of a photovoltaic simulator with a novel reference signal generator and two-stage LC output filter. IEEE Trans. Power Electron. 2010, 25, 1331–1338. [Google Scholar] [CrossRef]

- Koutroulis, E.; Kalaitzakis, K.; Voulgaris, N.C. Development of a microcontroller-based, Photovoltaic Maximum Power Point Tracking Control System. IEEE Trans. Power Electron. 2001, 16, 46–54. [Google Scholar] [CrossRef]

- Huang, Y.; Shen, M.; Peng, F.Z.; Wang, J. Z-source inverter for residential photovoltaic systems. IEEE Trans. Power Electron. 2006, 21, 1776–1782. [Google Scholar] [CrossRef]

- Chen, Y.; Smedley, K.M. A cost-effective single-stage inverter with Maximum Power Point tracking. IEEE Trans. Power Electron. 2004, 19, 1289–1294. [Google Scholar] [CrossRef]

- Quan, L.; Wolfs, P. A review of the Single Phase Photovoltaic Module Integrated Converter topologies with three different DC link configurations. IEEE Trans. Power Electron. 2008, 23, 1320–1333. [Google Scholar] [CrossRef]

- Padmanaban, S.; Priyadarshi, N.; Bhaskar, M.S.; Holm-Nielsen, J.B.; Hossain, E.; Azam, F. A hybrid photovoltaic-fuel cell for grid integration with Jaya-based Maximum Power Point Tracking: Experimental Performance Evaluation. IEEE Access 2019, 7, 82978–82990. [Google Scholar] [CrossRef]

- Mehrjerdi, H. Modeling, integration, and optimal selection of the turbine technology in the hybrid wind-photovoltaic renewable energy system design. Energy Convers. Manag. 2020, 205, 112350. [Google Scholar] [CrossRef]

- Nagamine, F.; Shimokawa, R.; Suzuki, M.; Abe, T. New Solar Simulator for Multi-Junction Solar Cell Measurements. In Proceedings of the Conference Record of the Twenty Third IEEE Photovoltaic Specialists Conference, Louisville, KY, USA, 10–14 May 1993; pp. 686–690. [Google Scholar]

- Techajunta, S.; Chirarattananon, S.; Exell, R.H.B. Experiments in a solar simulator on solid desiccant regeneration and air dehumidification for air conditioning in a tropical humid climate. Renew. Energy 1999, 17, 549–568. [Google Scholar] [CrossRef]

- Chang, C.-H.; Lin, C.; Ku, C.-W. A High Efficiency Solar Array Simulator Implemented by an LLC Resonant DC/DC Converter. In Proceedings of the 2010 International Power Electronics Conference—ECCE ASIA, Sapporo, Japan, 21–24 June 2010; pp. 2603–2609. [Google Scholar]

- Zhang, W.; Kimball, J.W. DC-DC Converter Based Photovoltaic Simulator with a Double Current Mode Controller. In Proceedings of the 2016 IEEE Power and Energy Conference at Illinois (PECI), Urbana, IL, USA, 19–20 February 2016; pp. 1–6. [Google Scholar]

- Zeng, Q.; Song, P.; Chang, L. A Photovoltaic Simulator Based on DC Chopper. In Proceedings of the IEEE CCECE2002 Canadian Conference on Electrical and Computer Engineering, Halifax, NS, Canada, 18–20 September 2022; pp. 257–261. [Google Scholar]

- Koran, A.; LaBella, T.; Lai, J.-S. High efficiency photovoltaic source simulator with fast response time for Solar Power Conditioning Systems Evaluation. IEEE Trans. Power Electron. 2014, 29, 1285–1297. [Google Scholar] [CrossRef]

- Lu, D.D.C.; Nguyen, Q.N. A photovoltaic panel emulator using a Buck-Boost DC/DC converter and a low cost micro-controller. Sol. Energy 2012, 86, 1477–1484. [Google Scholar] [CrossRef]

- Kang, F.-s.; Park, S.-J.; Cho, S.E.; Kim, J.-M. Photovoltaic Power Interface Circuit incorporated with a Buck-boost converter and a full-bridge inverter. Appl. Energy 2005, 82, 266–283. [Google Scholar] [CrossRef]

- Mokhlis, M.; Ferfra, M.; Vall, H.A.; Idrissi, R.E.; Ahmed, C.C.; Taouni, A. Design and Hardware Implementation of Backstepping Controller Dedicated to the Photovoltaic Emulator. In Proceedings of the 5th International Conference on Renewable Energies for Developing Countries (REDEC), Marrakech, Morocco, 29–30 June 2020; pp. 1–6. [Google Scholar]

- Balahewa, I.; Tennakoon, S.; Perera, H.; Kumarawadu, S. A Novel Hybrid Control Strategy with Gain Scheduling for Photovoltaic Emulators. In Proceedings of the 2022 IEEE Electrical Power and Energy Conference (EPEC), Online, 5–7 December 2022; pp. 267–272. [Google Scholar]

- Alaoui, M.; Maker, H.; Mouhsen, A. A New PV Source Emulator Based on Modified Hybrid Referencing Technique with Nonlinear Lyapunov Controller. In Proceedings of the 2020 1st International Conference on Innovative Research in Applied Science Engineering and Technology (IRASET), Meknes, Morocco, 16–19 April 2020; pp. 1–6. [Google Scholar]

- Ramyar, A.; Avestruz, A.-T. Reconfigurable photovoltaic emulator for differential diffusion charge redistribution solar modules. IEEE Open J. Ind. Appl. 2021, 2, 36–46. [Google Scholar] [CrossRef]

- Ullah, N.; Nisar, F.; Alahmadi, A.A. Closed loop control of photo voltaic emulator using fractional calculus. IEEE Access 2020, 8, 28880–28887. [Google Scholar] [CrossRef]

- Hassan Hosseini, S.M.; Keymanesh, A.A. Design and construction of photovoltaic simulator based on dual-diode model. Sol. Energy 2016, 137, 594–607. [Google Scholar] [CrossRef]

- Unlu, M.; Camur, S. A Simple Photovoltaic Simulator Based on a One-Diode Equivalent Circuit Model. In Proceedings of the 2017 4th International Conference on Electrical and Electronic Engineering (ICEEE), Ankara, Turkey, 8–10 April 2017; pp. 33–36. [Google Scholar]

- Khawaldeh, H.A.; Aljarajreh, H.; Al-Soeidat, M.; Lu, D.D.-C.; Li, L. Performance Investigation of a PV Emulator Using Current Source and Diode String. In Proceedings of the 2018 26th International Conference on Systems Engineering (ICSEng), Sydney, NSW, Australia, 18–20 December 2018; pp. 1–5. [Google Scholar]

- Khawaldeh, H.A.; Al-Soeidat, M.; Dah-Chuan Lu, D.; Li, L. Fast Photovoltaic Emulator Based on PV-cell Equivalent Circuit Model. In Proceedings of the 2021 IEEE 12th Energy Conversion Congress & Exposition—Asia (ECCE-Asia), Singapore, 24–27 May 2021; pp. 2121–2126. [Google Scholar]

- Votzi, H.; Himmelstoss, F.A.; Ertl, H. Basic Linear-Mode Solar-Cell Simulators. In Proceedings of the 2009 35th Annual Conference of IEEE Industrial Electronics, Porto, Portugal, 3–5 November 2009; pp. 261–265. [Google Scholar]

- Chin, V.J.; Salam, Z.; Ishaque, K. Cell modelling and model parameters estimation techniques for Photovoltaic Simulator Application: A Review. Appl. Energy 2015, 154, 500–519. [Google Scholar] [CrossRef]

- Zhang, C. A SIC-based liquid-cooled electric vehicle traction inverter operating at high ambient temperature. CPSS Trans. Power Electron. Appl. 2022, 7, 160–175. [Google Scholar] [CrossRef]

- Korasiak, P.; Jaglarz, J. A new photovoltaic emulator designed for testing low-power inverters connected to the LV grid. Energies 2022, 15, 2646. [Google Scholar] [CrossRef]

- Villalva, M.G.; Gazoli, J.R.; Filho, E.R. Comprehensive approach to modeling and simulation of photovoltaic arrays. IEEE Trans. Power Electron. 2009, 24, 1198–1208. [Google Scholar] [CrossRef]

- Abbassi, R.; Abbassi, A.; Jemli, M.; Chebbi, S. Identification of unknown parameters of solar cell models: A comprehensive overview of available approaches. Renew. Sustain. Energy Rev. 2018, 90, 453–474. [Google Scholar] [CrossRef]

- Humada, A.M.; Hojabri, M.; Mekhilef, S.; Hamada, H.M. Solar cell parameters extraction based on single and double-diode models: A Review. Renew. Sustain. Energy Rev. 2016, 56, 494–509. [Google Scholar] [CrossRef] [Green Version]

- Farivar, G.; Asaei, B. Photovoltaic Module Single Diode Model Parameters Extraction Based on manufacturer Datasheet Parameters. In Proceedings of the 2010 IEEE International Conference on Power and Energy, Kuala Lampur, Malaysia, 29 November–1 December 2010; pp. 929–934. [Google Scholar]

- Diodes Incorporated. 25A Glass Passivated Bridge Rectifier. GBJ2510 Datasheet. Available online: https://www.diodes.com/assets/Datasheets/ds21221.pdf (accessed on 5 January 2023).

- CUI Devices. Heat Sink. HSE-B20250-045H Datasheet. Available online: https://www.mouser.kr/datasheet/2/670/hse_b20250_045h-1778156.pdf (accessed on 5 January 2023).

- ENF Solar Home Page. Available online: https://www.enfsolar.com/directory/panel (accessed on 5 January 2023).

- Salem, F.; Awadallah, M.A. Detection and assessment of partial shading in photovoltaic arrays. J. Electr. Syst. Inf. Technol. 2016, 3, 23–32. [Google Scholar] [CrossRef]

- Jordan, D.C.; Sekulic, B.; Marion, B.; Kurtz, S.R. Performance and aging of a 20-year-old silicon PV system. IEEE J. Photovolt. 2015, 5, 744–751. [Google Scholar] [CrossRef]

- Babaa, S.E.; Armstrong, M.; Pickert, V. Overview of maximum power point tracking control methods for PV Systems. J. Power Energy Eng. 2014, 2, 59–72. [Google Scholar] [CrossRef]

- Kaeonin, R.; Naetiladdanon, S.; Sangswang, A. A Photovoltaic Simulator Based on Diode Characteristics. In Proceedings of the 2019 7th International Electrical Engineering Congress (iEECON), Hua Hin, Thailand, 6–8 March 2019; pp. 1–4. [Google Scholar]

- Abuagreb, M.; Allehyani, M.; Johnson, B.K. Design and Test of a Combined PV and Battery System Under Multiple Load and Irradiation Conditions. In Proceedings of the 2019 IEEE Power & Energy Society Innovative Smart Grid Technologies Conference (ISGT), Washington, DC, USA, 18–21 February 2019; pp. 1–5. [Google Scholar]

- Abuagreb, M.; Beleed, H.; Johnson, B.K. Energy Management of a Battery Combined with PV Generation. In Proceedings of the 2019 North American Power Symposium (NAPS), Wichita, KS, USA, 13–15 October 2019; pp. 1–6. [Google Scholar]

- TI Application Report, Revised May 2013, AN-2121 SolarMagic™ SM3320-BATT-EV Charge Controller Reference Design. Available online: https://www.ti.com/lit/an/snosb76c/snosb76c.pdf?ts=1674630330288&ref_url= (accessed on 23 January 2023).

- Chroma. Solar Array Simulation. Model 62050H-600S Datasheet. Available online: https://www.testequipmenthq.com/datasheets/CHROMA-62050H-600S-Datasheet.pdf (accessed on 23 January 2023).

- Elektro-Automatik. Photovoltaics Array Simulation, EA-PSI 9000 2U Datasheet. Available online: https://elektroautomatik.com/shop/media/pdf/c3/b5/e7/datasheet_psi9000_2u_en.pdf (accessed on 23 January 2023).

- Sanchis, P.; López, J.; Ursúa, A.; Gubía, E.; Marroyo, L. On the testing, characterization, and evaluation of PV inverters and dynamic MPPT performance under real varying operating conditions. Prog. Photovolt. Res. Appl. 2007, 15, 541–556. [Google Scholar] [CrossRef]

| Electrical Performance Parameters (STC *) | ||||||

|---|---|---|---|---|---|---|

| PMax (W) | 250 | 300 | 400 | 450 | 500 | 600 |

| VMP (V) | 30.7 | 36.5 | 40.8 | 47.8 | 48.6 | 35.0 |

| IMP (A) | 8.1 | 8.2 | 9.8 | 9.4 | 10.2 | 17.0 |

| VOC (V) | 36.9 | 44.7 | 49.4 | 58.5 | 58.9 | 40.0 |

| ISC (A) | 9.0 | 8.9 | 10.4 | 9.7 | 10.8 | 19.0 |

| No. of Cells | 60 | 72 | 72 | 72 | 96 | 120 |

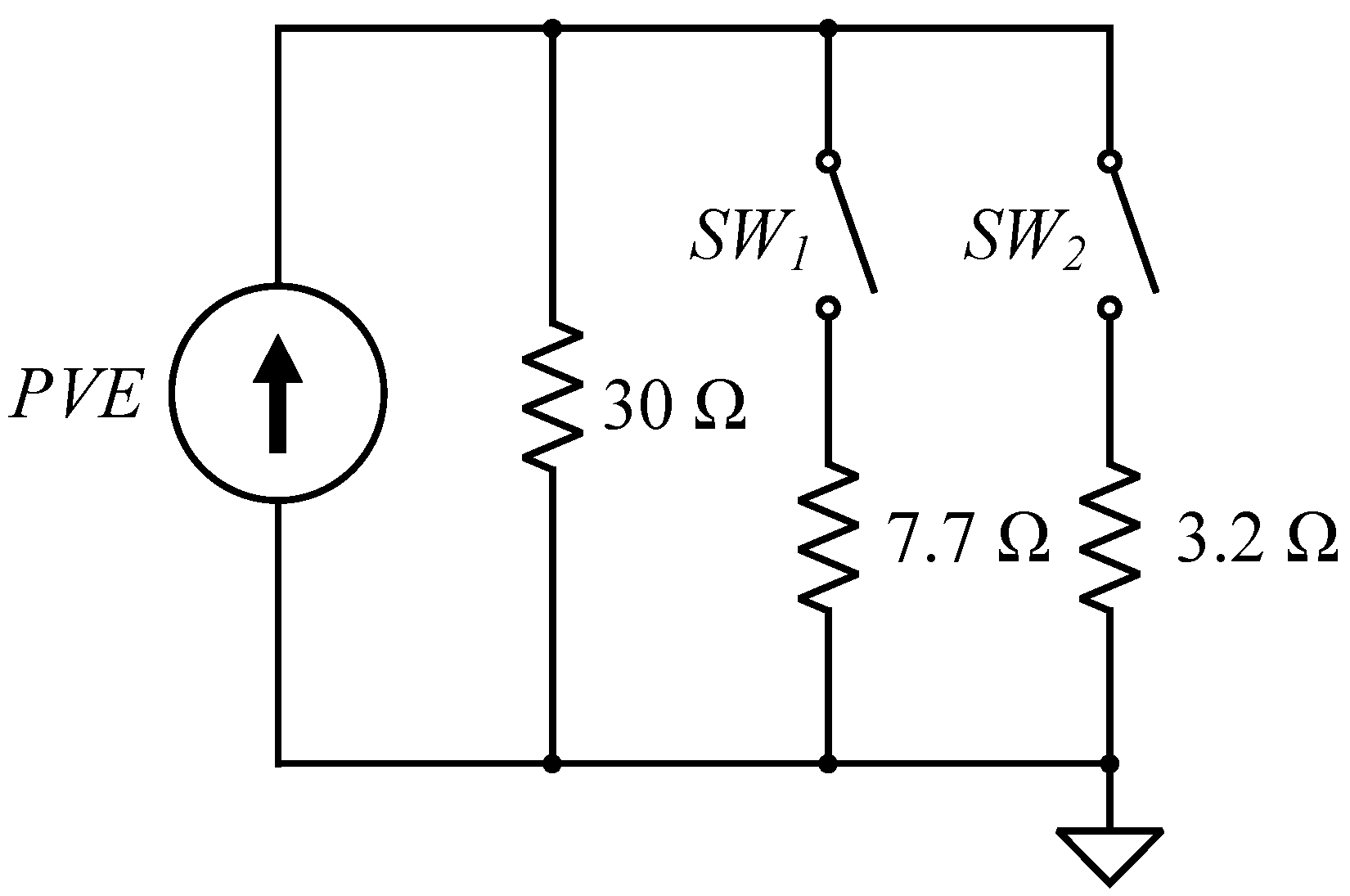

| Step | A | B | C |

|---|---|---|---|

| Switch #1 | Open | Closed | Open |

| Switch #2 | Open | Open | Closed |

| Resistance (Ω) | 30.0 | 6.2 | 2.2 |

| Current (A) | 1.5 | 6.5 | 12.0 |

| Power (W) | 70 | 260 | 304 |

| Rs,add | 0 Ω | 0.1 Ω | 0.2 Ω | 0.3 Ω |

|---|---|---|---|---|

| IMP (A) | 11.0 | 11.0 | 11.0 | 11.0 |

| VMP (V) | 35.0 | 33.7 | 32.5 | 31.2 |

| PMP (W) | 384.6 | 371.1 | 357.7 | 343.0 |

| Efficiency (%) | 91 | 87 | 84 | 82 |

| PVE Model | A-1 | A-2 | B-1 | |

|---|---|---|---|---|

| Case 1 | VOC (V) | 22.6 | 22.8 | 27.0 |

| ISC (A) | 9.0 | 9.0 | 9.0 | |

| Pout (W) | 203.4 | 205.2 | 243.0 | |

| Case 2 | VOC (V) | 23.0 | 22.5 | 25.7 |

| ISC (A) | 10.0 | 9.0 | 7.0 | |

| Pout (W) | 230.0 | 202.5 | 179.9 | |

| Case 3 | VOC (V) | 23.0 | 21.6 | 24.0 |

| ISC (A) | 10.0 | 7.0 | 5.0 | |

| Pout (W) | 230.0 | 151.2 | 120.0 | |

| Case 1 | Case 2 | Case 3 | ||||

|---|---|---|---|---|---|---|

| ILoad (A) | V (V) | P (W) | V (V) | P (W) | V (V) | P (W) |

| 0.0 | 69.8 | 0 | 71.5 | 0 | 68.0 | 0 |

| 1.0 | 68.2 | 68.2 | 69.0 | 69.0 | 66.0 | 66.0 |

| 2.0 | 66.7 | 133.4 | 67.1 | 134.2 | 63.7 | 127.4 |

| 3.0 | 65.0 | 195.0 | 65.2 | 195.6 | 60.8 | 182.4 |

| 4.0 | 63.3 | 253.2 | 62.9 | 251.6 | 56.9 | 227.6 |

| 5.0 | 61.2 | 306.0 | 60.2 | 301.0 | 38.4 | 192.0 |

| 6.0 | 58.9 | 353.4 | 56.2 | 337.2 | 36.8 | 220.8 |

| 7.0 | 55.7 | 389.9 | 37.3 | 261.1 | 18.1 | 126.7 |

| 8.0 | 51.0 | 408.0 | 35.4 | 283.2 | 17.2 | 137.6 |

| 9.0 | 24.2 | 217.8 | 16.5 | 148.5 | 16.2 | 145.8 |

| 10.0 | 0 | 0 | 13.7 | 137.0 | 13.4 | 134.0 |

| 11.0 | - | - | 0 | 0 | 0 | 0 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Choi, S.; Park, S.; Hong, J.; Won, J. A Design and Validation of 400 W PV Emulator Using Simple Equivalent Circuit for PV Power System Test. Energies 2023, 16, 1561. https://doi.org/10.3390/en16041561

Choi S, Park S, Hong J, Won J. A Design and Validation of 400 W PV Emulator Using Simple Equivalent Circuit for PV Power System Test. Energies. 2023; 16(4):1561. https://doi.org/10.3390/en16041561

Chicago/Turabian StyleChoi, Seungho, Sangyoung Park, Junhee Hong, and Jehyuk Won. 2023. "A Design and Validation of 400 W PV Emulator Using Simple Equivalent Circuit for PV Power System Test" Energies 16, no. 4: 1561. https://doi.org/10.3390/en16041561