Adaptive Fast Integral Terminal Sliding Mode Control Strategy Based on Four-Switch Buck–Boost Converters

Abstract

1. Introduction

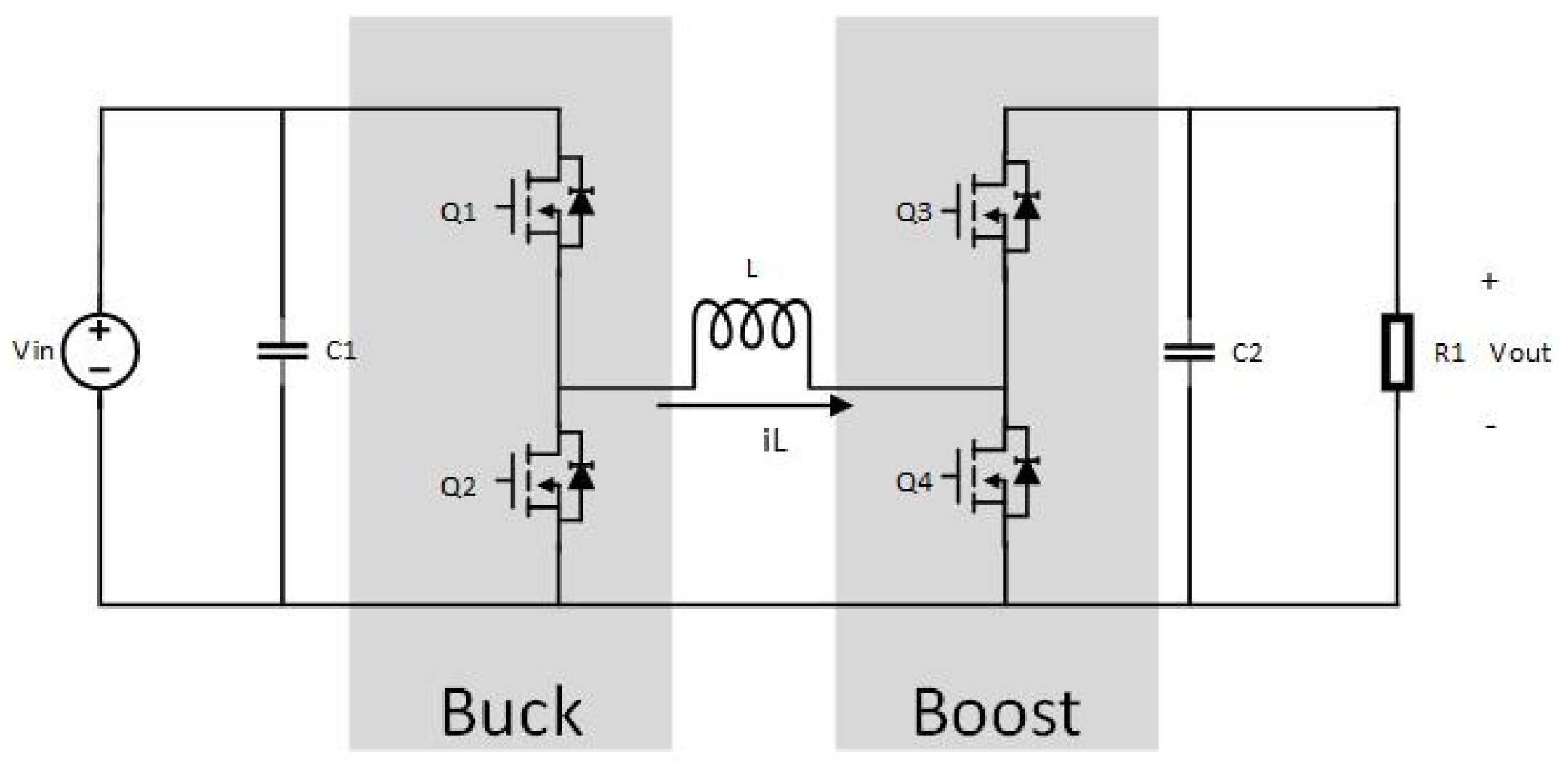

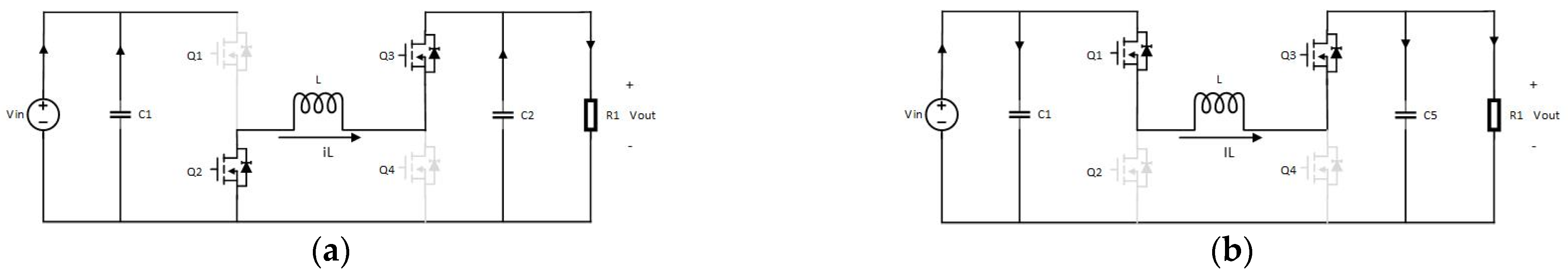

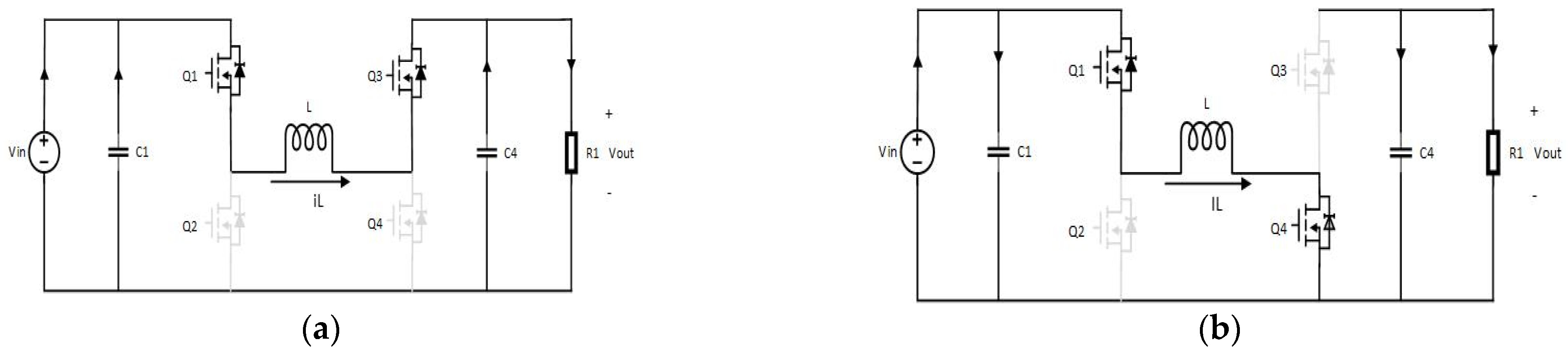

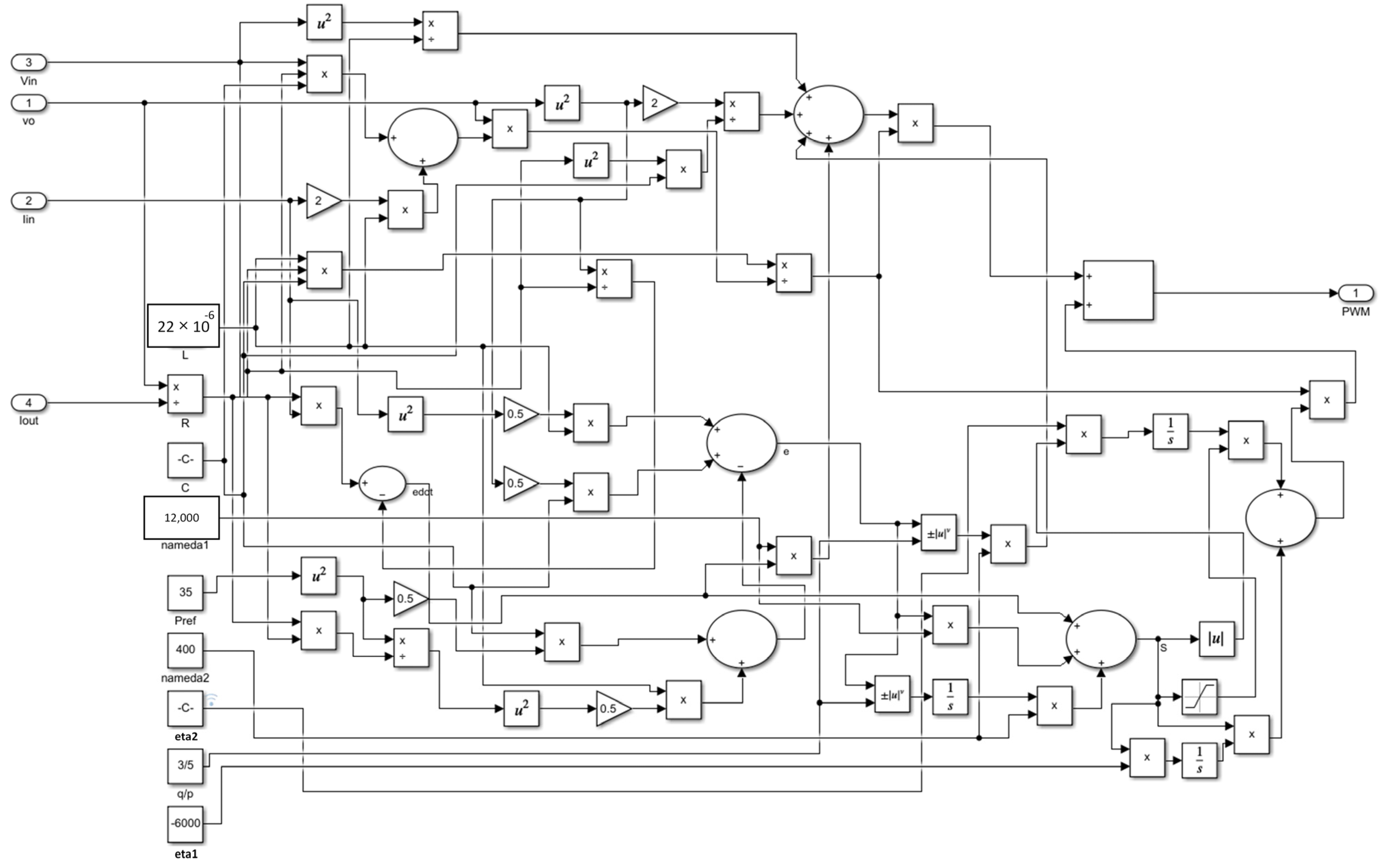

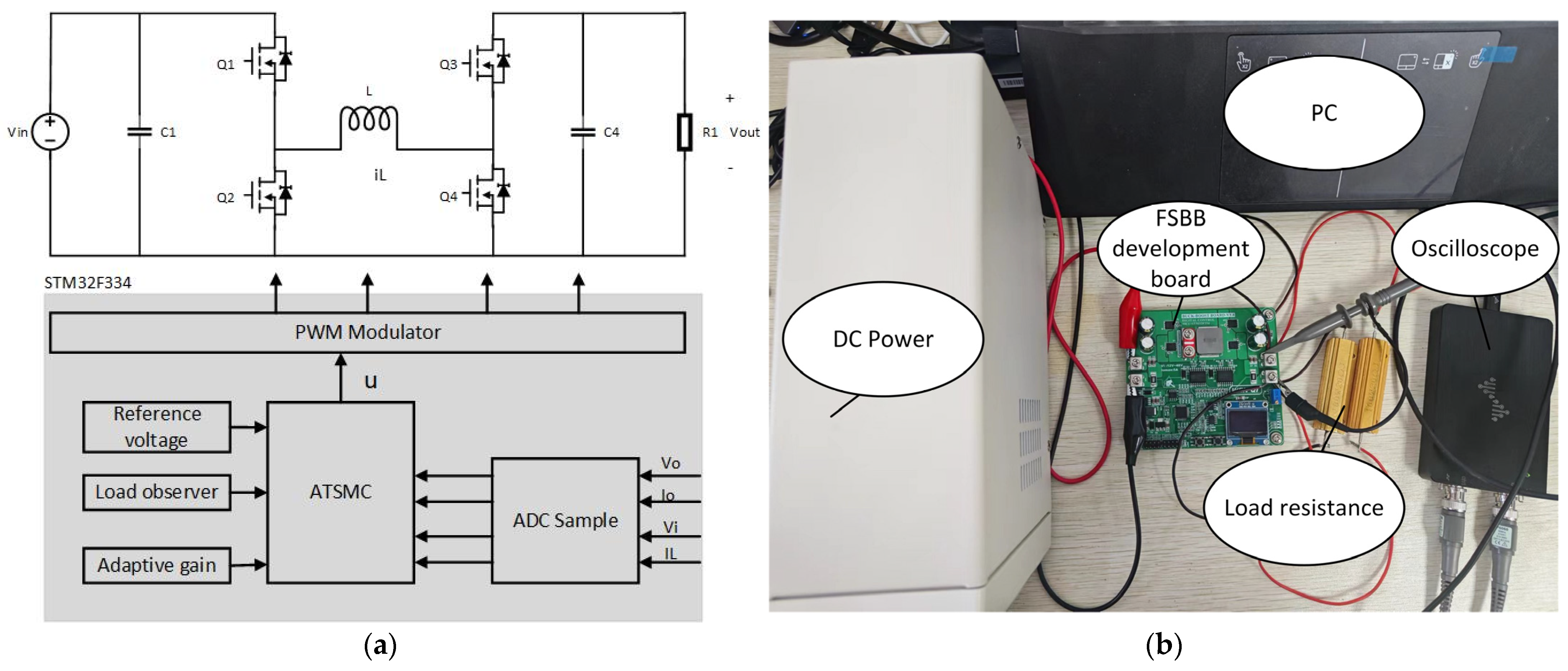

2. Working Principle and Modeling of FSBB

2.1. Operational Principle

2.2. Modeling Analysis

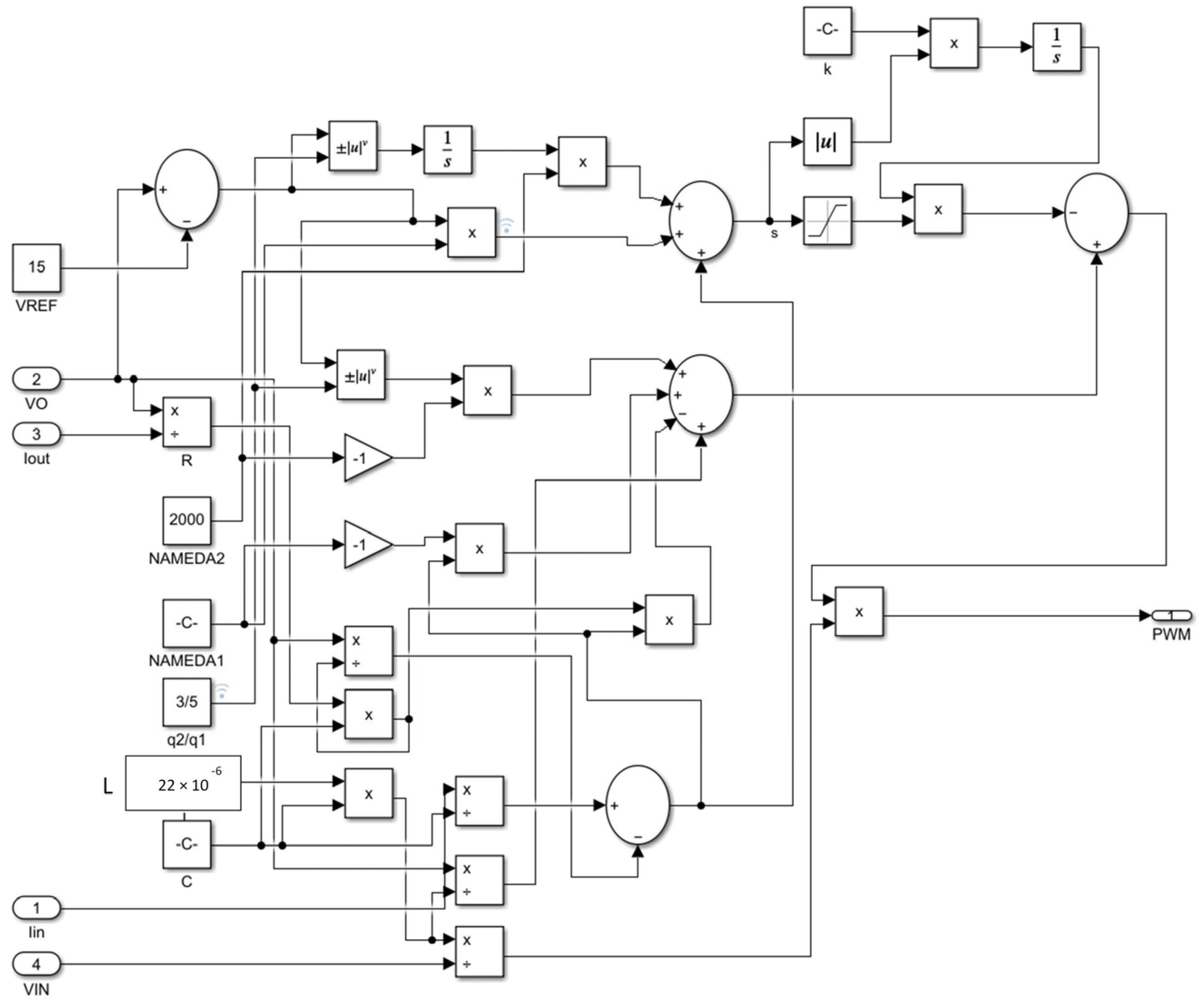

3. Controller Design

3.1. Buck Mode

3.2. Boost Mode

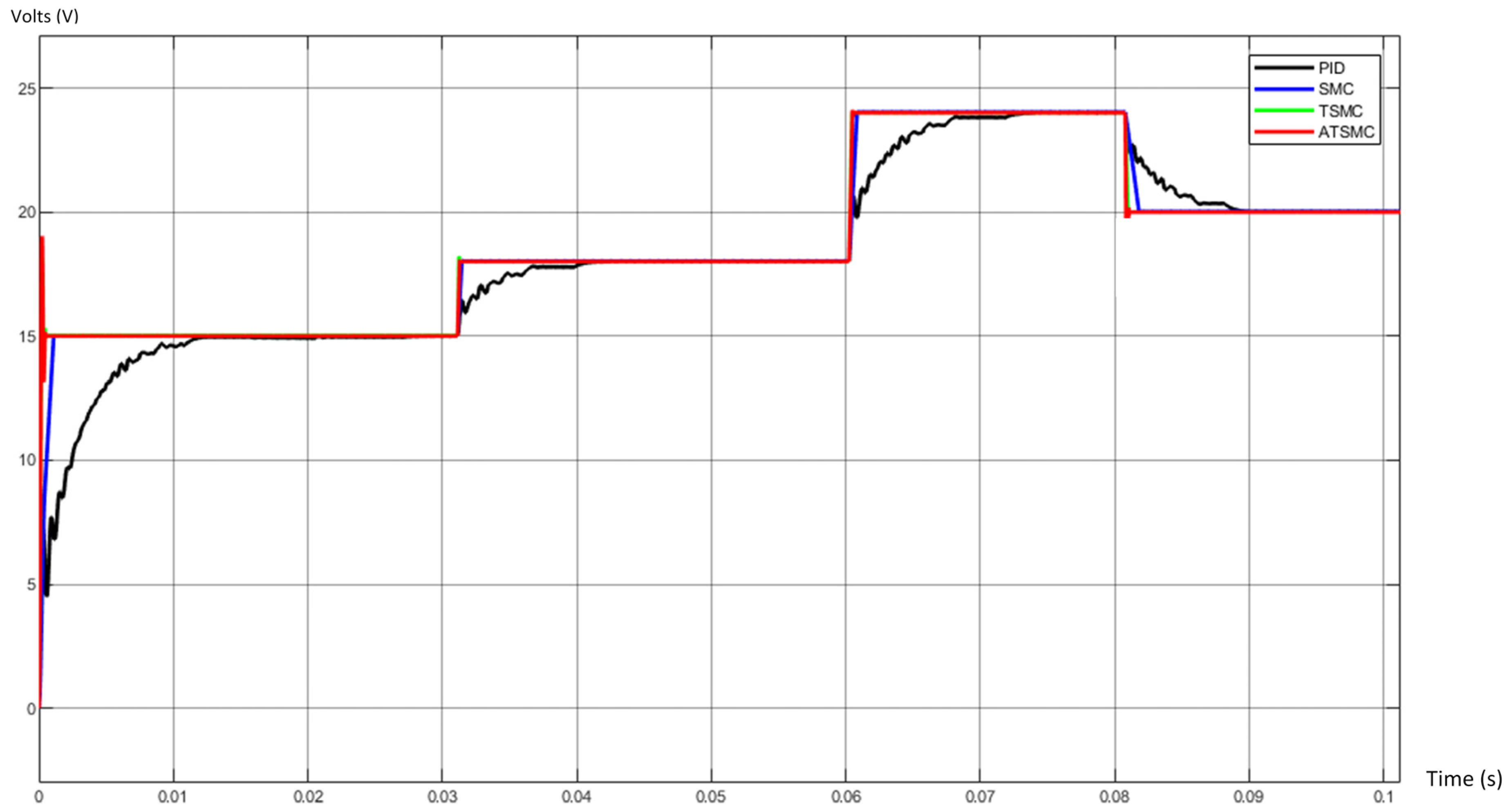

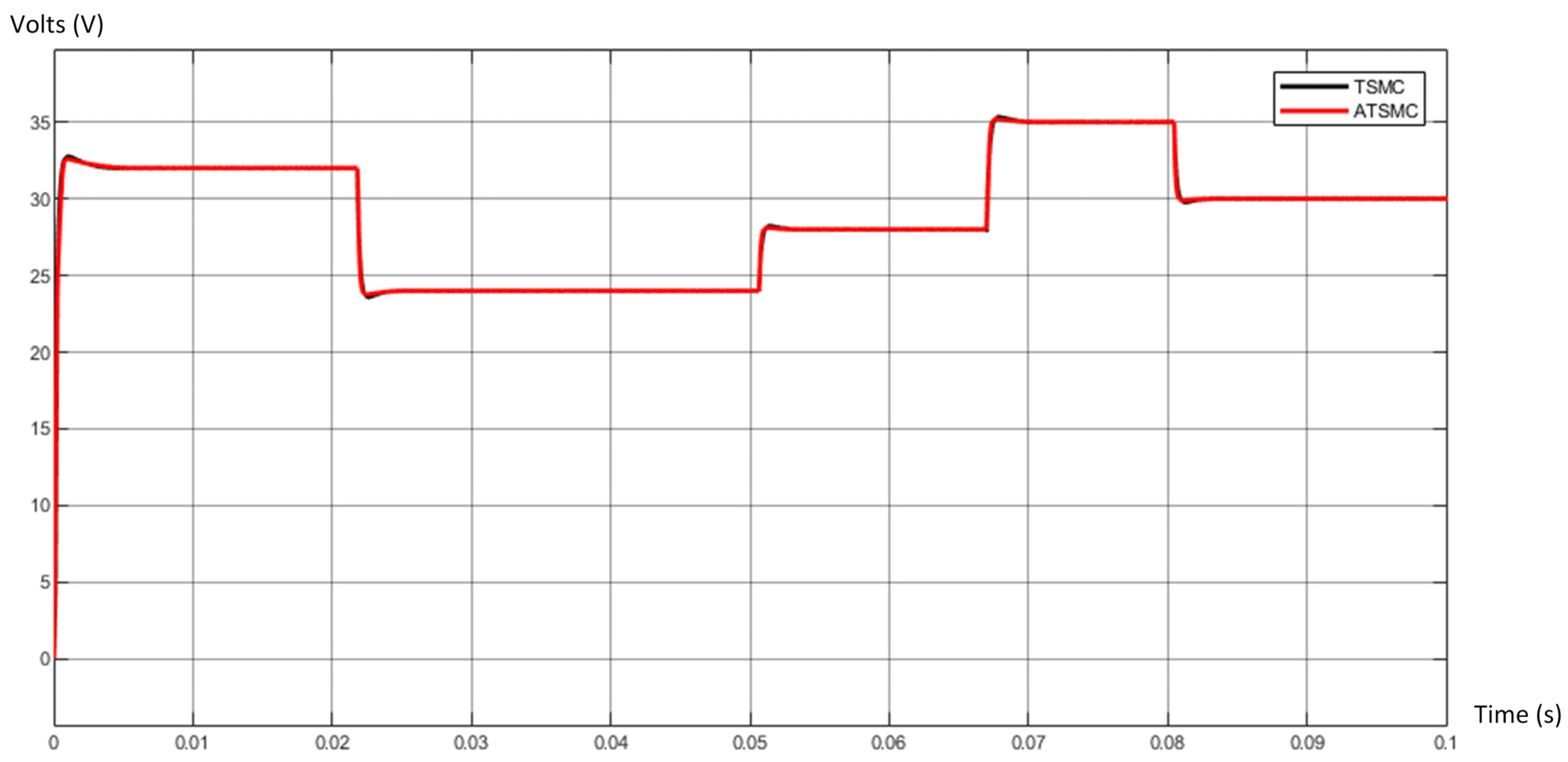

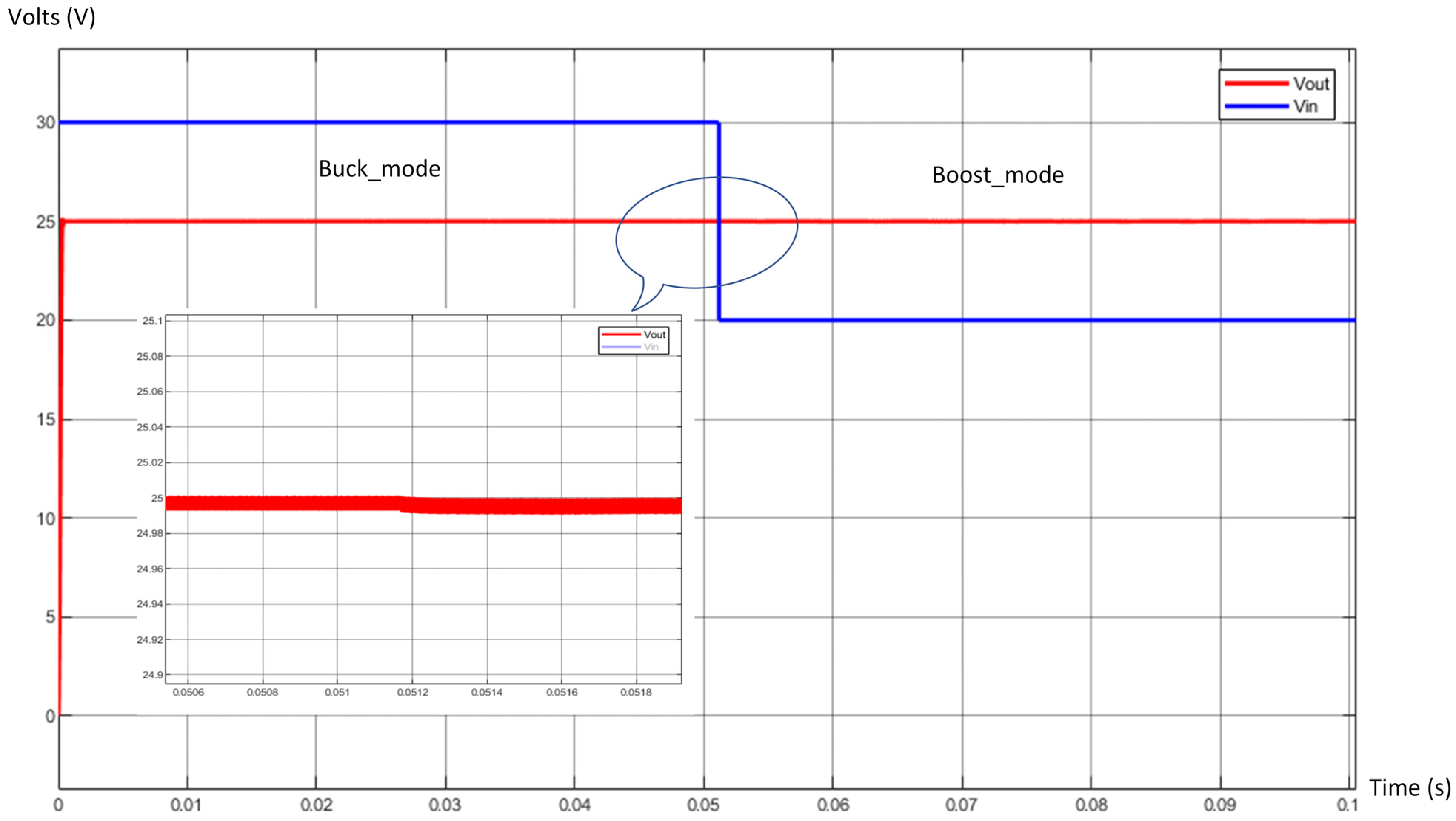

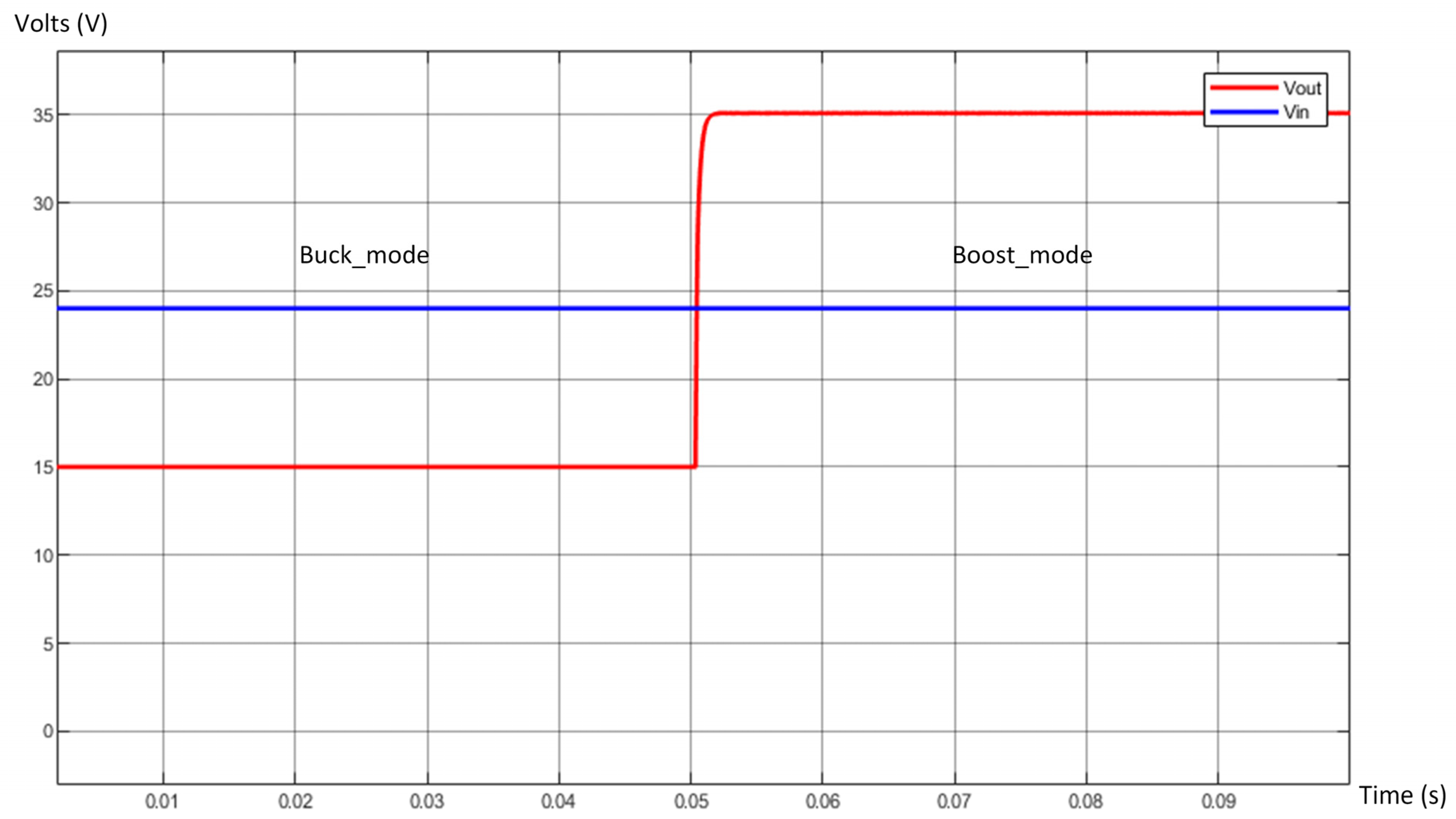

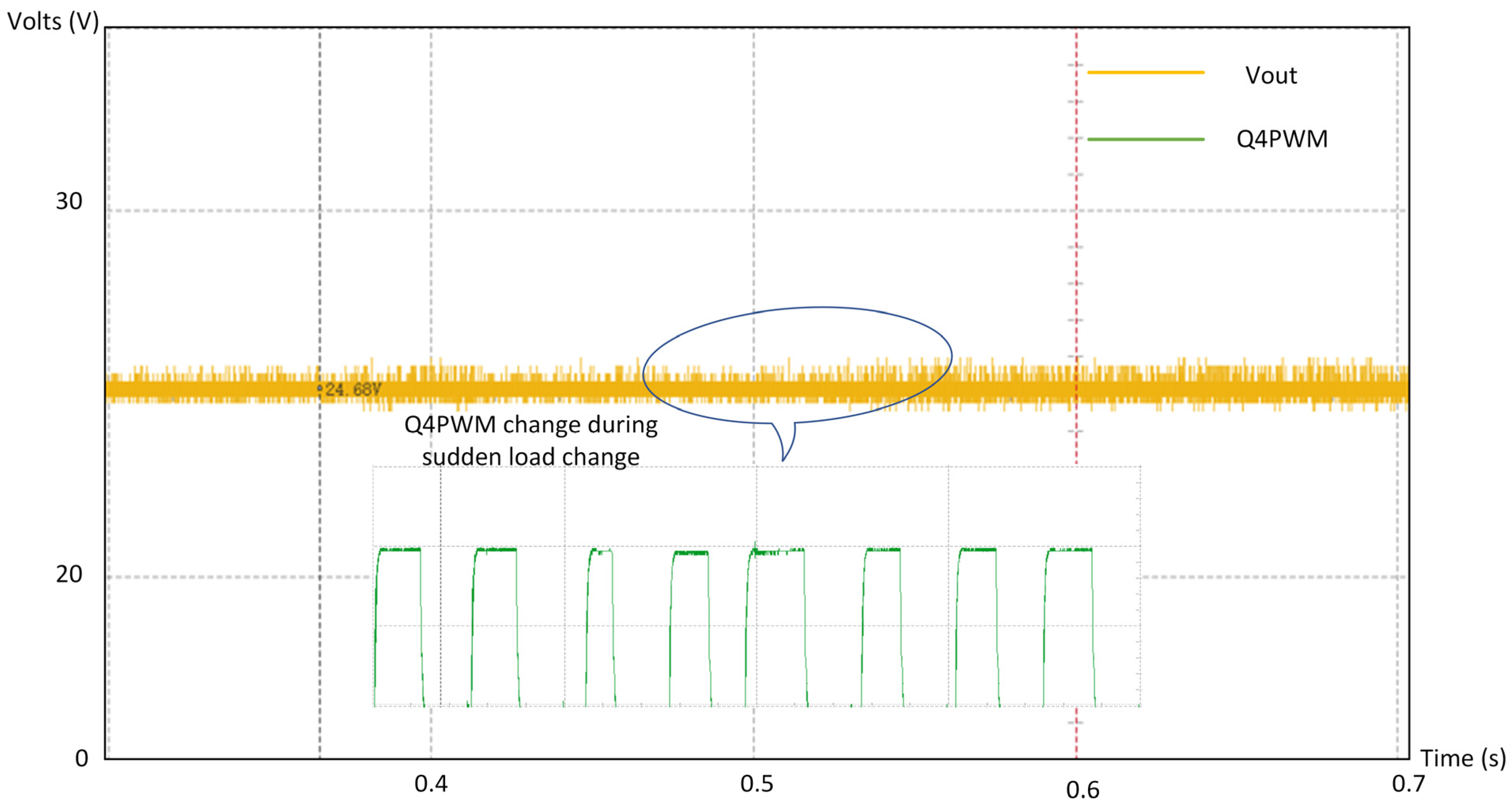

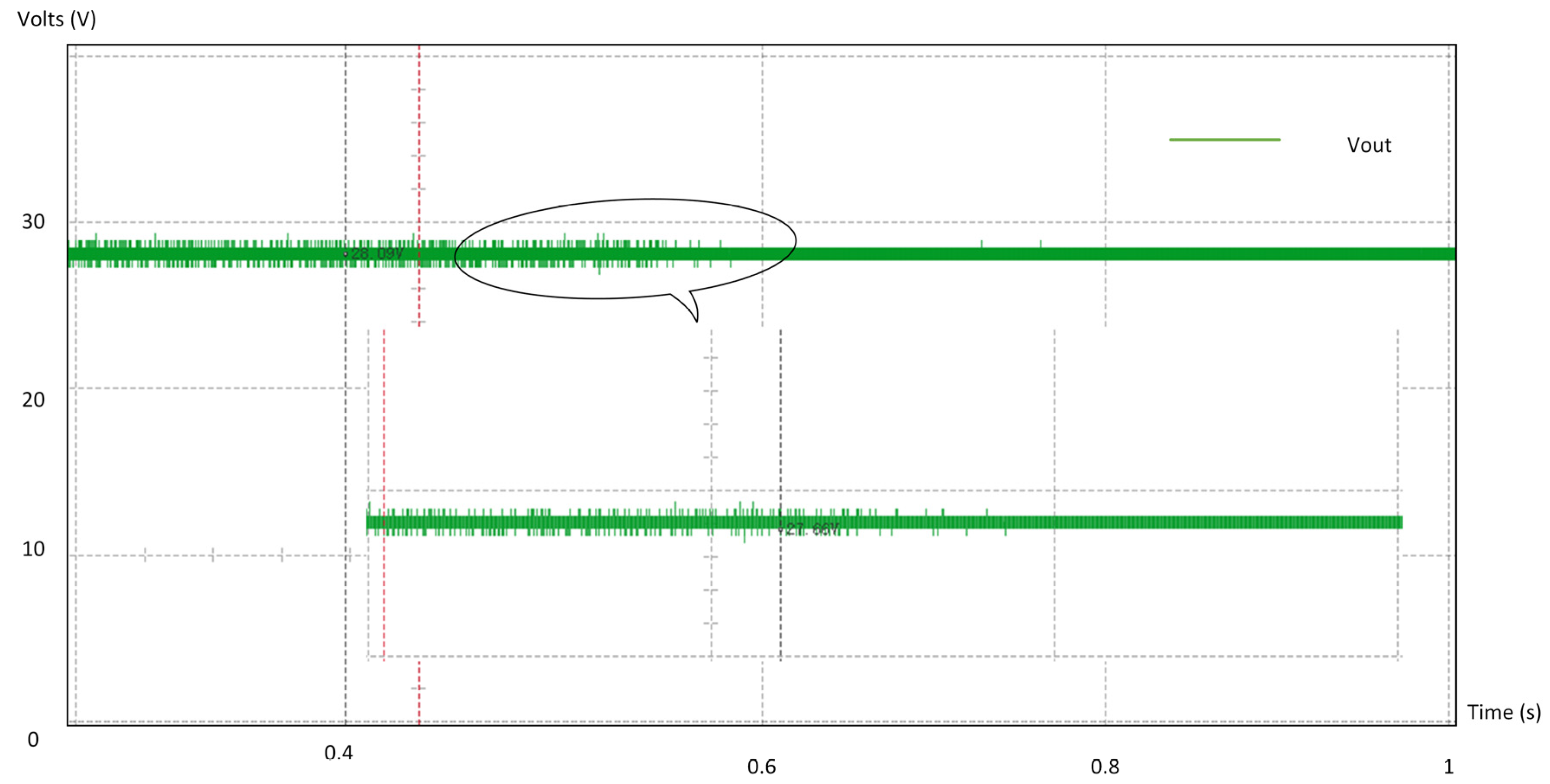

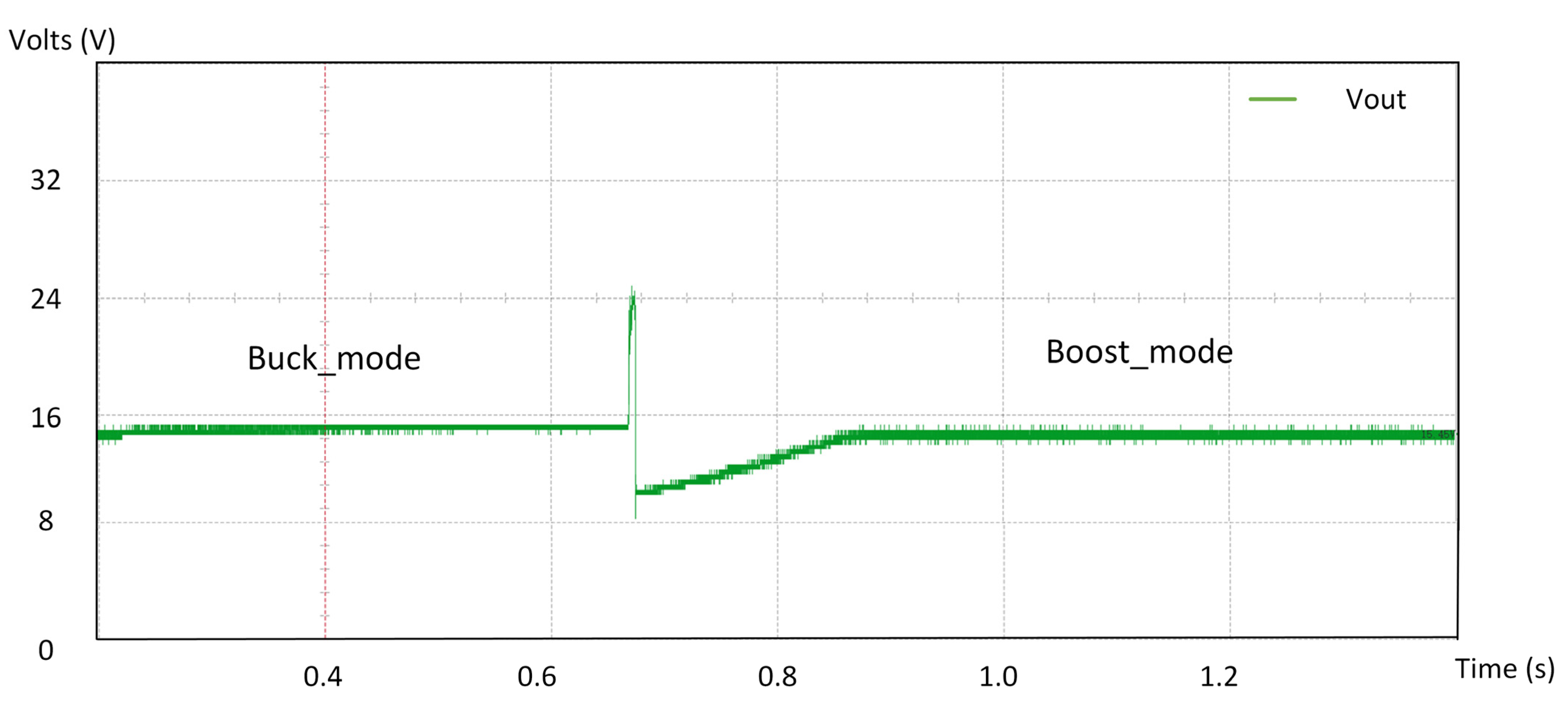

4. Simulation Results

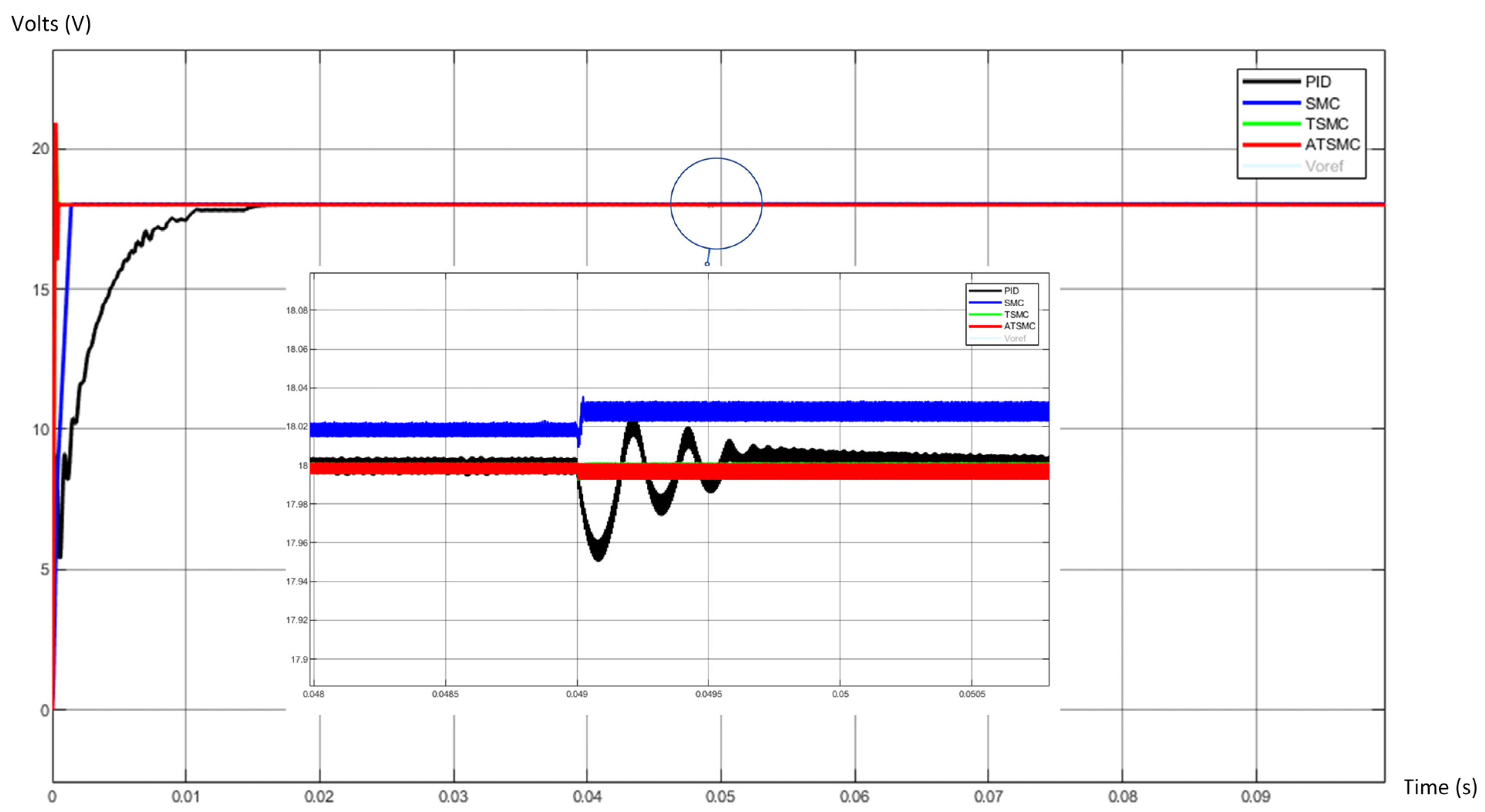

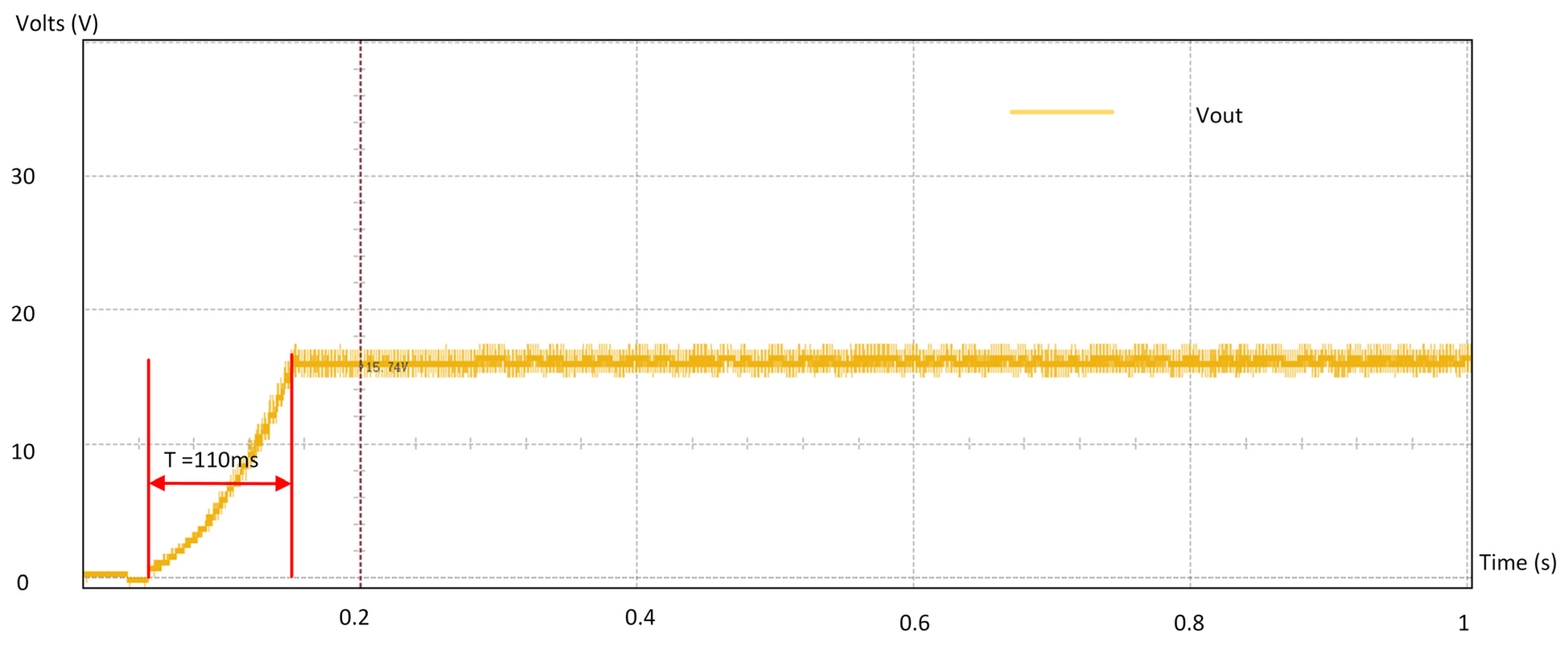

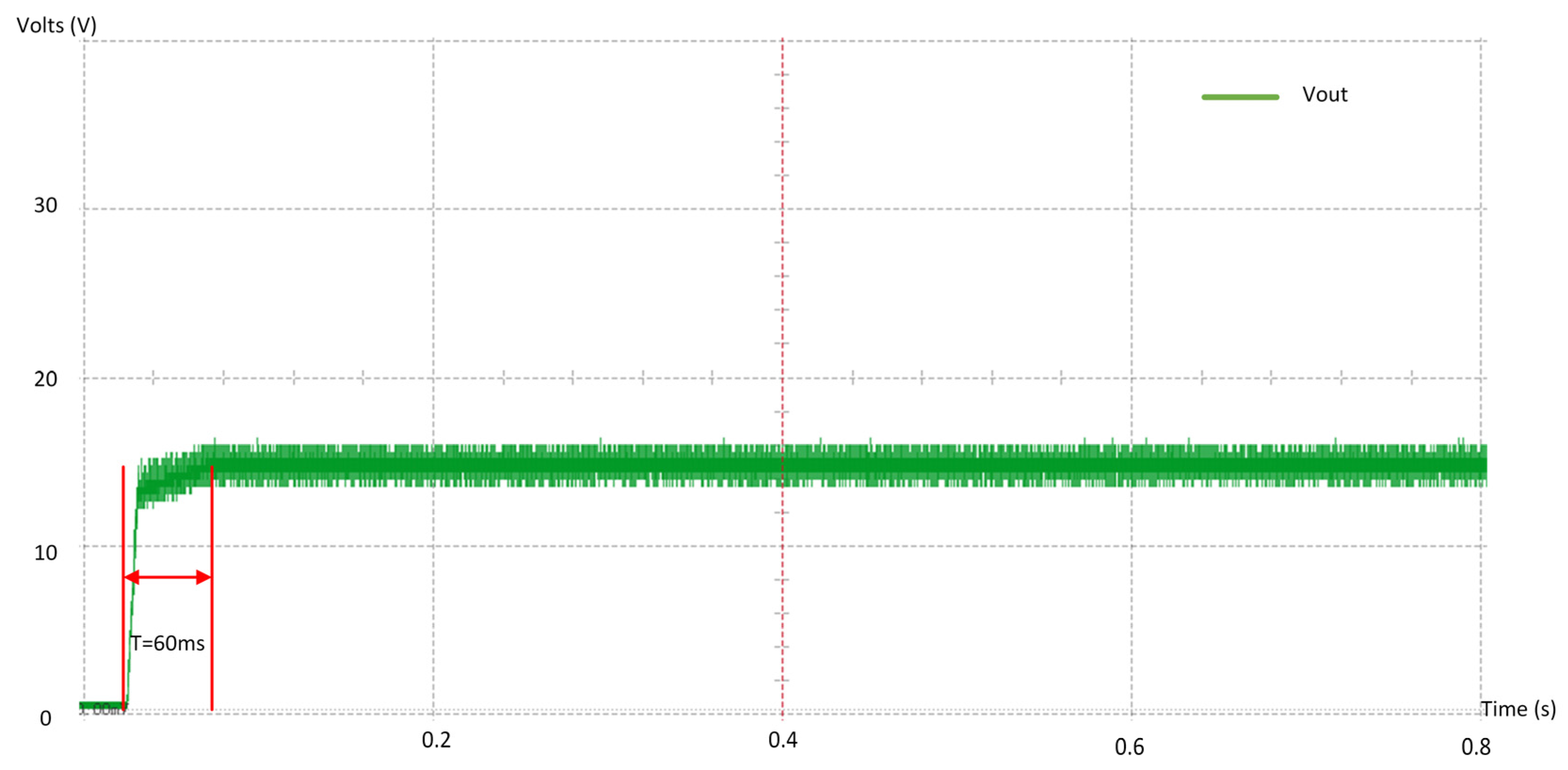

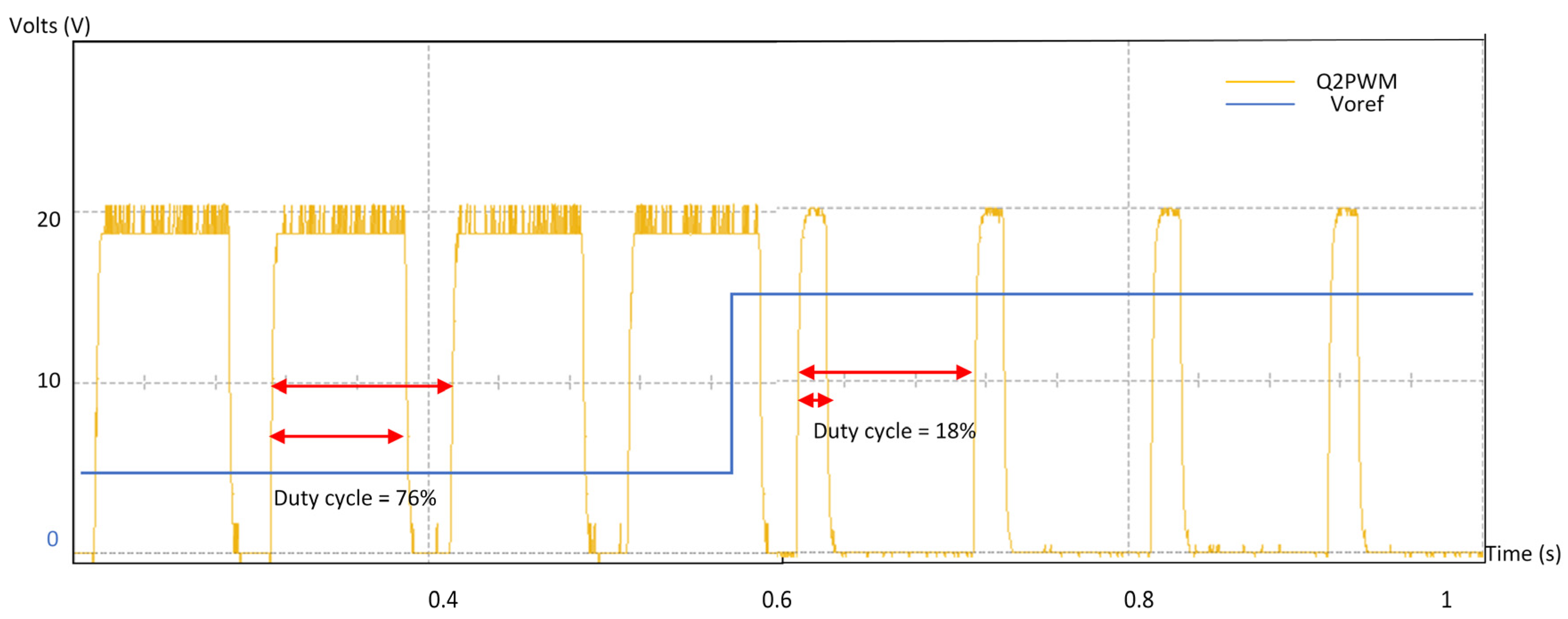

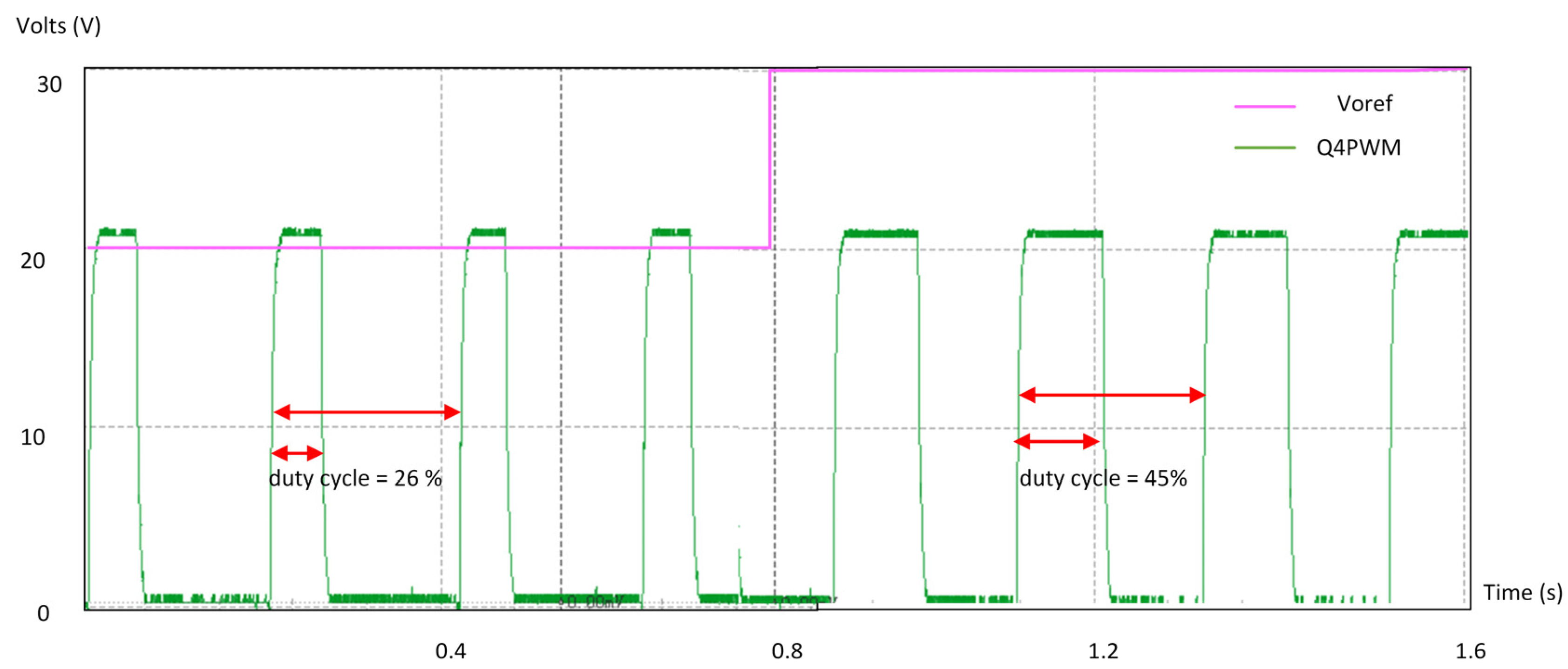

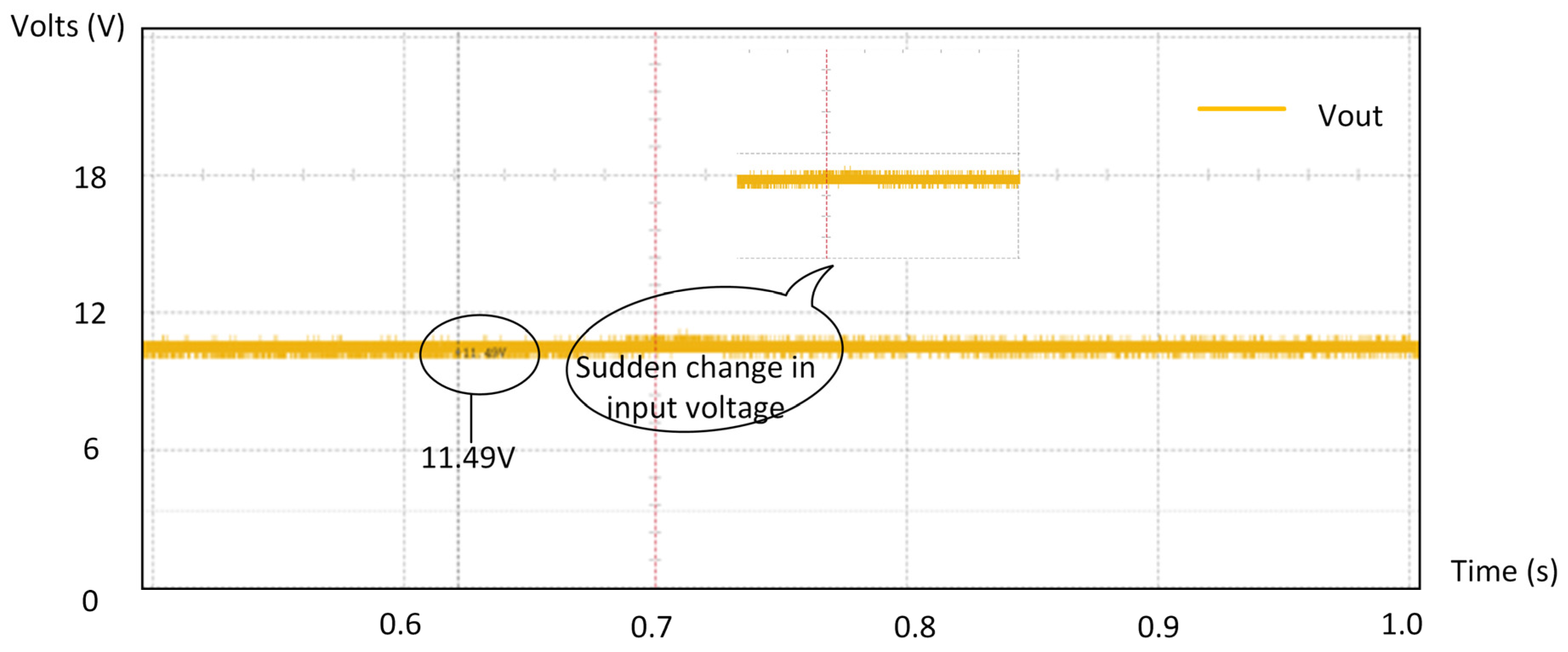

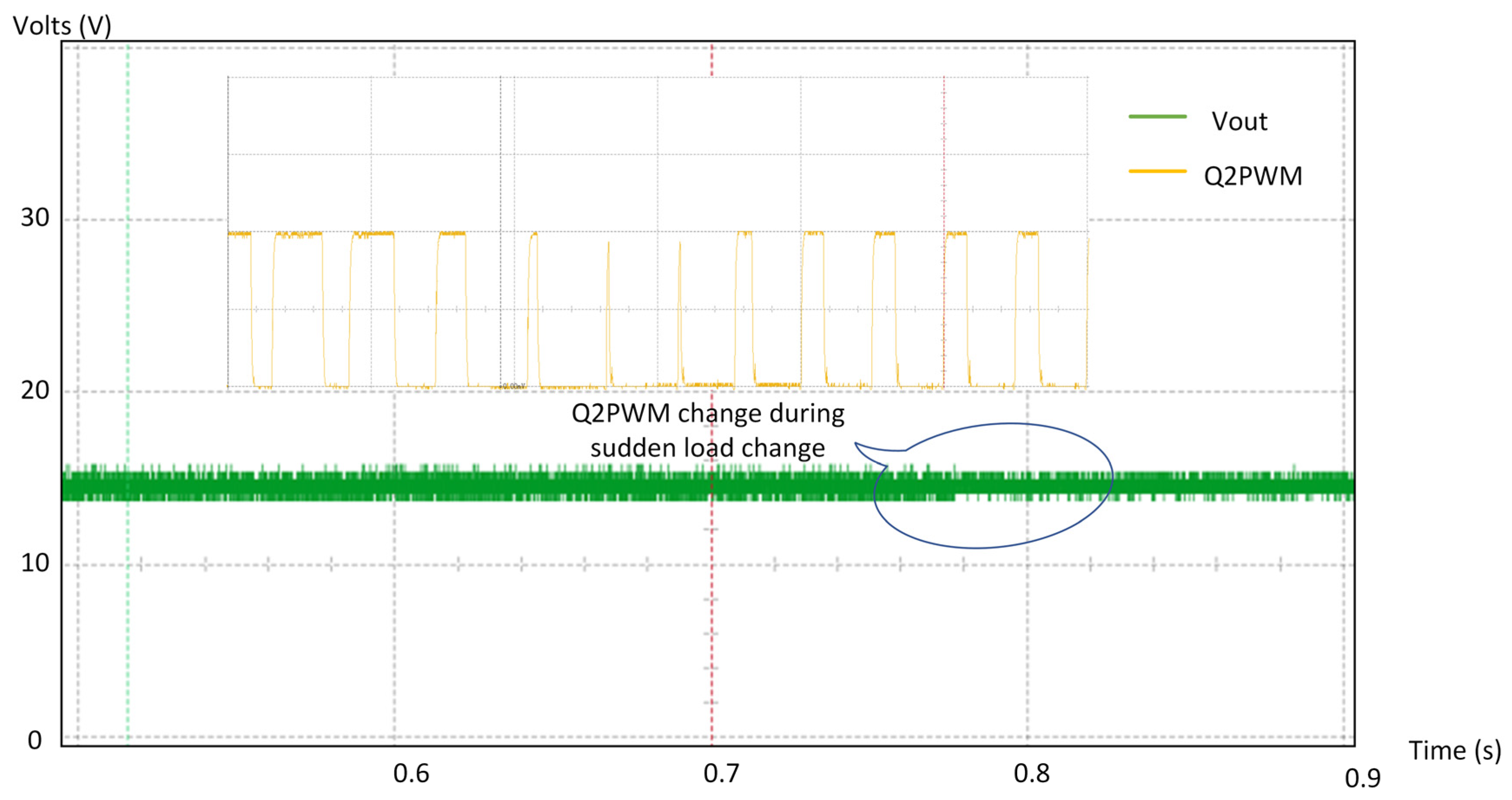

5. Board Verification

6. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Xu, Q.; Zhang, C.; Wen, C.; Wang, P. A novel composite nonlinear controller for stabilization of constant power load in DC microgrid. IEEE Trans. Smart Grid 2017, 10, 752–761. [Google Scholar] [CrossRef]

- Janabi, A.; Wang, B. Switched-capacitor voltage boost converter for electric and hybrid electric vehicle drives. IEEE Trans. Power Electron. 2019, 35, 5615–5624. [Google Scholar] [CrossRef]

- Pinto, R.A.; Cosetin, M.R.; Bolzan, T.E.; Marchesan, T.B.; Campos, A.; Alonso, J.M.; Prado, R.N. A bidirectional buck-boost converter to supply LEDs from batteries during peak load time. In Proceedings of the IECON 2011—37th Annual Conference of the IEEE Industrial, Melbourne, VIC, Australia, 7–10 November 2011. [Google Scholar]

- Linares, J.; Barahona, J.L.; Sira, H.; Contreras, M.A. Robust passivity-based control of a buck–boost-converter/DC-motor system: An active disturbance rejection approach. IEEE Trans. Ind. Appl. 2012, 48, 2362–2371. [Google Scholar] [CrossRef]

- Chen, I.C.; Liang, C.W.; Tsai, T.H. A single-inductor dual-input dual-output DC–DC converter for photovoltaic and piezoelectric energy harvesting systems. IEEE Trans. Circuits Syst. II Express Briefs 2019, 66, 1763–1767. [Google Scholar] [CrossRef]

- Camara, M.B.; Gualous, H.; Gustin, F.; Berthon, A.; Dakyo, B. DC/DC converter design for supercapacitor and battery power management in hybrid vehicle applications—Polynomial control strategy. IEEE Trans. Ind. Electron. 2009, 57, 587–597. [Google Scholar] [CrossRef]

- Khan, M.A.; Ahmed, A.; Husain, I.; Sozer, Y.; Badawy, M. Performance analysis of bidirectional DC–DC converters for electric vehicles. IEEE Trans. Ind. Appl. 2015, 51, 3442–3452. [Google Scholar] [CrossRef]

- Yong, J.; Xu, X.; Zeng, L.; Li, L. A review of low voltage DC power distribution system. Proc. CSEE 2013, 33, 42–52. [Google Scholar]

- Zhang, N.; Zhang, G.; See, K.W. Systematic derivation of dead-zone elimination strategies for the noninverting synchronous buck–boost converter. IEEE Trans. Power Electron. 2017, 33, 3497–3508. [Google Scholar] [CrossRef]

- Orellana, M.; Petibon, S.; Estibals, B.; Alonso, C. Four switch buck-boost converter for photovoltaic DC-DC power applications. In Proceedings of the IECON 2010—36th Annual Conference on IEEE Industrial Electronics Society, Glendale, AZ, USA, 7–13 November 2010. [Google Scholar]

- Lee, H.S.; Yun, J.J. High-efficiency bidirectional buck–boost converter for photovoltaic and energy storage systems in a smart grid. IEEE Trans. Power Electron. 2018, 34, 4316–4328. [Google Scholar] [CrossRef]

- Waffler, S.; Kolar, J.W. A novel low-loss modulation strategy for high-power bidirectional buck + boost converters. IEEE Trans. Power Electron. 2009, 24, 1589–1599. [Google Scholar] [CrossRef]

- Huang, P.C.; Wu, W.Q.; Ho, H.H.; Chen, K.H. Hybrid buck–boost feedforward and reduced average inductor current techniques in fast line transient and high-efficiency buck–boost converter. IEEE Trans. Power Electron. 2009, 25, 719–730. [Google Scholar] [CrossRef]

- Ren, X.; Ruan, X.; Qian, H.; Li, M.; Chen, Q. Three-mode dual-frequency two-edge modulation scheme for four-switch buck–boost converter. IEEE Trans. Power Electron. 2008, 24, 499–509. [Google Scholar]

- Chen, C.W.; Chen, K.H.; Chen, Y.M. Modeling and controller design of an autonomous PV module for DMPPT PV systems. IEEE Trans. Power Electron. 2013, 29, 4723–4732. [Google Scholar] [CrossRef]

- Kim, S.K.; Lee, K.B. Robust feedback-linearizing output voltage regulator for DC/DC boost converter. IEEE Trans. Ind. Electron. 2015, 62, 7127–7135. [Google Scholar] [CrossRef]

- Sarvi, M.; Soltani, I.; NamazyPour, N.; Rabbani, N. A New Sliding Mode Controller for DC/DC Converters in Photovoltaic Systems. J. Energy 2013, 2013, 871025. [Google Scholar] [CrossRef]

- Mohammadzamani, F.; Hashemi, M.; Shahgholian, G. Adaptive neural control of non-linear fractional order multi-agent systems in the presence of error constraints and input saturation. IET Control Theory Appl. 2022, 16, 1283–1298. [Google Scholar] [CrossRef]

- Cai, J.; Zhao, Y.; Hou, Y.; Chen, Y. Research on Control Strategy of Single-Mode Four-Switch Buck-Boost Converter. In Proceedings of the 2021 China Automation Congress (CAC), Beijing, China, 22–24 October 2021. [Google Scholar]

- Komurcugil, H.; Guler, N.; Bayhan, S. Lyapunov-function based control strategy for four-switch buck-boost dc-dc converters. In Proceedings of the 2022 IEEE 31st International Symposium on Industrial Electronics (ISIE), Anchorage, AK, USA, 1–3 June 2022. [Google Scholar]

- Ullah, Q.; Busarello, T.D.C.; Brandao, D.I.; Simões, M.G. Design and performance evaluation of SMC-based DC–DC converters for microgrid applications. Energies 2023, 16, 4212. [Google Scholar] [CrossRef]

- Tan, S.C.; Lai, Y.M.; Tse, C.K. A unified approach to the design of PWM-based sliding-mode voltage controllers for basic DC-DC converters in continuous conduction mode. IEEE Trans. Circuits Syst. I Regul. Pap. 2006, 53, 1816–1827. [Google Scholar]

- Ardhenta, L.; Rusli, M. Sliding mode control of output voltage in DC-DC Boost converter using PI sliding surface. In Proceedings of the 2021 International Conference on Electrical and Information Technology (IEIT), Malang, Indonesia, 14–15 September 2021. [Google Scholar]

- Qiao, L.; Zhang, W. Adaptive non-singular integral terminal sliding mode tracking control for autonomous underwater vehicles. IET Control Theory Appl. 2017, 11, 1293–1306. [Google Scholar] [CrossRef]

- Qiao, L.; Zhang, W. Adaptive second-order fast nonsingular terminal sliding mode tracking control for fully actuated autonomous underwater vehicles. IEEE J. Ocean. Eng. 2018, 44, 363–385. [Google Scholar] [CrossRef]

- Liu, P.; Wang, Z. Adaptive Discrete-Time Sliding Mode Control Design for Buck Converters with Disturbances. In Proceedings of the 2023 42nd Chinese Control Conference (CCC), Tianjin, China, 24–26 July 2023. [Google Scholar]

- Zambrano-Prada, D.; Aroudi, A.E.; Vázquez-Seiszdedos, L.; Lopez-Santos, O.; Haroun, R.; Martínez-Salamero, L. Adaptive Sliding Mode Control for a Boost Converter with Constant Power Load. In Proceedings of the 2023 IEEE Conference on Power Electronics and Renewable Energy (CPERE), Luxor, Egypt, 19–21 February 2023. [Google Scholar]

- Linares-Flores, J.; Heredia-Barba, R.; Heredia, O.; Castro-Heredia, G.; Curiel-Olivares, G.; Juarez-Abad, J.A. Adaptive sliding mode control based on a hyperbolic tangent function for DC-to-DC buck-boost power converter. In Proceedings of the 2020 IEEE Energy Conversion Congress and Exposition (ECCE), Detroit, MI, USA, 11–15 October 2022. [Google Scholar]

- Chang, Y.; Wang, A.; Gao, P.; Wang, Y.; Luo, M.; Huang, W. A non-singular terminal sliding mode control of the DC microgrid with constant power loads. In Proceedings of the 2023 IEEE 2nd Industrial Electronics Society Annual On-Line Conference (ONCON), Virtual, 8–10 December 2023. [Google Scholar]

- Chang, Y.; Gao, P.; Wang, A.; Wang, Y.; Zhang, C.; Huang, W. A Non-Singular Terminal Sliding Mode Control of Buck-Boost Converters Based on Extended State Observer. In Proceedings of the 2023 IEEE 2nd Industrial Electronics Society Annual On-Line Conference (ONCON), Virtual, 8–10 December 2023. [Google Scholar]

- Liu, Z.; Lin, X.; Gao, Y.; Xu, R.; Wang, J.; Wang, Y.; Liu, J. Fixed-time sliding mode control for DC/DC buck converters with mismatched uncertainties. IEEE Trans. Circuits Syst. I Regul. Pap. 2022, 70, 472–480. [Google Scholar] [CrossRef]

- Wang, Z.; Li, S.; Li, Q. Continuous nonsingular terminal sliding mode control of DC–DC boost converters subject to time-varying disturbances. IEEE Trans. Circuits Syst. II Express Briefs 2019, 67, 2552–2556. [Google Scholar] [CrossRef]

- Malge, S.V.; Ghogare, M.G.; Patil, S.L.; Deshpande, A.S.; Pandey, S.K. Chatter-free non-singular fast terminal sliding mode control of interleaved boost converter. IEEE Trans. Circuits Syst. II Express Briefs 2022, 70, 186–190. [Google Scholar] [CrossRef]

- Kaifei, Z.; Yiguang, C.; Haoran, Z.; Guowen, L. Fast Integral Terminal Sliding Mode Control of PMSM Based on New Sliding Mode Reaching Law. In Proceedings of the 2022 25th International Conference on Electrical Machines and Systems (ICEMS), Chiang Mai, Thailand, 29 November–2 December 2022. [Google Scholar]

- Sharma, K.; Palwalia, D.K. Robust controller design for DC-DC converters using fuzzy logic. In Proceedings of the 2017 4th International Conference on Signal Processing, Computing and Control (ISPCC), Solan, India, 21–23 September 2017. [Google Scholar]

- Guo, L.; Hung, J.Y.; Nelms, R.M. Evaluation of DSP-based PID and fuzzy controllers for DC–DC converters. IEEE Trans. Ind. Electron. 2009, 56, 2237–2248. [Google Scholar]

| References | Publication Year | Control Methods | Control Model | Challenges |

|---|---|---|---|---|

| Cai, J. [19] | 2021 | PID-2p2z | FSBB | More extended system settling times. |

| Ullah, Q. [21] | 2023 | Sliding mode control | FSBB | The systematic error can no longer converge in a finite time. |

| Liu, P. [26] | 2023 | Adaptive sliding mode control | Buck | Combining observers improves tracking accuracy but increases design complexity. |

| Zambrano-Prada, D. [27] | 2023 | Adaptive sliding mode control | Boost | The hyperbolic tracking error slows down the system’s responses. |

| Liu, Z. [31] | 2023 | Terminal sliding mode control | Buck | A second-order, fixed-time convergence law improves the algorithm complexity. |

| Wang, Z. [32] | 2020 | Terminal sliding mode control | Boost | A finite-time perturbation observer increases the complexity of the design structure. |

| Kaifei, Z. [34] | 2022 | Terminal sliding mode control | permanent magnet synchronous motor | Fast integral terminal sliding mode control effectively improves the dynamic characteristics of the system but cannot cope with variable operating environments. |

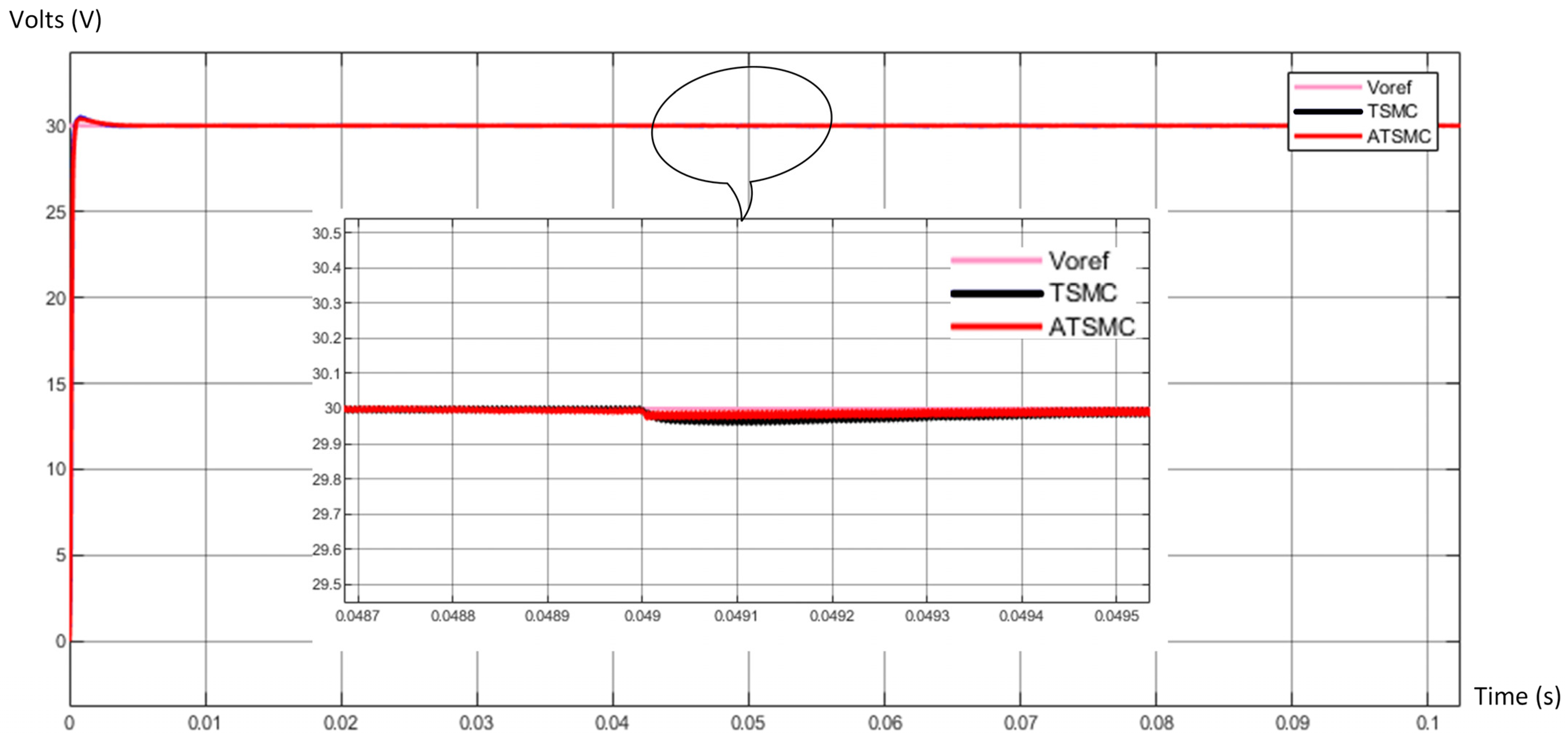

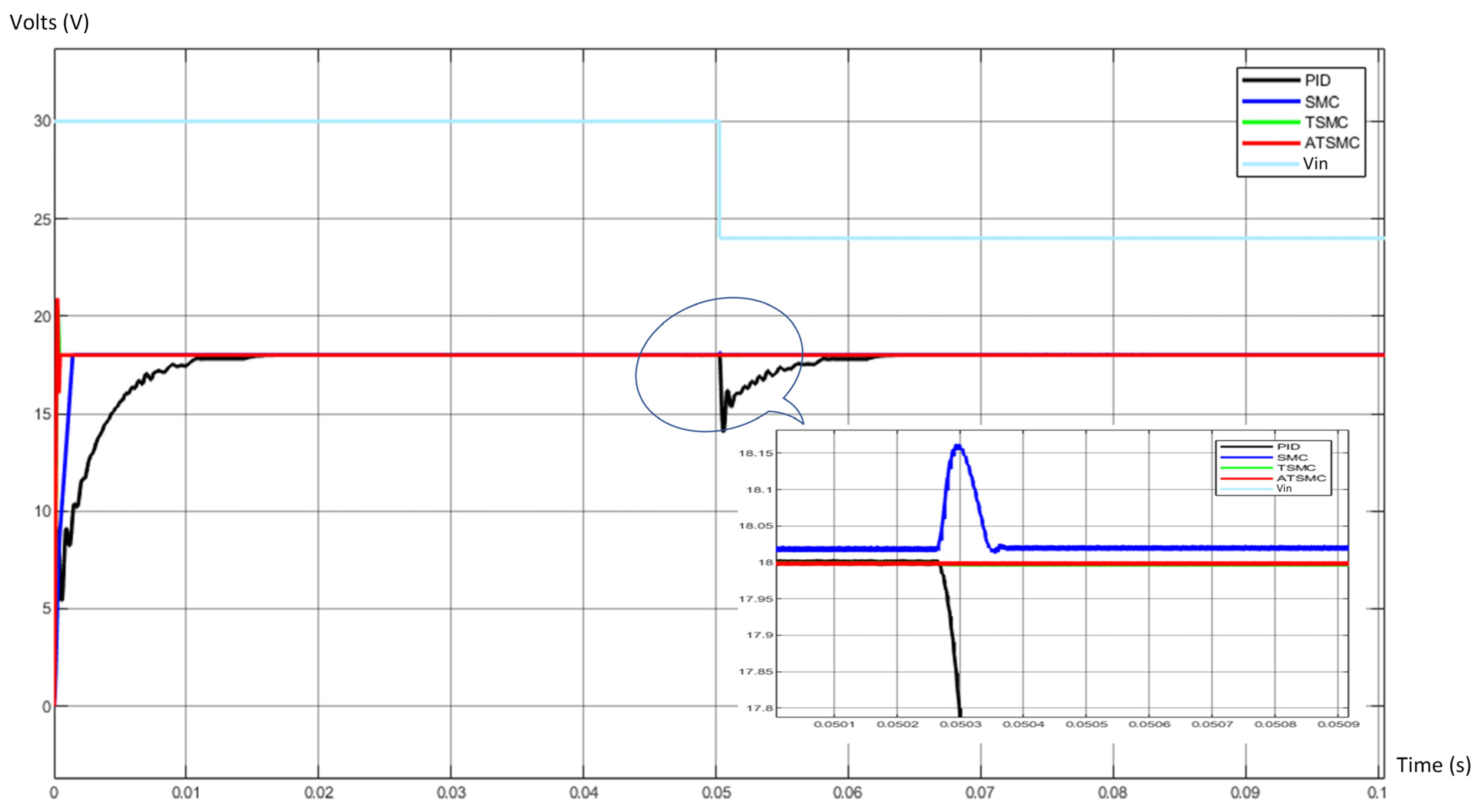

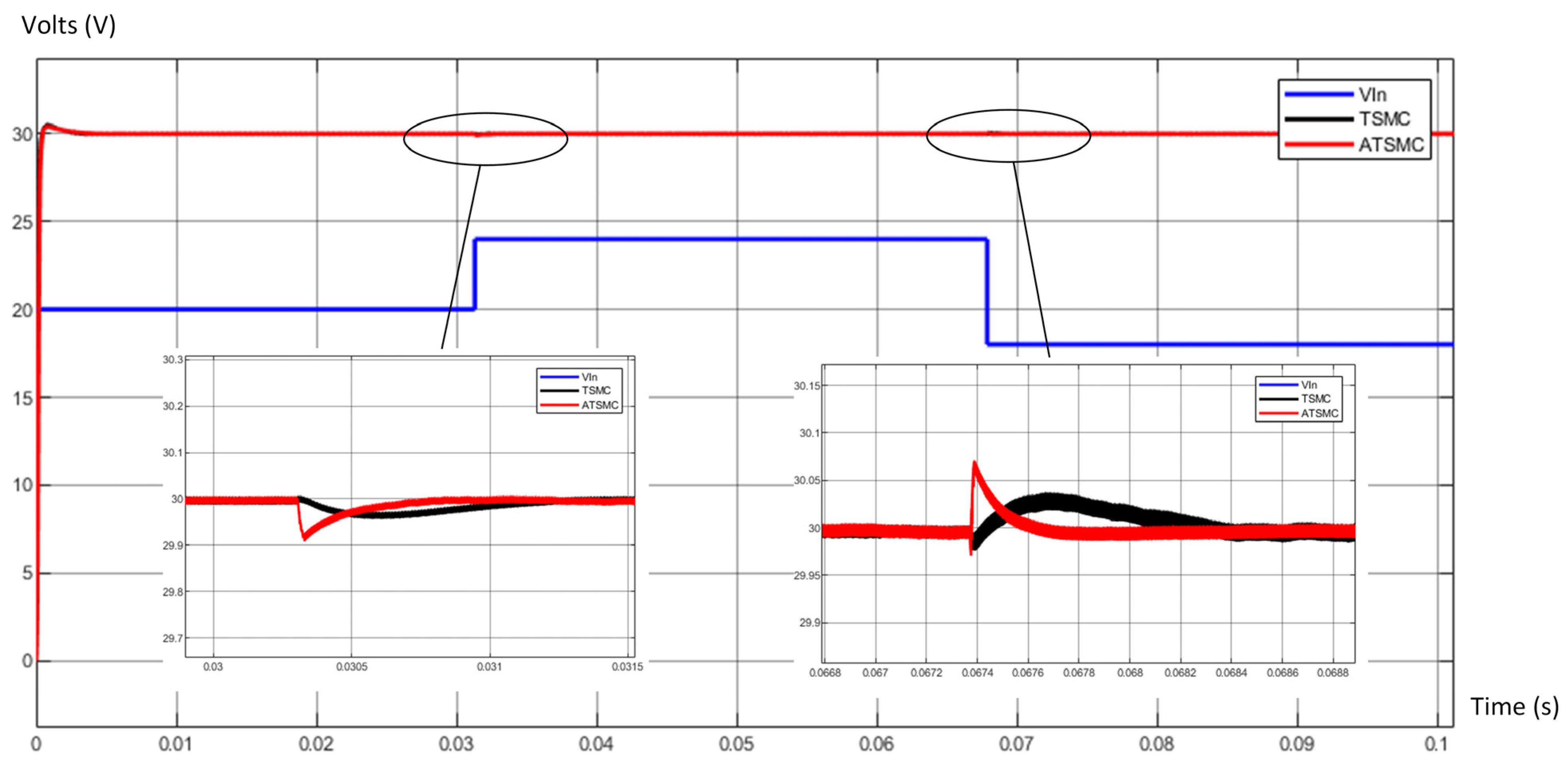

| Test Algorithm | Mode | ST (ms) | Load Regulation | Line Regulation |

|---|---|---|---|---|

| FLC [35] PID [19] SMC [21] TSMC | Buck | 10 | 1.84% | 0.96% |

| 21 | 2.3% | 1.04% | ||

| 1.31 0.4 | 1.67% 0.33% | 0.77% 0.083% | ||

| ATSMC | 0.51 | 0.25% | 0.027% | |

| FLC [36] PID [19] SMC [21] | Boost | 17 | 2.3% | 1.1% |

| 19 5 | 1.6% 0.9% | 1.2% 0.6% | ||

| TSMC ATSMC | 2.5 | 0.16% | 0.083% | |

| 2 | 0.03% | 0.03% |

| Description | Symbol | Nominal Value |

|---|---|---|

| Output Voltage | Vo | 5–48 V |

| Input Voltage | Vin | 10–30 V |

| Inductance | L | 22 uH |

| Capacitance | C | 440 uF |

| Minimum Load Resistance | R(min) | 10 Ω |

| Maximum Load Resistance | R(max) | 30 Ω |

| Switch Frequency | Fs | 200 kHz |

| Test Algorithm | Mode | ST (ms) | Load Regulation | Line Regulation |

|---|---|---|---|---|

| PID | 188 | 14.5% | 8.2% | |

| SMC | Buck | 141 | 2.2% | 1.9% |

| ATSMC | 60 | 0.8% | 0.33% | |

| PID SMC ATSMC | Boost | 401 178 | 9.4% 1.54% | 6.3 1.33% |

| 110 | 0.16% | 0.15% |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Ma, B.; Jiao, J.; Ye, Z. Adaptive Fast Integral Terminal Sliding Mode Control Strategy Based on Four-Switch Buck–Boost Converters. Energies 2024, 17, 3645. https://doi.org/10.3390/en17153645

Ma B, Jiao J, Ye Z. Adaptive Fast Integral Terminal Sliding Mode Control Strategy Based on Four-Switch Buck–Boost Converters. Energies. 2024; 17(15):3645. https://doi.org/10.3390/en17153645

Chicago/Turabian StyleMa, Borui, Jiye Jiao, and Zilong Ye. 2024. "Adaptive Fast Integral Terminal Sliding Mode Control Strategy Based on Four-Switch Buck–Boost Converters" Energies 17, no. 15: 3645. https://doi.org/10.3390/en17153645

APA StyleMa, B., Jiao, J., & Ye, Z. (2024). Adaptive Fast Integral Terminal Sliding Mode Control Strategy Based on Four-Switch Buck–Boost Converters. Energies, 17(15), 3645. https://doi.org/10.3390/en17153645