A Comparative Study of Silicon Carbide Merged PiN Schottky Diodes with Electrical-Thermal Coupled Considerations

Abstract

:1. Introduction

2. Materials and Methods

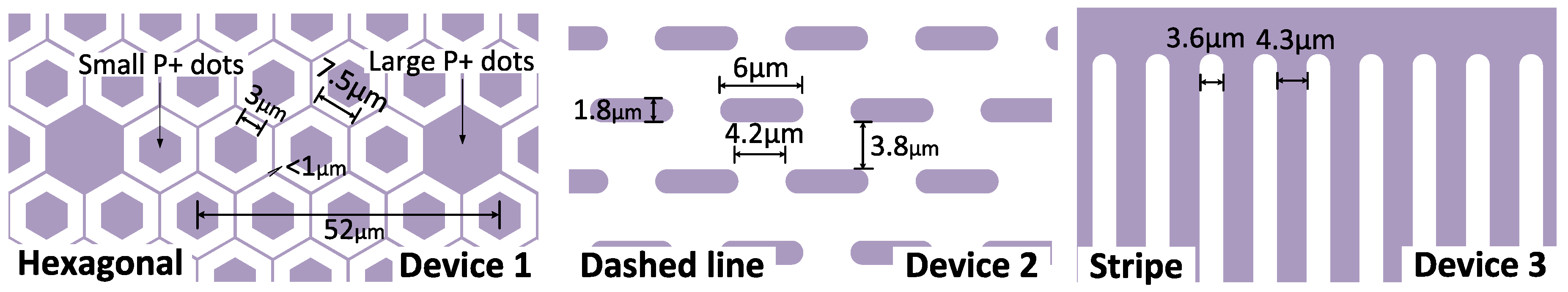

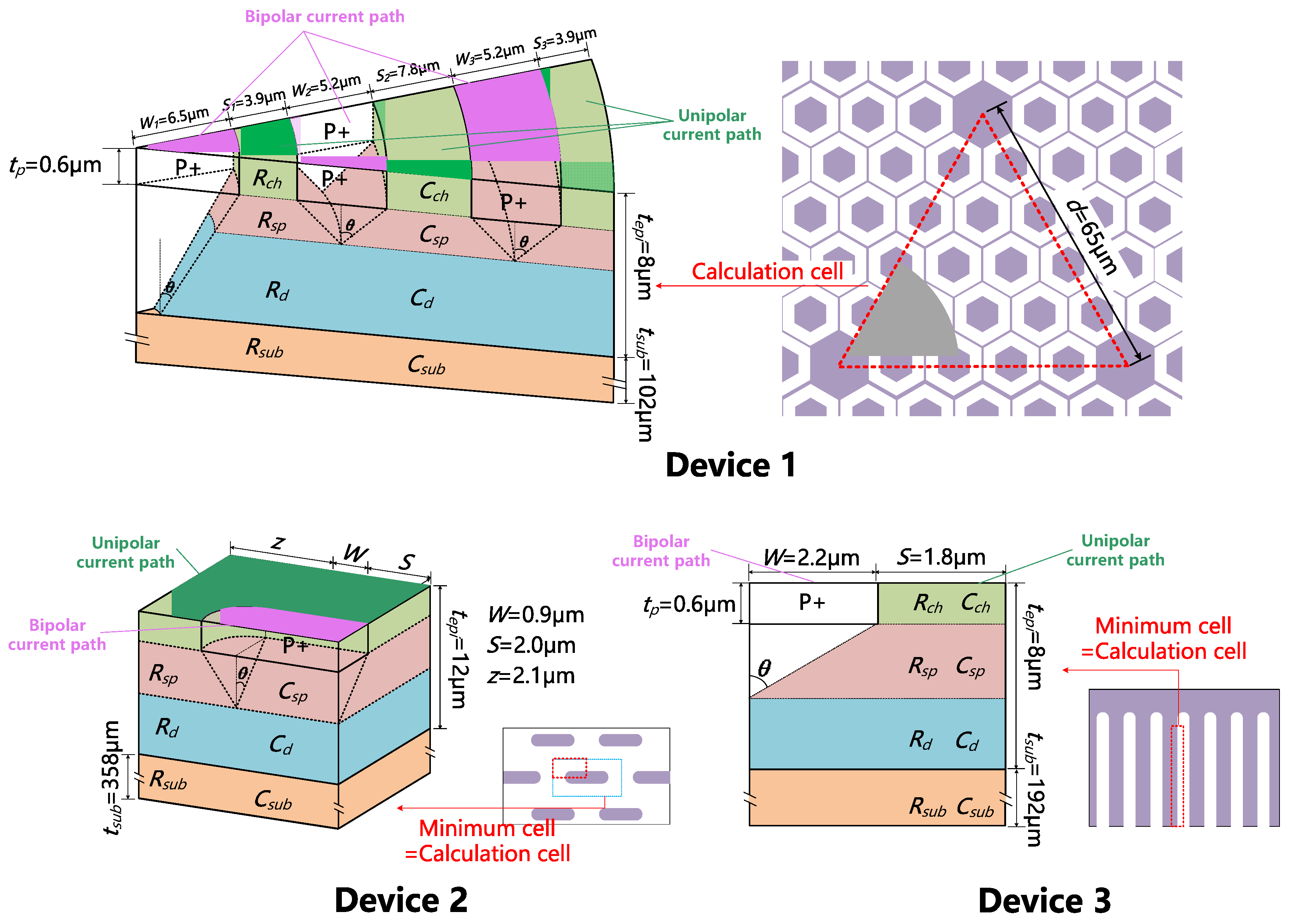

2.1. Device Structural Parameters

2.2. Device Simulation Structure and Models

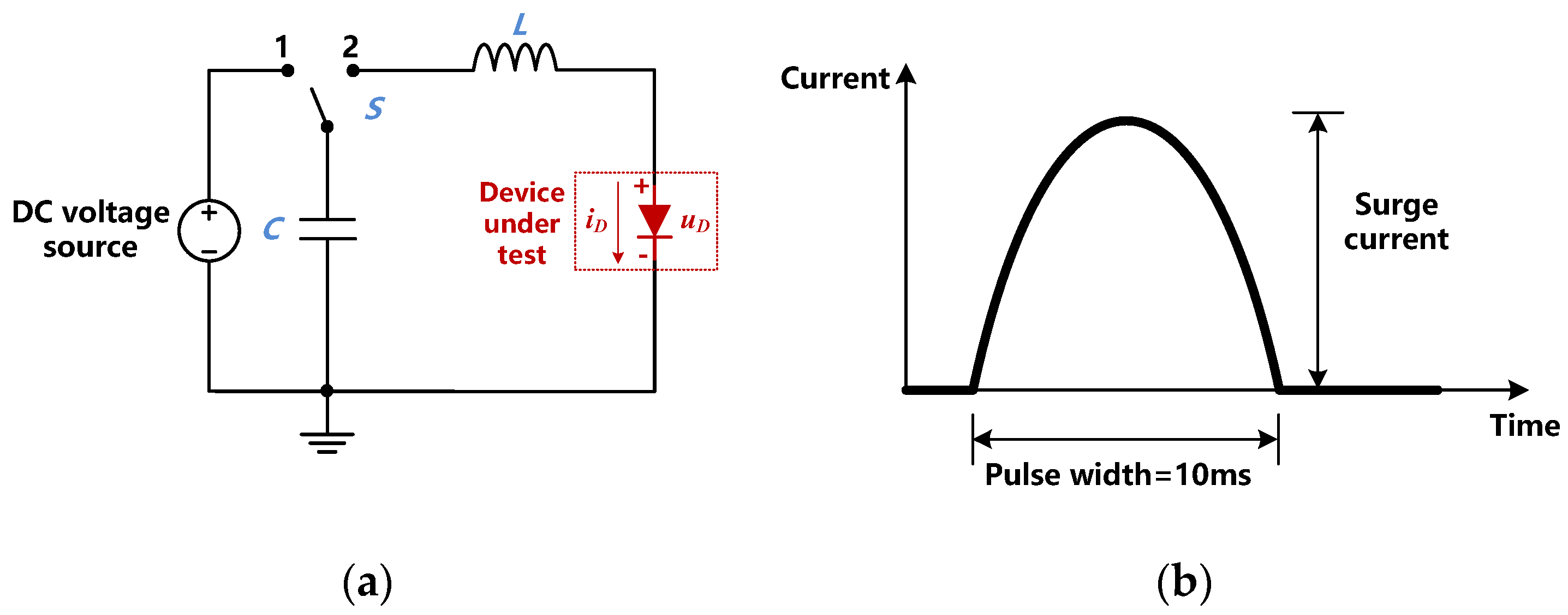

2.3. Experimental Setups of the Forward Characteristic Measurements and Serge Tests

3. Results

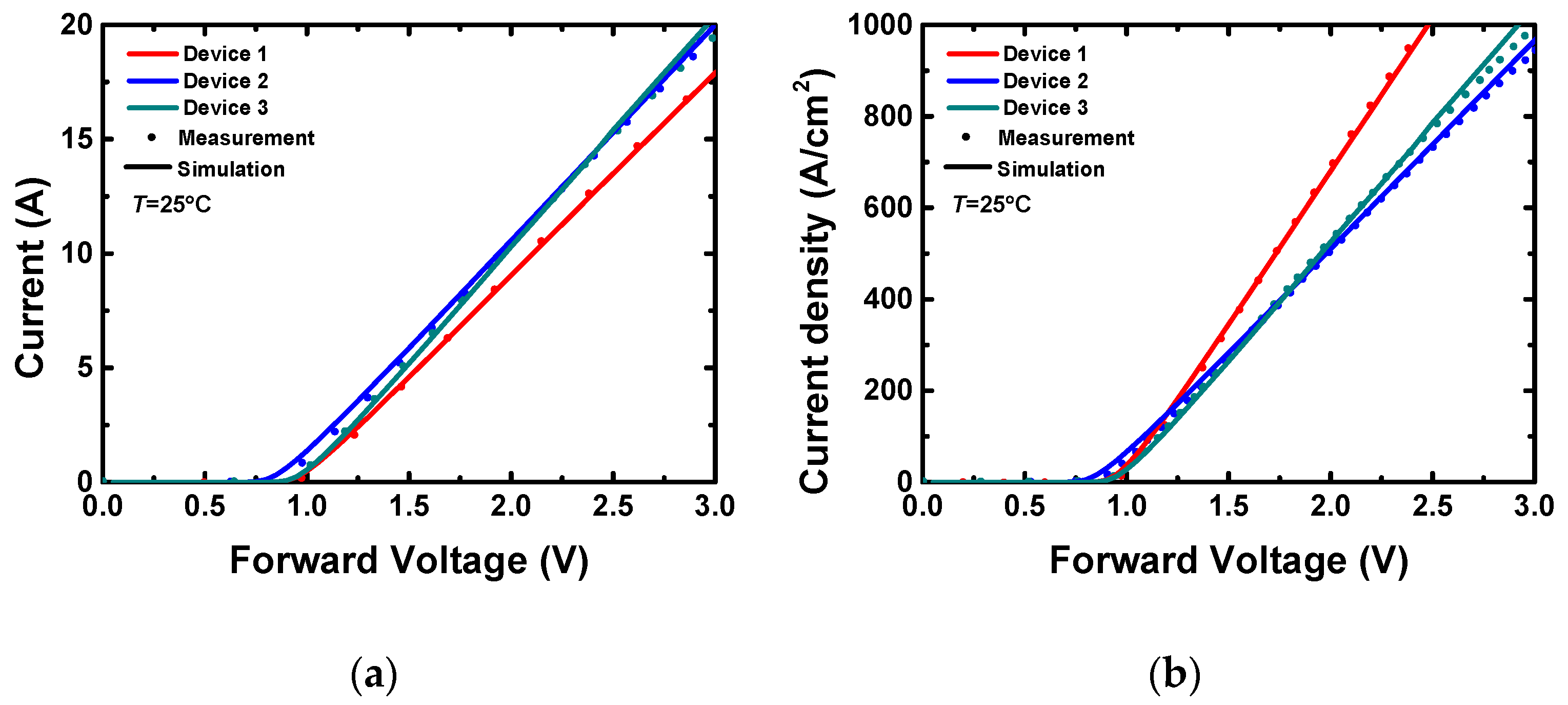

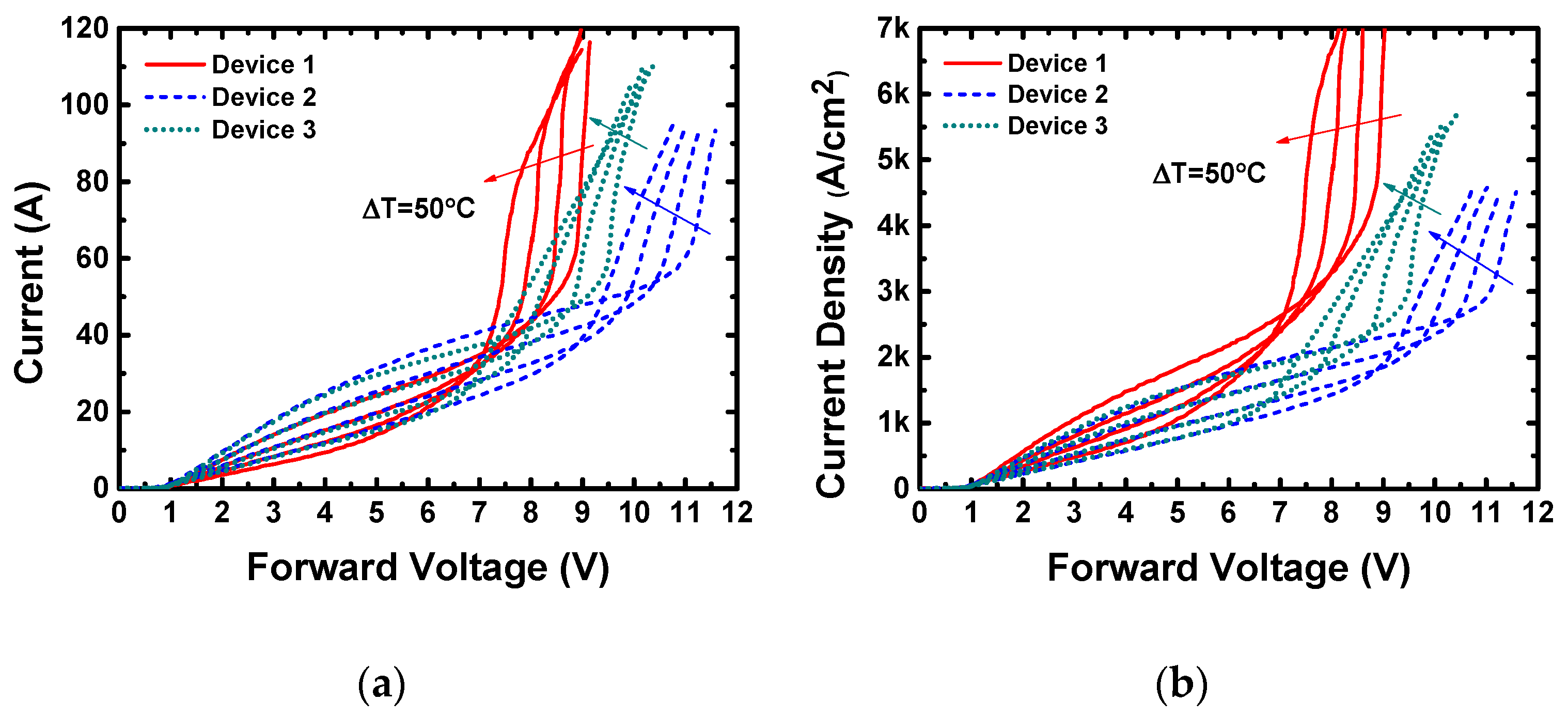

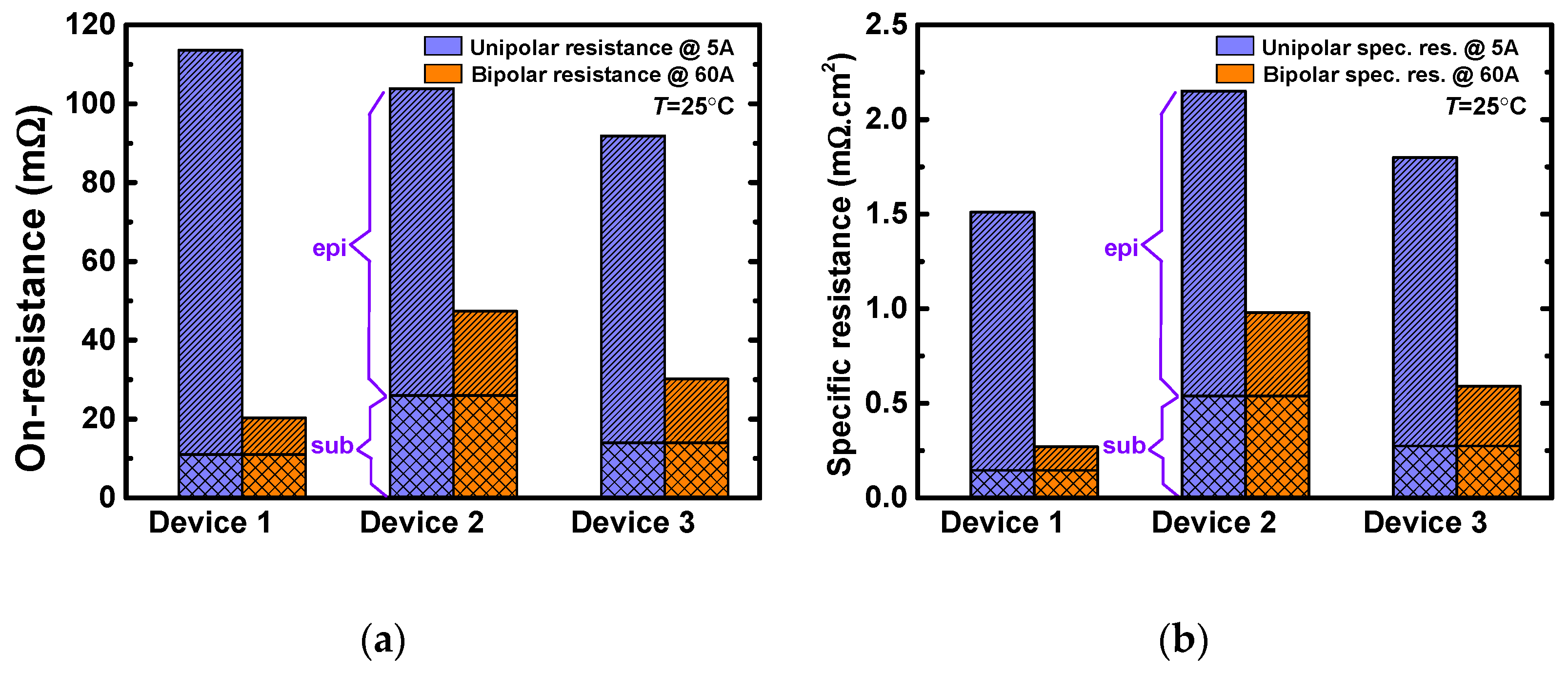

3.1. Simulated and Measured Results of the Forward Characteristics

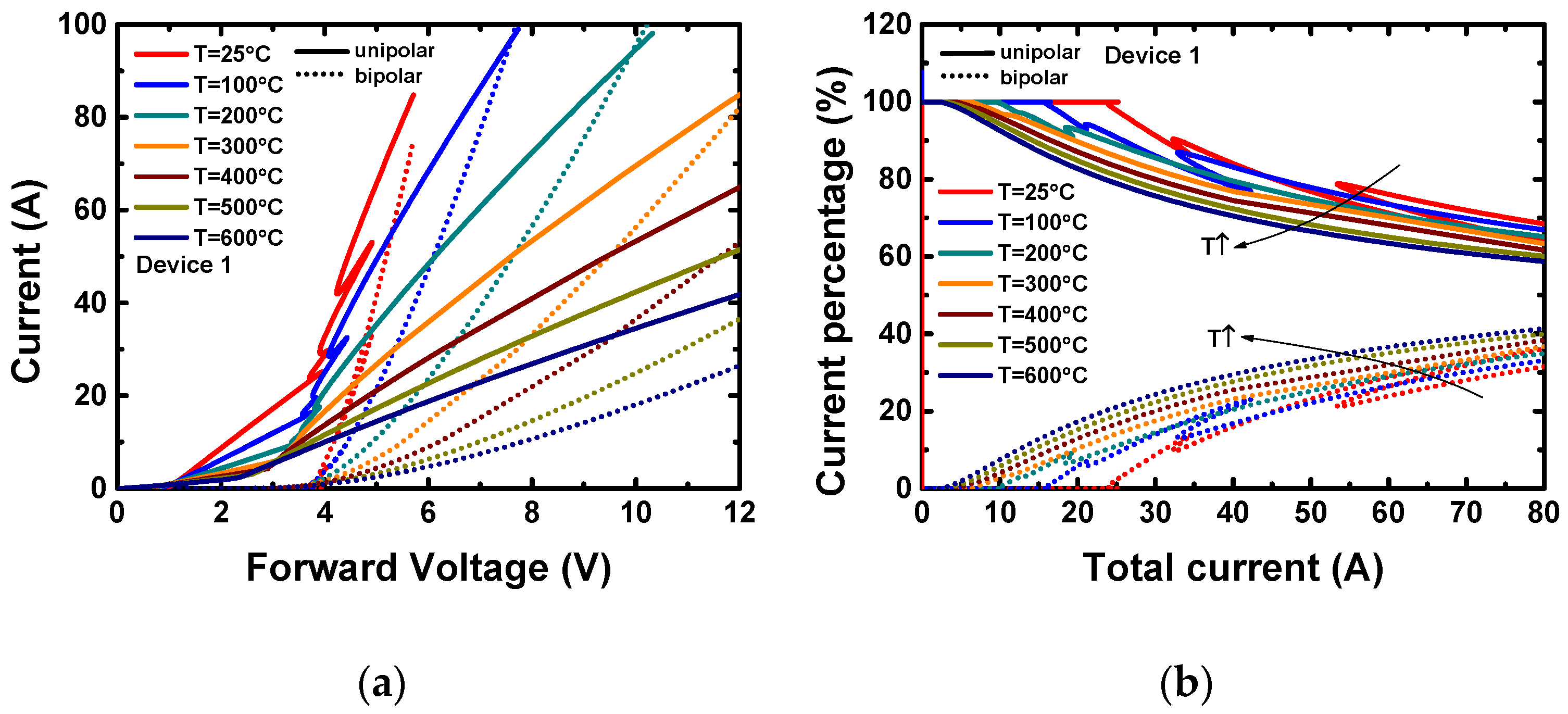

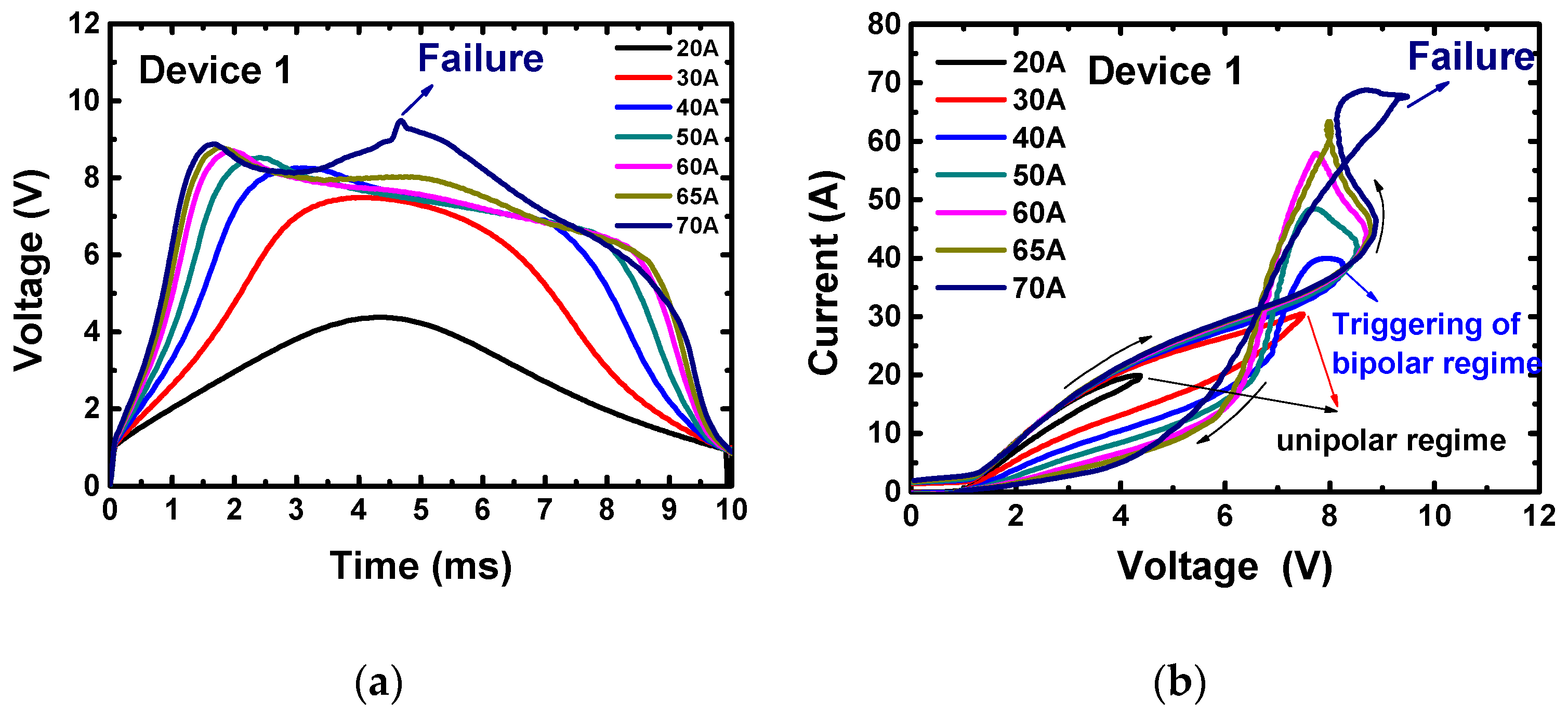

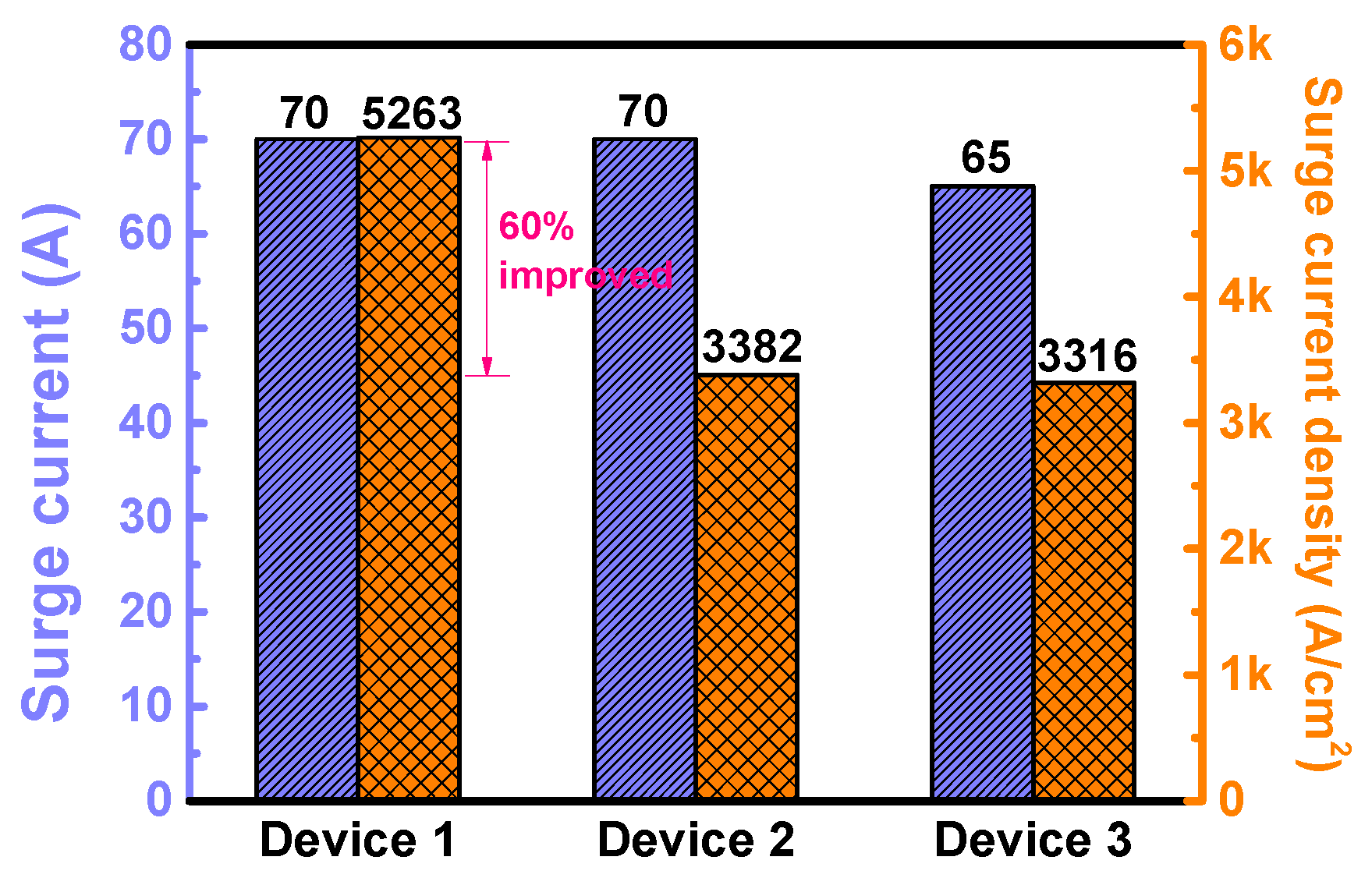

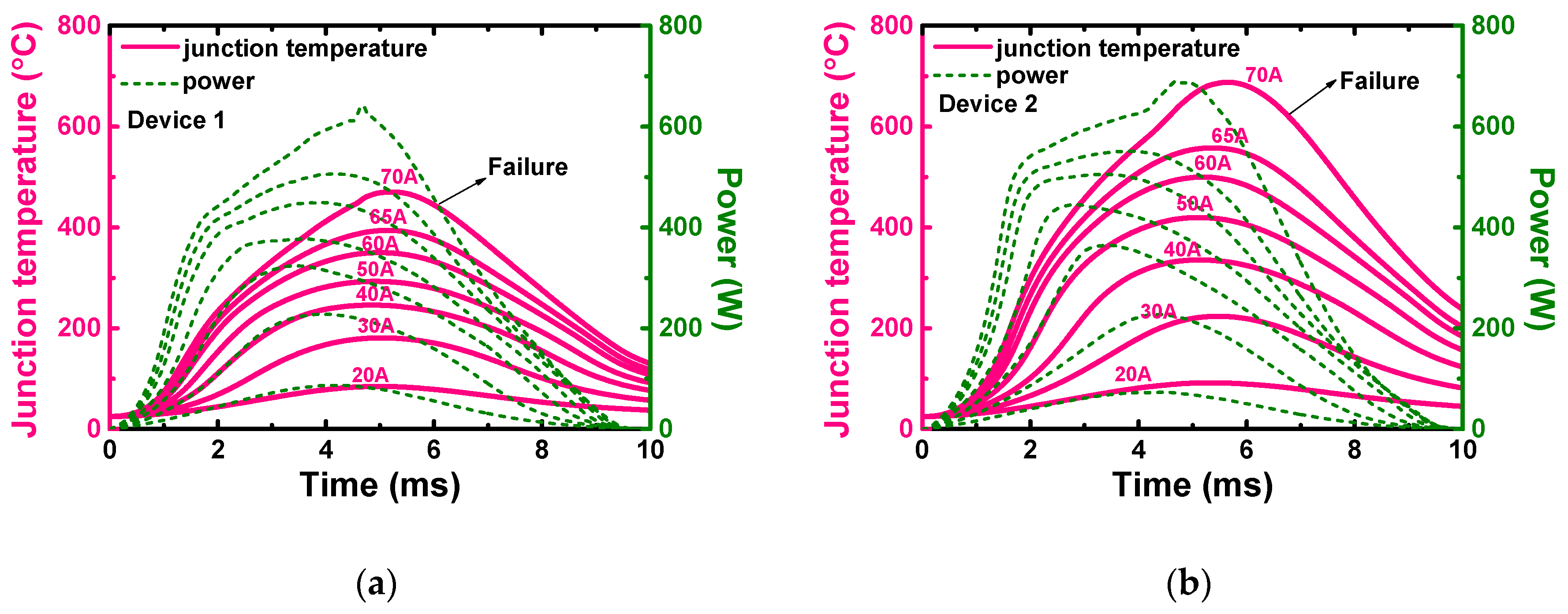

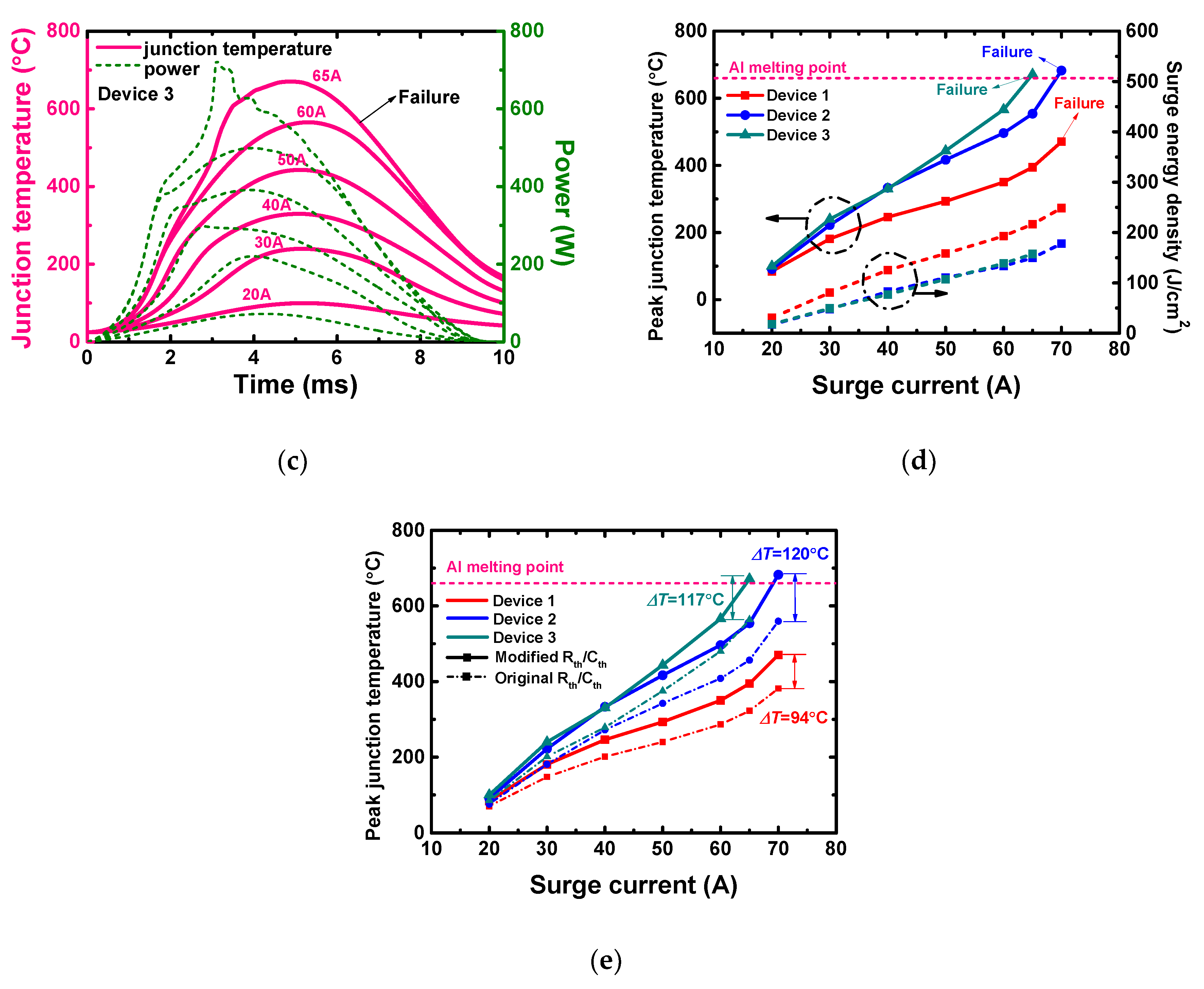

3.2. Surge Current Capabilities

4. Discussion

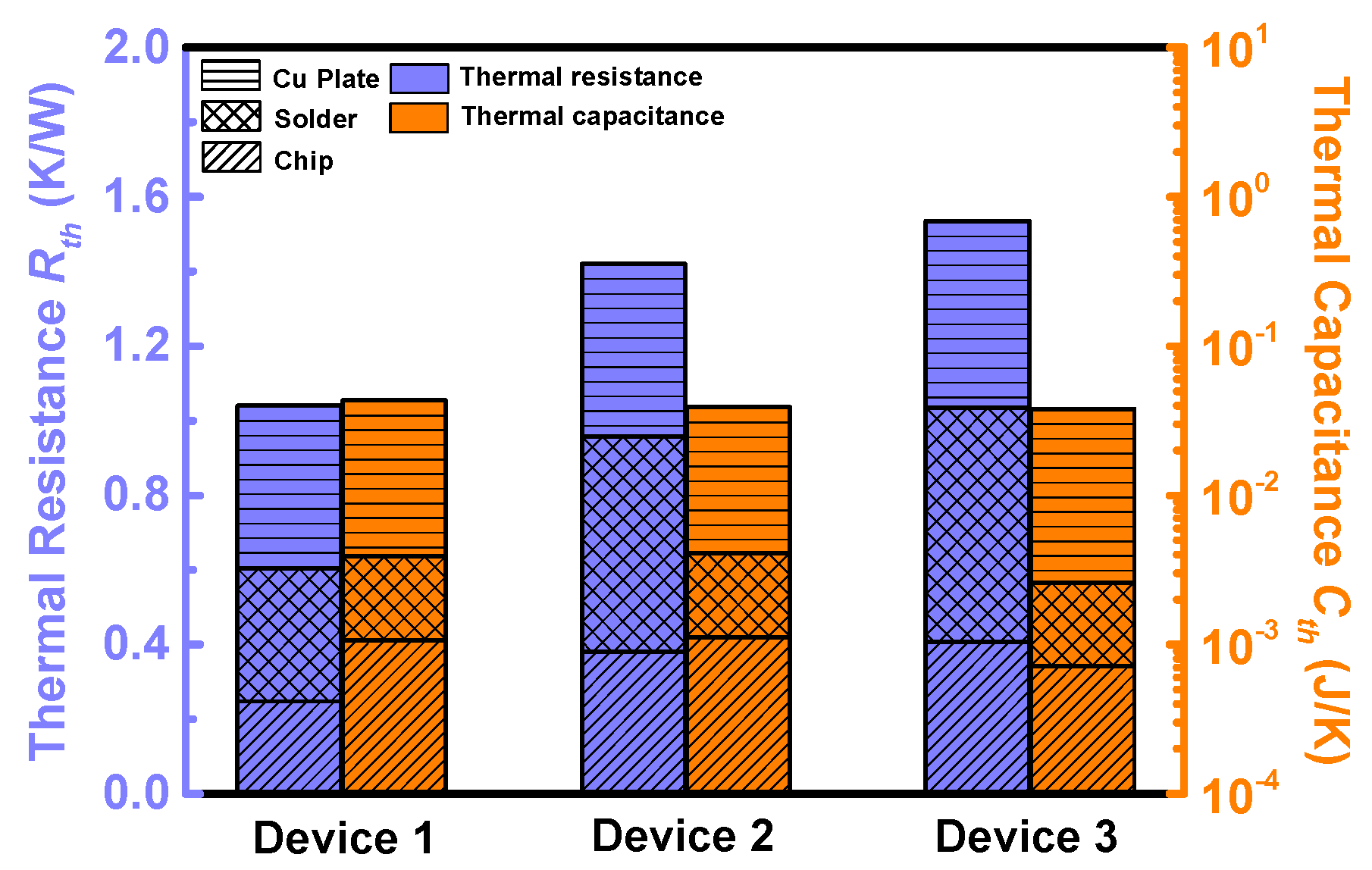

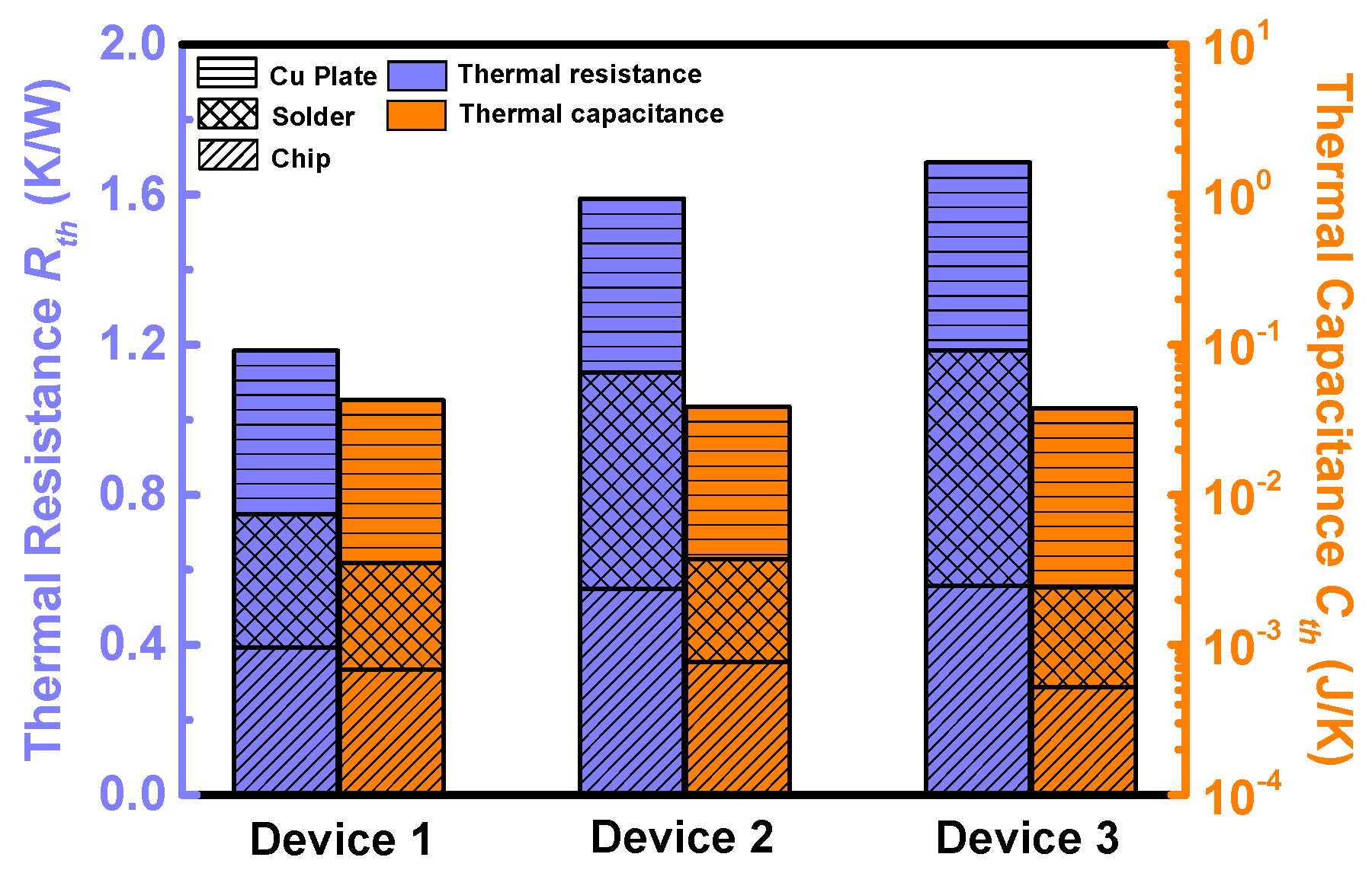

4.1. Thermal Impedance Measurement

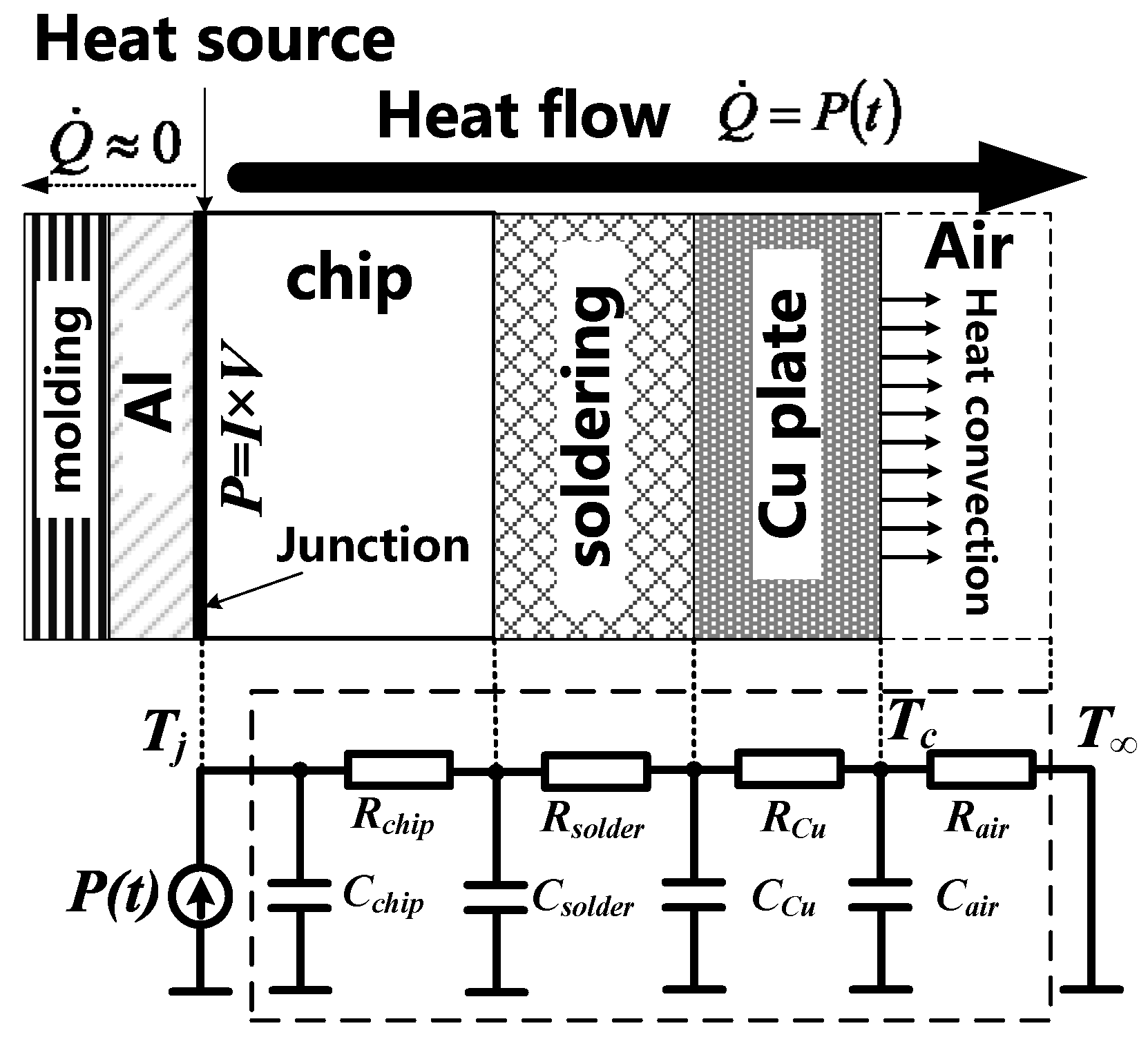

4.2. Thermal RC Model for Junction Temperature Calculation

4.3. Analysis

5. Conclusions

Supplementary Materials

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

Appendix A

Appendix B

References

- Singh, R.; Cooper, J.A.; Melloch, M.R.; Chow, T.P.; Palmour, J.W. SiC power Schottky and PiN diodes. IEEE Trans. Electron Dev. 2002, 49, 665–672. [Google Scholar] [CrossRef]

- Morisette, D.T.; Cooper, J.A.; Melloch, M.R.; Dolny, G.M.; Shenoy, P.M.; Zafrani, M.; Gladish, J. Static and dynamic characterization of large-area high-current-density SiC Schottky diodes. IEEE Trans. Electron Dev. 2001, 48, 349–352. [Google Scholar] [CrossRef]

- Bjoerk, F.; Hancock, J.; Treu, M.; Rupp, R.; Reimann, T. 2nd generation 600V SiC Schottky diodes use merged pn/Schottky structure for surge overload protection. In Proceedings of the 21th Annual IEEE Applied Power Electronics Conference and Exposition (APEC’ 06), Dallas, TX, USA, 19–23 March 2006. [Google Scholar] [CrossRef]

- Lutz, J.; Baburske, R. Some aspects on ruggedness of SiC power devices. Microelectron. Reliab. 2014, 54, 49–56. [Google Scholar] [CrossRef]

- Kimoto, T.; Yamada, K.; Niwa, H.; Suda, J. Promise and challenges of high-voltage SiC bipolar power devices. Energies 2016, 9, 908. [Google Scholar] [CrossRef] [Green Version]

- Kimoto, T.; Niwa, H.; Kaji, N.; Kobayashi, T.; Zhao, Y.; Mori, S.; Aketa, M. Progress and future challenges of SiC power devices and process technology. In Proceedings of the IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2–6 December 2017; pp. 9.5.1–9.5.4. [Google Scholar] [CrossRef]

- Friedrichs, P. SiC based power semiconductor in applications - aspects and prospects. In Proceedings of the International Power Electronics Conference (IPEC-Niigata 2018—ECCE Asia), Niigata, Japan, 20–24 May 2018; pp. 3584–3587. [Google Scholar] [CrossRef]

- Rupp, R.; Treu, M.; Voss, S.; Bjork, F.; Reimann, T. 2nd generation SiC Schottky diodes: A new benchmark in SiC device ruggedness. In Proceedings of the International Symposium on Power Semiconductor Devices and IC’s (ISPSD), Naples, Italy, 4–8 June 2006; pp. 1–4. [Google Scholar] [CrossRef]

- Rupp, R.; Gerlach, R.; Kabakow, A.; Schörner, R.; Hecht, C.; Elpelt, R.; Draghici, M. Avalanche behaviour and its temperature dependence of commercial SiC MPS diodes: Influence of design and voltage class. In Proceedings of the International Symposium on Power Semiconductor Devices and IC’s (ISPSD), Waikoloa, HI, USA, 15–19 June 2014; pp. 67–70. [Google Scholar] [CrossRef]

- Palanisamy, S.; Kowalsky, J.; Lutz, J.; Basler, T.; Rupp, R.; Moazzami-Fallah, J. Repetitive surge current test of SiC MPS diode with load in bipolar regime. In Proceedings of the International Symposium on Power Semiconductor Devices and IC’s (ISPSD), Chicago, IL, USA, 13–17 May 2018; pp. 367–370. [Google Scholar] [CrossRef]

- Banu, V.; Soler, V.; Montserrat, J.; Millán, J.; Godignon, P. Power cycling analysis method for high-voltage SiC diodes. Microelectron. Reliab. 2016, 64, 429–433. [Google Scholar] [CrossRef]

- Friedrichs, P. SiC power devices as enabler for high power density - aspects and prospects. Mater. Sci. Forum 2014, 778–780, 1104–1109. [Google Scholar] [CrossRef]

- Draghici, M.; Rupp, R.; Gerlach, R.; Zippelius, B. A new 1200V SiC MPS diode with improved performance and ruggedness. Mater. Sci. Forum 2015, 821–823, 608–611. [Google Scholar] [CrossRef]

- Elpelt, R.; Draghici, M.; Gerlach, R.; Rupp, R.; Schörner, R. SiC MPS devices: One etep closer to the ideal diode. Mater. Sci. Forum 2018, 924, 609–612. [Google Scholar] [CrossRef]

- Hefner, A.; Berning, D.; Lai, J.S.; Liu, C.; Singh, R. Silicon carbide merged PiN Schottky diode switching characteristics and evaluation for power supply applications. In Proceedings of the Conference Record of the 2000 IEEE Industry Applications Conference. Thirty-Fifth IAS Annual Meeting and World Conference on Industrial Applications of Electrical Energy (Cat. No.00CH37129), Rome, Italy, 8–12 October 2000; pp. 2948–2954. [Google Scholar] [CrossRef]

- Huang, Y.; Wachutka, G. Comparative study of contact topographies of 4.5kV SiC MPS diodes for optimizing the forward characteristics. In Proceedings of the International Conference on Simulation of Semiconductor Processes and Devices (SISPAD), Nuremberg, Germany, 6–8 September 2016; pp. 117–120. [Google Scholar] [CrossRef]

- Park, J.; Park, K.; Won, J.; Kim, K.; Koo, S.; Kim, S.; Mun, J. Control of pn-junction turn-on voltage in 4H-SiC merged PiN Schottky diode. Appl. Phys. Lett. 2017, 110, 142103. [Google Scholar] [CrossRef]

- Huang, Y.; Erlbacher, T.; Buettner, J.; Wachutka, G. A trade-off between nominal forward current density and surge current capability for 4.5kV SiC MPS diodes. In Proceedings of the 28th International Symposium on Power Semiconductor Devices and ICs (ISPSD), Prague, Czech, 12–16 June 2016; pp. 63–66. [Google Scholar] [CrossRef]

- Sharma, R.K.; Hazdra, P.; Popelka, S.; Mihaila, A.; Bartolf, H. Optimization of 1700V 4H-SiC JBS diode parameters. Mater. Sci. Forum 2016, 858, 782–785. [Google Scholar] [CrossRef]

- Banu, V.; Berthou, M.; Montserrat, J.; Jordà, X.; Godignon, P. Impact of layout on the surge current robustness of 1.2 KV SiC diodes. In Proceedings of the International Semiconductor Conference (CAS), Sinaia, Romania, 11–14 October 2017; pp. 147–150. [Google Scholar] [CrossRef]

- Wu, J.; Ren, N.; Wang, H.; Sheng, K. 1.2-kV 4H-SiC merged PiN Schottky diode with improved surge current capability. IEEE J. Emerg. Sel. Top. Power Electron. 2019, 7, 1496–1504. [Google Scholar] [CrossRef]

- Ren, N.; Wu, J.; Liu, L.; Sheng, K. Improving surge current capability of SiC merged PiN Schottky diode by adding plasma spreading layers. IEEE Trans. Power Electron. 2020. (early access). [Google Scholar] [CrossRef]

- Heinze, B.; Lutz, J.; Neumeister, M.; Rupp, R.; Holz, M. Surge current ruggedness of silicon carbide Schottky- and merged-PiN-Schottky diodes. In Proceedings of the 20th International Symposium on Power Semiconductor Devices and IC’s, Orlando, FL, USA, 18–22 May 2008; pp. 245–248. [Google Scholar] [CrossRef]

- Brunt, E.V.; Barbieri, T.; Barkley, A.; Solovey, J.; Richmond, J.; Hull, B. Surge current failure mechanisms in 4H-SiC JBS rectifiers. In Proceedings of the International Symposium on Power Semiconductor Devices and IC’s (ISPSD), Chicago, IL, USA, 13–17 May 2018; pp. 415–418. [Google Scholar] [CrossRef]

- Huang, X.; Wang, G.; Lee, M.C.; Huang, A.Q. Reliability of 4H-SiC SBD/JBS diodes under repetitive surge current stress. In Proceedings of the 2012 IEEE Energy Conversion Congress and Exposition (ECCE), Raleigh, NC, USA, 15–20 September 2012; pp. 2245–2248. [Google Scholar] [CrossRef]

- Fichtner, S.; Frankeser, S.; Lutz, J.; Rupp, R.; Basler, T.; Gerlach, R. Ruggedness of 1200 V SiC MPS diodes. Microelectron. Reliab. 2015, 55, 1677–1681. [Google Scholar] [CrossRef]

- Palanisamy, S.; Fichtner, S.; Lutz, J.; Basler, T.; Rupp, R. Various structures of 1200V SiC MPS diode models and their simulated surge current behavior in comparison to measurement. In Proceedings of the International Symposium on Power Semiconductor Devices and IC’s (ISPSD), Prague, Czech Republic, 12–16 June 2016. [Google Scholar] [CrossRef]

- Palanisamy, S.; Yoganath, G.V.; Zeng, G.; Lutz, J.; Kowalsky, J.; Basler, T. Temperature determination of SiC MPS diodes during surge current event with measurement and simulation. In Proceedings of the 2019 21st European Conference on Power Electronics and Applications (EPE ’19 ECCE Europe), Genova, Italy, 3–5 September 2019; pp. 1–9. [Google Scholar] [CrossRef]

- Zhong, W.; Tang, Y.; Li, C.; Chen, H.; Zhang, Y.; Bai, Y.; Liu, X. Electro-thermal analysis of 1.2 kV-100 A SiC JBS diodes under surge current stress. In Proceedings of the 2019 16th China International Forum on Solid State Lighting & 2019 International Forum on Wide Bandgap Semiconductors China (SSLChina: IFWS), Shenzhen, China, 25–27 November 2019; pp. 22–25. [Google Scholar] [CrossRef]

- Starzak, Ł.; Stefanskyi, A.; Zubert, M.; Napieralski, A. Improvement of an electro-thermal model of SiC MPS diodes. IET Power Electron. 2018, 11, 660–667. [Google Scholar] [CrossRef]

- Lakrim, A.; Tahri, D. SiC merged PiN and Schottky (MPS) power diodes electrothermal modeling in SPICE. Int. J. Energy Power Eng. 2014, 8, 1390–1394. [Google Scholar] [CrossRef]

- Starzak, Ł.; Zubert, M.; Janicki, M.; Torzewicz, T.; Napieralska, M.; Jablonski, G.; Napieralski, A. Behavioral approach to SiC MPS diode electrothermal model generation. IEEE Trans. Electron Dev. 2013, 60, 630–638. [Google Scholar] [CrossRef]

- Du, Y.; Rodrigues, R.; Jiang, T. A measurement method to extract the transient junction temperature profile of power semiconductors at surge conditions. In Proceedings of the IEEE Energy Conversion Congress and Exposition (ECCE), Cincinnati, OH, USA, 1–5 October 2017; pp. 2512–2519. [Google Scholar] [CrossRef]

- Bouguezzi, S.; Ayadi, M.; Ghariani, M. Developing a simple analytical thermal model for discrete semiconductor in operating condition. Appl. Therm. Eng. 2016, 100, 155–169. [Google Scholar] [CrossRef]

- Rupp, R.; Gerlach, R.; Kabakow, A. Current distribution in the various functional areas of a 600 V SiC MPS diode in forward operation. Mater. Sci. Forum 2012, 717–720, 929–932. [Google Scholar] [CrossRef]

- Ruff, M.; Mitlehner, H.; Helbig, R. SiC devices: Physics and numerical simulation. IEEE Trans. on Electron Dev. 1994, 41, 1040–1054. [Google Scholar] [CrossRef]

- Li, H.; Wang, J.; Ren, N.; Xu, H.; Sheng, K. Investigation of 1200 V SiC MOSFETs’ surge reliability. Micromachines 2019, 10, 485. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- JEDEC Standard JESD 51-14. JEDEC Standard for Transient Dual Interface Test Method for the Measurement of the Thermal Resistance Junction to Case of Semiconductor Devices With Heat Flow Trough A Single Path; Jedec Solid State Technology Association: Arlington, VA, USA, December 2010. [Google Scholar]

- Farkas, G.; Hara, T.; Rencz, M. 6-Thermal transient testing. In Wide Bandgap Power Semiconductor Packaging: Materials, Components, and Reliability, 1st ed.; Woodhead Publishing, Elsevier Ltd.: Duxford, UK, 2018. [Google Scholar] [CrossRef]

- Luo, Y. Structure function based thermal resistance & thermal capacitance measurement for electronic system. In Proceedings of the 2010 IEEE CPMT Symposium Japan, Tokyo, Japan, 24–26 August 2010. [Google Scholar] [CrossRef]

- Szekely, V.; Bien, T.V. Fine structure of heat flow path in semiconductor devices: A measurement and identification method. Solid Slate Electron. 1988, 31, 1363–1368. [Google Scholar] [CrossRef]

- Zhu, L.; Chow, T.P. Analytical modeling of high-voltage 4H-SiC junction barrier Schottky (JBS) rectifiers. IEEE Trans. Electron Dev. 2008, 55, 1857–1863. [Google Scholar] [CrossRef]

- Ren, N.; Wang, J.; Sheng, K. Design and experimental study of 4H-SiC trenched junction barrier Schottky diodes. IEEE Trans. Electron Dev. 2014, 61, 2459–2465. [Google Scholar] [CrossRef]

| Variable | Definition | Variable | Definition |

|---|---|---|---|

| Nepi | Doping concentration of the epitaxy layer | Cchip | Steady thermal capacitance of the chip |

| tp | Depth of the P+ region | Rch | Channel thermal resistance |

| tepi | Thickness of the epitaxy layer | Cch | Channel thermal capacitance |

| tsub | Thickness of the substrate | Rsp | Spreading thermal resistance |

| Aact | Area of the active region | Csp | Spreading thermal capacitance |

| Achip | Area of the chip | Rd | Drift thermal resistance |

| Acell | Area of the calculation cell | Cd | Drift thermal capacitance |

| m | Number of the calculation cell, m = Aact/Acell | Rsub | Substrate thermal resistance |

| κ | Thermal conductivity of the chip | Csub | Substrate thermal capacitance |

| CV | Specific volumetric heat capacity | Rtot | Total thermal resistance of the device for junction temperature calculation |

| θ | Current path spreading angle | Ctot | Total thermal capacitance of the device for junction temperature calculation |

| Rchip | Steady thermal resistance of the chip | T | Temperature |

| Cross-Section View of Chips | Dev | tepi (μm) | Nepi (cm−3) | tsub (μm) | Aact (mm2) | Layout Design | P+ Ratio |

|---|---|---|---|---|---|---|---|

| 1 | 8.0 | 6.0 × 1015 | 102 | 1.33 | Hexagon | 35% |

| 2 | 12.0 | 6.6 × 1015 | 358 | 2.07 | Dash line | 18% | |

| 3 | 8.0 | 6.0 × 1015 | 192 | 1.96 | Stripe | 54% |

| Model Classification | Models Used in Simulation | Description |

|---|---|---|

| Carrier statistics models | fermi-dirac | Energy state occupation probability model with fermi-dirac statics |

| bgn (Bandgap narrowing) | Doping-dependent bandgap width model | |

| Carrier mobility model | analytical | Doping- and temperature- dependent mobility model |

| fldmob | Electrical-field-dependent mobility model | |

| Recombination model | Shockley-Read-Hall (SRH) | Indirect recombination mechanism with two carriers and a recombination center involved. Important for SiC. |

| Auger | Direct recombination mechanism with three carriers involved. Important at high current densities. |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Wu, J.; Ren, N.; Guo, Q.; Sheng, K. A Comparative Study of Silicon Carbide Merged PiN Schottky Diodes with Electrical-Thermal Coupled Considerations. Materials 2020, 13, 2669. https://doi.org/10.3390/ma13112669

Wu J, Ren N, Guo Q, Sheng K. A Comparative Study of Silicon Carbide Merged PiN Schottky Diodes with Electrical-Thermal Coupled Considerations. Materials. 2020; 13(11):2669. https://doi.org/10.3390/ma13112669

Chicago/Turabian StyleWu, Jiupeng, Na Ren, Qing Guo, and Kuang Sheng. 2020. "A Comparative Study of Silicon Carbide Merged PiN Schottky Diodes with Electrical-Thermal Coupled Considerations" Materials 13, no. 11: 2669. https://doi.org/10.3390/ma13112669