Abstract

We investigate the effect of applied gate and drain voltages on the charge transport properties in a zinc oxide (ZnO) nanowire field effect transistor (FET) through temperature- and voltage-dependent measurements. Since the FET based on nanowires is one of the fundamental building blocks in potential nanoelectronic applications, it is important to understand the transport properties relevant to the variation in electrically applied parameters for devices based on nanowires with a large surface-to-volume ratio. In this work, the threshold voltage shift due to a drain-induced barrier-lowering (DIBL) effect was observed using a Y-function method. From temperature-dependent current-voltage (I-V) analyses of the fabricated ZnO nanowire FET, it is found that space charge-limited conduction (SCLC) mechanism is dominant at low temperatures and low voltages; in particular, variable-range hopping dominates the conduction in the temperature regime from 4 to 100 K, whereas in the high-temperature regime (150–300 K), the thermal activation transport is dominant, diminishing the SCLC effect. These results are discussed and explained in terms of the exponential distribution and applied voltage-induced variation in the charge trap states at the band edge.

1. Introduction

Zinc oxide (ZnO) has received considerable interest over the past few decades as a promising material for a variety of applications in electronics, optics, and photonics because it exhibits a direct wide bandgap (~3.37 eV), a large exciton binding energy (60 meV), a variety of nanoscale forms, and piezoelectricity [1,2]. Recently, ZnO nanostructures have attracted much attention to the fields of nanoscale electronic and optoelectronic devices, such as sensors [3], solar cells [4], energy harvesting devices [5], light-emitting diodes [6], and especially field effect transistors (FETs) [7].

Since the FET based on nanowires is one of the fundamental building blocks in potential nanoelectronic applications, it is very important to understand charge transport behaviors in nanowire-based transistors. The electrical properties of nanowire-based FET devices sensitively depend on their size and shape, defects and impurities, and surface states or defects [7,8,9]. Moreover, it has been generally accepted that the contacts between the nanowire and the metal electrodes play also an important role in the charge transport properties of nanowire-based FETs due to their large surface-to-volume ratio coupled with unique geometry [10,11,12]. For example, Lee and coworkers reported the distinct electrical transport features of FETs made from ZnO nanowires with two different types of geometric properties: one type consisted of corrugated nanowires with a relatively smaller diameter and higher density of surface states or defects, and the other type involved smooth ZnO nanowires with a relatively larger diameter and lower density of surface states or defects [7]. Lord et al. [10] showed that the electrical transport behavior of nanocontacts between ZnO nanowires and Au metals can switch from Schottky to Ohmic depending on the size of the metal contact in relation to the nanowire diameter. Jo et al. [11] and He et al. [12] demonstrated the influence of the contact resistance on the electrical properties in In2O3 and ZnO nanowires, respectively.

In addition to structural geometry effects associated with nanowires and devices, importantly, a better understanding of the charge transport properties relevant to the variation in the electrical parameters actually applied to devices based on nanowires is required for the application of new nanoscale electronics and devices. Recently, several studies on the effect of bias stress in ZnO nanowire FETs have been reported [13,14]. Ju et al. [13] reported the effects of bias stress (gate or drain stress) on the stability of the ZnO nanowire FET with a self-assembled organic gate insulator. Choe et al. [14] investigated the threshold voltage instability induced by gate bias stress in ZnO nanowire FETs, which is associated with the trapping of charges in the interface trap sites located in interfaces between the nanowire and dielectric layer.

Herein, we report the effect of applied gate and drain voltages on the charge transport properties in a ZnO nanowire FET with a back-gated configuration. To do this, temperature-dependent current-voltage (I-V) measurements from 4 to 300 K were carried out. Using a Y-function method, we find that the threshold voltage (Vth) shifts to a negative gate bias direction due to the drain-induced barrier lowering (DIBL) effect, leading to increasing carrier concentration in the channel. The temperature-dependent I-V measurements show that the transport behavior of the fabricated ZnO nanowire FET is governed by space charge-limited conduction (SCLC) at low temperatures and low voltages, in particular by variable-range hopping (VRH) conduction mechanism in the temperature regime from 4 to 100 K, and by the thermal activation transport at the high-temperature regime (150–300 K).

2. Materials and Methods

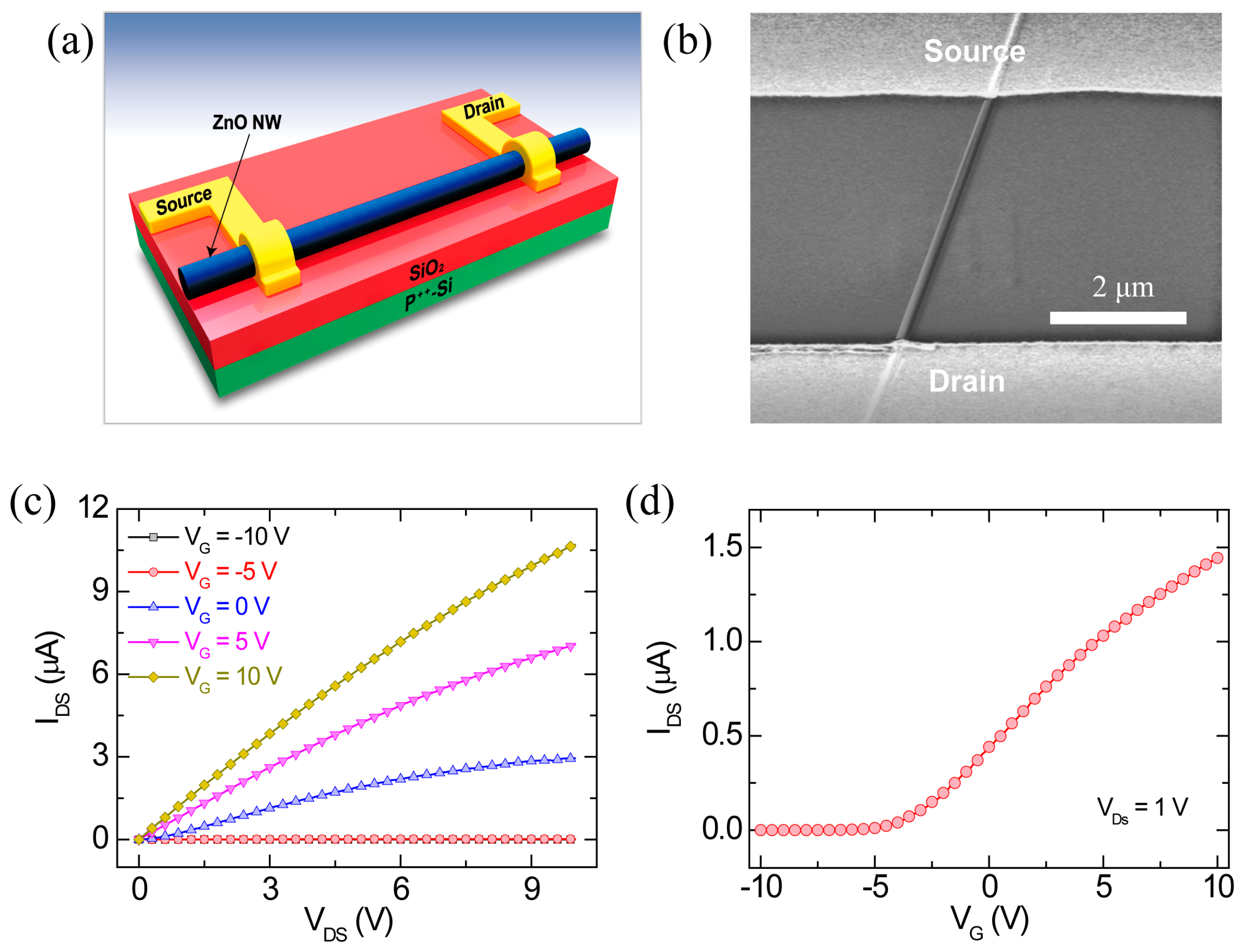

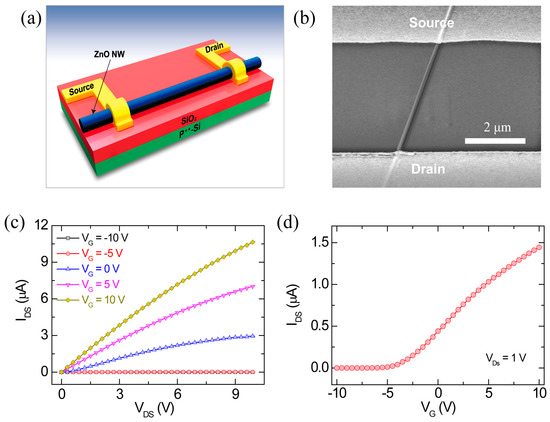

High-density ZnO nanowires were grown on Au-coated c-plane sapphire substrates by a vapor transport method without using metal-catalysts. To grow the high-density ZnO nanowires, a mixed source of ZnO powder (99.995%) and graphite powder (99%) in a ratio of 1:1 was blended with ethanol. The source materials and substrates were placed in an alumina boat, which was then loaded into the center of a horizontal tube furnace. The furnace was heated at a rate of 35 °C/min and held at approximately 920 °C for 40–60 min. During the whole growth process, a mixed gas of Ar and O2 with mixture ratio of 99:1 was maintained and then the flow rate of the mixed gas was 20 SCCM (standard cubic centimeters per minute) and the pressure of the furnace was kept at approximately 600 Torr. When the furnace was allowed to cool to room temperature naturally, a large amount of a white product was grown on the surface of the Au-coated c-plane sapphire substrate (not shown). Structural characterization of the ZnO nanowires vertically grown on the sapphire substrate was performed using field emission scanning electron microscope (FESEM) and transmission electron microscope (TEM), as shown in Figure S1. The energy dispersive x-ray spectroscopy (EDS) of the as-grown ZnO nanowires shows compositional elements (the inset in Figure S1a). The TEM images (Figure S1c–e) indicate that the growth direction of the ZnO nanowires is along the c-axis. A selected area electron diffraction (SAED) pattern confirms the (0001) growth direction (the inset of Figure S1d). The photoluminescence (PL) measurement of the ZnO nanowires at room temperature was examined by utilizing a FEX system (NOST, Seongnam-si, Korea) with a He–Cd laser (325 nm) as an incident excitation source (Figure S2). Next, the ZnO nanowires that were grown on the Au-coated sapphire substrate were transferred onto a highly-doped silicon wafer with 100 nm-thick thermally grown silicon dioxide (SiO2) by dropping and drying a liquid suspension of ZnO nanowires for the fabrication of FET devices. For all the fabricated ZnO nanowire FETs, source and drain electrodes consisting of Ti (100 nm)/Au (80 nm) were deposited by an electron beam evaporator, as shown in Figure 1a. The distance between the source and drain electrodes is approximately 4 μm (Figure 1b). The electrical properties of the nanowire FET device were characterized using a semiconductor characterization system (Keithley 4200-SCS, Keithley, Cleveland, OH, USA) at a temperature range of 4–300 K. It should be noted that even though the nanowires are synthesized in the same conditions, there can be wire-to-wire or device-to-device variations in the electrical and optical properties, which strongly depend on the dimension (diameter and length, etc.) and surface states of the as-grown nanowires [7,15].

Figure 1.

(a) Schematic illustration of the fabricated ZnO nanowire FET with a back-gate configuration; (b) A SEM image of the fabricated ZnO nanowire FET; (c) Output characteristics (IDS-VDS) and (d) transfer characteristics (IDS-VG) at VDS = 1 V of the fabricated ZnO nanowire FET, which was measured at room temperature. The inset in (d) shows a semi-logscale IDS-VG curve at VDS = 1 V.

3. Results and Discussion

A schematic illustration and a scanning electron microscopy (SEM) image of the fabricated ZnO nanowire FET with a back-gate configuration are shown in Figure 1a,b. Figure 1c,d shows the output (IDS-VDS) and transfer (IDS-VG) characteristics of the fabricated ZnO nanowire FET with a back-gate configuration (Figure 1a,b), respectively. The fabricated ZnO nanowire FET showed typical n-type semiconductor properties and depletion-mode operation, which exhibited a nonzero current at zero gate bias and a negative threshold voltage [15].

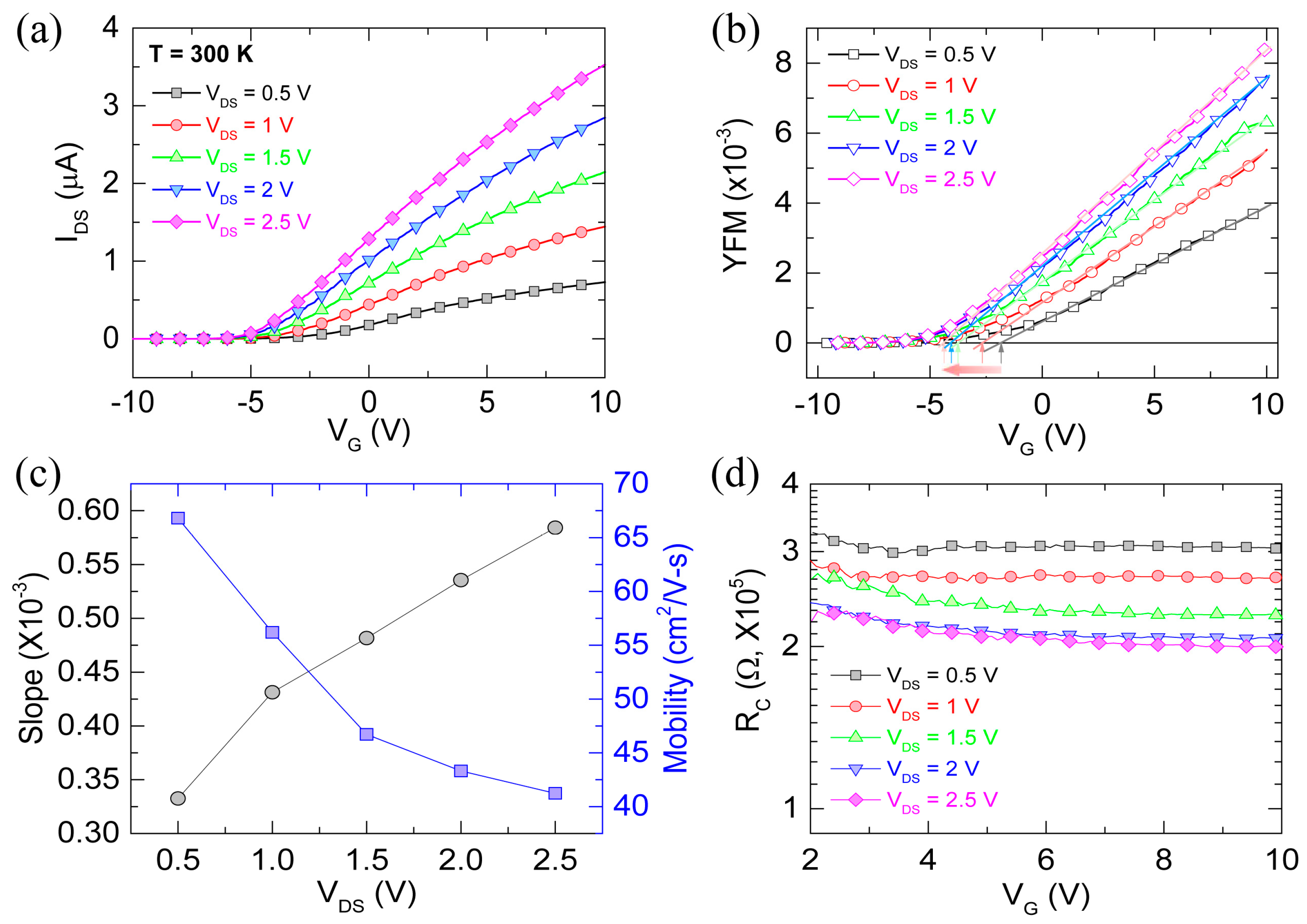

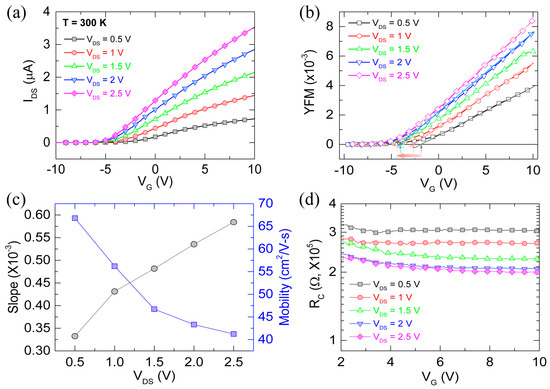

Figure 2a shows the transfer characteristics at different drain-source voltages for the fabricated ZnO nanowire FET measured at room temperature. From this, electrical characteristics were analyzed by the Y-function method (YFM) (Figure 2b), which has been widely used for contact resistance and mobility based on a straightforward analysis of the drain current (IDS) in the linear region (electron accumulation region) [16,17]. The Y-function can be obtained from the IDS-VG (Figure 2a) as follows [17],

where gm = dIDS/dVG, μ is the mobility, CG is the gate capacitance, L is the channel length, and Vth is the threshold voltage, in which μ and Vth can be determined from the slope and the VG-axis intercept of the linear region of the Y-function, respectively (Figure 2b,c). In Figure 2b, it is clearly seen that Vth shifts to a negative gate bias direction (marked by arrows) when VDS increases from 0.5 to 2.5 V, which indicates the DIBL effect [18]. This effect can reduce the Schottky barrier between source/drain electrodes and the nanowire contacts, affecting the contact resistance (RC). Using the Y-function, the RC at interfaces between source/drain electrodes and the ZnO nanowire can be calculated from the following equation [17],

where k is the slope of the linear region of the Y-function. The slopes of the linear region of the Y-function are different (Figure 2c), indicating the difference in RC [17] (Figure 2d). Importantly, the contact resistance is present at a metal-nanowire interface and can affect the electrical performance of nanowire FETs [19]. The work function difference between the ZnO and the contact metal leads to the formation of an energy barrier at the interface between the two materials, which can influence the barrier height.

Figure 2.

(a) IDS-VG curves measured at room temperature (T = 300 K) for the ZnO nanowire FET, with VDS varying from 0.5 to 2.5 V; (b) YFM value as a function of VG at different VDS values for the ZnO nanowire FET. From the linear fitting, Vth and mobility can be extracted from the VG-axis intercept and the slope, respectively. Each arrow indicates the Vth for each VDS; (c) Slope and mobility as a function of VDS extracted from linearly fitted curves in (b); (d) Contact resistance as a function of gate bias, with VDS varying from 0.5 to 2.5 V.

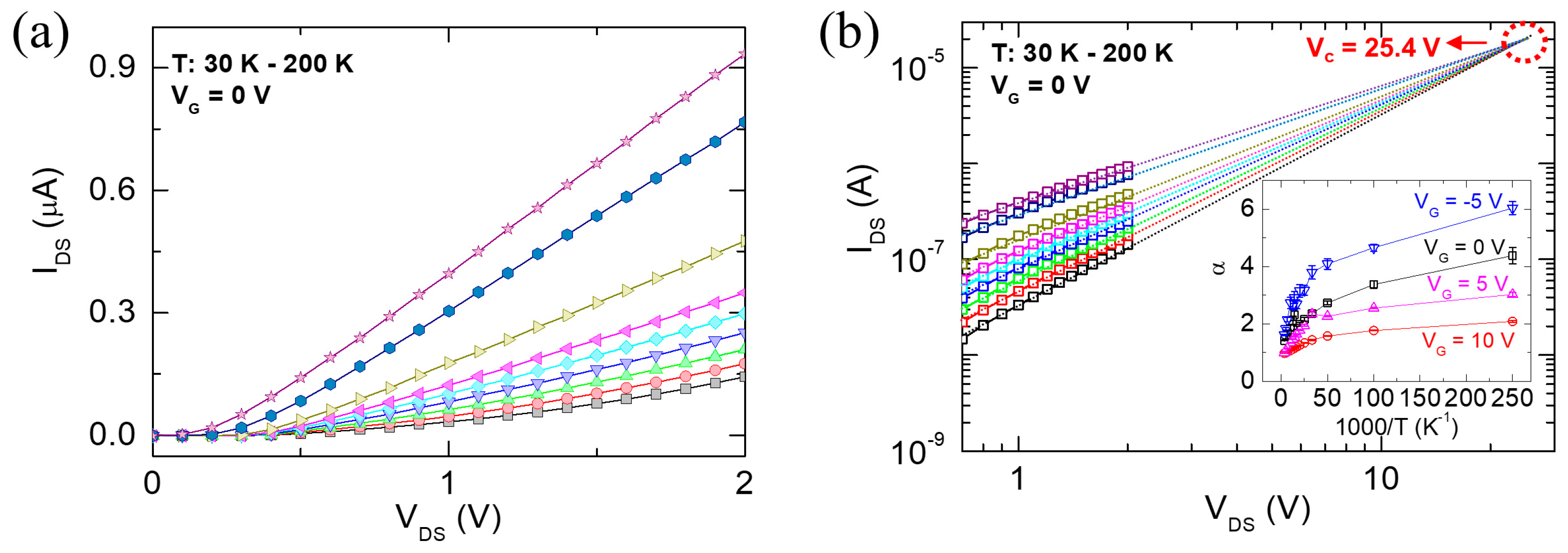

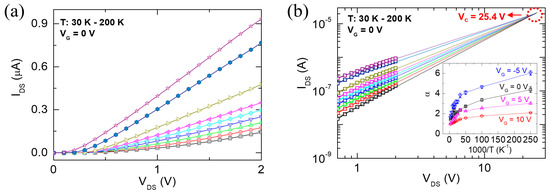

To understand the charge transport mechanism in our nanowire FET with different contact resistances, the temperature-dependent electrical measurement and analyses of the ZnO nanowire FET were examined. Figure 3a shows the IDS-VDS characteristics of the ZnO nanowire FET at different temperatures ranging from 30 to 200 K. With decreasing temperature, the IDS decreased, indicating a strong temperature dependence. In addition, the logscale IDS–VDS showed the power law relationship, I ∝ Vα, and such power law dependence with α > 2 is a characteristic feature of SCLC in a semiconductor with an exponential charge trap distribution at the band edge [19,20]. The exponents, α, were extracted from logscale IDS-VDS curves in the temperature range from 4 to 300 K at different gate biases, as shown in the inset of Figure 3b. The α values increased with decreasing temperature, exceeding 2 in the low-temperature range. This result implies the existence of trap states in the ZnO nanowire. The values reached approximately 1 in the high- temperature range due to the thermally activated electrons, resulting in deviation from SCLC. The trap densities (Nt) can be estimated by extrapolating the logscale IDS-VDS characteristics, as shown in Figure 3b. Figure 3b shows a crossover point at which the conductance was independent of the temperature. The VDS value at the crossover point is denoted as a crossover voltage (Vc) and it was approximately 25.4 V. The Vc can be expressed by [20],

where q is the electric charge, L is the channel length, ε0 is the vacuum permittivity, and εr is the relative permittivity of ZnO (~8.5). From the above equation, the calculated Nt at Vc = 25.4 V, was 1.5 × 1015 cm−3. According to previous reports [21,22], most of the trap densities arise from oxygen vacancies located on the nanowire surface rather than at the nanowire center. Therefore, the calculated Nt may correspond to the interface trap states at the metal-nanowire contacts or the nanowire-dielectric layer, which could affect the charge transport of the ZnO nanowire FET.

Figure 3.

(a) IDS-VDS curves measured at VG = 0 V and different temperatures (30–200 K) for the ZnO nanowire FET; (b) The extrapolation derived from the corresponding logscale IDS-VDS characteristics at different temperatures of (a), which provide a critical voltage (VC).

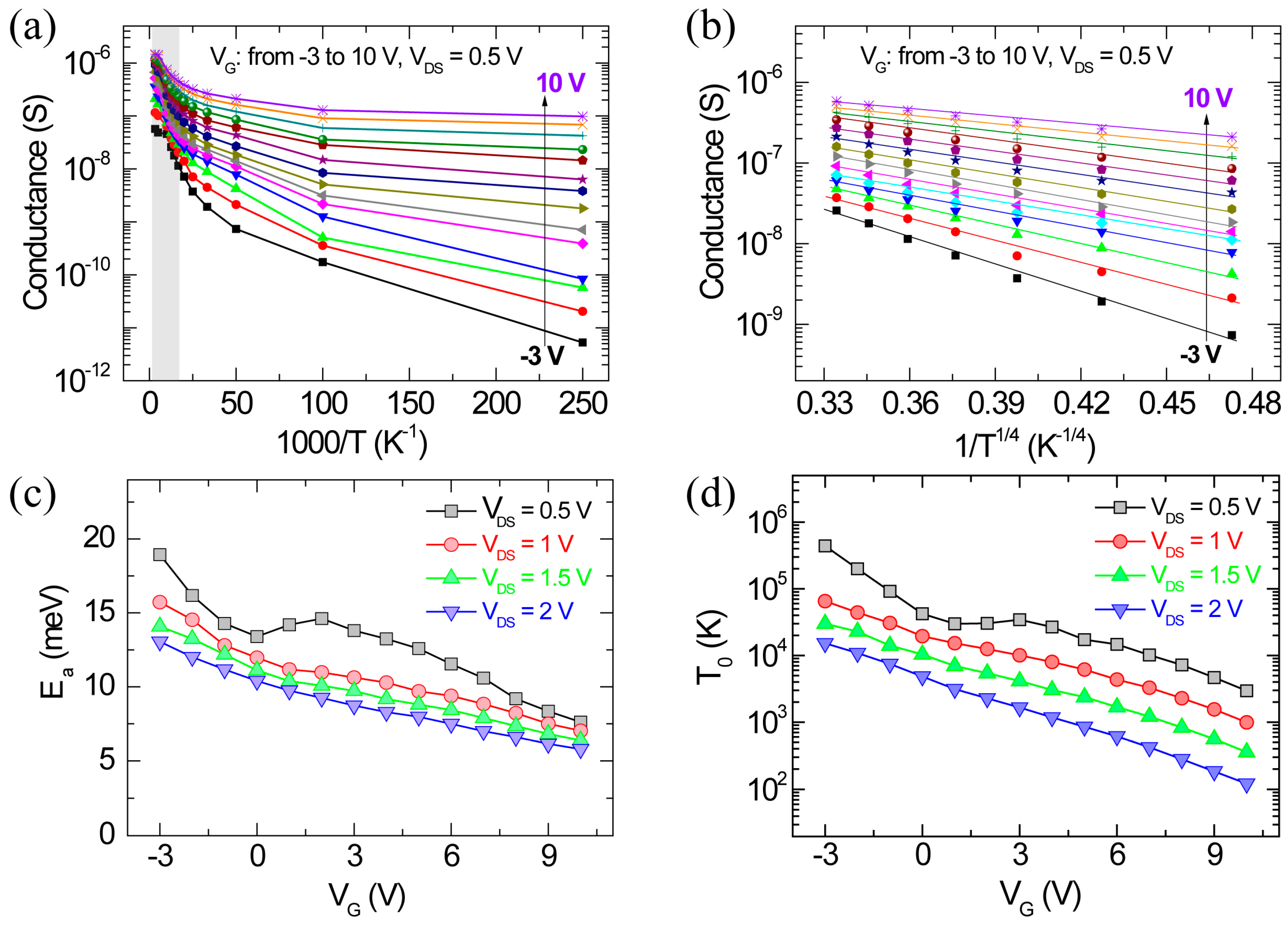

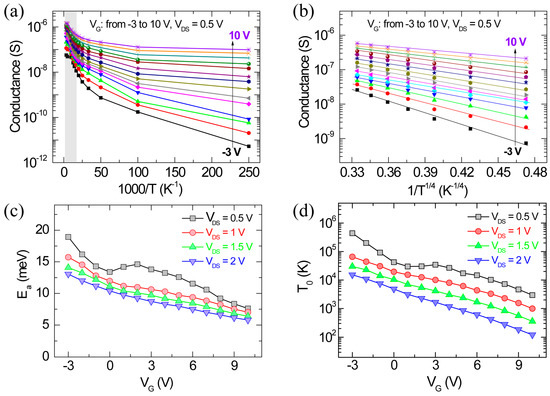

Next, we carried out analyses of the Arrhenius plots of the conductance (G) versus 1000/T at different VG values to further investigate the transport mechanism of the ZnO nanowire FET, as shown in Figure 4a,b. Two different regimes in the temperature-dependent conductance of the nanowire FET device were clearly observed at different VG values (VG from −3 to 10 V, 1 V steps), implying different charge transport mechanisms. Note that the Arrhenius plots at low VDS regime (0.5, 1, 1.5, and 2 V) were also characterized for different VG values. In the high-temperature region (150–300 K) (marked by the gray-colored region), the thermally activated carriers were dominant in the charge transport, indicating a conductance proportional to exp(−Ea/kT), which can be expressed as Equation (4) below [23,24,25].

where G and G0 are the conductance and weak temperature-dependent constant, respectively, Ea is the activation energy, kB is the Boltzmann constant, and T is the temperature. The Ea characterized by the linear region in the semi-log plot of conductance versus 1/T is shown in Figure 4a. Here, the Ea can be extracted by the linear fits in the high-temperature region in Figure 4a (marked by the gray-colored region). Figure 4c shows the extracted Ea as a function of the VG at different VDS values for the device. The Ea decreased due to the lowered Schottky barrier at the metal/semiconductor interface when the applied biases increased, including VG and VDS. In contrast, in the low-temperature region (4–100 K), the carrier conduction is mainly attributed to VRH, which exhibits charge transport through the trap states near the Fermi level. According to previous reports [23,26,27,28,29,30], the VRH conduction can be expected due to charge trapping at localized states in semiconducting nanomaterials at low applied bias and low temperature where the Fermi level lies in localized sates within a band gap. The conductance following the three-dimensional (3D) VRH mechanism can be expressed by the following equation [25,31,32],

where T0 are the characteristic characteristic temperature. Figure 4b shows that the low-temperature conductance of the device is well fitted by the 3D VRH as a function of T−1/4 at low applied bias, indicating that the conductance follows 3D VRH model well for low electric fields. From Equation (5), the values of T0, which represent how actively VRH occurs [25,31,32], were extracted, as shown in Figure 4d. As the applied biases (VG and low VDS) increased, the T0 also continuously decreased, implying reduced VRH conduction. The result might be due to the enhanced electron concentration from the lowering of the Schottky barrier. The increased electron concentration might additionally fill the trap states, leading to the reduction in hopping conduction [25,31,32]. As a result, the Ea and T0 values can be modified by the applied electric field, which is associated with the modulation of localized trap states. This trend is consistent with the results reported for semiconducting nanomaterials with localized trap states [23,30,33].

Figure 4.

(a) Arrhenius plots of the conductance (G) versus 1000/T at different gate voltages from −3 to 10 V for VDS = 0.5 V. (b) Semilogarithm plots showing the temperature dependence of conductance (G) vs 1/T1/4 fitted by Equation (5) at different gate voltages for VDS = 0.5 V. The activation energy (Ea) (c) and characteristic temperature (T0) (d) depending on the applied gate and drain voltages.

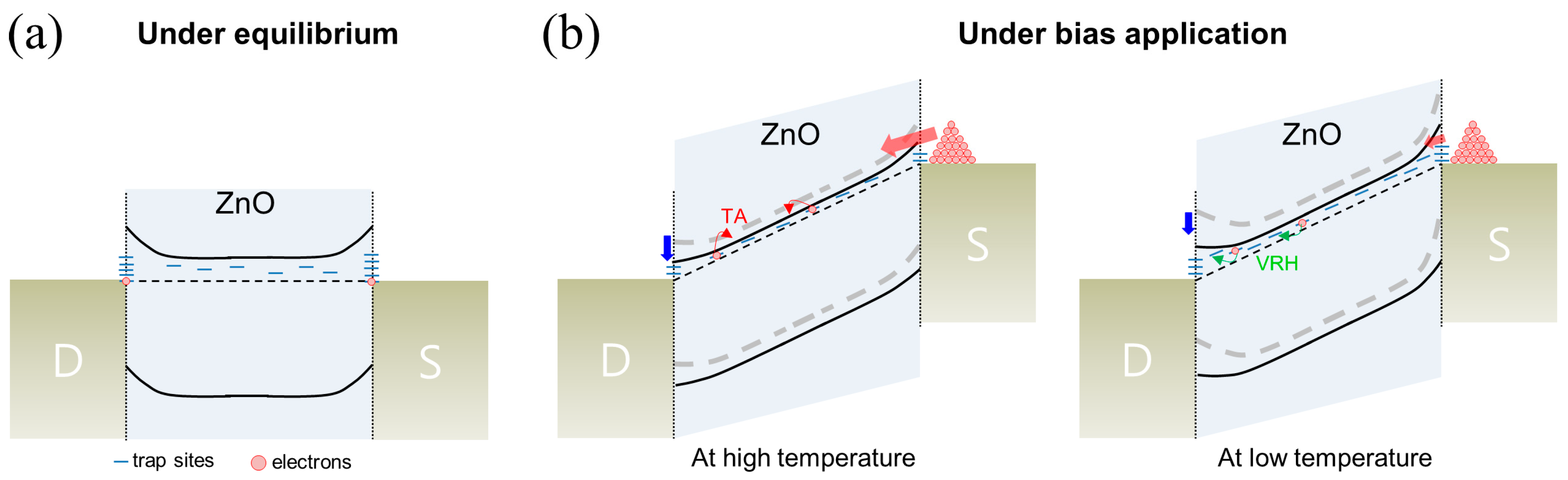

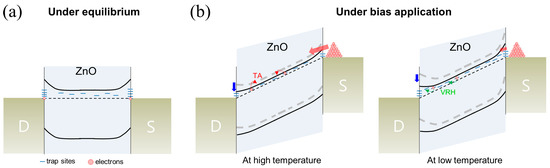

The energy band diagram presented in Figure 5 qualitatively shows the charge transport mechanisms of the ZnO nanowire FET, as discussed above. Unlike the equilibrium condition (Figure 5a), the applied biases (VG and VDS) could induce Schottky barrier modulation, resulting in changes in the carrier injection properties at the metal-semiconductor contact, as shown in Figure 5b. As a result, the modified Schottky barrier could affect the carrier concentration, leading to a change in the density of localized trap states in the channel. Furthermore, different temperature-dependent charge transport mechanisms were observed. Specifically, thermal activated (TA) conduction of electrons from a shallow level of localized states was dominant for charge transport in the high-temperature range, denoted as TA in Figure 5b (left), whereas the VRH conduction through the trap states near the Fermi level was dominant in the low-temperature range, denoted as VRH in Figure 5b (right).

Figure 5.

Energy band diagrams depicting the charge transport mechanism for the ZnO nanowire FET (a) under equilibrium and (b) under bias application at low and high temperatures. The blue arrow indicates Schottky barrier modulation according to the applied gate and drain voltages.

4. Conclusions

In summary, we fabricated a ZnO nanowire FET with a back-gated configuration and characterized the electrical properties of the FET device through temperature-dependent measurements to study the effect of applied gate and drain voltages on the charge transport properties. The Y-function method showed that the Vth shifted to a negative gate bias direction due to the DIBL effect. The temperature-dependent I-V measurements showed that the transport behavior of the ZnO nanowire FET was governed by SCLC at low temperatures and low voltages, in particular, by VRH conduction in the temperature regime from 4 to 100 K and by thermal activation transport at the high-temperature regime (150–300 K).

Supplementary Materials

The following are available online at https://www.mdpi.com/1996-1944/13/2/268/s1, Figure S1: SEM and TEM characterizations of the as-grown ZnO nanowires, Figure S2: PL data of the as-grown ZnO nanowires.

Author Contributions

Experiments; J.Y., F.H. and K.H.S.; writing—original draft preparation, review and editing; J.Y., J.I.S. and W.-K.H.; supervision, J.I.S. and W.-K.H. All authors have read and agreed to the published version of the manuscript.

Funding

This research was funded by Korea Basic Science Institute (grant numbers D39630 and D010500). J.I.S. acknowledges that this work was supported by the Dongguk University Research Fund of 2018.

Conflicts of Interest

The authors declare no conflict of interest.

References

- Wang, Z.L. Zinc oxide nanostructures: Growth, properties and applications. J. Phys. Condens. Matter 2004, 16, R829–R858. [Google Scholar] [CrossRef]

- Yang, P.; Yan, H.; Mao, S.; Russo, R.; Johnson, J.; Saykally, R.; Morris, N.; Pham, J.; He, R.; Choi, H.-J. Controlled growth of ZnO nanowires and their optical properties. Adv. Funct. Mater. 2002, 12, 323–331. [Google Scholar] [CrossRef]

- Rackauskas, S.; Barbero, N.; Barolo, C.; Viscardi, G. ZnO nanowire application in chemoresistive sensing: A review. Nanomaterials 2017, 7, 381. [Google Scholar] [CrossRef] [PubMed]

- Consonni, V.; Briscoe, J.; Kärber, E.; Li, X.; Cossuet, T. ZnO nanowires for solar cells: A comprehensive review. Nanotechnology 2019, 30, 362001. [Google Scholar] [CrossRef] [PubMed]

- Li, Y.; Çelik-Buter, Z.; Butler, D.P. An integrated piezoelectric zinc oxide nanowire micro-energy harvester. Nano Energy 2016, 26, 456–465. [Google Scholar] [CrossRef]

- Bao, J.; Zimmler, M.A.; Capasso, F.; Wang, X.; Ren, Z.F. Broadband ZnO single-nanowire light-emitting diode. Nano Lett. 2006, 6, 1719–1722. [Google Scholar] [CrossRef]

- Hong, W.-K.; Sohn, J.I.; Hwang, D.-K.; Kwon, S.-S.; Jo, G.; Song, S.; Kim, S.-M.; Ko, H.-J.; Park, S.-J.; Welland, M.E.; et al. Tunable electronic Transport Characteristics of Surface-Architecture-Controlled ZnO Nanowire Field Effect Transistors. Nano Lett. 2008, 8, 950–956. [Google Scholar] [CrossRef] [PubMed]

- Lieber, C.M. One- dimensional nanostructures: Chemistry, physics & applications. Solid State Commun. 1998, 107, 607–616. [Google Scholar]

- Schmidt-Mende, L.; MacManus-Driscoll, J.L. ZnO—Nanostructures, defects, and devices. Mater. Today 2007, 10, 40–48. [Google Scholar] [CrossRef]

- Lord, A.M.; Maffeis, T.G.; Kryvchenkova, O.; Cobley, R.J.; Kalna, K.; Kepaptsoglou, D.M.; Ramasse, Q.M.; Walton, A.S.; Ward, M.B.; Köble, J.; et al. Controlling the electrical transport properties of nanocontacts to nanowire. Nano Lett. 2015, 15, 4248–4254. [Google Scholar] [CrossRef]

- Jo, G.; Maeng, J.; Kim, T.-W.; Hong, W.-K.; Choi, B.-S.; Lee, T. Channel-length and gate-bias dependence of contact resistance and mobility for In2O3 nanowire field effect transistors. J. Appl. Phys. 2007, 102, 084508. [Google Scholar] [CrossRef]

- He, J.-H.; Ke, J.-J.; Chang, P.-H.; Tsai, K.-T.; Yang, P.C.; Chan, I.-M. Development of Ohmic nanocontacts via surface modification for nanowire-based electronic and optoelectronic devices: ZnO nanowires as an example. Nanoscale 2012, 4, 3399–3404. [Google Scholar] [CrossRef] [PubMed]

- Ju, S.; Janes, D.B.; Lu, G.; Facchetti, A.; Marks, T.J. Effects of bias stress on ZnO nanowire field-effect transistors fabricated with organic gate nanodielectrics. Appl. Phys. Lett. 2006, 89, 193506. [Google Scholar] [CrossRef]

- Choe, M.; Park, W.; Kang, J.W.; Jeong, S.; Hong, W.-K.; Lee, B.H.; Park, S.-J.; Lee, T. Investigation of threshold voltage instability induced by gate bias stress in ZnO nanowire field effect transistors. Nanotechnology 2012, 23, 485201. [Google Scholar] [CrossRef]

- Hong, W.-K.; Hwang, D.-K.; Park, I.-K.; Jo, G.; Song, S.; Park, S.-J.; Lee, T.; Kim, B.-J.; Stach, E.A. Realization of highly reproducible ZnO nanowire field effect transistors with n-channel depletion and enhancement modes. Appl. Phys. Lett. 2007, 90, 243103. [Google Scholar] [CrossRef]

- Kim, T.-Y.; Amani, M.; Ahn, G.H.; Song, Y.; Javey, A.; Chung, S.; Lee, T. Electrical properties of synthesized large-area MoS2 field-effect transistors fabricated with inkjet-printed contacts. ACS Nano 2016, 10, 2819–2826. [Google Scholar] [CrossRef]

- Zhao, Y.; Xiao, X.; Huo, Y.; Wang, Y.; Zhang, T.; Jiang, K.; Wang, J.; Fan, S.; Li, Q. Influence of asymmetric contact form on contact resistance and Schottky barrier, and corresponding applications of diode. ACS Appl. Mater. Interfaces 2017, 9, 18945–18955. [Google Scholar] [CrossRef]

- Jo, G.; Maeng, J.; Kim, T.-W.; Hong, W.-K.; Jo, M.; Hwang, H.; Lee, T. Effects of channel-length scaling on In2O3 nanowire field effect transistors studied by conducting atomic force microscopy. Appl. Phys. Lett. 2007, 90, 173106. [Google Scholar] [CrossRef]

- Liao, Z.-M.; Lv, Z.-K.; Zhou, Y.-B.; Xu, J.; Zhang, J.-M.; Yu, D.-P. The effect of adsorbates on the space–charge-limited current in single ZnO nanowires. Nanotechnology 2008, 19, 335204. [Google Scholar] [CrossRef]

- Xu, W.; Chin, A.; Ye, L.; Ning, C.Z.; Yu, H. Charge transport and trap characterization in individual GaSb nanowires. J. Appl. Phys. 2012, 111, 104515. [Google Scholar] [CrossRef]

- Fang, D.Q.; Zhang, R.Q. Size effects on formation energies and electronic structures of oxygen and zinc vacancies in ZnO nanowires: A first-principle study. J. Appl. Phys. 2011, 109, 044306. [Google Scholar] [CrossRef]

- Shao, Y.; Yoon, J.; Kim, H.; Lee, T.; Lu, W. Analysis of surface states in ZnO nanowire field effect transistors. Appl. Surf. Sci. 2014, 301, 2–8. [Google Scholar] [CrossRef]

- Chang, P.-C.; Lu, J.G. Temperature dependent conduction and UV induced metal-to-insulator transition in ZnO nanowires. Appl. Phys. Lett. 2008, 92, 212113. [Google Scholar] [CrossRef]

- Lin, Y.-F.; Jian, W.-B.; Wang, C.P.; Suen, Y.-W.; Wu, Z.-Y.; Chen, F.-R.; Kai, J.-J.; Lin, J.-J. Contact to ZnO and intrinsic resistances of individual ZnO nanowires with a circular cross section. Appl. Phys. Lett. 2007, 90, 223117. [Google Scholar] [CrossRef]

- Lin, Y.-F.; Chen, T.-H.; Chang, C.-H.; Chang, Y.-W.; Chiu, Y.-C.; Hung, H.-C.; Kai, J.-J.; Liu, Z.; Fang, J.; Jian, W.-B. Electron transport in high-resistance semiconductor nanowires through two-probe measurements. Phys. Chem. Chem. Phys. 2010, 12, 10928–10932. [Google Scholar] [CrossRef] [PubMed]

- Ko, D. Charge Transport Properties in Semiconductor Nanowires. Ph.D. Thesis, Ohio State University, Columbus, OH, USA, 2011. [Google Scholar]

- Liu, X.; Liu, J.; Antipina, L.Y.; Hu, J.; Yue, C.; Sanchez, A.M.; Sorokin, P.B.; Mao, Z.; Wei, J. Direct fabrication of functional ultrathin single-crystal nanowires from quasi-one-dimensional van der Waals crystals. Nano Lett. 2016, 16, 6188–6195. [Google Scholar] [CrossRef]

- Kaiser, A.B.; Gómez-Navarro, C.; Sundaram, R.S.; Burghard, M.; Kern, K. Electrical conduction mechanism in chemically derived graphene monolayers. Nano Lett. 2009, 9, 1787–1792. [Google Scholar] [CrossRef]

- Varade, V.; Anjaneyulu, P.; Sangeeth, C.S.S.; Ramesh, K.P.; Menon, R. Electric field activated nonlinear anisotropic charge transport in doped polypyrrole. Appl. Phys. Lett. 2013, 103, 233305. [Google Scholar] [CrossRef]

- Radisavljevic, B.; Kis, A. Mobility engineering and a metal-insulator transition in monolayer MoS2. Nat. Mater. 2013, 12, 815–820. [Google Scholar] [CrossRef] [PubMed]

- Tian, J.; Cai, J.; Hui, C.; Zhang, C.; Bao, L.; Gao, M.; Shen, C.; Gao, H. Boron nanowires for flexible electronics. Appl. Phys. Lett. 2008, 93, 122105. [Google Scholar] [CrossRef]

- Ma, Y.-J.; Zhang, Z.; Zhou, F.; Lu, L.; Jin, A.; Gu, C. Hopping conduction in single ZnO nanowires. Nanotechnology 2005, 16, 746–749. [Google Scholar] [CrossRef]

- Ayari, A.; Cobas, E.; Ogundadegbe, O.; Fuhrer, M.S. Realization and electrical characterization of ultrathin crystals of layered transition-metal dichalcogenides. J. Appl. Phys. 2007, 101, 014507. [Google Scholar] [CrossRef]

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).