Challenges and Perspectives for Vertical GaN-on-Si Trench MOS Reliability: From Leakage Current Analysis to Gate Stack Optimization

Abstract

:1. Introduction

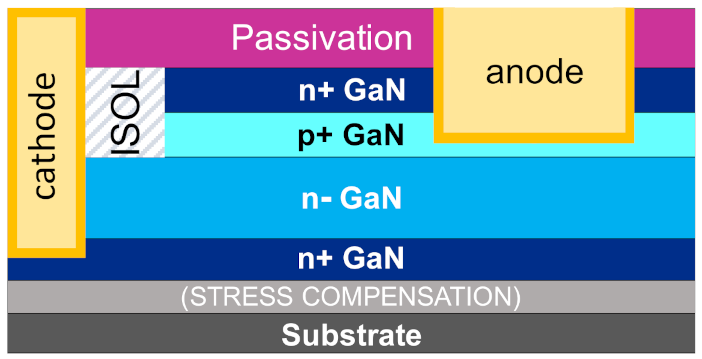

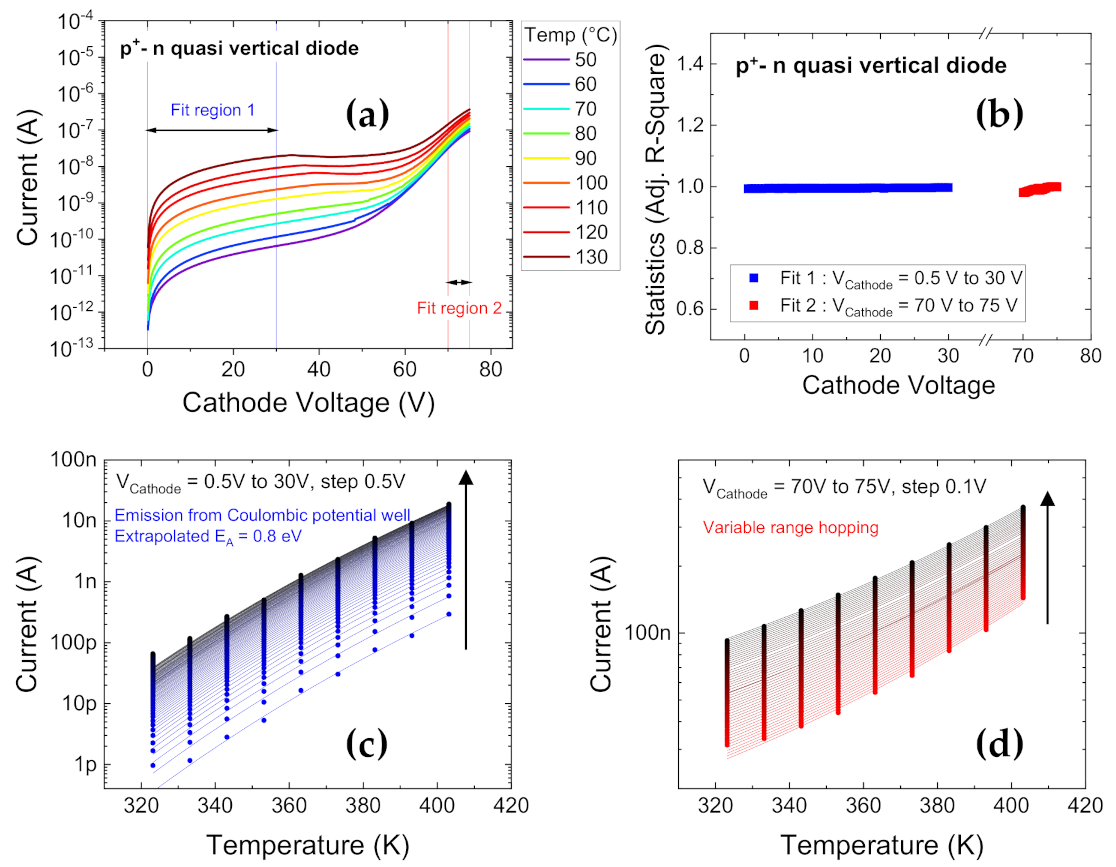

2. OFF-State-Leakage and Doping Constraints of Quasi-Vertical GaN-on-Si Diodes from IMEC, Leuven, Belgium

2.1. Leakage Modeling

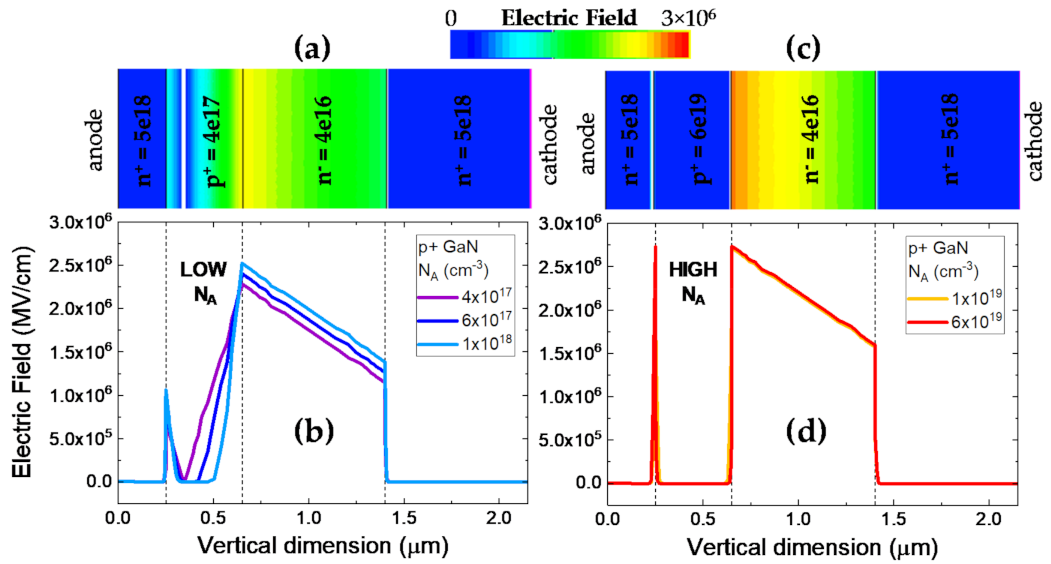

2.2. Simulation of Doping Constraints in Diode Breakdown

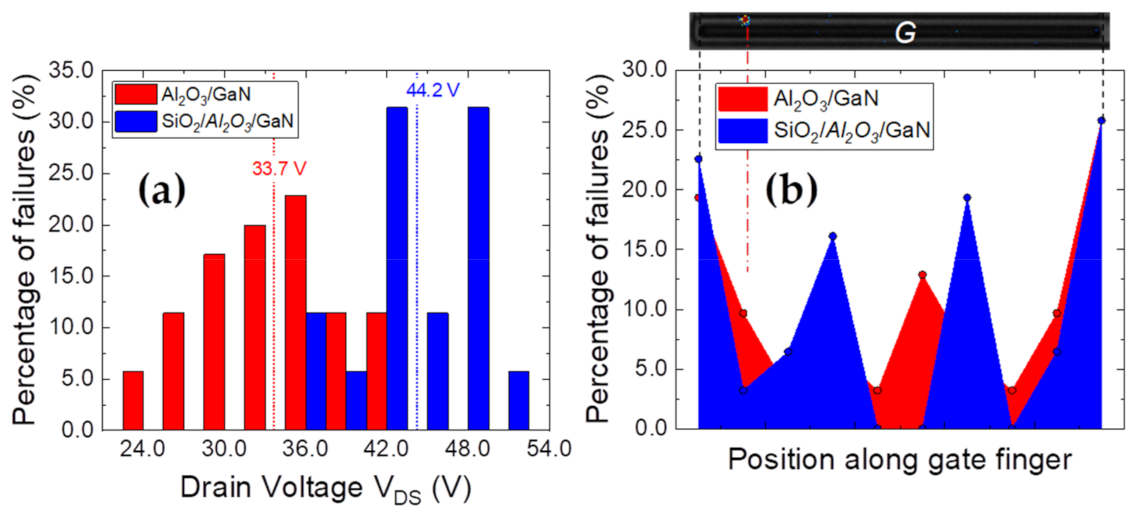

3. OFF-State and ON-State–Optimization of the M-O-S Stack in Quasi-Vertical MOSFETs from IMEC, Leuven, Belgium

3.1. Optimising Dielectric Composition

3.2. Optimising Trench Fabrication

4. ON-State-Light Assisted Analysis of Trapping Mechanisms in Quasi-Vertical MOSFETs from IMEC, Leuven, Belgium

5. Conclusions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Vecchia, M.D.; Ravyts, S.; Broeck, G.V.D.; Driesen, J. Gallium-Nitride Semiconductor Technology and Its Practical Design Challenges in Power Electronics Applications: An Overview. Energies 2019, 12, 2663. [Google Scholar] [CrossRef] [Green Version]

- Flack, T.J.; Pushpakaran, B.N.; Bayne, S.B. GaN Technology for Power Electronic Applications: A Review. J. Electron. Mater. 2016, 45, 2673–2682. [Google Scholar] [CrossRef]

- Hu, J.; Zhang, Y.; Sun, M.; Piedra, D.; Chowdhury, N.; Palacios, T. Materials and processing issues in vertical GaN power electronics. Mater. Sci. Semicond. Process. 2018, 78, 75–84. [Google Scholar] [CrossRef] [Green Version]

- Keshmiri, N.; Wang, D.; Agrawal, B.; Hou, R.; Emadi, A. Current Status and Future Trends of GaN HEMTs in Electrified Transportation. IEEE Access 2020, 8, 70553–70571. [Google Scholar] [CrossRef]

- Chowdhury, S.; Mishra, U.K. Lateral and Vertical Transistors Using the AlGaN/GaN Heterostructure. IEEE Trans. Electron Devices 2013, 60, 3060–3066. [Google Scholar] [CrossRef]

- Baliga, B.J. Semiconductors for High-voltage, Vertical Channel Field-effect Transistors. J. Appl. Phys. 1982, 53, 7. [Google Scholar] [CrossRef]

- Kim, I.-J.; Matsumoto, S.; Sakai, T.; Yachi, T. New power device figure of merit for high-frequency applications. In Proceedings of the International Symposium on Power Semiconductor Devices and IC’s: ISPSD ‘95, Yokohama, Japan, 23–25 May 1995. [Google Scholar] [CrossRef]

- Wang, H.; Wang, F.; Zhang, J. Power Semiconductor Device Figure of Merit for High-Power-Density Converter Design Applications. IEEE Trans. Electron Devices 2007, 55, 466–470. [Google Scholar] [CrossRef]

- Roccaforte, F.; Greco, G.; Fiorenza, P.; Iucolano, F. An Overview of Normally-Off GaN-Based High Electron Mobility Transistors. Materials 2019, 12, 1599. [Google Scholar] [CrossRef] [Green Version]

- Shenai, K. Future Prospects of Widebandgap (WBG) Semiconductor Power Switching Devices. IEEE Trans. Electron Devices 2014, 62, 248–257. [Google Scholar] [CrossRef]

- Meneghesso, G.; Meneghini, M.; Bisi, D.; Rossetto, I.; Cester, A.; Mishra, U.K.; Zanoni, E. Trapping phenomena in AlGaN/GaN HEMTs: A study based on pulsed and transient measurements. Semicond. Sci. Technol. 2013, 28, 074021. [Google Scholar] [CrossRef]

- Ueda, T. GaN power devices: Current status and future challenges. Jpn. J. Appl. Phys. 2019, 58, SC0804. [Google Scholar] [CrossRef]

- Hu, J.; Stoffels, S.; Lenci, S.; De Jaeger, B.; Ronchi, N.; Tallarico, A.N.; Wellekens, D.; You, S.; Bakeroot, B.; Groeseneken, G.; et al. Statistical Analysis of the Impact of Anode Recess on the Electrical Characteristics of AlGaN/GaN Schottky Diodes With Gated Edge Termination. IEEE Trans. Electron Devices 2016, 63, 3451–3458. [Google Scholar] [CrossRef]

- Uemoto, Y.; Hikita, M.; Ueno, H.; Matsuo, H.; Ishida, H.; Yanagihara, M.; Ueda, T.; Tanaka, T.; Ueda, D. Gate Injection Transistor (GIT)—A Normally-Off AlGaN/GaN Power Transistor Using Conductivity Modulation. IEEE Trans. Electron Devices 2007, 54, 3393–3399. [Google Scholar] [CrossRef]

- Meneghini, M.; Fabris, E.; Sun, M.; Palacios, T.; Meneghesso, G.; Zanoni, E.; Ruzzarin, M.; De Santi, C.; Nomoto, K.; Hu, Z.; et al. Degradation Mechanisms of GaN-Based Vertical Devices: A Review. Phys. Status Solidi (A) 2020, 217. [Google Scholar] [CrossRef]

- Ohta, H.; Kaneda, N.; Horikiri, F.; Narita, Y.; Yoshida, T.; Mishima, T.; Nakamura, T. Vertical GaN p-n Junction Diodes with High Breakdown Voltages Over 4 kV. IEEE Electron Device Lett. 2015, 36, 1180–3182. [Google Scholar] [CrossRef]

- Kizilyalli, I.C.; Edwards, A.P.; Aktas, O.; Prunty, T.; Bour, D. Vertical Power p-n Diodes Based on Bulk GaN. IEEE Trans. Electron Devices 2015, 62, 414–422. [Google Scholar] [CrossRef]

- Oka, T. Recent development of vertical GaN power devices. Jpn. J. Appl. Phys. 2019, 58, SB0805. [Google Scholar] [CrossRef]

- Ramanathan, D.; Coles, C.; Meier, W. Not All GaN Transistors Are Built Equal: The Benefits of Vertical GaN-on-GaN. In Proceedings of the PCIM Europe Digital Days 2020; International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, Nuremburg, Germany, 7–8 July 2020; pp. 1–4. [Google Scholar]

- De Santi, C.; Fabris, E.; Meneghesso, G.; Zanoni, E.; Meneghini, M. GaN Vertical p–i–n Diodes in Avalanche Regime: Time-Dependent Behavior and Degradation. IEEE Electron Device Lett. 2020, 41, 1300–1303. [Google Scholar] [CrossRef]

- Fukushima, H.; Usami, S.; Ogura, M.; Ando, Y.; Tanaka, A.; Deki, M.; Kushimoto, M.; Nitta, S.; Honda, Y.; Amano, H. Deeply and vertically etched butte structure of vertical GaN p–n diode with avalanche capability. Jpn. J. Appl. Phys. 2019, 58, SCCD25. [Google Scholar] [CrossRef]

- Zhang, Y.; Sun, M.; Piedra, D.; Hu, J.; Liu, Z.; Lin, Y.; Gao, X.; Shepard, K.; Palacios, T. 1200 V GaN vertical fin power field-effect transistors. In Proceedings of the 2017 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2–6 December 2017. [Google Scholar]

- Panasonic GaN Power Transistors. New Contender for the Power Transistor Throne: How GaN Is Threatening the MOSFET’s Crown, April 2018. Available online: https://eu.industrial.panasonic.com/sites/default/pidseu/files/pan_18047_whitepaper_gan_web.pdf (accessed on 20 February 2021).

- Ji, D.; Agarwal, A.; Li, H.; Li, W.; Keller, S.; Chowdhury, S. 880 V/2.7 M Cm2 MIS Gate Trench CAVET on Bulk GaN Substrates. IEEE Electron Device Lett. 2018, 39, 863–865. [Google Scholar] [CrossRef]

- Hu, J.; Stoffels, S.; Lenci, S.; Bakeroot, B.; De Jaeger, B.; Van Hove, M.; Ronchi, N.; Venegas, R.; Liang, H.; Zhao, M.; et al. Performance Optimization of Au-Free Lateral AlGaN/GaN Schottky Barrier Diode with Gated Edge Termination on 200-mm Silicon Substrate. IEEE Trans. Electron Devices 2016, 63, 997–1004. [Google Scholar] [CrossRef]

- Zhang, Y.; Sun, M.; Wong, H.-Y.; Lin, Y.; Srivastava, P.; Hatem, C.; Azize, M.; Piedra, D.; Yu, L.; Sumitomo, T.; et al. Origin and Control of OFF-State Leakage Current in GaN-on-Si Vertical Diodes. IEEE Trans. Electron Devices 2015, 62, 2155–2161. [Google Scholar] [CrossRef] [Green Version]

- Zhang, Y.; Piedra, D.; Sun, M.; Hennig, J.; Dadgar, A.; Yu, L.; Palacios, T. High-Performance 500 V Quasi- and Fully-Vertical GaN-on-Si pn Diodes. IEEE Electron Device Lett. 2016, 38, 248–251. [Google Scholar] [CrossRef]

- Zhang, X.; Zou, X.; Lu, X.; Tang, C.W.; Lau, K.M. Fully- and Quasi-Vertical GaN-on-Si p-i-n Diodes: High Performance and Comprehensive Comparison. IEEE Trans. Electron Devices 2017, 64, 809–815. [Google Scholar] [CrossRef]

- Zhang, Y.; Yuan, M.; Chowdhury, N.; Cheng, K.; Palacios, T. 720-V/0.35-m Ω⋅Ω cm2Fully Vertical GaN-on-Si Power Diodes by Selective Removal of Si Substrates and Buffer Layers. IEEE Electron Device Lett. 2018, 39, 715–718. [Google Scholar] [CrossRef]

- Zou, X.; Zhang, X.; Lu, X.; Tang, C.W.; Lau, K.M. Fully Vertical GaN p-i-n Diodes Using GaN-on-Si Epilayers. IEEE Electron Device Lett. 2016, 37, 636–639. [Google Scholar] [CrossRef]

- Mase, S.; Hamada, T.; Freedsman, J.J.; Egawa, T. Effect of Drift Layer on the Breakdown Voltage of Fully-Vertical GaN-on-Si p-n Diodes. IEEE Electron Device Lett. 2017, 38, 1720–1723. [Google Scholar] [CrossRef]

- Khadar, R.A.; Liu, C.; Soleimanzadeh, R.; Matioli, E. Fully Vertical GaN-on-Si power MOSFETs. IEEE Electron Device Lett. 2019, 40, 443–446. [Google Scholar] [CrossRef]

- Zubair, A.; Perozek, J.; Niroula, J.; Aktas, O.; Odnoblyudov, V.; Palacios, T. First Demonstration of GaN Vertical Power FinFETs on Engineered Substrate. In Proceedings of the 2020 Device Research Conference (DRC), Columbus, OH, USA, 21–24 June 2020; pp. 1–2. [Google Scholar]

- Liu, C.; Khadar, R.A.; Matioli, E. GaN-on-Si Quasi-Vertical Power MOSFETs. IEEE Electron Device Lett. 2017, 39, 71–74. [Google Scholar] [CrossRef]

- Liu, C.; Khadar, R.A.; Matioli, E. Vertical GaN-on-Si MOSFETs With Monolithically Integrated Freewheeling Schottky Barrier Diodes. IEEE Electron Device Lett. 2018, 39, 1034–1037. [Google Scholar] [CrossRef]

- Liu, C.; Khadar, R.A.; Matioli, E. 645 V quasi-vertical GaN power transistors on silicon substrates. In Proceedings of the 2018 IEEE 30th International Symposium on Power Semiconductor Devices and ICs (ISPSD), Chicago, IL, USA, 13–17 May 2018; pp. 240–243. [Google Scholar]

- Chowdhury, S.; Swenson, B.L.; Mishra, U.K. Enhancement and Depletion Mode AlGaN/GaN CAVET With Mg-Ion-Implanted GaN as Current Blocking Layer. IEEE Electron Device Lett. 2008, 29, 543–545. [Google Scholar] [CrossRef]

- Ji, D.; Li, W.; Agarwal, A.; Chan, S.H.; Haller, J.; Bisi, D.; Labrecque, M.; Gupta, C.; Cruse, B.; Lal, R.; et al. Improved Dynamic RON of GaN Vertical Trench MOSFETs (OG-FETs) Using TMAH Wet Etch. IEEE Electron Device Lett. 2018, 39, 1030–1033. [Google Scholar] [CrossRef]

- Gupta, C.; Chan, S.H.; Enatsu, Y.; Agarwal, A.; Keller, S.; Mishra, U.K. OG-FET: An in-situ Oxide, GaN interlayer based vertical trench MOSFET. IEEE Electron Device Lett. 2016, 37, 1. [Google Scholar] [CrossRef]

- Xiao, M.; Gao, X.; Palacios, T.; Zhang, Y. Leakage and breakdown mechanisms of GaN vertical power FinFETs. Appl. Phys. Lett. 2019, 114, 163503. [Google Scholar] [CrossRef]

- Li, W.; Xing, H.G.; Nomoto, K.; Lee, K.; Islam, S.; Hu, Z.; Zhu, M.; Gao, X.; Pilla, M.; Jena, D. Development of GaN Vertical Trench-MOSFET With MBE Regrown Channel. IEEE Trans. Electron Devices 2018, 65, 2558–2564. [Google Scholar] [CrossRef]

- Otake, H.; Chikamatsu, K.; Yamaguchi, A.; Fujishima, T.; Ohta, H. Vertical GaN-Based Trench Gate Metal Oxide Semiconductor Field-Effect Transistors on GaN Bulk Substrates. Appl. Phys. Express 2008, 1, 011105. [Google Scholar] [CrossRef]

- Gupta, C.; Chan, S.H.; Lund, C.; Agarwal, A.; Koksaldi, O.S.; Liu, J.; Enatsu, Y.; Keller, S.; Mishra, U.K. Comparing electrical performance of GaN trench-gate MOSFETs with a-Plane and m-Plane Sidewall Channels. Appl. Phys. Express 2016, 9, 121001. [Google Scholar] [CrossRef]

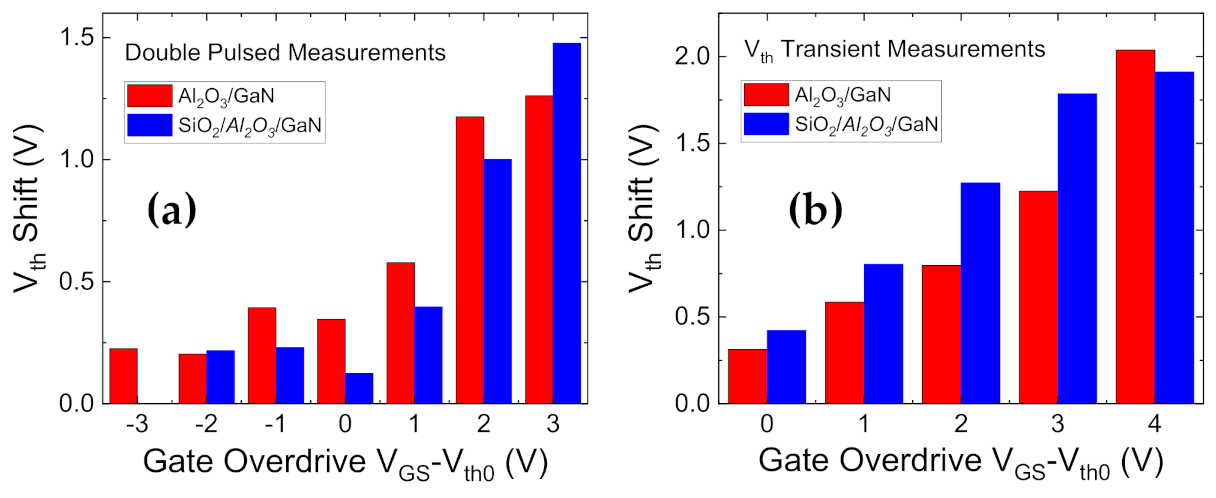

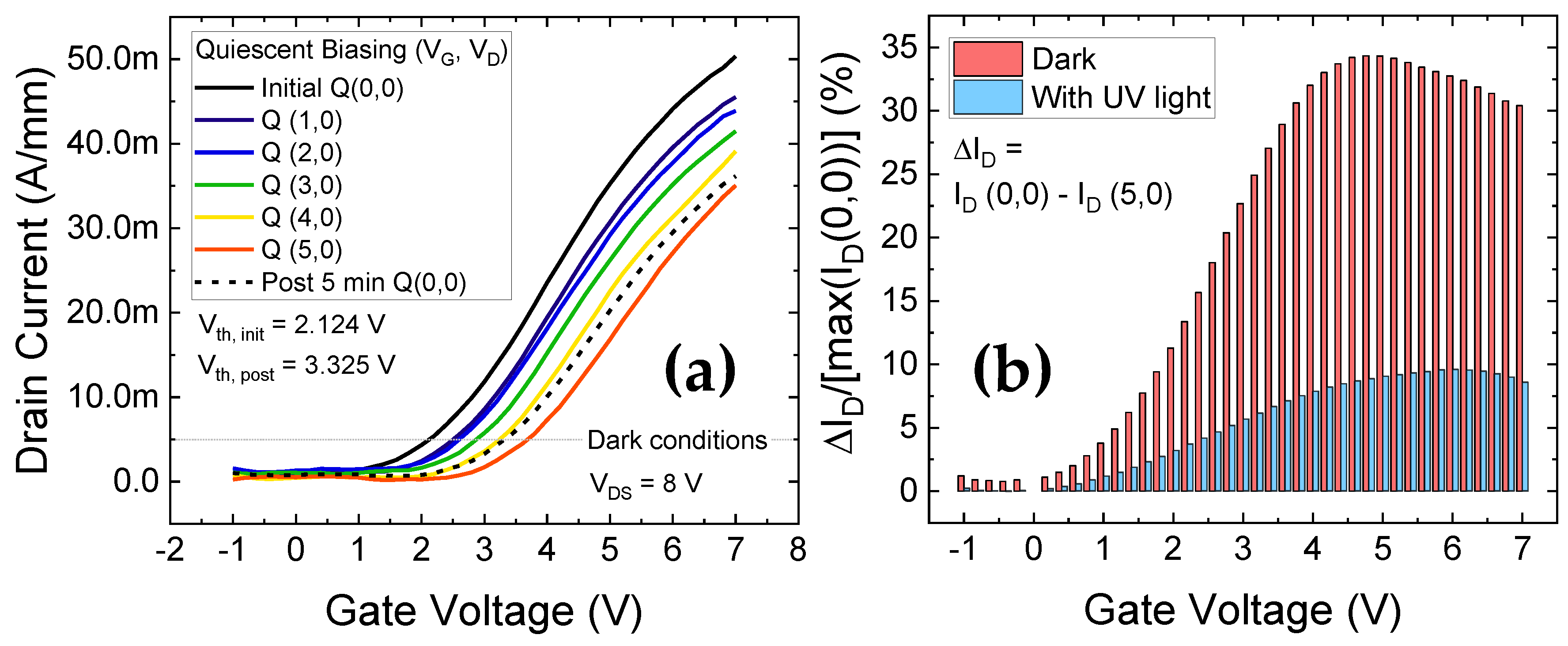

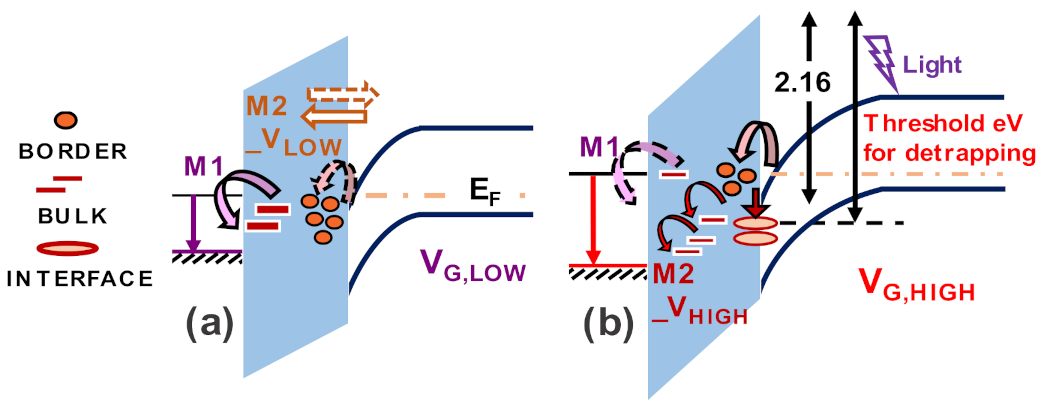

- Mukherjee, K.; Borga, M.; Ruzzarin, M.; De Santi, C.; Stoffels, S.; You, S.; Geens, K.; Liang, H.; Decoutere, S.; Meneghesso, G.; et al. Analysis of threshold voltage instabilities in semi-vertical GaN-on-Si FETs. Appl. Phys. Express 2020, 13, 024004. [Google Scholar] [CrossRef]

- Borga, M.; Mukherjee, K.; De Santi, C.; Stoffels, S.; Geens, K.; You, S.; Bakeroot, B.; Decoutere, S.; Meneghesso, G.; Zanoni, E.; et al. Modeling of gate capacitance of GaN-based trench-gate vertical metal-oxide-semiconductor devices. Appl. Phys. Express 2020, 13, 024006. [Google Scholar] [CrossRef]

- Mukherjee, K.; De Santi, C.; Borga, M.; You, S.; Geens, K.; Bakeroot, B.; Decoutere, S.; Meneghesso, G.; Zanoni, E.; Meneghini, M. Use of Bilayer Gate Insulator in GaN-on-Si Vertical Trench MOSFETs: Impact on Performance and Reliability. Materials 2020, 13, 4740. [Google Scholar] [CrossRef]

- Zhang, Y.; Dadgar, A.; Palacios, T. Gallium nitride vertical power devices on foreign substrates: A review and outlook. J. Phys. D: Appl. Phys. 2018, 51, 273001. [Google Scholar] [CrossRef]

- Dadgar, A. Sixteen years GaN on Si. Phys. Status Solidi (B) 2015, 252, 1063–1068. [Google Scholar] [CrossRef]

- Zhu, T.; Oliver, R.A. Unintentional doping in GaN. Phys. Chem. Chem. Phys. 2012, 14, 9558–9573. [Google Scholar] [CrossRef] [PubMed]

- Wickenden, A.; Koleske, D.; Henry, R.; Twigg, M.; Fatemi, M. Resistivity control in unintentionally doped GaN films grown by MOCVD. J. Cryst. Growth 2004, 260, 54–62. [Google Scholar] [CrossRef]

- Chung, B.; Gershenzon, M. The influence of oxygen on the electrical and optical properties of GaN crystals grown by metalorganic vapor phase epitaxy. J. Appl. Phys. 1992, 72, 651–659. [Google Scholar] [CrossRef]

- Seager, C.H.; Wright, A.F.; Yu, J.; Götz, W. Role of carbon in GaN. J. Appl. Phys. 2002, 92, 6553–6560. [Google Scholar] [CrossRef]

- Zhang, Y.; Wong, H.-Y.; Sun, M.; Joglekar, S.; Yu, L.; Braga, N.A.; Mickevicius, R.V.; Palacios, T. Design space and origin of off-state leakage in GaN vertical power diodes. In Proceedings of the 2015 IEEE International Electron Devices Meeting (IEDM), Washington, DC, USA, 7–9 December 2015; pp. 35.1.1–35.1.4. [Google Scholar]

- Rackauskas, B.; Dalcanale, S.; Uren, M.J.; Kachi, T.; Kuball, M. Leakage mechanisms in GaN-on-GaN vertical pn diodes. Appl. Phys. Lett. 2018, 112, 233501. [Google Scholar] [CrossRef]

- Mukherjee, K.; De Santi, C.; Buffolo, M.; Borga, M.; You, S.; Geens, K.; Bakeroot, B.; Decoutere, S.; Gerosa, A.; Meneghesso, G.; et al. Understanding the Leakage Mechanisms and Breakdown Limits of Vertical GaN-on-Si p+n−n Diodes: The Road to Reliable Vertical MOSFETs. Micromachines 2021, 12, 445. [Google Scholar] [CrossRef]

- Podor, B. Thermal ionization energy of Mg acceptors in GaN: Effects of doping level and compensation. In Proceedings of the SPIE 4412, International Conference on Solid State Crystals 2000: Growth, Characterization, and Applications of Single Crystals, Zakopane, Poland, 10 August 2001; pp. 299–303. [Google Scholar]

- Sabui, G.; Parbrook, P.J.; Arredondo-Arechavala, M.; Shen, Z.J. Modeling and simulation of bulk gallium nitride power semiconductor devices. AIP Adv. 2016, 6, 055006. [Google Scholar] [CrossRef]

- Yang, J.; Zhao, D.; Jiang, D.; Chen, P.; Zhu, J.; Liu, Z.; Le, L.; He, X.; Li, X.; Zhang, Y.T.; et al. Influence of hydrogen impurities on p-type resistivity in Mg-doped GaN films. J. Vac. Sci. Technol. A 2015, 33, 021505. [Google Scholar] [CrossRef]

- Musolino, M.; Van Treeck, D.; Tahraoui, A.; Scarparo, L.; De Santi, C.; Meneghini, M.; Zanoni, E.; Geelhaar, L.; Riechert, H. A physical model for the reverse leakage current in (In,Ga)N/GaN light-emitting diodes based on nanowires. J. Appl. Phys. 2016, 119, 44502. [Google Scholar] [CrossRef] [Green Version]

- Han, D.-P.; Oh, C.-H.; Kim, H.; Shim, J.-I.; Kim, K.-S.; Shin, D.-S. Conduction Mechanisms of Leakage Currents in InGaN/GaN-Based Light-Emitting Diodes. IEEE Trans. Electron Devices 2014, 62, 587–592. [Google Scholar] [CrossRef]

- Chiu, F.-C. A Review on Conduction Mechanisms in Dielectric Films. Adv. Mater. Sci. Eng. 2014, 2014, 1–18. [Google Scholar] [CrossRef] [Green Version]

- Hill, R.M. Hopping conduction in amorphous solids. Philos. Mag. 1971, 24, 1307–1325. [Google Scholar] [CrossRef]

- Shan, Q.; Meyaard, D.S.; Dai, Q.; Cho, J.; Schubert, E.F.; Son, J.K.; Sone, C. Transport-mechanism analysis of the reverse leakage current in GaInN light-emitting diodes. Appl. Phys. Lett. 2011, 99, 253506. [Google Scholar] [CrossRef] [Green Version]

- Zhou, S.; Lv, J.; Wu, Y.; Zhang, Y.; Zheng, C.; Liu, S. Reverse leakage current characteristics of InGaN/GaN multiple quantum well ultraviolet/blue/green light-emitting diodes. Jpn. J. Appl. Phys. 2018, 57, 051003. [Google Scholar] [CrossRef]

- Kuksenkov, D.V.; Temkin, H.; Osinsky, A.; Gaska, R.; Khan, M.A. Origin of conductivity and low-frequency noise in reverse-biased GaN p-n junction. Appl. Phys. Lett. 1998, 72, 1365–1367. [Google Scholar] [CrossRef]

- Kim, J.; Kim, J.-Y.; Tak, Y.; Kim, J.; Hong, H.-G.; Yang, M.; Chae, S.; Park, J.; Park, Y.; Chung, U.-I. Investigation of Reverse Leakage Characteristics of InGaN/GaN Light-Emitting Diodes on Silicon. IEEE Electron Device Lett. 2012, 33, 1741–1743. [Google Scholar] [CrossRef]

- Jung, E.; Lee, J.K.; Kim, M.S.; Kim, H. Leakage Current Analysis of GaN-Based Light-Emitting Diodes Using a Parasitic Diode Model. IEEE Trans. Electron Devices 2015, 62, 3322–3325. [Google Scholar] [CrossRef]

- Look, D.C.; Reynolds, D.C.; Kim, W.; Aktas, O.; Botchkarev, A.; Salvador, A.; Morkoç, H. Deep-center hopping conduction in GaN. J. Appl. Phys. 1996, 80, 2960–2963. [Google Scholar] [CrossRef] [Green Version]

- Ferdous, M.S.; Wang, X.; Fairchild, M.N.; Hersee, S.D. Effect of threading defects on InGaN∕GaN multiple quantum well light emitting diodes. Appl. Phys. Lett. 2007, 91, 231107. [Google Scholar] [CrossRef] [Green Version]

- Zhao, L.; Chen, L.; Yu, G.; Yan, D.; Yang, G.; Gu, X.; Liu, B.; Lu, H. Tunneling-Hopping Transport Model for Reverse Leakage Current in InGaN/GaN Blue Light-Emitting Diodes. IEEE Photon. Technol. Lett. 2017, 29, 1447–1450. [Google Scholar] [CrossRef]

- Tsou, C.-W.; Ji, M.-H.; Bakhtiary-Noodeh, M.; Detchprohm, T.; Dupuis, R.D.; Shen, S.-C. Temperature-Dependent Leakage Current Characteristics of Homojunction GaN p-i-n Rectifiers Using Ion-Implantation Isolation. IEEE Trans. Electron Devices 2019, 66, 4273–4278. [Google Scholar] [CrossRef]

- Mazzola, M.S.; Saddow, S.E.; Neudeck, P.G.; Lakdawala, V.K.; We, S. Observation of the D-center in 6H-SiC p-n diodes grown by chemical vapor deposition. Appl. Phys. Lett. 1994, 64, 2730–2732. [Google Scholar] [CrossRef]

- Hill, R.M. Poole-Frenkel conduction in amorphous solids. Philos. Mag. 1971, 23, 59–86. [Google Scholar] [CrossRef]

- Frenkel, J. On Pre-Breakdown Phenomena in Insulators and Electronic Semi-Conductors. Phys. Rev. 1938, 54, 647–648. [Google Scholar] [CrossRef]

- Simmons, J.G. Conduction in thin dielectric films. J. Phys. D Appl. Phys. 1971, 4, 613–657. [Google Scholar] [CrossRef]

- Lee, M.; Lee, H.U.; Song, K.M.; Kim, J. Significant improvement of reverse leakage current characteristics of Si-based homoepitaxial InGaN/GaN blue light emitting diodes. Sci. Rep. 2019, 9, 1–6. [Google Scholar] [CrossRef]

- Hirsch, L.; Barrieere, A.S.; A. Electrical characterization of InGaN/GaN light emitting diodes grown by molecular beam epitaxy. J. Appl. Phys. 2003, 94, 5014. [Google Scholar] [CrossRef]

- Kim, J.; Kim, J.; Tak, Y.; Chae, S.; Kim, J.-Y.; Park, Y. Effect of V-Shaped Pit Size on the Reverse Leakage Current of InGaN/GaN Light-Emitting Diodes. IEEE Electron Device Lett. 2013, 34, 1409–1411. [Google Scholar] [CrossRef]

- Zhang, Y.; Sun, M.; Piedra, D.; Azize, M.; Zhang, X.; Fujishima, T.; Palacios, T. GaN-on-Si Vertical Schottky and p-n Diodes. IEEE Electron Device Lett. 2014, 35, 618–620. [Google Scholar] [CrossRef]

- Demchenko, D.O.; Diallo, I.C.; Reshchikov, M.A. Yellow Luminescence of Gallium Nitride Generated by Carbon Defect Complexes. Phys. Rev. Lett. 2013, 110, 087404. [Google Scholar] [CrossRef]

- Huber, M.; Silvestri, M.; Knuuttila, L.; Pozzovivo, G.; Andreev, A.; Kadashchuk, A.; Bonanni, A.; Lundskog, A. Impact of residual carbon impurities and gallium vacancies on trapping effects in AlGaN/GaN metal insulator semiconductor high electron mobility transistors. Appl. Phys. Lett. 2015, 107, 032106. [Google Scholar] [CrossRef] [Green Version]

- Karch, J. Improving on Adjusted R-Squared. Collabra Psychol. 2020, 6. [Google Scholar] [CrossRef]

- Cheng, K.; Liang, H.; Van Hove, M.; Geens, K.; De Jaeger, B.; Srivastava, P.; Kang, X.; Favia, P.; Bender, H.; Decoutere, S.; et al. AlGaN/GaN/AlGaN Double Heterostructures Grown on 200 mm Silicon (111) Substrates with High Electron Mobility. Appl. Phys. Express 2011, 5, 011002. [Google Scholar] [CrossRef]

- Gao, J.; Hao, M.; Li, W.; Xu, Z.; Mandal, S.; Nemanich, R.; Chowdhury, S. Al2 O3 Insertion Layer for Improved PEALD SiO2 /(Al)GaN Interfaces. Phys. Status Solidi (A) 2018, 215. [Google Scholar] [CrossRef]

- Posthuma, N.E.; You, S.; Stoffels, S.; Liang, H.; Zhao, M.; Decoutere, S. Gate Architecture Design for Enhancement Mode P-GaN Gate HEMTs for 200 and 650V Applications. In Proceedings of the 2018 IEEE 30th International Symposium on Power Semiconductor Devices and ICs (ISPSD), Chicago, IL, USA, 13–17 May 2018; pp. 188–191. [Google Scholar]

- Robertson, J.; Falabretti, B. Band offsets of high K gate oxides on III-V semiconductors. J. Appl. Phys. 2006, 100, 014111. [Google Scholar] [CrossRef]

- Robertson, J. High dielectric constant oxides. Eur. Phys. J. Appl. Phys. 2004, 28, 265–291. [Google Scholar] [CrossRef] [Green Version]

- Yatabe, Z.; Hori, Y.; Ma, W.-C.; Asubar, J.T.; Akazawa, M.; Sato, T.; Hashizume, T. Characterization of electronic states at insulator/(Al)GaN interfaces for improved insulated gate and surface passivation structures of GaN-based transistors. Jpn. J. Appl. Phys. 2014, 53. [Google Scholar] [CrossRef] [Green Version]

- Ruzzarin, M.; Meneghini, M.; Bisi, D.; Sun, M.; Palacios, T.; Meneghesso, G.; Zanoni, E. Instability of Dynamic- and Threshold Voltage in GaN-on-GaN Vertical Field-Effect Transistors. IEEE Trans. Electron Devices 2017, 64, 3126–3131. [Google Scholar] [CrossRef]

- Ruzzarin, M.; Meneghini, M.; De Santi, C.; Meneghesso, G.; Zanoni, E.; Sun, M.; Palacios, T. Degradation of vertical GaN FETs under gate and drain stress. In Proceedings of the 2018 IEEE International Reliability Physics Symposium (IRPS), Burlingame, CA, USA, 11–15 March 2018. [Google Scholar]

- Hori, Y.; Mizue, C.; Hashizume, T. Process Conditions for Improvement of Electrical Properties of Al2O3/n-GaN Structures Prepared by Atomic Layer Deposition. Jpn. J. Appl. Phys. 2010, 49, 080201. [Google Scholar] [CrossRef]

- Kim, S.; Hori, Y.; Ma, W.-C.; Kikuta, D.; Narita, T.; Iguchi, H.; Uesugi, T.; Kachi, T.; Hashizume, T. Interface Properties of Al2O3/n-GaN Structures with Inductively Coupled Plasma Etching of GaN Surfaces. Jpn. J. Appl. Phys. 2012, 51, 60201. [Google Scholar] [CrossRef]

- Saxena, R.S.; Kumar, M.J. Trench Gate Power MOSFET: Recent Advances and Innovations. arXiv 2012, arXiv:1208.5553. [Google Scholar]

- Zhang, Y.; Sun, M.; Liu, Z.; Piedra, D.; Hu, J.; Gao, X.; Palacios, T. Trench formation and corner rounding in vertical GaN power devices. Appl. Phys. Lett. 2017, 110, 193506. [Google Scholar] [CrossRef]

- Osipov, K.; John, W.; Kemf, N.; Chevtchenko, S.; Kurpas, P.; Matalla, M.; Krüger, O.; Wuerfl, J. Fabrication Technology of GaN/AlGaN HEMT Slanted Sidewall Gates Using Thermally Reflowed ZEP Resist and CHF3/SF6 Plasma Etching. In Proceedings of the International Conference on Compound Semiconductor Manufacturing Technology, CS MANTECH, New Orleans, LA, USA, 13–16 May 2013; pp. 139–142. [Google Scholar]

- Thies, A.; Kemf, N.; Chevtchenko, S.; Krüger, O. Formation of Slanted Gates for Gan-Based Hemts by Combined Plasma and Wet Chemical Etching of Silicon Nitride. In Proceedings of the International Conference on Compound Semiconductor Manufacturing Technology, CS MANTECH, New Orleans, LA, USA, 13–16 May 2013; pp. 395–398. [Google Scholar]

- Gupta, C.; Ji, D.; Chan, S.H.; Agarwal, A.; Leach, W.; Keller, S.; Chowdhury, S.; Mishra, U.K. Impact of Trench Dimensions on the Device Performance of GaN Vertical Trench MOSFETs. IEEE Electron Device Lett. 2017, 38, 1559–1562. [Google Scholar] [CrossRef]

- Zeng, J.; Mawby, P.; Towers, M.; Board, K. Modelling of the quasisaturation behaviour in the high-voltage MOSFET with vertical trench gate. IEE Proc. Circuits Devices Syst. 1996, 143, 28. [Google Scholar] [CrossRef]

- Shimizu, R.; Kuribayashi, H.; Hiruta, R.; Sudoh, K.; Iwasaki, H. Mechanism and Control Technology of Trench Corner Rounding by Hydrogen Annealing for Highly Reliable Trench MOSFET. In Proceedings of the 18th International Symposium on Power Semiconductor Devices & IC’s, Naples, Italy, 4–8 June 2006. [Google Scholar]

- Simon-Najasek, M.; Huebner, S.; Altmann, F.; Graff, A. Advanced FIB sample preparation techniques for high resolution TEM investigations of HEMT structures. Microelectron. Reliab. 2014, 54, 1785–1789. [Google Scholar] [CrossRef]

- Graff, A.; Simon-Najasek, M.; Poppitz, D.; Altmann, F. Physical failure analysis methods for wide band gap semiconductor devices. In Proceedings of the 2018 IEEE International Reliability Physics Symposium (IRPS), Burlingame, CA, USA, 11–15 March 2018. [Google Scholar]

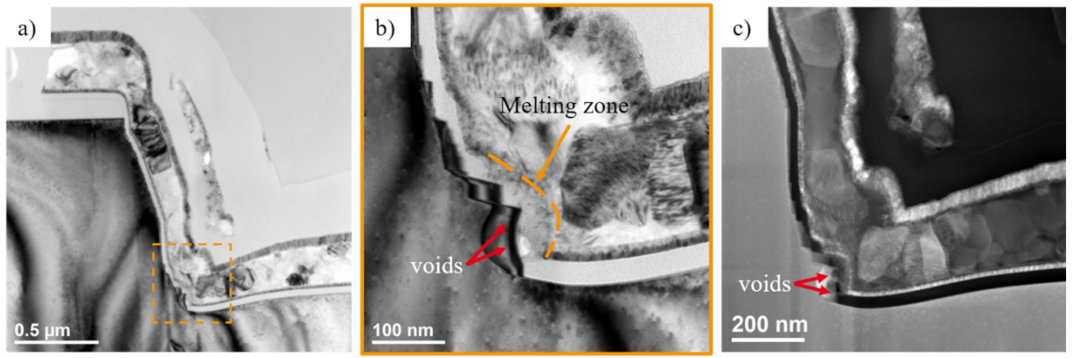

- Diehle, P.; Hubner, S.; De Santi, C.; Mukherjee, K.; Zanoni, E.; Meneghini, M.; Geens, K.; You, S.; Decoutere, S.; Altmann, F. Root cause analysis of gate shorts in semi-vertical GaN MOSFET devices. In Proceedings of the 2020 13th International Conference on Advanced Semiconductor Devices and Microsystems (ASDAM), Smolenice, Slovakia, 11–14 October 2020; pp. 10–13. [Google Scholar]

- Bisi, D.; Stocco, A.; Meneghini, M.; Rampazzo, F.; Cester, A.; Meneghesso, G.; Zanoni, E. High-Voltage Double-Pulsed Measurement System for GaN-Based Power HEMTs. In Proceedings of the 2014 IEEE International Reliability Physics Symposium, Waikoloa, HI, USA, 1–5 June 2014; pp. CD.11.1–CD.11.4. [Google Scholar]

- Lagger, P.; Reiner, M.; Pogany, D.; Ostermaier, C. Comprehensive Study of the Complex Dynamics of Forward Bias-Induced Threshold Voltage Drifts in GaN Based MIS-HEMTs by Stress/Recovery Experiments. IEEE Trans. Electron Devices 2014, 61, 1022–1030. [Google Scholar] [CrossRef]

- Stockman, A.; Canato, E.; Tajalli, A.; Meneghini, M.; Meneghesso, G.; Zanoni, E.; Moens, P.; Bakeroot, B. On the origin of the leakage current in p-gate AlGaN/GaN HEMTs. In Proceedings of the 2018 IEEE International Reliability Physics Symposium (IRPS), Burlingame, CA, USA, 11–15 March 2018. [Google Scholar] [CrossRef]

- Ren, B.; Sumiya, M.; Liao, M.; Koide, Y.; Liu, X.; Shen, Y.; Sang, L. Interface trap characterization of Al2O3/GaN vertical-type MOS capacitors on GaN substrate with surface treatments. J. Alloys Compd. 2018, 767, 600–605. [Google Scholar] [CrossRef]

- Kaneki, S.; Ohira, J.; Toiya, S.; Yatabe, Z.; Asubar, J.T.; Hashizume, T. Highly-stable and low-state-density Al2O3/GaN interfaces using epitaxial n-GaN layers grown on free-standing GaN substrates. Appl. Phys. Lett. 2016, 109, 162104. [Google Scholar] [CrossRef] [Green Version]

- Rosenkranz, R. Failure localization with active and passive voltage contrast in FIB and SEM. J. Mater. Sci. Mater. Electron. 2011, 22, 1523–1535. [Google Scholar] [CrossRef]

- Simon-Najasek, M.; Jatzkowski, J.; Große, C.; Altmann, F. A New Technique for Non-Invasive Short-Localisation in Thin Dielectric Layers by Electron Beam Absorbed Current (EBAC) Imaging. In Proceedings of the 38th International Symposium for Testing and Failure Analysis, Pheonix, AZ, USA, 11–15 November 2012; pp. 61–66. [Google Scholar] [CrossRef]

- Bisi, D.; Chan, S.H.; Liu, X.; Yeluri, R.; Keller, S.; Meneghini, M.; Meneghesso, G.; Zanoni, E.; Mishra, U.K. On trapping mechanisms at oxide-traps in Al2O3/GaN metal-oxide-semiconductor capacitors. Appl. Phys. Lett. 2016, 108, 112104. [Google Scholar] [CrossRef]

- Lagger, P.; Steinschifter, P.; Reiner, M.; Stadtmüller, M.; Denifl, G.; Naumann, A.; Muller, J.; Wilde, L.; Sundqvist, J.; Pogany, D.; et al. Role of the dielectric for the charging dynamics of the dielectric/barrier interface in AlGaN/GaN based metal-insulator-semiconductor structures under forward gate bias stress. Appl. Phys. Lett. 2014, 105, 033512. [Google Scholar] [CrossRef]

- Sato, M.; Kamiyama, S.; Matsuki, T.; Ishikawa, D.; Ono, T.; Morooka, T.; Yugami, J.; Ikeda, K.; Ohji, Y. Study of a Negative Threshold Voltage Shift in Positive Bias Temperature Instability and a Positive Threshold Voltage Shift the Negative Bias Temperature Instability of Yttrium-Doped HfO2Gate Dielectrics. Jpn. J. Appl. Phys. 2010, 49, 04DC24. [Google Scholar] [CrossRef]

- Choi, M.; Janotti, A.; Van De Walle, C.G. Native point defects and dangling bonds in α-Al2O3. J. Appl. Phys. 2013, 113, 044501. [Google Scholar] [CrossRef]

- Swenson, B.L.; Mishra, U.K. Photoassisted high-frequency capacitance-voltage characterization of the Si3N4/GaN interface. J. Appl. Phys. 2009, 106, 064902. [Google Scholar] [CrossRef]

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Mukherjee, K.; De Santi, C.; Borga, M.; Geens, K.; You, S.; Bakeroot, B.; Decoutere, S.; Diehle, P.; Hübner, S.; Altmann, F.; et al. Challenges and Perspectives for Vertical GaN-on-Si Trench MOS Reliability: From Leakage Current Analysis to Gate Stack Optimization. Materials 2021, 14, 2316. https://doi.org/10.3390/ma14092316

Mukherjee K, De Santi C, Borga M, Geens K, You S, Bakeroot B, Decoutere S, Diehle P, Hübner S, Altmann F, et al. Challenges and Perspectives for Vertical GaN-on-Si Trench MOS Reliability: From Leakage Current Analysis to Gate Stack Optimization. Materials. 2021; 14(9):2316. https://doi.org/10.3390/ma14092316

Chicago/Turabian StyleMukherjee, Kalparupa, Carlo De Santi, Matteo Borga, Karen Geens, Shuzhen You, Benoit Bakeroot, Stefaan Decoutere, Patrick Diehle, Susanne Hübner, Frank Altmann, and et al. 2021. "Challenges and Perspectives for Vertical GaN-on-Si Trench MOS Reliability: From Leakage Current Analysis to Gate Stack Optimization" Materials 14, no. 9: 2316. https://doi.org/10.3390/ma14092316