Comparative Analysis of Reconfigurable Platforms for Memristor Emulation

Abstract

1. Introduction

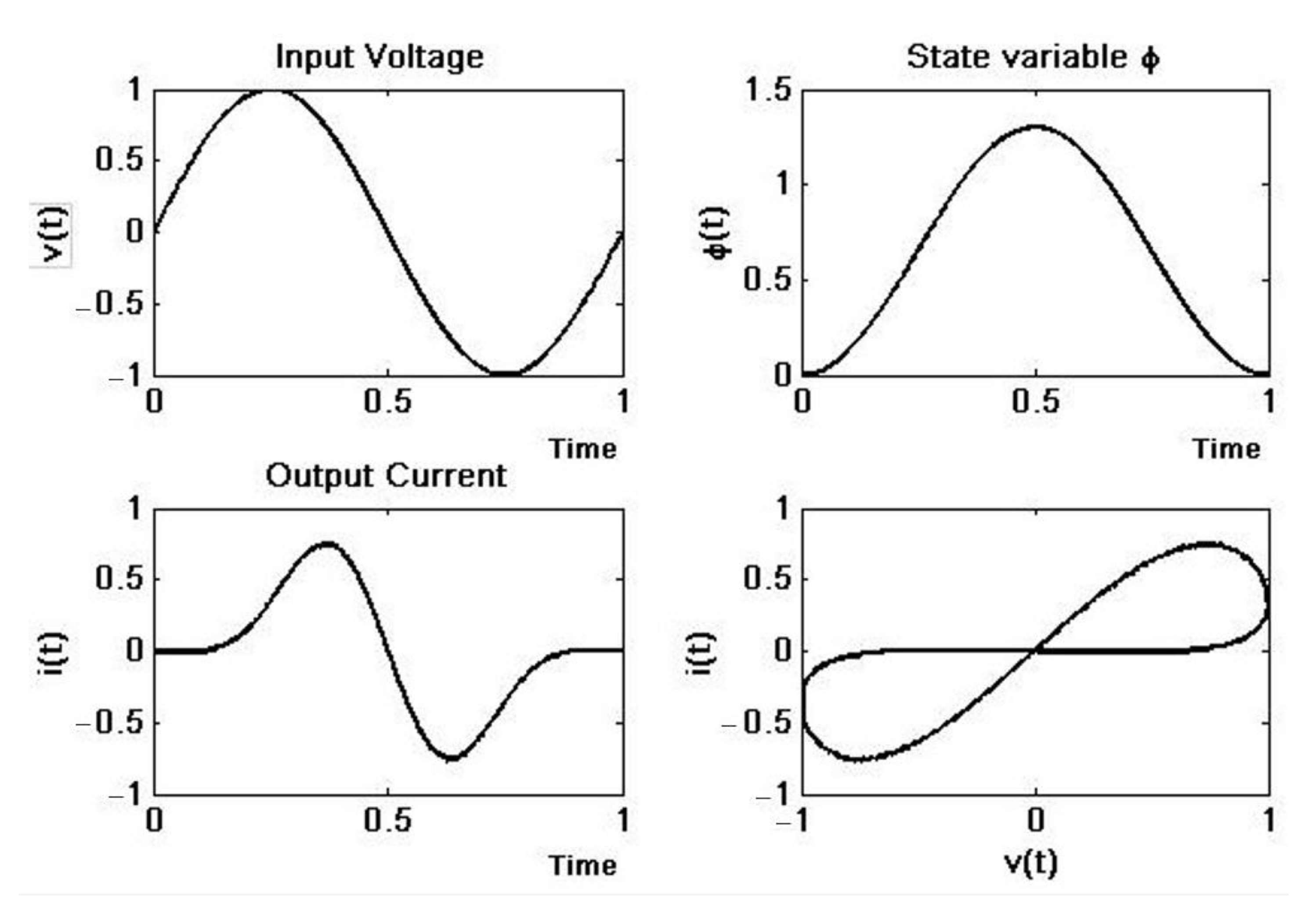

2. Materials and Methods

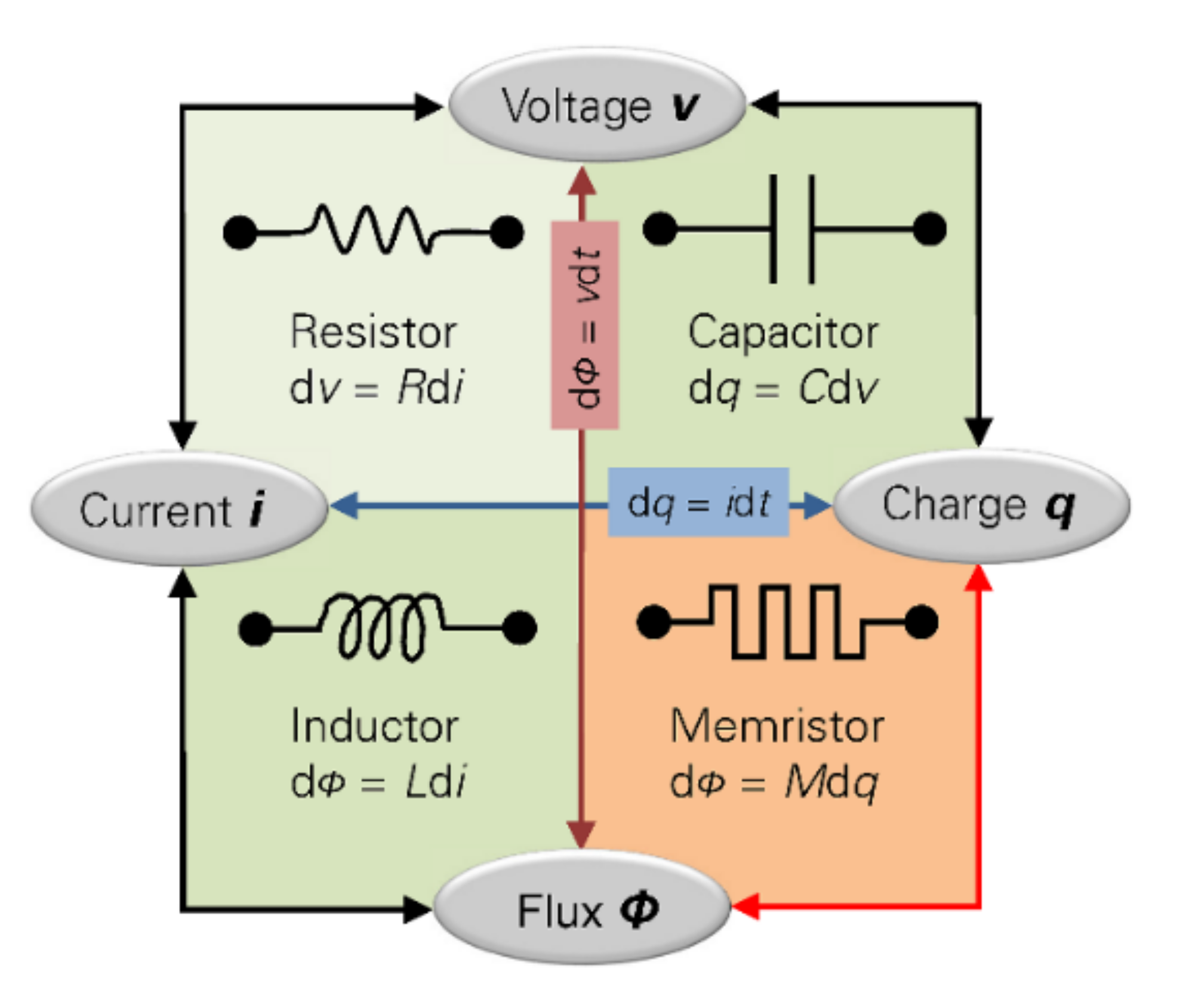

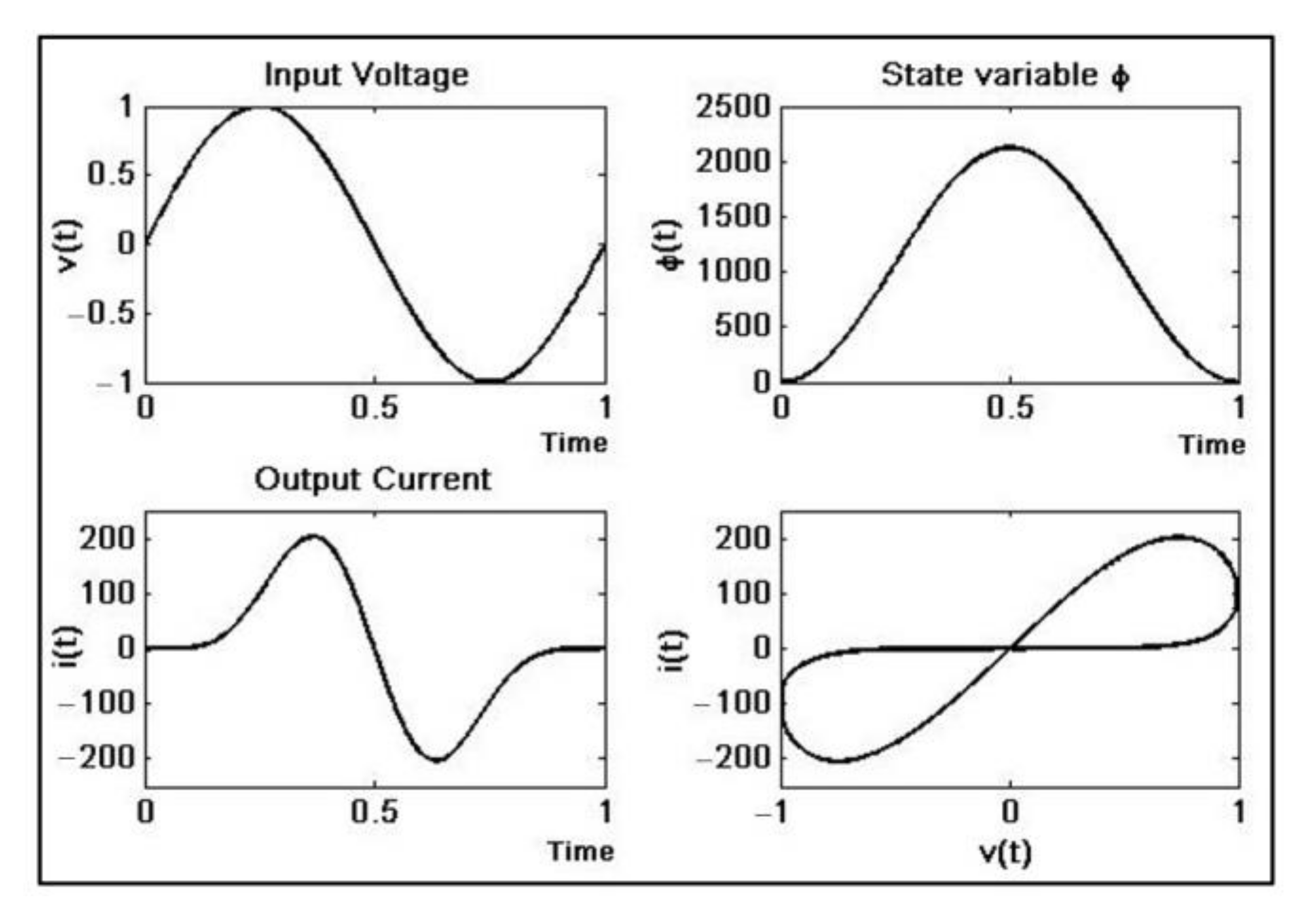

2.1. Memristor Overview

2.2. Circuit Implementation

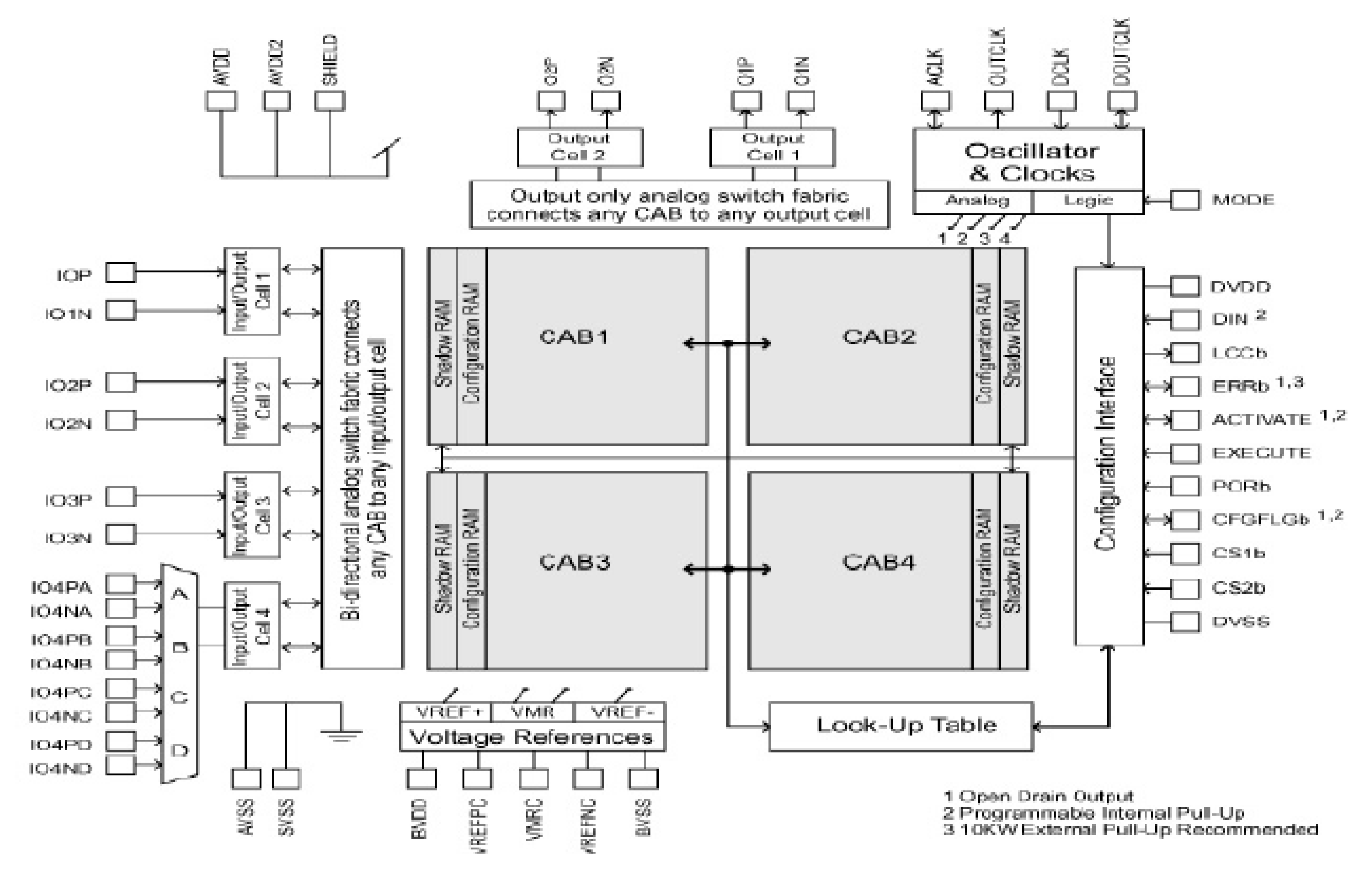

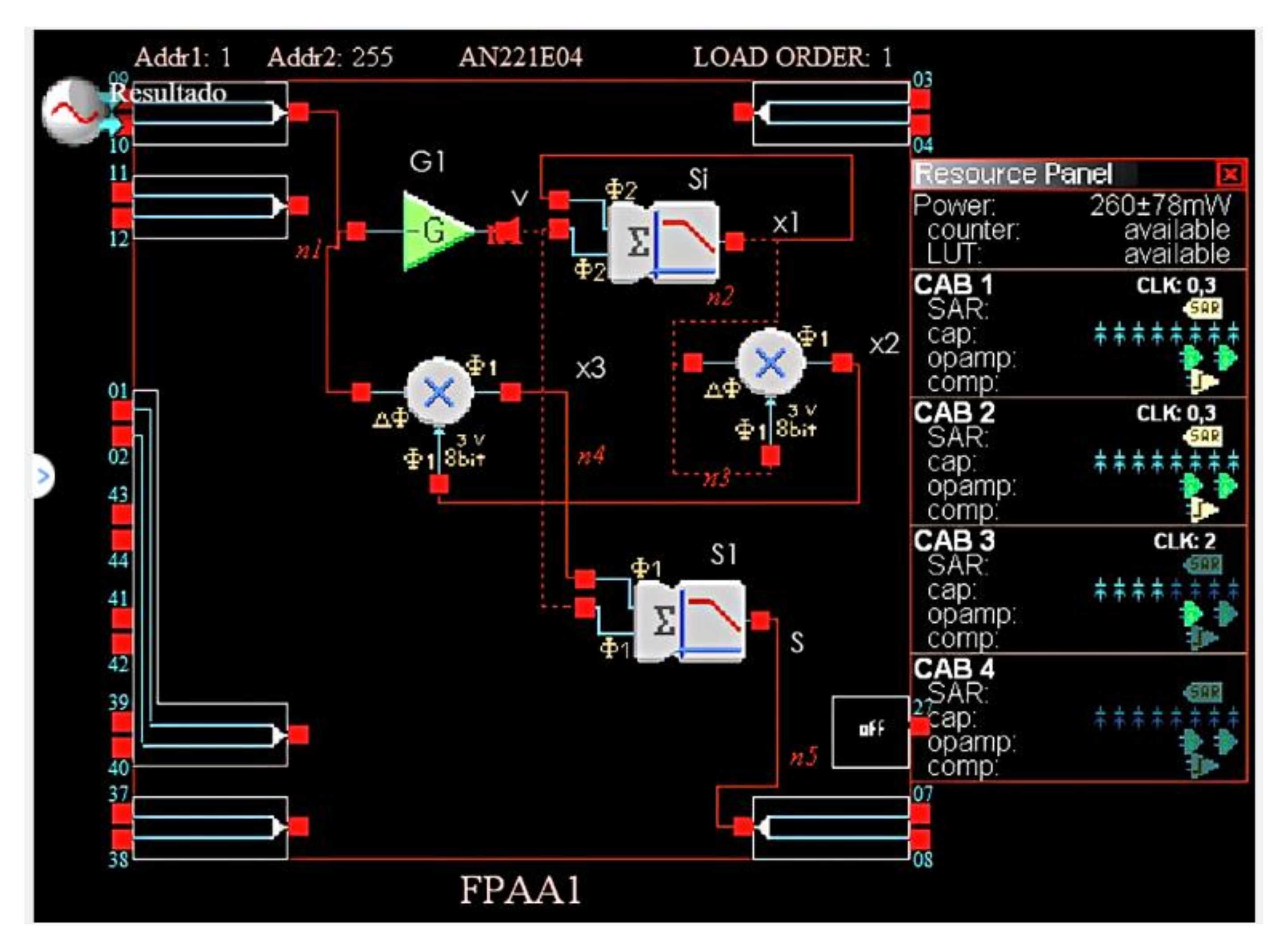

2.2.1. FPAA Emulator

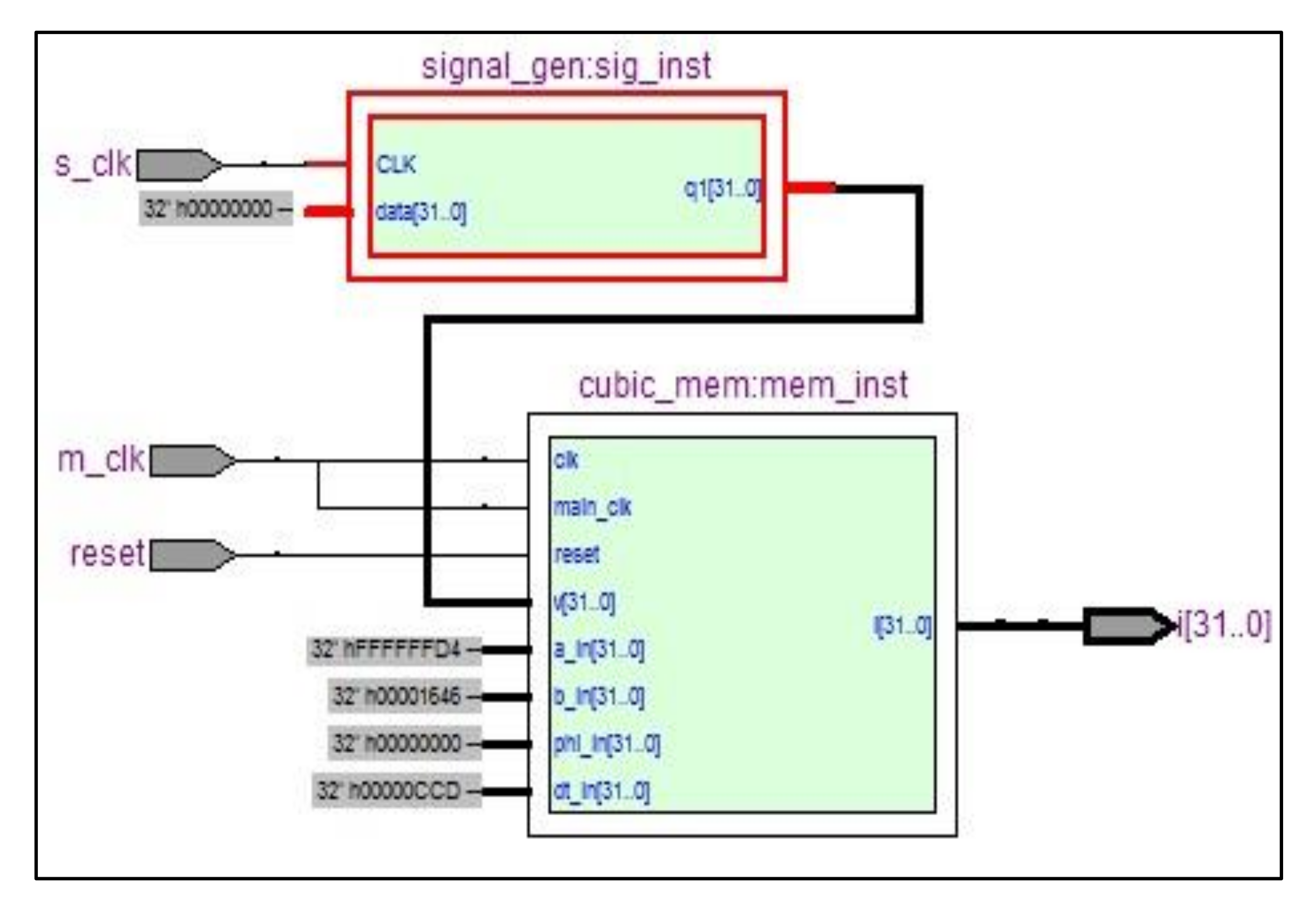

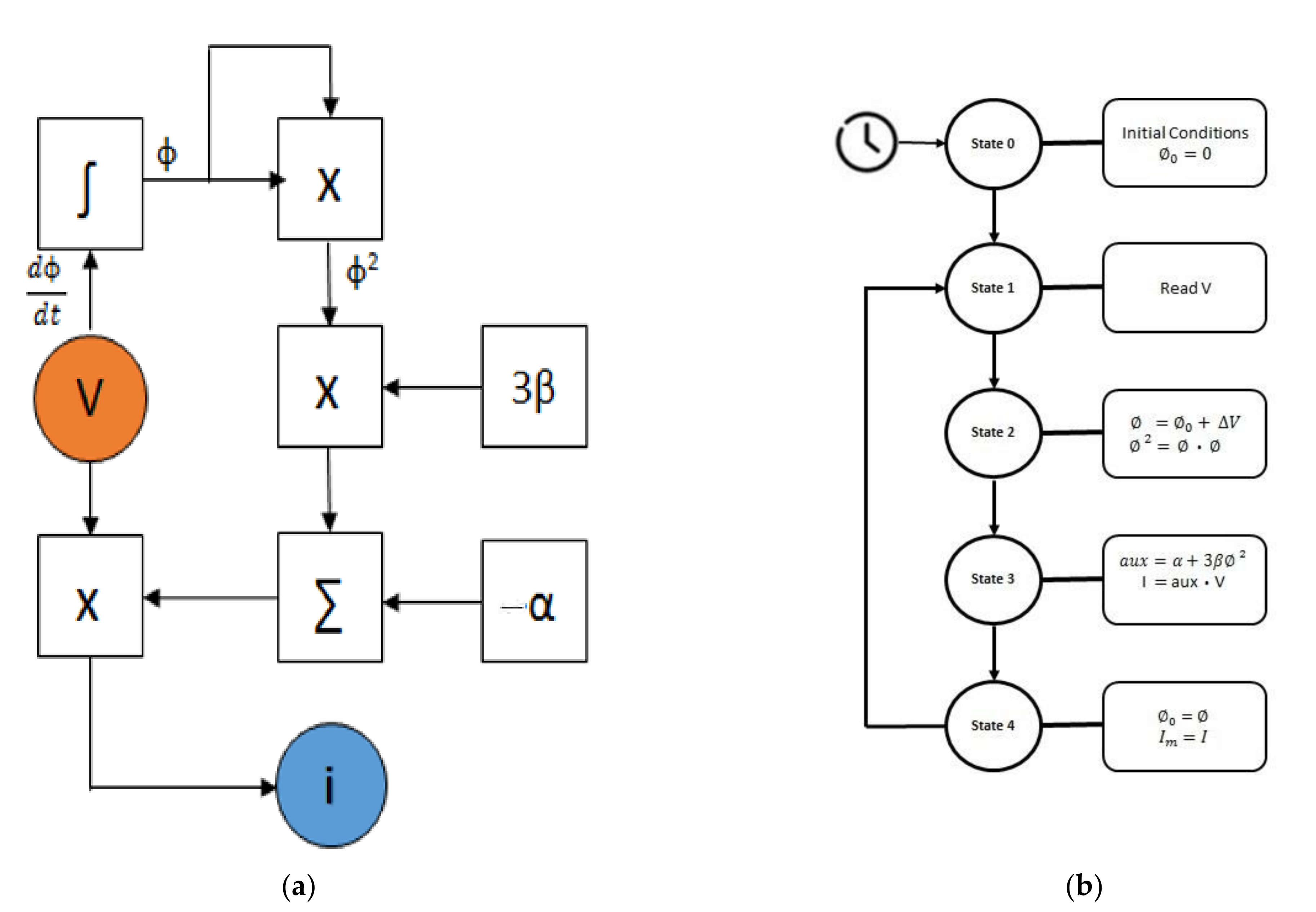

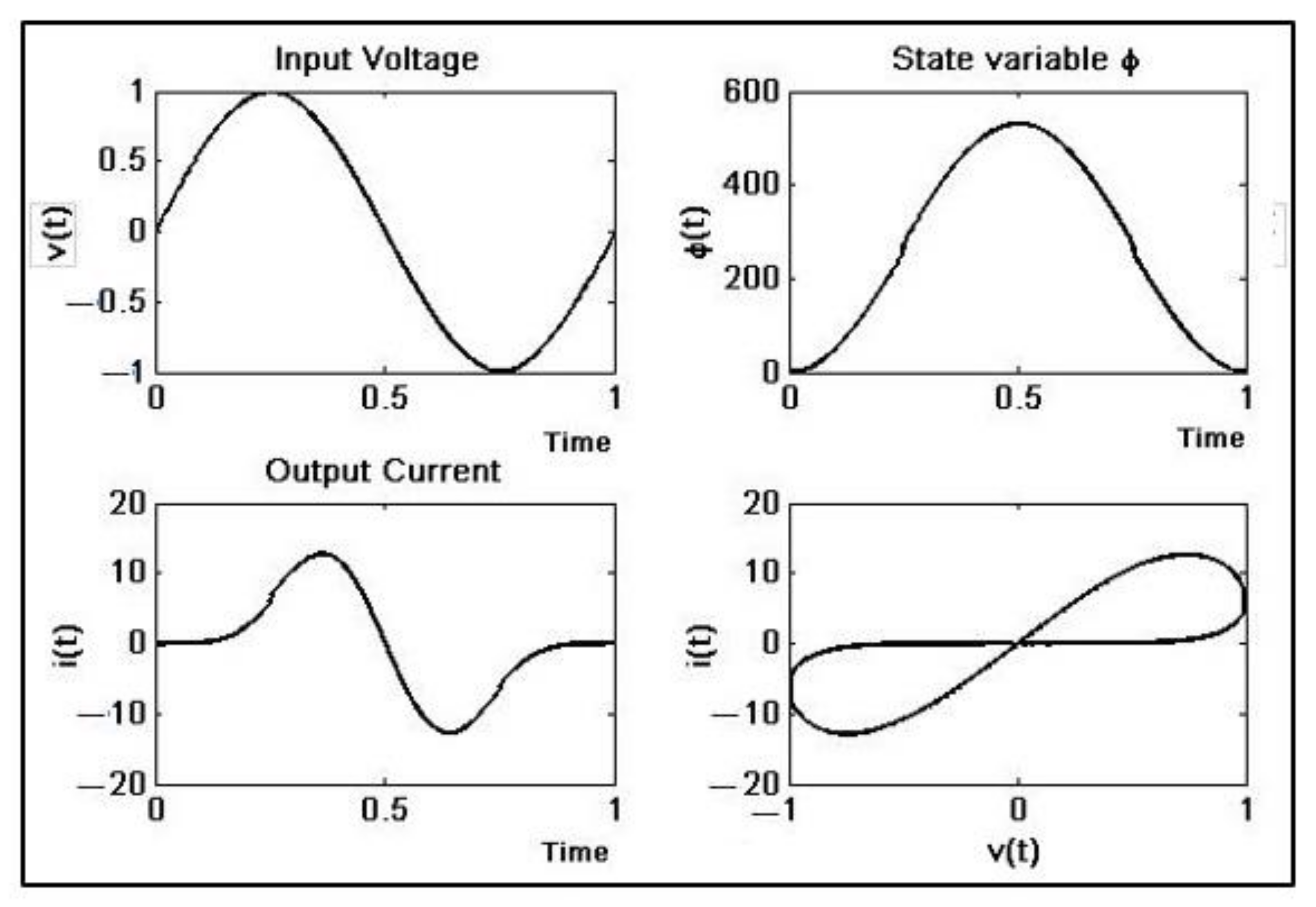

2.2.2. FPGA Implementation

3. Results and Discussion

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Chua, L. Memristor-The missing circuit element. IEEE Trans. Circuit Theory 1971, 18, 507–519. [Google Scholar] [CrossRef]

- Mohanty, S. Memristor: From Basics to Deployment. IEEE Potentials 2013, 32, 34–39. [Google Scholar] [CrossRef]

- Strukov, D.B.; Snider, G.S.; Stewart, D.R.; Williams, R.S. The missing memristor found. Nature 2008, 453, 80–83. [Google Scholar] [CrossRef] [PubMed]

- Yang, C.; Choi, H.; Park, S.; Sah, M.P.; Kim, H.; O Chua, L. A memristor emulator as a replacement of a real memristor. Semicond. Sci. Technol. 2014, 30, 015007. [Google Scholar] [CrossRef]

- Muthuswamy, B. Implementing Memristor Based Chaotic Circuits. Int. J. Bifurc. Chaos 2010, 20, 1335–1350. [Google Scholar] [CrossRef]

- Itoh, M.; Chua, L.O. Memristor Oscillators. Int. J. Bifurc. Chaos 2008, 18, 3183–3206. [Google Scholar] [CrossRef]

- Pershin, Y.; Di Ventra, M. Memristive circuits simulate memcapacitors and meminductors. Electron. Lett. 2010, 46, 517–518. [Google Scholar] [CrossRef]

- Muthuswamy, B.; Chua, L.O. Simplest Chaotic Circuit. Int. J. Bifurc. Chaos 2010, 20, 1567–1580. [Google Scholar] [CrossRef]

- Pershin, Y.V.; Di Ventra, M. Practical Approach to Programmable Analog Circuits With Memristors. IEEE Trans. Circuits Syst. I: Regul. Pap. 2010, 57, 1857–1864. [Google Scholar] [CrossRef]

- Bilotta, E.; Chiaravalloti, F.; Pantano, P. Spontaneous Synchronization in Two Mutually Coupled Memristor-Based Chua’s Circuits: Numerical Investigations. Math. Probl. Eng. 2014, 2014, e594962. [Google Scholar] [CrossRef]

- Ho, Y.; Huang, G.M.; Li, P. Nonvolatile Memristor Memory: Device Characteristics and Design Implications. In Proceedings of the 2009 IEEE/ACM International Conference on Computer-Aided Design-Digest of Technical Papers, San Jose, CA, USA, 28 December 2009; pp. 485–490. [Google Scholar]

- Wang, L.; Duan, M.; Duan, S. Memristive Perceptron for Combinational Logic Classification. Math. Probl. Eng. 2013, 2013, e625790. [Google Scholar] [CrossRef]

- Tran, T.; Rothenbuhler, A.; Smith, E.H.B.; Saxena, V.; Campbell, K.A. Reconfigurable Threshold Logic Gates using memristive devices. In Proceedings of the IEEE Subthreshold Microelectronics Conference (SubVT), Waltham, MA, USA, 9–10 October 2012; pp. 1–3. [Google Scholar] [CrossRef]

- Kim, H.; Sah, M.P.; Yang, C.; Cho, S.; Chua, L.O. Memristor Emulator for Memristor Circuit Applications. IEEE Trans. Circuits Syst. I: Regul. Pap. 2012, 59, 2422–2431. [Google Scholar] [CrossRef]

- Dong, Z.; Duan, S.; Hu, X.; Wang, L.; Li, H. A Novel Memristive Multilayer Feedforward Small-World Neural Network with Its Applications in PID Control. Sci. World J. 2014, 2014, e394828. [Google Scholar] [CrossRef] [PubMed]

- Afifi, A.; Ayatollahi, A.; Raissi, F. STDP implementation using memristive nanodevice in CMOS-Nano neuromorphic networks. IEICE Electron. Express 2009, 6, 148–153. [Google Scholar] [CrossRef][Green Version]

- Jo, S.H.; Chang, T.; Ebong, I.; Bhadviya, B.B.; Mazumder, P.; Lu, W. Nanoscale Memristor Device as Synapse in Neuromorphic Systems. Nano Lett. 2010, 10, 1297–1301. [Google Scholar] [CrossRef]

- Saadeldeen, H.; Franklin, D.; Long, G.; Hill, C.; Browne, A.; Strukov, D.; Sherwood, T.; Chong, F.T. Memristors for Neural Branch Prediction: A Case Study in Strict Latency and Write Endurance Challenges. In Proceedings of the ACM International Conference on Computing Frontiers, Association for Computing Machinery, Sicily, Italy, 11–13 May 2013; pp. 1–10. [Google Scholar] [CrossRef]

- Ebong, I.E.; Mazumder, P. CMOS and Memristor-Based Neural Network Design for Position Detection. Proc. IEEE 2011, 100, 2050–2060. [Google Scholar] [CrossRef]

- Ziegler, M.; Soni, R.; Patelczyk, T.; Ignatov, M.; Bartsch, T.; Meuffels, P.; Kohlstedt, H. An Electronic Version of Pavlov’s Dog. Adv. Funct. Mater. 2012, 22, 2744–2749. [Google Scholar] [CrossRef]

- Chen, L.; Li, C.; Huang, T.; Wang, X. Quick noise-tolerant learning in a multi-layer memristive neural network. Neurocomputing 2014, 129, 122–126. [Google Scholar] [CrossRef]

- Zamarreño-Ramos, C.; Camuñas-Mesa, L.A.; Pérez-Carrasco, J.A.; Masquelier, T.; Serrano-Gotarredona, T.; Linares-Barranco, B. On Spike-Timing-Dependent-Plasticity, Memristive Devices, and Building a Self-Learning Visual Cortex. Front. Behav. Neurosci. 2011, 5, 26. [Google Scholar] [CrossRef]

- Duan, S.; Zhang, Y.; Hu, X.; Wang, L.; Li, C. Memristor-based chaotic neural networks for associative memory. Neural Comput. Appl. 2014, 25, 1437–1445. [Google Scholar] [CrossRef]

- Sheri, A.M.; Hwang, H.; Jeon, M.; Lee, B.-G. Neuromorphic Character Recognition System with Two PCMO Memristors as a Synapse. IEEE Trans. Ind. Electron. 2013, 61, 2933–2941. [Google Scholar] [CrossRef]

- Chen, L.; Li, C.; Huang, T.; Chen, Y.; Wen, S.; Qi, J. A synapse memristor model with forgetting effect. Phys. Lett. A 2013, 377, 3260–3265. [Google Scholar] [CrossRef]

- Cruz-Albrecht, J.M.; DeRosier, T.; Srinivasa, N. A scalable neural chip with synaptic electronics using CMOS integrated memristors. Nanotechnology 2013, 24, 384011. [Google Scholar] [CrossRef] [PubMed]

- Knowm. Available online: https://knowm.org/ (accessed on 17 May 2022).

- Zhu, L.J.; Wang, F.Q. Design and analysis of new meminductor model based on Knowm memristor. Acta Phys. Sin. 2019, 68, 198501. [Google Scholar] [CrossRef]

- Memristors, KnowM. Available online: https://knowm.org/downloads/Knowm_Memristors.pdf (accessed on 17 May 2022).

- Pershin, Y.; Di Ventra, M. SPICE Model of Memristive Devices with Threshold. Radioengineering 2012, 22, 2. [Google Scholar]

- Wang, Y.; Fei, W.; Yu, H. SPICE simulator for hybrid CMOS memristor circuit and system. In Proceedings of the 2012 13th International Workshop on Cellular Nanoscale Networks and Their Applications, Turin, Italy, 29–31 August 2012; pp. 1–6. [Google Scholar] [CrossRef]

- Biolek, D.; Biolek, Z.; Biolkova, V. SPICE modeling of memristive, memcapacitative and meminductive systems. In Proceedings of the 2009 European Conference on Circuit Theory and Design, Antalya, Turkey, 23–27 August 2009; pp. 249–252. [Google Scholar] [CrossRef]

- Zaplatilek, K. Memristor Modeling in MATLAB®&Simulink®. In Proceedings of the 5th European Computing Conference, Paris, France, 28–30 April 2011; pp. 62–67. [Google Scholar]

- Borgese, G.; Vena, S.; Pantano, P.; Pace, C.; Bilotta, E. Simulation, Modeling, and Analysis of Soliton Waves Interaction and Propagation in CNN Transmission Lines for Innovative Data Communication and Processing. Discret. Dyn. Nat. Soc. 2015, 2015, 1–13. [Google Scholar] [CrossRef]

- Pershin, Y.V.; Di Ventra, M. Experimental demonstration of associative memory with memristive neural networks. Neural Networks 2010, 23, 881–886. [Google Scholar] [CrossRef]

- Biolek, D.; Bajer, J.; Biolkova, V.; Kolka, Z. Mutators for transforming nonlinear resistor into memristor. In Proceedings of the 2011 20th European Conference on Circuit Theory and Design (ECCTD), Linkoping, Sweden, 29–31 August 2011; pp. 488–491. [Google Scholar] [CrossRef]

- Fitch, A.; Lu, H.; Wang, X.; Sreeram, V.; Qi, W. Realization of an analog model of memristor based on light dependent resistor. In Proceedings of the 2012 IEEE International Symposium on Circuits and Systems (ISCAS), Seoul, Korea, 20–23 May 2012; pp. 1139–1142. [Google Scholar] [CrossRef]

- Valsa, J.; Biolek, D.; Biolek, Z. An analogue model of the memristor. Int. J. Numer. Model. Electron. Netw. Devices Fields 2010, 24, 400–408. [Google Scholar] [CrossRef]

- Ila, V.; Batlle, J.; Cufi, X.; Garcia, R. Recent Trends in Fpaa Devices. In Multimedia Information Processing; World Scientific: Singapore, 2002; pp. 186–190. [Google Scholar] [CrossRef]

- Borgese, G.; Pace, C.; Pantano, P.; Bilotta, E. Reconfigurable Implementation of a CNN-UM Platform for Fast Dynamical Systems Simulation. Appl. Electron. Pervading Ind. Environ. Soc. 2014, 289, 85–101. [Google Scholar] [CrossRef]

- Borgese, G.; Pace, C.; Pantano, P.; Bilotta, E. FPGA-based distributed computing microarchitecture for complex physical dynamics investigation. IEEE Trans. Neural Networks Learn. Syst. 2013, 24, 1390–1399. [Google Scholar] [CrossRef]

- Ananth, R.S. Signal Processing Structures for Power-Supervisory and Low-Frequency Applications (Dissertation); National Library of Canada: Ottawa, ON, Canada, 1996. [Google Scholar]

- Garcia, P.; Compton, K.; Schulte, M.; Blem, E.; Fu, W. An Overview of Reconfigurable Hardware in Embedded Systems. EURASIP J. Embed. Syst. 2006, 2006, 1–19. [Google Scholar] [CrossRef]

- Hulub, M.; Frasca, M.; Fortuna, L.; Arena, P. Implementation and synchronization of 3×3 grid scroll chaotic circuits with analog programmable devices. Chaos: Interdiscip. J. Nonlinear Sci. 2006, 16, 013121. [Google Scholar] [CrossRef] [PubMed]

- Kilic, R.; Dalkiran, F.Y. Programmable Design and Implementation of a Chaotic System Utilizing Multiple Nonlinear Functions. Turk. J. Electr. Eng. Comput. Sci. 2010, 18, 647–656. [Google Scholar] [CrossRef]

- Volos, C.; Kyprianidis, I.; Stavrinides, S.G.; Stouboulos, I.N.; Anagnostopoulos, A.N. Memristors: A New Approach in Nonlinear Circuits Design. In Proceedings of the 14th WSEAS International Conference on Communications, World Scientific and Engineering Academy and Society (WSEAS), Stevens Point, WI, USA, 23–25 July 2010; pp. 25–30. [Google Scholar]

- Fitch, A.L. Development of Memristor Based Circuits; World Scientific: Singapore, 2013. [Google Scholar]

- Kavehei, O.; Kim, Y.-S.; Iqbal, A.; Eshraghian, K.; Al-Sarawi, S.; Abbott, D. The fourth element: Insights into the memristor. In Proceedings of the 2009 International Conference on Communications, Circuits and Systems, Milpitas, CA, USA, 23–25 July 2009; pp. 921–927. [Google Scholar] [CrossRef]

- Chua, L.O.; Kang, S.M. Memristive devices and systems. Proc. IEEE 1976, 64, 209–223. [Google Scholar] [CrossRef]

- Kavehei, O.; Iqbal, A.; Kim, Y.S.; Eshraghian, K.; Al-Sarawi, S.; Abbott, D. The fourth element: Characteristics, modelling and electromagnetic theory of the memristor. Proc. R. Soc. A Math. Phys. Eng. Sci. 2010, 466, 2175–2202. [Google Scholar] [CrossRef]

- Moshnyaga, V.; Esseling, M.; Sudheendra, L.; Lebedev, O.I.; Gehrke, K.; van Tendeloo, G.; Samwer, K. Memristor Behaviour in Nano-Sized Vertical Lsmo/Lsmo Tunnel Junctions. arXiv 2010, arXiv:1002.0495. [Google Scholar]

- Muthuswamy, B.; Kokate, P. Memristor-Based Chaotic Circuits. IETE Technol. Rev. 2009, 26, 417. [Google Scholar] [CrossRef]

- Mutlu, R.; Karakulak, E. A methodology for memristance calculation. Turk. J. Electr. Eng. Comput. Sci. 2014, 22, 121–131. [Google Scholar] [CrossRef]

- Kilic, R. A Practical Guide for Studying Chua’s Circuits; World Scientific: Singapore, 2010; Volume 71. [Google Scholar]

- Butcher, J.C. Numerical Methods for Ordinary Differential Equations; Wiley: Hoboken, NJ, USA, 2008. [Google Scholar]

- Zhao, J.; Kim, Y.-B. Circuit implementation of FitzHugh-Nagumo neuron model using Field Programmable Analog Arrays. In Proceedings of the 2007 50th Midwest Symposium on Circuits and Systems, Montreal, QC, Canada, 5–8 August 2007; pp. 772–775. [Google Scholar] [CrossRef]

- Guerrero-Rivera, R.; Morrison, A.; Diesmann, M.; Pearce, T.C. Programmable logic construction kits for hyper-real-time neuronal modeling. Neural Comput. 2006, 18, 2651–2679. [Google Scholar] [CrossRef]

- Terasic Technologies. Terasic-All FPGA Boards-Stratix IV-Altera DE4 Development and Education Board. Available online: http://www.terasic.com.tw/cgi-bin/page/archive.pl?Language=English&CategoryNo=138&No= (accessed on 12 December 2021).

- EDA Playground. Available online: https://www.edaplayground.com/ (accessed on 12 December 2021).

| Name | Options | Parameters | Clocks |

|---|---|---|---|

| Multiplier 1 (Multiplier v1.2.2)  Anadigm (Approved) | Sample and Hold Off Y Input Full Scale 3 Volts | Multiplication Factor 1.00 | Clock A 125 kHz (Chip Clock 3) Clock B 2 MHz (Chip Clock 0) |

| Multiplier 2 (Multiplier v1.2.2)  Anadigm (Approved) | Sample and Hold Off Y Input Full Scale 3 Volts | Multiplication Factor 1.00 | Clock A 125 kHz (Chip Clock 3) Clock B 2 MHz (Chip Clock 0) |

| SumFilter 2 (SumFilter v1.1.3)  Anadigm (Approved) | Output Changes On Phase 2 Input 1 Non-inverting Input 2 Non-inverting Input 3 Off | Corner Frequency [kHz] 12.5 Gain 1 (Upper Input) 0.870 Gain 2 (Lower Input) 0.0676 | Clock A 125 kHz (Chip Clock 3) |

| G1 (GainInv v1.1.4)  Anadigm (Approved) | Gain 0.0100 | Clock A 2 MHz (Chip Clock 0) | |

| SumFilter 2 (SumFilter v1.1.3)  Anadigm (Approved) | Output Changes On Phase 1 Input 1 Non-inverting Input 2 Non-inverting Input 3 Off | Corner Frequency [kHz] 100.0 Gain 1 (Upper Input) 1.00 Gain 2 (Lower Input) 0.0500 | Clock A 1 MHz (Chip Clock 2) |

| Number | Binary | Hexadecimal |

|---|---|---|

| 1.0 | 0_000000000000001.0000000000000000 | “00010000” |

| 0.025 | 0_000000000000000.0000011001100110 | “00000666” |

| FPGA Resource | Used Resources |

|---|---|

| Combinational ALUTs | 10,345 |

| Total Registers | 10,345 |

| DSP Block 18-bit Elements | 118 |

| Total Block memory bits | 4,434,148 |

| Logic utilization | 9% |

| FPGA Resource | Used Resources |

|---|---|

| Combinational ALUTs | 1298 |

| Total Registers | 16,105 |

| DSP Block 18-bit Elements | 118 |

| Total Block memory bits | 100,352 |

| Logic utilization | 1% |

| Fs | One Period Time | ||

|---|---|---|---|

| MHz | Nro Samples | Time | |

| Matlab | 8 | 133,366 | 64.6 ms |

| FPAA | 4 | 66,667 | 16.7 ms |

| FPGA | 2 | 32,347 | 16.7 ms |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Mayacela, M.; Rentería, L.; Contreras, L.; Medina, S. Comparative Analysis of Reconfigurable Platforms for Memristor Emulation. Materials 2022, 15, 4487. https://doi.org/10.3390/ma15134487

Mayacela M, Rentería L, Contreras L, Medina S. Comparative Analysis of Reconfigurable Platforms for Memristor Emulation. Materials. 2022; 15(13):4487. https://doi.org/10.3390/ma15134487

Chicago/Turabian StyleMayacela, Margarita, Leonardo Rentería, Luis Contreras, and Santiago Medina. 2022. "Comparative Analysis of Reconfigurable Platforms for Memristor Emulation" Materials 15, no. 13: 4487. https://doi.org/10.3390/ma15134487

APA StyleMayacela, M., Rentería, L., Contreras, L., & Medina, S. (2022). Comparative Analysis of Reconfigurable Platforms for Memristor Emulation. Materials, 15(13), 4487. https://doi.org/10.3390/ma15134487