Failures of Cu-Cu Joints under Temperature Cycling Tests

Abstract

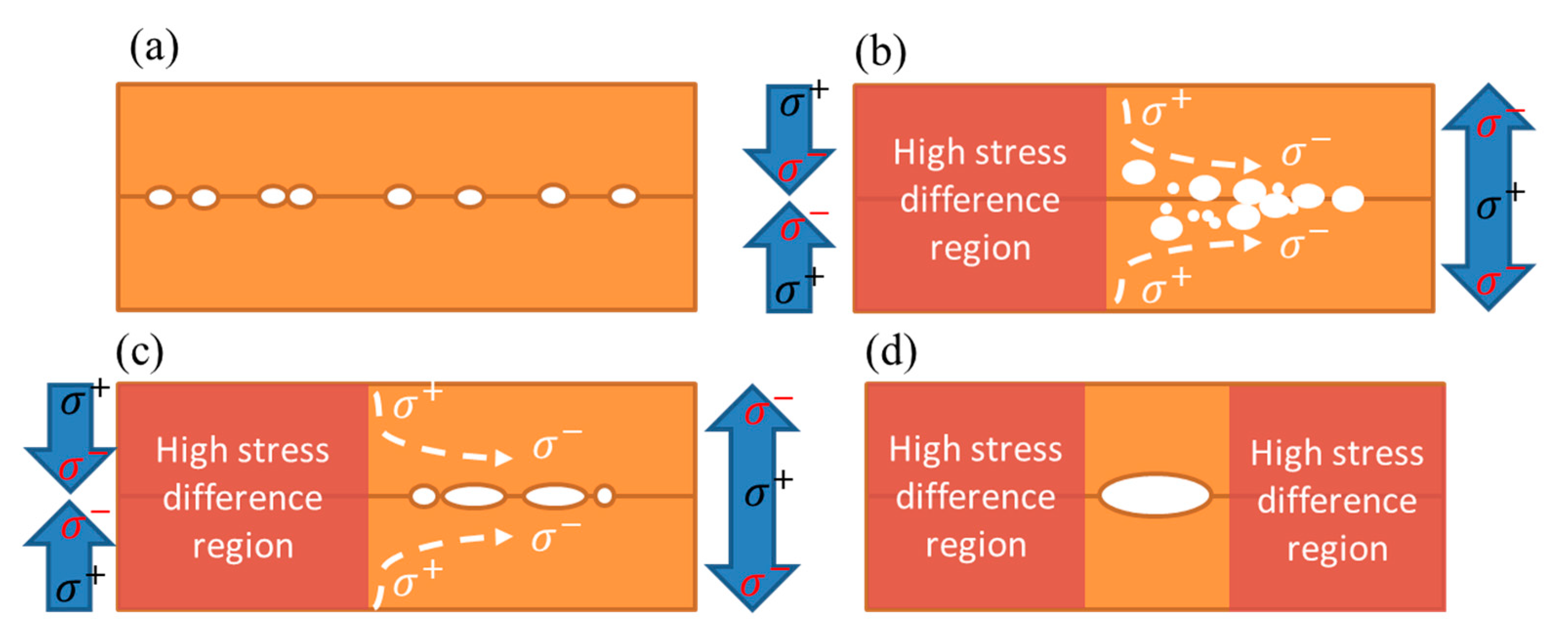

:1. Introduction

2. Experimental and Simulation Section

3. Results and Discussion

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Kagawa, Y.; Fujii, N.; Aoyagi, K.; Kobayashi, Y.; Nishi, S.; Todaka, N.; Takeshita, S.; Taura, J.; Takahashi, H.; Nishimura, Y. Novel Stacked CMOS Image Sensor with Advanced Cu2Cu Hybrid Bonding. In Proceedings of the IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 3–7 December 2016; IEEE: Piscataway, NJ, USA; pp. 8.4.1–8.4.4. [Google Scholar]

- Tu, K.-N. Reliability challenges in 3D IC packaging technology. Microelectron. Reliab. 2011, 51, 517–523. [Google Scholar] [CrossRef]

- Tanida, K.; Umemoto, M.; Morifuji, T.; Kajiwara, R.; Ando, T.; Tomita, Y.; Tanaka, N.; Takahashi, K. Au bump interconnection in 20 µm pitch on 3D chip stacking technology. Jpn. J. Appl. Phys. 2003, 42, 6390. [Google Scholar] [CrossRef]

- Gao, G.; Mirkarimi, L.; Fountain, G.; Wang, L.; Uzoh, C.; Workman, T.; Guevara, G.; Mandalapu, C.; Lee, B.; Katkar, R. Scaling Package Interconnects below 20 µm Pitch with Hybrid Bonding. In Proceedings of the IEEE 68th Electronic Components and Technology Conference (ECTC), San Francisco, CA, USA, 29 May–1 June 2018; IEEE: Piscataway, NJ, USA; pp. 314–322. [Google Scholar]

- Tsai, Y.-C.; Hu, H.-W.; Chen, K.-N. Low temperature copper-copper bonding of non-planarized copper pillar with passivation. IEEE Electron. Device Lett. 2020, 41, 1229–1232. [Google Scholar] [CrossRef]

- Beilliard, Y.; Moreau, S.; Di Cioccio, L.; Coudrain, P.; Romano, G.; Nowodzinski, A.; Aussenac, F.; Jouneau, P.-h.; Rolland, E.; Signamarcheix, T. Advances toward Reliable High Density Cu-Cu Interconnects by Cu-SiO2 Direct Hybrid Bonding. In Proceedings of the International 3D Systems Integration Conference (3DIC), Kinsdale, Ireland, 1–3 December 2014; IEEE: Piscataway, NJ, USA; pp. 1–8. [Google Scholar]

- Lim, D.; Ang, X.; Wei, J.; Ng, C.; Tan, C. Void density reduction at the Cu–Cu bonding interface by means of prebonding surface passivation with self-assembled monolayer. Electrochem. Solid-State Lett. 2010, 13, H412. [Google Scholar] [CrossRef]

- Ide, E.; Angata, S.; Hirose, A.; Kobayashi, K.F. Metal–metal bonding process using Ag metallo-organic nanoparticles. Acta Mater. 2005, 53, 2385–2393. [Google Scholar] [CrossRef]

- Kief, M.; Egelhoff, W., Jr. Growth and structure of Fe and Co thin films on Cu (111), Cu (100), and Cu (110): A comprehensive study of metastable film growth. Phys. Rev. B 1993, 47, 10785. [Google Scholar] [CrossRef]

- Shie, K.-C.; Gusak, A.; Tu, K.; Chen, C. A kinetic model of copper-to-copper direct bonding under thermal compression. J. Mater. Res. Technol. 2021, 15, 2332–2344. [Google Scholar] [CrossRef]

- Shie, K.-C.; Juang, J.-Y.; Chen, C. Instant Cu-to-Cu direct bonding enabled by <111>-oriented nanotwinned Cu bumps. Jpn. J. Appl. Phys. 2019, 59, SBBA03. [Google Scholar] [CrossRef]

- Shie, K.-C.; Hsu, P.-N.; Li, Y.-J.; Tran, D.-P.; Chen, C. Failure Mechanisms of Cu–Cu bumps under thermal cycling. Materials 2021, 14, 5522. [Google Scholar] [CrossRef]

- Gondcharton, P.; Imbert, B.; Benaissa, L.; Verdier, M. Voiding phenomena in copper-copper bonded structures: Role of creep. ECS J. Solid State Sci. Technol. 2015, 4, P77. [Google Scholar] [CrossRef] [Green Version]

- Gondcharton, P.; Imbert, B.; Benaissa, L.; Fournel, F.; Verdier, M. Effect of copper–copper direct bonding on voiding in metal thin films. J. Electron. Mater. 2015, 44, 4128–4133. [Google Scholar] [CrossRef]

- Cocks, A.; Ashby, M. On creep fracture by void growth. Prog. Mater. Sci. 1982, 27, 189–244. [Google Scholar] [CrossRef]

- Su, P.; Rzepka, S.; Korhonen, M.; Li, C. The effects of underfill on the reliability of flip chip solder joints. J. Electron. Mater. 1999, 28, 1017–1022. [Google Scholar] [CrossRef]

- Ernst, L.; Van’t Hof, C.; Yang, D.; Kiasat, M.; Zhang, G.; Bressers, H.; Caers, J.; Den Boer, A.; Janssen, J. Mechanical modeling and characterization of the curing process of underfill materials. J. Electron. Packag. 2002, 124, 97–105. [Google Scholar] [CrossRef]

- Tu, P.; Chan, Y.; Hung, K. Reliability of microBGA assembly using no-flow underfill. Microelectron. Reliab. 2001, 41, 1993–2000. [Google Scholar] [CrossRef]

- Banijamali, B.; Chiu, C.-C.; Hsieh, C.-C.; Lin, T.-S.; Hu, C.; Hou, S.-Y.; Ramalingam, S.; Jeng, S.-P.; Madden, L.; Yu, D.C. Reliability Evaluation of a CoWoS-Enabled 3D IC Package. In Proceedings of the IEEE 63rd Electronic Components and Technology Conference, Las Vegas, NV, USA, 28–31 May 2013; IEEE: Piscataway, NJ, USA; pp. 35–40. [Google Scholar]

- Darveaux, R. Thermal Cycle Fatigue Life Prediction for Flip Chip Solder Joints. In Proceedings of the IEEE 64th Electronic Components and Technology Conference (ECTC), Lake Buena Vista, FL, USA, 27–30 May 2014; IEEE: Piscataway, NJ, USA; pp. 703–711. [Google Scholar]

- Banijamali, B.; Ramalingam, S.; Nagarajan, K.; Chaware, R. Advanced Reliability Study of TSV Interposers and Interconnects for the 28 nm Technology FPGA. In Proceedings of the IEEE 61st Electronic Components and Technology Conference (ECTC), Lake Buena Vista, FL, USA, 31 May–3 June 2011; IEEE: Piscataway, NJ, USA; pp. 285–290. [Google Scholar]

- Taluy, A.; Lhostis, S.; Jouve, A.; Garnier, G.; Dezandre, E.; Farcy, A.; Chéramy, S.; Sillon, N.; Sylvestre, A. Performances of Wafer-Level UnderFill with 50µm Pitch Interconnections: Comparison with Conventional Underfill. In Proceedings of the IEEE 13th Electronics Packaging Technology Conference, Singapore, 7–9 September 2011; IEEE: Piscataway, NJ, USA; pp. 129–134. [Google Scholar]

- Wachtman, J.B.; Tefft, W.E.; Lam, D.G.; Apstein, C.S. Exponential temperature dependence of Young’s modulus for several oxides. Phys. Rev. 1961, 122, 1754–1759. [Google Scholar]

- Butts, D.A.; Gale, W.F. Equilibrium Diagrams, in Smithells Metals Reference Book; Elsevier: Amsterdam, The Netherlands, 2004; pp. 11-1–11-534. [Google Scholar]

- Jin, S.; Mavoori, H. Low-thermal-expansion copper composites via negative CTE metallic elements. JOM 1998, 50, 70–72. [Google Scholar] [CrossRef]

- Subramaniam, C.; Yasuda, Y.; Takeya, S.; Ata, S.; Nishizawa, A.; Futaba, D.; Yamada, T.; Hata, K. Carbon nanotube-copper exhibiting metal-like thermal conductivity and silicon-like thermal expansion for efficient cooling of electronics. Nanoscale 2014, 6, 2669–2674. [Google Scholar] [CrossRef]

- Wang, X.; Wang, X.; Liu, M.; Crimp, M.A.; Wang, Y.; Qu, Z. Anisotropic thermal expansion coefficient of multilayer graphene reinforced copper matrix composites. J. Alloys Compd. 2018, 755, 114–122. [Google Scholar] [CrossRef]

- Wu, Y.S.; Lai, T.-Y.; Li, M.; Lu, T.-F.; Wang, Y.H.; Tseng, T.Y. Bonding mechanisms of roughened nanotwinned-Cu surface at temperature as low as 120 °C. ECS J. Solid State Sci. Technol. 2020, 9, 124005. [Google Scholar] [CrossRef]

- Majzoobi, G.H.; Kashfi, M.; Bonora, N.; Iannitti, G.; Ruggiero, A.; Khademi, E. Damage characterization of aluminum 2024 thin sheet for different stress triaxialities. Arch. Civ. Mech. Eng. 2018, 18, 702–712. [Google Scholar] [CrossRef]

- Liu, J.; Zhang, G.; Wang, B.; Li, W.; Wang, J. Gate failure physics of SiC MOSFETs under short-circuit stress. IEEE Electron Device Lett. 2019, 41, 103–106. [Google Scholar] [CrossRef]

- Flinn, P.A. Mechanical stress in VLSI interconnections: Origins, effects, measurement, and modeling. MRS Bull. 1995, 20, 70–73. [Google Scholar] [CrossRef]

| Materials | CTE (ppm/°C) | Thermal Conductivity (W/m·K) | Young’s Modulus (Pa) | Poisson’s Ratio |

|---|---|---|---|---|

| Cu | 16.8 | 413 (at −73 °C) 401 (at 0 °C) 392 (at 127 °C) | 1.1 × 1011 | 0.34 |

| PBO (HD-8820) | 64.0 | 0.2 | 2.3 × 103 | 0.30 |

| UF (U8410-314A) | 3.0 × 101 (<115 °C) 1.1 × 102 (130 °C) | 0.4 | 8.5 × 109 (<115 °C) 2.0 × 108 (130 °C) | 0.30 |

| SiO2 | 2.7 | 1.3 | 6.5 × 1010 | 0.28 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Hsu, P.-N.; Shie, K.-C.; Tran, D.-P.; Tsou, N.-T.; Chen, C. Failures of Cu-Cu Joints under Temperature Cycling Tests. Materials 2022, 15, 4944. https://doi.org/10.3390/ma15144944

Hsu P-N, Shie K-C, Tran D-P, Tsou N-T, Chen C. Failures of Cu-Cu Joints under Temperature Cycling Tests. Materials. 2022; 15(14):4944. https://doi.org/10.3390/ma15144944

Chicago/Turabian StyleHsu, Po-Ning, Kai-Cheng Shie, Dinh-Phuc Tran, Nien-Ti Tsou, and Chih Chen. 2022. "Failures of Cu-Cu Joints under Temperature Cycling Tests" Materials 15, no. 14: 4944. https://doi.org/10.3390/ma15144944

APA StyleHsu, P.-N., Shie, K.-C., Tran, D.-P., Tsou, N.-T., & Chen, C. (2022). Failures of Cu-Cu Joints under Temperature Cycling Tests. Materials, 15(14), 4944. https://doi.org/10.3390/ma15144944