A Unified PUF and Crypto Core Exploiting the Metastability in Latches

Abstract

1. Introduction

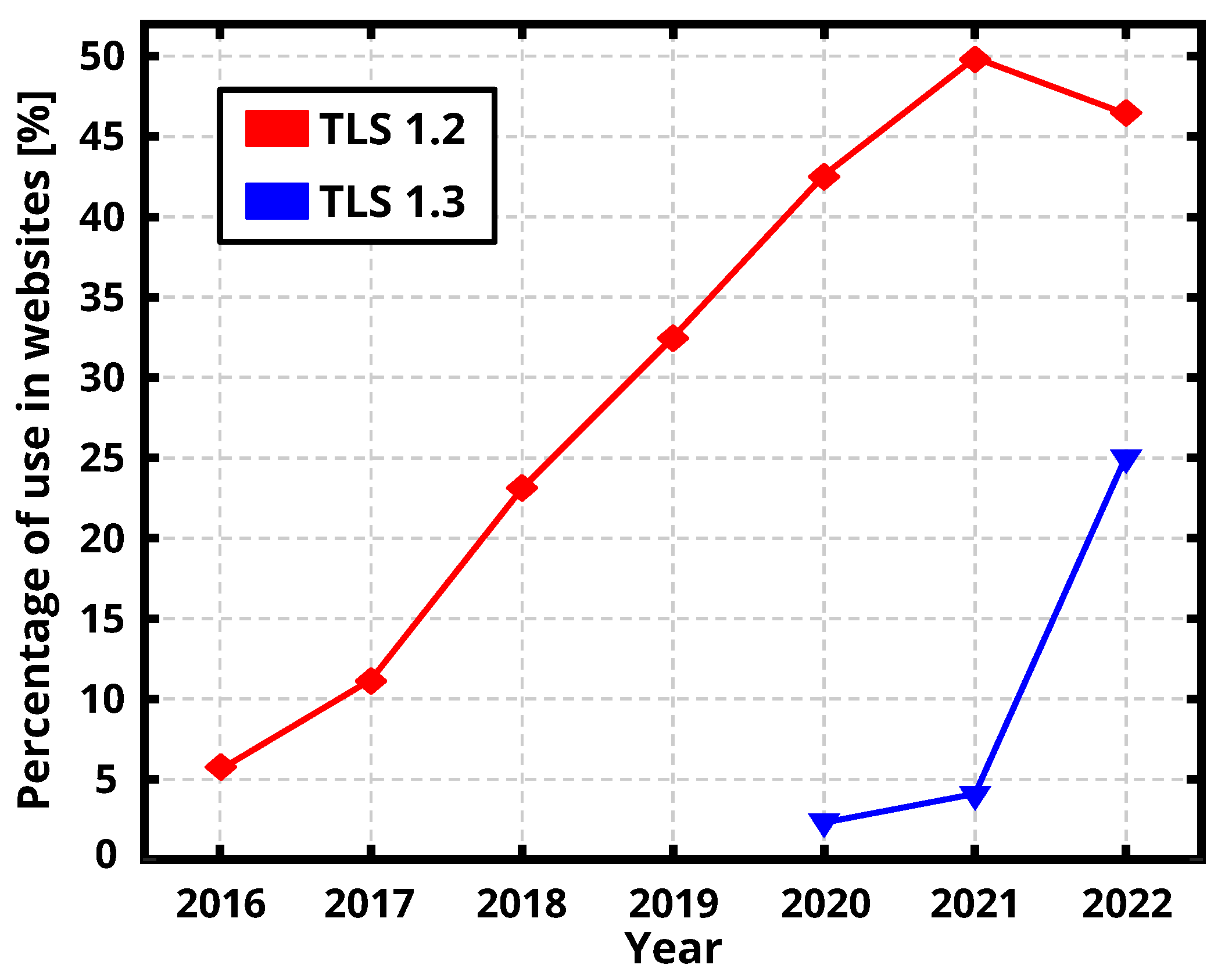

2. Transport Layer Security

3. Physical Unclonable Function

3.1. Physical Phenomena

3.2. Analytical Model

3.3. Implementation

4. ChaCha20

5. Results

6. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Kumar, V.B.Y.; Chattopadhyay, A.; Haj-Yahya, J.; Mendelson, A. ITUS: A Secure RISC-V System-on-Chip. In Proceedings of the 32nd IEEE International System-on-Chip Conference (SOCC), Singapore, 3–6 September 2019; pp. 418–423. [Google Scholar]

- Nasahl, P.; Schilling, R.; Werner, M.; Mangard, S. HECTOR-V: A Heterogeneous CPU Architecture for a Secure RISC-V Execution Environment. In Proceedings of the ACM Asia Conference on Computer and Communications Security (ASIA CCS), Virtual, 7–11 June 2021; pp. 187–199. [Google Scholar]

- Hoang, T.-T.; Duran, C.; Serrano, R.; Sarmiento, M.; Nguyen, K.-D.; Tsukamoto, A.; Suzaki, K.; Pham, C.-K. Trusted Execution Environment Hardware by Isolated Heterogeneous Architecture for Key Scheduling. IEEE Access 2022, 10, 46014–46027. [Google Scholar] [CrossRef]

- Taneja, S.; Rajanna, V.K.; Alioto, M. 36.1 Unified In-Memory Dynamic TRNG and Multi-Bit Static PUF Entropy Generation for Ubiquitous Hardware Security. In Proceedings of the IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 13–22 February 2021; Volume 64, pp. 498–500. [Google Scholar] [CrossRef]

- Taneja, S.; Rajanna, V.K.; Alioto, M. In-Memory Unified TRNG and Multi-Bit PUF for Ubiquitous Hardware Security. IEEE J. Solid-State Circuits 2022, 57, 153–166. [Google Scholar] [CrossRef]

- Nam, J.W.; Ahn, J.H.; Hong, J.P. Compact SRAM-Based PUF Chip Employing Body Voltage Control Technique. IEEE Access 2022, 10, 22311–22319. [Google Scholar] [CrossRef]

- Serrano, R.; Duran, C.; Sarmiento, M.; Pham, C.K. A Unified NVRAM and TRNG in Standard CMOS Technology. IEEE Access 2022, 10, 79213–79221. [Google Scholar] [CrossRef]

- Ray, B.; Milenković, A. True Random Number Generation Using Read Noise of Flash Memory Cells. IEEE Trans. Electron Devices 2018, 65, 963–969. [Google Scholar] [CrossRef]

- Ardila, J.; Santamaria, J.; Florez, K.; Roa, E. A Stable Physically Unclonable Function Based on a Standard CMOS NVR. In Proceedings of the IEEE International Symposium on Circuits and Systems (ISCAS), Sevilla, Spain, 10–21 October 2020; pp. 1–4. [Google Scholar] [CrossRef]

- Taneja, S.; Alioto, M. Fully Synthesizable Unified True Random Number Generator and Cryptographic Core. IEEE J. Solid-State Circuits 2021, 56, 3049–3061. [Google Scholar] [CrossRef]

- Amaki, T.; Hashimoto, M.; Onoye, T. An Oscillator-based True Random Number Generator with Jitter Amplifier. In Proceedings of the IEEE International Symposium on Circuits and Systems (ISCAS), Rio de Janeiro, Brazil, 15–18 May 2011; pp. 725–728. [Google Scholar] [CrossRef]

- Peetermans, A.; Rozic, V.; Verbauwhede, I. A Highly-Portable True Random Number Generator Based on Coherent Sampling. In Proceedings of the 29th International Conference on Field Programmable Logic and Applications (FPL), Barcelona, Spain, 9–13 September 2019; pp. 218–224. [Google Scholar] [CrossRef]

- Chen, T.; Ma, Y.; Lin, J.; Cao, Y.; Lv, N.; Jing, J. A Lightweight Full Entropy TRNG With On-Chip Entropy Assurance. Trans. Comput.-Aided Des. Integr. Circuits Syst. 2021, 40, 2431–2444. [Google Scholar] [CrossRef]

- Wieczorek, P.; Golofit, K. Metastability occurrence based physical unclonable functions for FPGAs. Electron. Lett. 2014, 50, 281–283. [Google Scholar] [CrossRef]

- Yang, K.; Fick, D.; Henry, M.B.; Lee, Y.; Blaauw, D.; Sylvester, D. 16.3 A 23 Mb/s 23 pJ/b fully synthesized true-random-number generator in 28 nm and 65 nm CMOS. In Proceedings of the IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC), San Francisco, CA, USA, 9–13 February 2014; pp. 280–281. [Google Scholar] [CrossRef]

- Yang, K.; Dong, Q.; Blaauw, D.; Sylvester, D. 14.2 A physically unclonable function with BER < 10−8 for robust chip authentication using oscillator collapse in 40 nm CMOS. In Proceedings of the IEEE International Solid-State Circuits Conference (ISSCC) Digest of Technical Papers, San Francisco, CA, USA, 22–26 February 2015; pp. 1–3. [Google Scholar] [CrossRef]

- Serrano, R.; Duran, C.; Sarmiento, M.; Hoang, T.T.; Tsukamoto, A.; Suzaki, K.; Pham, C.K. A Robust and Healthy Against PVT Variations TRNG Based on Frequency Collapse. IEEE Access 2022, 10, 41852–41862. [Google Scholar] [CrossRef]

- Park, J.; Kim, B.J.; Sim, J.Y. A PVT-Tolerant Oscillation-Collapse-Based True Random Number Generator with an Odd Number of Inverter Stages. IEEE Trans. Circuits Syst. Ii Express Briefs 2022, 69, 4058–4062. [Google Scholar] [CrossRef]

- Serrano, R.; Duran, C.; Hoang, T.T.; Sarmiento, M.; Nguyen, K.D.; Tsukamoto, A.; Suzaki, K.; Pham, C.K. A Fully Digital True Random Number Generator With Entropy Source Based in Frequency Collapse. IEEE Access 2021, 9, 105748–105755. [Google Scholar] [CrossRef]

- Mathew, S.K.; Srinivasan, S.; Anders, M.A.; Kaul, H.; Hsu, S.K.; Sheikh, F.; Agarwal, A.; Satpathy, S.; Krishnamurthy, R.K. 2.4 Gbps, 7 mW All-Digital PVT-Variation Tolerant True Random Number Generator for 45 nm CMOS High-Performance Microprocessors. IEEE J. Solid-State Circ. 2012, 47, 2807–2821. [Google Scholar] [CrossRef]

- Torii, N.; Yamamoto, D.; Matsumoto, T. Evaluation of Latch-Based Physical Random Number Generator Implementation on 40 Nm ASICs. In Proceedings of the International Workshop on Trustworthy Embedded Devices (TrustED), Hofburg Palace, Vienna, 28 October 2016; pp. 23–30. [Google Scholar]

- Tao, S.; Dubrova, E. TVL-TRNG: Sub-Microwatt True Random Number Generator Exploiting Metastability in Ternary Valued Latches. In Proceedings of the IEEE International Symposium on Multiple-Valued Logic (ISMVL), Novi Sad, Serbia, 22–24 May 2017; pp. 130–135. [Google Scholar]

- Najm, Z.; Jap, D.; Jungk, B.; Picek, S.; Bhasin, S. On Comparing Side-channel Properties of AES and ChaCha20 on Microcontrollers. In Proceedings of the IEEE Asia Pacific Conference on Circuits and Systems (APCCAS), Chengdu, China, 26–30 October 2018; pp. 552–555. [Google Scholar] [CrossRef]

- Saraiva, D.A.F.; Leithardt, V.R.Q.; de Paula, D.; Sales Mendes, A.; González, G.V.; Crocker, P. PRISEC: Comparison of Symmetric Key Algorithms for IoT Devices. Sensors 2019, 19, 4312. [Google Scholar] [CrossRef] [PubMed]

- Darbar, S.; Mervin, J.; Selvakumar, D. Side Channel Leakage Assessment Strategy On Attack Resistant AES Architectures. In Proceedings of the 24th International Symposium on VLSI Design and Test (VDAT), Bhubaneswar, India, 23–25 July 2020; pp. 1–6. [Google Scholar] [CrossRef]

- Aamir, M.; Sharma, S.; Grover, A. ChaCha20-in-Memory for Side-Channel Resistance in IoT Edge-Node Devices. IEEE Open J. Circuits Syst. 2021, 2, 833–842. [Google Scholar] [CrossRef]

- Chou, Y.-H.; Lu, S.-L.L. A High Performance, Low Energy, Compact Masked 128-Bit AES in 22 nm CMOS Technology. In Proceedings of the International Symposium on VLSI Design, Automation and Test (VLSI-DAT), Hsinchu, Taiwan, 22–25 April 2019; pp. 1–4. [Google Scholar] [CrossRef]

- Kumar, R.; Suresh, V.; Kar, M.; Satpathy, S.; Anders, M.A.; Kaul, H.; Agarwal, A.; Hsu, S.; Chen, G.K.; Krishnamurthy, R.K.; et al. A 4900-μm2 839-Mb/s Side-Channel Attack-Resistant AES-128 in 14-nm CMOS With Heterogeneous Sboxes, Linear Masked MixColumns, and Dual-Rail Key Addition. IEEE J. Solid-State Circuits 2020, 55, 945–955. [Google Scholar] [CrossRef]

- Hong, Y.-L.; Weng, Y.-K.; Huang, S.-H. Hardware Implementation for Fending off Side-Channel Attacks. In Proceedings of the IEEE International Conference on Consumer Electronics-Taiwan (ICCE-TW), Penghu, Taiwan, 15–17 September 2021; pp. 1–2. [Google Scholar] [CrossRef]

- Rescorla, E. The Transport Layer Security (TLS) Protocol Version 1.3; RFC 8446; RFC Editor: Marina del Rey, CA, USA, 2018. [Google Scholar] [CrossRef]

- Serrano, R.; Duran, C.; Hoang, T.-T.; Sarmiento, M.; Tsukamoto, A.; Suzaki, K.; Pham, C.-K. ChaCha20-Poly1305 Crypto Core Compatible with Transport Layer Security 1.3. In Proceedings of the International SoC Design Conference (ISOCC), Jeju Island, Korea, 6–9 October 2021; pp. 17–18. [Google Scholar]

- Serrano, R.; Duran, C.; Sarmiento, M.; Pham, C.K.; Hoang, T.T. ChaCha20-Poly1305 Authenticated Encryption with Additional Data for Transport Layer Security 1.3. Cryptography 2022, 6, 30. [Google Scholar] [CrossRef]

- Bernstein, D.J. The Salsa20 Family of Stream Ciphers. In New Stream Cipher Designs: The eSTREAM Finalists; Springer: Berlin/Heidelberg, Germany, 2008; pp. 84–97. [Google Scholar] [CrossRef]

- Rescorla, E.; Dierks, T. The Transport Layer Security (TLS) Protocol Version 1.2; RFC 5246; RFC Editor: Marina del Rey, CA, USA, 2008. [Google Scholar] [CrossRef]

- Nir, Y.; Langley, A. ChaCha20 and Poly1305 for IETF Protocols; RFC 8439; RFC Editor: Marina del Rey, CA, USA, 2018. [Google Scholar] [CrossRef]

- Deng, D.; Hou, S.; Wang, Z.; Guo, Y. Configurable Ring Oscillator PUF Using Hybrid Logic Gates. IEEE Access 2020, 8, 161427–161437. [Google Scholar] [CrossRef]

- Garcia-Bosque, M.; Aparicio, R.; Díez-Señorans, G.; Sánchez-Azqueta, C.; Celma, S. An analysis of the behaviour of a PUF based on ring oscillators depending on their locations. In Proceedings of the 17th Conference on Ph.D Research in Microelectronics and Electronics (PRIME), Villasimius, Italy, 12–15 June 2022; pp. 361–364. [Google Scholar] [CrossRef]

- Zayed, A.A.; Issa, H.H.; Shehata, K.A.; Ragai, H.F. Ultra-Low Power Oscillator Collapse Physical Unclonable Function Based on FinFET. IEEE Access 2021, 9, 27696–27707. [Google Scholar] [CrossRef]

- Park, J.; Kim, B.; Sim, J.Y. A BER-Suppressed PUF with an Amplification of Process Mismatch Effect in an Oscillator Collapse Topology. IEEE J. Solid-State Circuits 2022, 57, 2208–2219. [Google Scholar] [CrossRef]

- Waterman, A.; Lee, Y.; Patterson, D.A.; Asanović, K. The RISC-V Instruction Set Manual, Volume I: User-Level ISA, Version 2.1. In Technical Report UCB/EECS-2016-118; EECS Department, University of California: Berkeley, CA, USA, 2016. [Google Scholar]

- Pfau, J.; Reuter, M.; Harbaum, T.; Hofmann, K.; Becker, J. A Hardware Perspective on the ChaCha Ciphers: Scalable Chacha8/12/20 Implementations Ranging from 476 Slices to Bitrates of 175 Gbit/s. In Proceedings of the 32nd IEEE International System-on-Chip Conference (SOCC), Singapore, 3–6 September 2019; pp. 294–299. [Google Scholar] [CrossRef]

- Maiti, A.; Gunreddy, V.; Schaumont, P. A Systematic Method to Evaluate and Compare the Performance of Physical Unclonable Functions. In Embedded Systems Design with FPGAs; Athanas, P., Pnevmatikatos, D., Sklavos, N., Eds.; Springer: New York, NY, USA, 2013; pp. 245–267. [Google Scholar] [CrossRef]

- Gu, C.; Hanley, N.; O’neill, M. Improved Reliability of FPGA-Based PUF Identification Generator Design. ACM Trans. Reconfigurable Technol. Syst. 2017, 10, 1–23. [Google Scholar] [CrossRef]

- Jack, M.; Máire, O. Fast DRAM PUFs on Commodity Devices. IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst. 2020, 39, 3566–3576. [Google Scholar] [CrossRef]

- Garcia-Bosque, M.; Díez-Señorans, G.; Sánchez-Azqueta, C.; Celma, S. Proposal and Analysis of a Novel Class of PUFs Based on Galois Ring Oscillators. IEEE Access 2020, 8, 157830–157839. [Google Scholar] [CrossRef]

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Serrano, R.; Duran, C.; Sarmiento, M.; Dang, T.-K.; Hoang, T.-T.; Pham, C.-K. A Unified PUF and Crypto Core Exploiting the Metastability in Latches. Future Internet 2022, 14, 298. https://doi.org/10.3390/fi14100298

Serrano R, Duran C, Sarmiento M, Dang T-K, Hoang T-T, Pham C-K. A Unified PUF and Crypto Core Exploiting the Metastability in Latches. Future Internet. 2022; 14(10):298. https://doi.org/10.3390/fi14100298

Chicago/Turabian StyleSerrano, Ronaldo, Ckristian Duran, Marco Sarmiento, Tuan-Kiet Dang, Trong-Thuc Hoang, and Cong-Kha Pham. 2022. "A Unified PUF and Crypto Core Exploiting the Metastability in Latches" Future Internet 14, no. 10: 298. https://doi.org/10.3390/fi14100298

APA StyleSerrano, R., Duran, C., Sarmiento, M., Dang, T.-K., Hoang, T.-T., & Pham, C.-K. (2022). A Unified PUF and Crypto Core Exploiting the Metastability in Latches. Future Internet, 14(10), 298. https://doi.org/10.3390/fi14100298