A RF Redundant TSV Interconnection for High Resistance Si Interposer

Abstract

1. Introduction

2. Structural Design

3. Fabrication

4. RF Test and Analysis

5. S-Parameter Extraction

6. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Talebbeydokhti, P.; Dalmia, S.; Thai, T.; Sover, R.; Tal, S. Ultra large area SIPs and integrated mmW antenna array module for 5G mmWave outdoor applications. In Proceedings of the 2019 IEEE 69th Electronic Components and Technology Conference (ECTC), Las Vegas, NV, USA, 29–30 May 2019; pp. 294–299. [Google Scholar] [CrossRef]

- Hu, S.; Wang, L.; Xiong, Y.-Z.; Lim, T.G.; Zhang, B.; Shi, J.; Yuan, X. TSV Technology for millimeter-wave and terahertz design and applications. IEEE Trans. Compon. Packag. Manuf. Technol. 2010, 1, 260–267. [Google Scholar] [CrossRef]

- Yan, J.; Ma, S.; Jin, Y.; Wang, W.; Chen, J.; Luo, R.; Cai, H.; Li, J.; Xia, Y.; Hu, L.; et al. Fabrication and RF property evaluation of high-resistivity Si interposer for 2.5-D/3-D heterogeneous integration of RF devices. IEEE Trans. Compon. Packag. Manuf. Technol. 2018, 8, 2012–2020. [Google Scholar] [CrossRef]

- El Bouayadi, O.; Dussopt, L.; Lamy, Y.; Dehos, C.; Ferrandon, C.; Siligaris, A.; Soulier, B.; Simon, G.; Vincent, P. Silicon interposer: A versatile platform towards full-3D integration of wireless systems at millimeter-wave frequencies. In Proceedings of the 2019 IEEE 69th Electronic Components and Technology Conference (ECTC), Las Vegas, NV, USA, 29–30 May 2019; pp. 973–980. [Google Scholar]

- Lamy, Y.; Dussopt, L.; El Bouayadi, O.; Ferrandon, C.; Siligaris, A.; Dehos, C.; Vincent, P. A compact 3D silicon interposer package with integrated antenna for 60GHz wireless applications. In Proceedings of the 2013 IEEE International 3D Systems Integration Conference (3DIC), Francisco, CA, USA, 2–4 October 2013. [Google Scholar]

- Thadesar, P.A.; Bakir, M.S. Fabrication and characterization of polymer-enhanced TSVs, inductors, and antennas for mixed-signal silicon interposer platforms. IEEE Trans. Compon. Packag. Manuf. Technol. 2016, 6, 455–463. [Google Scholar] [CrossRef]

- Sekhar, V.N.; Toh, J.S.; Cheng, J.; Sharma, J.; Fernando, S.; Bangtao, C.; Fernando, S. Wafer level packaging of RF MEMS devices using TSV interposer technology. In Proceedings of the 2012 IEEE 14th Electronics Packaging Technology Conference (EPTC), Singapore, 5–7 December 2012. [Google Scholar]

- Tenailleau, J.-R.; Brunet, A.; Borel, S.; Voiron, F.; Bunel, C. TSV development, characterization and modeling for 2.5-D interposer applications. In Proceedings of the 2013 IEEE 63rd Electronic Components and Technology Conference, Las Vegas, NV, USA, 28–31 May 2013. [Google Scholar]

- Xu, Z.; Lu, J.Q. Three-dimensional coaxial through-silicon-via (TSV) design. IEEE Electron Device Lett. 2012, 10, 1441–1443. [Google Scholar] [CrossRef]

- Yu, P.; Lin, H.; He, Z.; Song, C.; Cai, J.; Wang, Q.; Wang, Z. Coaxial through-silicon-vias using low-κ SiO2 insulator. In Proceedings of the 2020 IEEE 70th Electronic Components and Technology Conference (ECTC), Orlando, FL, USA, 3–30 June 2020. [Google Scholar]

- Hwang, G.; Kalaiselvan, R.; Sam, M.I.E.; Hsiang-Yao, H. Study on through Silicon Via (TSV) filling failures on various electroplating conditions. In Proceedings of the 2019 IEEE 21st Electronics Packaging Technology Conference (EPTC), Singapore, 4–6 December 2019. [Google Scholar]

- Hollman, R.; Dimov, O.; Malik, S.; Hichri, H.; Arendt, M. Ultra fine RDL structure fabrication using alternative patterning and bottom-up plating processes. In Proceedings of the 2018 IEEE 68th Electronic Components and Technology Conference (ECTC), San Diego, CA, USA, 29 May–1 June 2018. [Google Scholar]

- Murugesan, M.; Fukushima, T.; Mori, K.; Nakamura, A.; Lee, Y.; Motoyoshi, M.; Bea, J.; Watariguchi, S.; Koyanagi, M. Fully-filled, highly-reliable fine-pitch interposers with TSV aspect ratio >10 for future 3D-LSI/IC packaging. In Proceedings of the 2019 IEEE 69th Electronic Components and Technology Conference (ECTC), Las Vegas, NV, USA, 25 May–2 June 2019. [Google Scholar]

- Bleiker, S.J.; Fischer, A.C.; Shah, U.; Somjit, N.; Haraldsson, T.; Roxhed, N.; Oberhammer, J.; Stemme, G.; Niklaus, F. High-aspect-ratio through silicon vias for high-frequency application fabricated by magnetic assembly of gold-coatednickel wires. IEEE Trans. Compon. Packag. Manuf. Technol. 2015, 5, 21–27. [Google Scholar] [CrossRef]

- Liu, X.; Chen, Q.; Dixit, P.; Chatterjee, R.; Tummala, R.R.; Sitaraman, S.K. Failure mechanisms and optimum design for electroplated copper Through-Silicon Vias (TSV). In Proceedings of the 2009 59th Electronic Components and Technology Conference, San Diego, CA, USA, 26–29 May 2009. [Google Scholar]

- Shen, J.; Chen, P.; Su, L.; Shi, T.; Tang, Z.; Liao, G. X-ray inspection of TSV defects with self-organizing map network and Otsu algorithm. Microelectron. Reliab. 2016, 67, 129–134. [Google Scholar] [CrossRef]

- Kang, U.; Chung, H.J.; Heo, S.; Park, D.H.; Lee, H.; Kim, J.H.; Ahn, S.H.; Cha, S.H.; Ahn, J.; Kwon, D.; et al. 8Gb 3D DDR3 DRAM using through-silicon-via technology. IEEE J. Solid State Circuits 2009, 45, 130–131. [Google Scholar]

- Hsieh, A.-C.; Hwang, T. TSV Redundancy: Architecture and design issues in 3-D IC. IEEE Trans. Very Large Scale Integr. Syst. 2011, 20, 711–722. [Google Scholar] [CrossRef]

- Jiang, L.; Xu, Q.; Eklow, B. On effective TSV repair for 3D-stacked ICs. In Proceedings of the Design, Automation and Test in Europe Conference and Exhibition (DATE), Dresden, Germany, 12–16 March 2012. [Google Scholar]

- Ma, S.; Chai, Y.; Yan, J.; Cai, H.; Hu, L.; He, S.; Wang, W.; Chen, J.; Jin, Y. A 2.5D integrated L band receiver based on high resistivity Si interposer. In Proceedings of the 2018 IEEE International Conference on Integrated Circuits, Technologies and Applications (ICTA), Beijing, China, 21–23 November 2018. [Google Scholar]

- Rahimi, A.; Somarajan, P.; Yu, Q. Modeling and characterization of through-silicon-vias (TSVs) in radio frequency regime in an active interposer technology. In Proceedings of the 2020 IEEE 70th Electronic Components and Technology Conference (ECTC), Lake Buena Vista, FL, USA, 26–29 May 2020. [Google Scholar]

- Lu, K.-C.; Horng, T.-S. Wideband and scalable equivalent-circuit model for differential through silicon vias with measurement verification. In Proceedings of the 2013 IEEE 63rd Electronic Components and Technology Conference, Las Vegas, NV, USA, 28–31 May 2013. [Google Scholar]

- Jung, D.H.; Kim, Y.; Kim, J.J.; Kim, H.; Choi, S.; Song, Y.-H.; Bae, H.-C.; Choi, K.-S.; Piersanti, S.; De Paulis, F.; et al. Through silicon via (TSV) defect modeling, measurement, and analysis. IEEE Trans. Compon. Packag. Manuf. Technol. 2016, 7, 138–152. [Google Scholar] [CrossRef]

- Leferink, F.B.J. Inductance calculations; methods and equations. In Proceedings of the International Symposium on Electromagnetic Compatibility, Atlanta, GA, USA, 14–18 August 1995; IEEE ISEMC. 1995; pp. 16–22. [Google Scholar]

- Kim, J.; Pak, J.S.; Cho, J.; Song, E.; Cho, J.; Kim, H.; Song, T.; Lee, J.; Lee, H.; Park, K.; et al. High-frequency scalable electrical model and analysis of a through silicon Via (TSV). IEEE Trans. Compon. Packag. Manuf. Technol. 2011, 1, 181–195. [Google Scholar]

- Hassan, M.D.; Farque, M.R.I. Left-handed metamaterial using Z-shaped SRR for multiband application by azimuthal angular rotationsm. Mater. Res. Express. 2017, 4, 045801. [Google Scholar] [CrossRef]

- Hassan, M.D.; Faruque, M.R.I.; Islam, S.S.; Islam, M.T. New compact double-negative miniaturized metamaterial for wideband operation. Materials 2016, 9, 830. [Google Scholar] [CrossRef] [PubMed]

- Hasan, M.; Faruque, M.R.I.; Islam, M.T. Compact left-handed meta-atom for S-, C- and Ku-band application. Appl. Sci. 2017, 7, 1071. [Google Scholar] [CrossRef]

- Ye, R.; Xu, J. SOLT calibration method and its application to radio-frequency measurement. Chin. J. Electron Devices 2006, 29, 179. [Google Scholar]

- Chen, C.D.; Tzuang, C.K.; Peng, S.T. Full-wave analysis of a lossy rectangular waveguide containing rough inner surfaces. IEEE Microw. Guided Wave Lett. 1992, 2, 180–181. [Google Scholar] [CrossRef]

- Palasantzas, G. Influence of self-affine and mound roughness on the surface impedance and skin depth of conductive materials. J. Phys. Chem. Solids 2004, 65, 1271–1275. [Google Scholar] [CrossRef]

- Scogna, A.C.; Schauer, M. Performance analysis of strip line surface roughness models. In Proceedings of the International Symposium on Electromagnetic Compatibility, Detroit, MI, USA, 18–22 August 2008. [Google Scholar]

- Noyan, K.; Aksun, M.I. Modern Microwave Circuits; Artech House: Boston, MA, USA, 2008; pp. 58–68. [Google Scholar]

- Khan, W.T.; Tong, J.; Sitaraman, S.; Sundaram, V.; Tummala, R.; Papapolymerou, J. Characterization of electrical properties of glass and transmission lines on thin glass up to 50 GHz. In Proceedings of the 2015 IEEE 65th Electronic Components and Technology Conference (ECTC), San Diego, CA, USA, 26–29 May 2015. [Google Scholar]

- Chung, D.J.; Bhattacharya, S.K.; Papapolymerou, J. Low loss multilayer transitions using via technology on LCP from DC to 40 GHz. In Proceedings of the 2009 59th Electronic Components and Technology Conference, San Diego, CA, USA, 26–29 May 2009. [Google Scholar]

- Chen, B.; Sekhar, V.N.; Jin, C.; Lim, Y.Y.; Toh, J.S.; Fernando, S.; Sharma, J. Low-loss broadband package platform with surface passivation and TSV for wafer-level packaging of RF-MEMS devices. IEEE Trans. Compon. Packag. Manuf. Technol. 2013, 3, 1443–1452. [Google Scholar] [CrossRef]

- Ebefors, T.; Fredlund, J.; Perttu, D.; Van Dijk, R.; Cifola, L.; Kaunisto, M.; Rantakari, P.; Vaha-Heikkila, T. The development and evaluation of RF TSV for 3D IPD applications. In Proceedings of the 2013 IEEE International 3D Systems Integration Conference (3DIC), Francisco, CA, USA, 2–4 October 2013. [Google Scholar]

- Lorival, J.E.; Calmon, F.; Sun, F.; Frantz, F.; Plossu, C.; Le Berre, M.; O’Connor, I.; Valorge, O.; Charbonnier, J.; Henry, D.; et al. An efficient and simple compact modeking approach for 3-D interconnects with IC’s stack global electrical context consideration. Microelectron. J. 2015, 46, 153–165. [Google Scholar] [CrossRef]

- Kim, N.; Wu, D.; Kim, D.; Rahman, A.; Wu, P. Interposer design optimization for high frequency signal transmission in passive and active interposer using through silicon via (TSV). In Proceedings of the 2011 IEEE 61st Electronic Components and Technology Conference (ECTC), Lake Buena Vista, FL, USA, 31 May–3 June 2011. [Google Scholar]

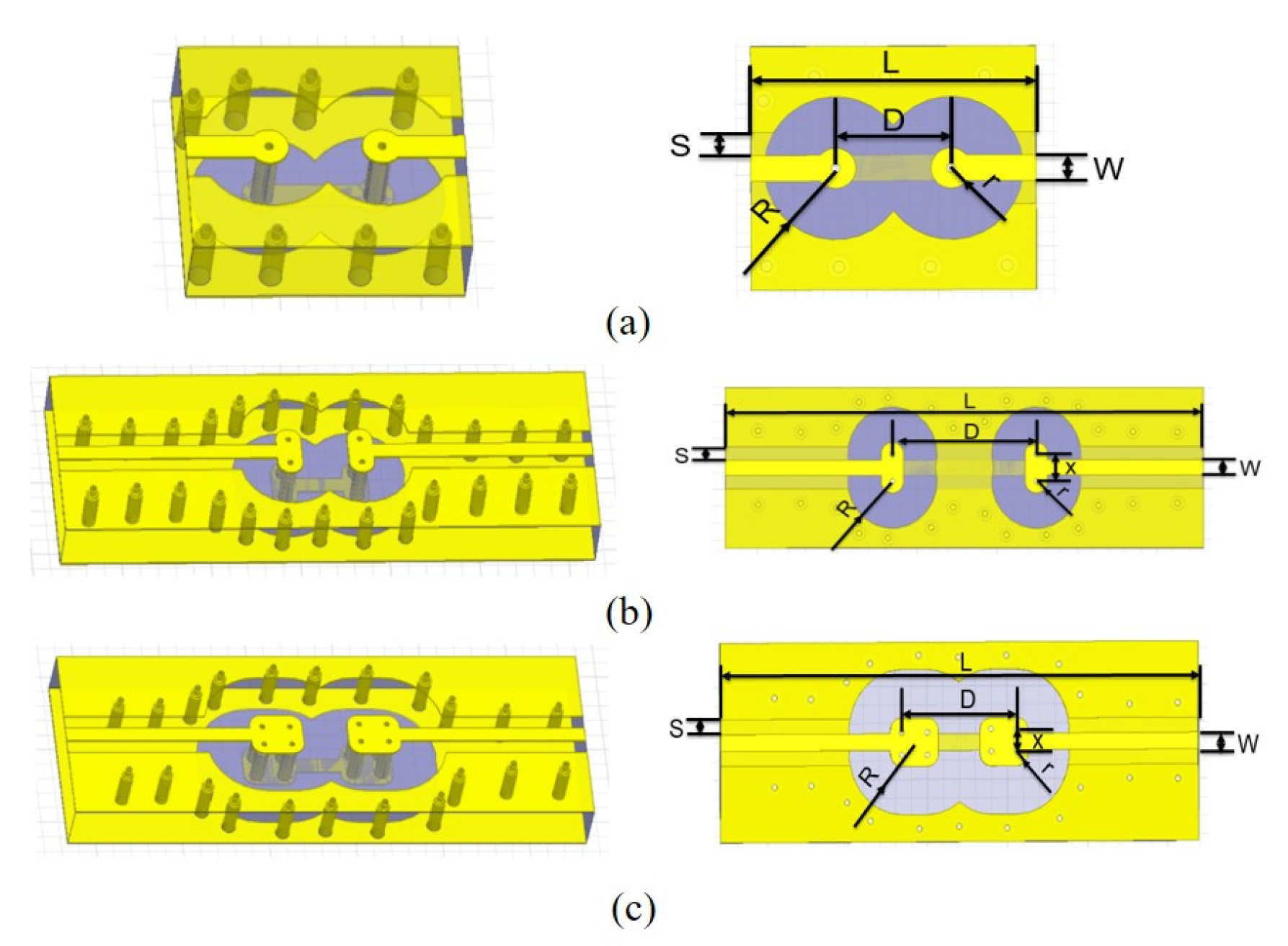

| Table 1 | L | S | W | D | R | r | x |

|---|---|---|---|---|---|---|---|

| Single TSV | 1000 | 70 | 100 | 400 | 250 | 75 | - |

| Dual redundant TSV | 3000 | 70 | 100 | 400 | 250 | 75 | 160 |

| Quad redundant TSV | 3000 | 70 | 100 | 640 | 250 | 75 | 120 |

| Symbol | Parameter |

|---|---|

| RRDL/RTSV | Resistance of RDL/TSV |

| LRDL | Self-Inductance of RDL |

| LTSVclosed | Inductance of RDL under the influence of proximity effect |

| CRDLinSub/Csub | Capacitance between RDL/TSV and substrate |

| GRDLinSub/Gsub | Conductance between RDLs/TSVs in silicon substrate |

| PF | Proximity effect correction factor |

| dCu | Skin depth |

| Points | Resistivity/μΩ·cm |

|---|---|

| 1 | 4.56 |

| 2 | 12.44 |

| 3 | 13.95 |

| 4 | 12.43 |

| 5 | 18.24 |

| 6 | 12.36 |

| Average value | 12.79 |

| Ref. | Substrate Material | Type of Vias | Transmission Loss of One Transition (dB) | Via Size (μm) | Via Length (μm) | |

|---|---|---|---|---|---|---|

| 10 GHz | 40 GHz | |||||

| [34] | Glass | Single TGV | 0.03 | 0.22 | Φ55 | 366 |

| [35] | LCP | Single Via | 0.071 | 0.12 | Φ55 | 51 |

| [36] | Si(HR) | Single TSV | 0.05 | — | Φ100 | 300 |

| [37] | Si(HR) | Single TSV | 0.04 | — | Φ8 & Φ90 | 25 & 280 |

| [38] | Si(HR) | Single TSV | 1.6 | — | Φ40 | 120 |

| [39] | Si(HR) | Single TSV | 0.37 | — | Φ10 | 100 |

| This Work | Si(HR) | Single TSV | 0.11 | 0.22 | Φ40 & Φ80 | 50 & 250 |

| Dual redundant TSV | 0.14 | 0.19 | ||||

| Quad redundant TSV | 0.2 | 0.46 | ||||

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Wang, M.; Ma, S.; Jin, Y.; Wang, W.; Chen, J.; Hu, L.; He, S. A RF Redundant TSV Interconnection for High Resistance Si Interposer. Micromachines 2021, 12, 169. https://doi.org/10.3390/mi12020169

Wang M, Ma S, Jin Y, Wang W, Chen J, Hu L, He S. A RF Redundant TSV Interconnection for High Resistance Si Interposer. Micromachines. 2021; 12(2):169. https://doi.org/10.3390/mi12020169

Chicago/Turabian StyleWang, Mengcheng, Shenglin Ma, Yufeng Jin, Wei Wang, Jing Chen, Liulin Hu, and Shuwei He. 2021. "A RF Redundant TSV Interconnection for High Resistance Si Interposer" Micromachines 12, no. 2: 169. https://doi.org/10.3390/mi12020169

APA StyleWang, M., Ma, S., Jin, Y., Wang, W., Chen, J., Hu, L., & He, S. (2021). A RF Redundant TSV Interconnection for High Resistance Si Interposer. Micromachines, 12(2), 169. https://doi.org/10.3390/mi12020169