Vertical Gate-All-Around Device Architecture to Improve the Device Performance for Sub-5-nm Technology

Abstract

:1. Introduction

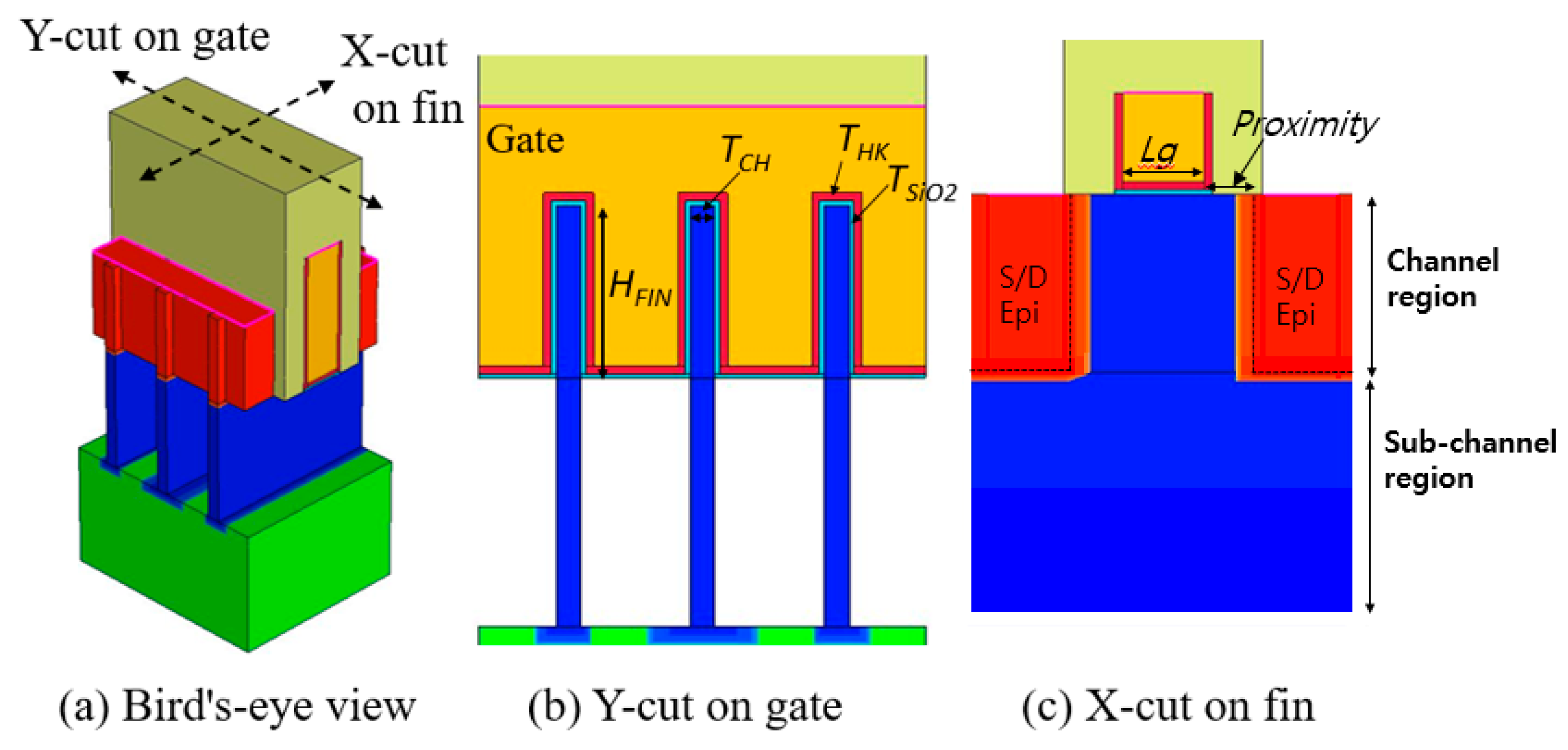

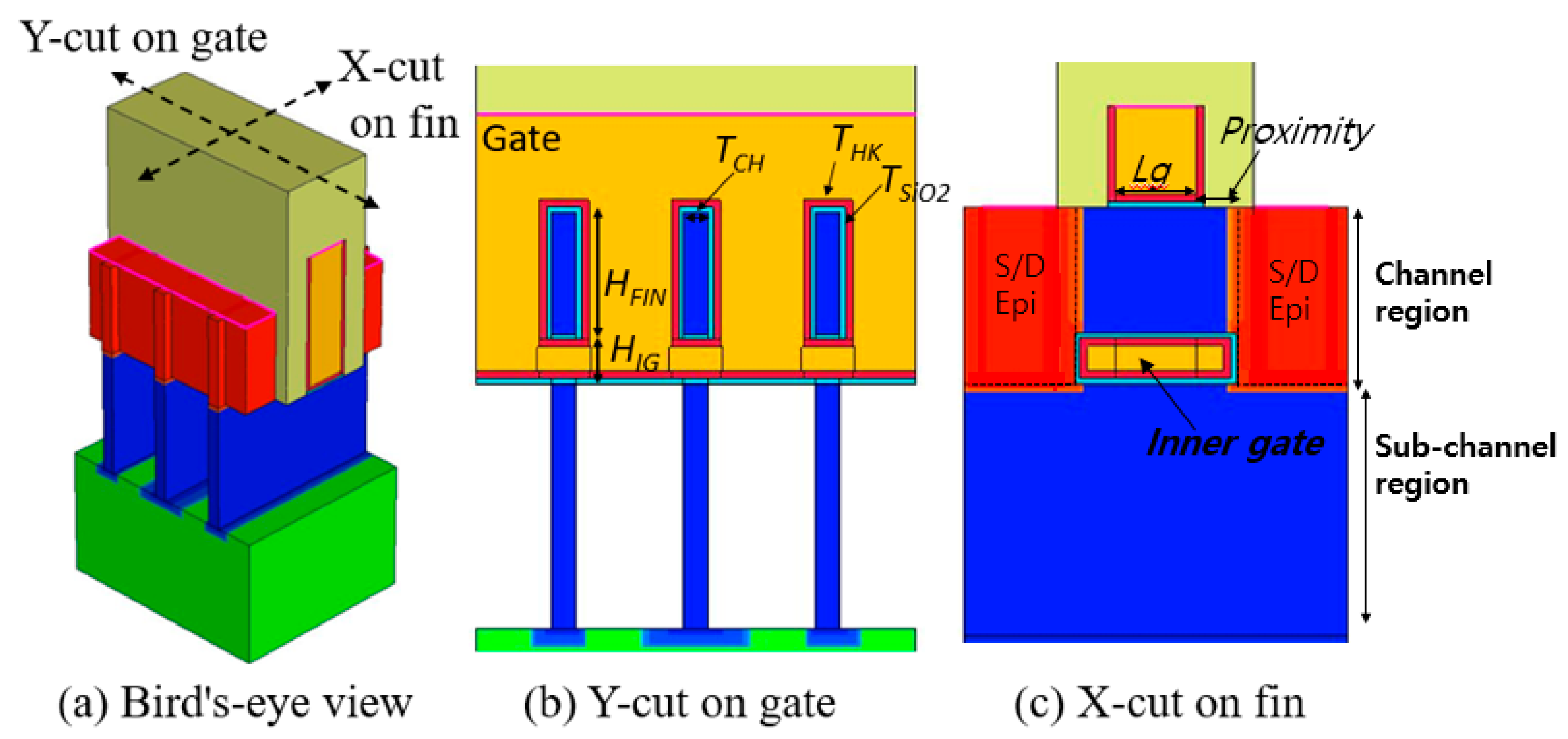

2. Device Structures and Calibration for Simulation

3. Results and Discussion

3.1. Comparison of Electrical Characteristics: FinFET vs. GAA-FinFET

3.2. Comparison of Electrical Characteristics: NSFET vs. GAA-FinFET

3.3. Impact of Doping Concentration in the Sub-Channel Region on Electrical Characteristics

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Auth, C.; Aliyarukunju, A.; Asoro, M.; Bergstrom, D.; Bhagwat, V.; Birdsall, J.; Bisnik, N.; Buehler, M.; Chikarmane, V.; Ding, G.; et al. A 10 nm high performance and low-power CMOS technology featuring 3rd generation FinFET transistors, Self-Aligned Quad Patterning, contact over active gate and cobalt local interconnects. In Proceedings of the 2017 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2–6 December 2017; pp. 29.1.1–29.1.4. [Google Scholar]

- Auth, C.; Allen, C.; Blattner, A.; Bergstrom, D.; Brazier, M.; Bost, M.; Buehler, M.; Chikarmane, V.; Ghani, T.; Glassman, T.; et al. A 22 nm high performance and low-power CMOS technology featuring fully-depleted tri-gate transistors, self-aligned contacts and high density MIM capacitors. In Proceedings of the 2012 Symposium on VLSI Technology, Honolulu, HI, USA, 12–14 June 2012; pp. 131–132. [Google Scholar]

- Bae, G.; Bae, D.-I.; Kang, M.; Hwang, S.M.; Kim, S.S.; Seo, B.; Kwon, T.Y.; Lee, T.J.; Moon, C.; Choi, Y.M.; et al. 3nm GAA Technology featuring Multi-Bridge-Channel FET for Low Power and High Performance Applications. In Proceedings of the 2018 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 1–5 December 2018; pp. 28.7.1–28.7.4. [Google Scholar]

- Feng, P.; Song, S.-C.; Nallapati, G.; Zhu, J.; Bao, J.; Moroz, V.; Choi, M.; Lin, X.-W.; Lu, Q.; Colombeau, B.; et al. Comparative Analysis of Semiconductor Device Architectures for 5-nm Node and Beyond. IEEE Electron. Device Lett. 2017, 38, 1657–1660. [Google Scholar] [CrossRef]

- Jeong, W.; Maeda, S.; Lee, H.; Lee, K.; Lee, T.; Park, D.; Kim, B.; Do, J.; Fukai, T.; Kwon, D.; et al. True 7nm platform technology featuring smallest FinFET and smallest SRAM cell by EUV, special constructs and 3rd generation single diffusion break. In Proceedings of the 2018 Symposium on VLSI Technology, Honolulu, HI, USA, 18–22 June 2018; pp. 59–60. [Google Scholar]

- Kim, S.-D.; Guillorn, M.; Lauer, I.; Oldiges, P.; Hook, T.; Na, M.-H. Performance trade-offs in FinFET and gate-all-around device architectures for 7 nm-node and beyond. In Proceedings of the IEEE SOI-3D-Subthreshold Microelectronics Technology Unified Conference (S3S), Rohnert Park, CA, USA, 5–8 October 2015; pp. 1–3. [Google Scholar]

- Loubet, N.; Hook, T.; Montanini, P.; Yeung, C.-W.; Kanakasabapathy, S.; Guillom, M.; Yamashita, T.; Zhang, J.; Miao, X.; Wang, J.; et al. Stacked nanosheet gate-all-around transistor to enable scaling beyond FinFET. In Proceedings of the 2017 IEEE Symposium on VLSI Technology, Kyoto, Japan, 5–8 June 2017; pp. T230–T231. [Google Scholar]

- Mertens, H.; Ritzenthaler, R.; Hikavyy, A.; Kim, M.S.; Tao, Z.; Wostyn, K.; Chew, S.A.; Keersgieter, A.D.; Mannaert, G.; Rosseel, E.; et al. Gate-all-around MOSFETs based on vertically stacked horizontal Si nanowires in a replacement metal gate process on bulk Si substrates. In Proceedings of the 2016 IEEE Symposium on VLSI Technology, Honolulu, HI, USA, 14–16 June 2016; pp. 1–2. [Google Scholar]

- Natarajan, S.; Agostinelli, M.; Akbar, S.; Bost, M.; Bowonder, A.; Chikarmane, V.; Chouksey, S.; Dasgupta, A.; Fischer, K.; Fu, Q.; et al. A 14 nm logic technology featuring 2nd-generation FinFET, air-gapped interconnects, self-aligned double patterning and a 0.0588 µm2 SRAM cell size. In Proceedings of the 2014 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 15–17 December 2014; pp. 71–73. [Google Scholar]

- Seo, K.-I.; Haran, B.; Gupta, D.; Guo, D.; Standaert, T.; Xie, R.; Shang, H.; Alptekin, E.; Bae, D.-I.; Bae, G. A 10nm platform technology for low power and high performance application featuring FINFET devices with multi workfunction gate stack on bulk and SOI. In Proceedings of the 2014 Symposium on VLSI Technology (VLSI-Technology): Digest of Technical Papers, Honolulu, HI, USA, 9–12 June 2014; pp. 1–2. [Google Scholar]

- Sicard, E.; Trojman, L. Introducing 5-nm FinFET Technology in Microwind. hal03254444f. 2021. Available online: https://hal.archives-ouvertes.fr/hal-03254444/document (accessed on 4 August 2022).

- Lee, S.Y.; Kim, S.M.; Yoon, E.J.; Oh, C.W.; Chung, I.; Park, D.; Kim, K. A novel multi-bridge-channel MOSFET (MBCFET): Fabrication technologies and characteristics. IEEE Trans. Nanotechnol. 2004, 2, 253–257. [Google Scholar]

- Yeap, G.; Lin, S.; Chen, Y.; Shang, H.; Wang, P.; Lin, H.; Peng, Y.; Sheu, J.; Wang, M.; Chen, X.; et al. 5nm cmos production technology platform featuring full-fledged euv, and high mobility channel finfets with densest 0.021 µm2 sram cells for mobile soc and high performance computing applications. In Proceedings of the 2019 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 7–11 December 2019; pp. 36.7.1–36.7.4. [Google Scholar]

- Das, U.K.; Bhattacharyya, T.K. Opportunities in device scaling for 3-nm node and beyond: FinFET versus GAA-FET versus UFET. IEEE Trans. Electron. Devices 2020, 67, 2633–2638. [Google Scholar] [CrossRef]

- Jeong, J.; Yoon, J.-S.; Lee, S.; Baek, R.-H. Comprehensive analysis of source and drain recess depth variations on silicon nanosheet FETs for sub 5-nm node SoC application. IEEE Access 2020, 8, 35873–35881. [Google Scholar] [CrossRef]

- Joung, S.; Kim, S. Leakage Performance Improvement in Multi-Bridge-Channel Field Effect Transistor (MBCFET) by Adding Core Insulator Layer. In Proceedings of the 2019 International Conference on Simulation of Semiconductor Processes and Devices (SISPAD), Udine, Italy, 4–6 September 2019; pp. 1–4. [Google Scholar]

- Wang, M.; Sun, Y.; Li, X.; Shi, Y.; Hu, S.; Shang, E.; Chen, S. Design technology co-optimization for 3 nm gate-all-around nanosheet FETs. In Proceedings of the 2020 IEEE 15th International Conference on Solid-State & Integrated Circuit Technology (ICSICT), Kunming, China, 3–6 November 2020; pp. 1–3. [Google Scholar]

- Choi, Y.; Lee, K.; Kim, K.Y.; Kim, S.; Lee, J.; Lee, R.; Kim, H.-M.; Song, Y.S.; Kim, S.; Lee, J.-H. Simulation of the effect of parasitic channel height on characteristics of stacked gate-all-around nanosheet FET. Solid-State Electron. 2020, 164, 107686. [Google Scholar] [CrossRef]

- Kim, S.; Kim, M.; Ryu, D.; Lee, K.; Kim, S.; Lee, J.; Lee, R.; Kim, S.; Lee, J.-H.; Park, B.-G. Investigation of electrical characteristic behavior induced by channel-release process in stacked nanosheet gate-all-around MOSFETs. IEEE Trans. Electron Devices 2020, 67, 2648–2652. [Google Scholar] [CrossRef]

- Bao, R.; Watanabe, K.; Zhang, J.; Guo, J.; Zhou, H.; Gaul, A.; Sankarapandian, M.; Li, J.; Hubbard, A.; Vega, R. Multiple-Vt solutions in nanosheet technology for high performance and low power applications. In Proceedings of the 2019 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 7–11 December 2019; pp. 11.2.1–11.2.4. [Google Scholar]

- Mertens, H.; Ritzenthaler, R.; Chasin, A.; Schram, T.; Kunnen, E.; Hikavyy, A.; Ragnarsson, L.-Å.; Dekkers, H.; Hopf, T.; Wostyn, K. Vertically stacked gate-all-around Si nanowire CMOS transistors with dual work function metal gates. In Proceedings of the 2016 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 3–7 December 2016; pp. 19.17.11–19.17.14. [Google Scholar]

- Yoon, J.-S.; Jeong, J.; Lee, S.; Baek, R.-H. Bottom oxide bulk FinFETs without punch-through-stopper for extending toward 5-nm node. IEEE Access 2019, 7, 75762–75767. [Google Scholar] [CrossRef]

- Kao, M.-Y.; Agarwal, H.; Liao, Y.-H.; Cheema, S.; Dasgupta, A.; Kushwaha, P.; Tan, A.; Salahuddin, S.; Hu, C. Negative capacitance enables FinFET scaling beyond 3nm node. arXiv 2020, arXiv:2007.14448. [Google Scholar]

- Sharan, N.; Shaik, K.A.; Jang, D.; Schuddinck, P.; Yakimets, D.; Bardon, M.G.; Mitard, J.; Arimura, H.; Bufler, F.M.; Eneman, G. Ge devices: A potential candidate for sub-5-nm nodes? IEEE Trans. Electron Devices 2019, 66, 4997–5002. [Google Scholar] [CrossRef]

- Sreenivasulu, V.B.; Narendar, V. Junctionless SOI FinFET with advanced spacer techniques for sub-3 nm technology nodes. AEU-Int. J. Electron. Commun. 2022, 145, 154069. [Google Scholar] [CrossRef]

- Taur, Y.; Ning, T.H. Fundamentals of Modern VLSI Devices; Cambridge University Press: Cambridge, UK, 2009. [Google Scholar]

| Symbol | Parameters | FinFET | GAA-FinFET | NSFET |

|---|---|---|---|---|

| Lg | Gate length | 16 nm | 16 nm | 16 nm |

| HFIN (WCH) | Fin height (Channel width) | 35 nm | 25 nm | 35 nm |

| FP | Fin pitch | 27 nm | 27 nm | N/A |

| TCH | Channel thickness | 5 nm | 5 nm | 5 nm |

| HIG | Inner gate height | N/A | 10 nm | 10 nm |

| - | S/D epi doping concentration | 1020 cm−3 (Arsenic) | 1020 cm−3 (Arsenic) | 1020 cm−3 (Arsenic) |

| - | Channel region doping concentration | 5 × 1017 cm−3 (Boron) | 5 × 1017 cm−3 (Boron) | 5 × 1017 cm−3 (Boron) |

| THK | Gate high-k thickness | 1.5 nm | 1.5 nm | 1.5 nm |

| TSiO2 | Gate oxide layer thickness | 1 nm | 1 nm | 1 nm |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Noh, C.; Han, C.; Won, S.M.; Shin, C. Vertical Gate-All-Around Device Architecture to Improve the Device Performance for Sub-5-nm Technology. Micromachines 2022, 13, 1551. https://doi.org/10.3390/mi13091551

Noh C, Han C, Won SM, Shin C. Vertical Gate-All-Around Device Architecture to Improve the Device Performance for Sub-5-nm Technology. Micromachines. 2022; 13(9):1551. https://doi.org/10.3390/mi13091551

Chicago/Turabian StyleNoh, Changwoo, Changwoo Han, Sang Min Won, and Changhwan Shin. 2022. "Vertical Gate-All-Around Device Architecture to Improve the Device Performance for Sub-5-nm Technology" Micromachines 13, no. 9: 1551. https://doi.org/10.3390/mi13091551

APA StyleNoh, C., Han, C., Won, S. M., & Shin, C. (2022). Vertical Gate-All-Around Device Architecture to Improve the Device Performance for Sub-5-nm Technology. Micromachines, 13(9), 1551. https://doi.org/10.3390/mi13091551