Design of Spectrum Processing Chiplet Based on FFT Algorithm

Abstract

:1. Introduction

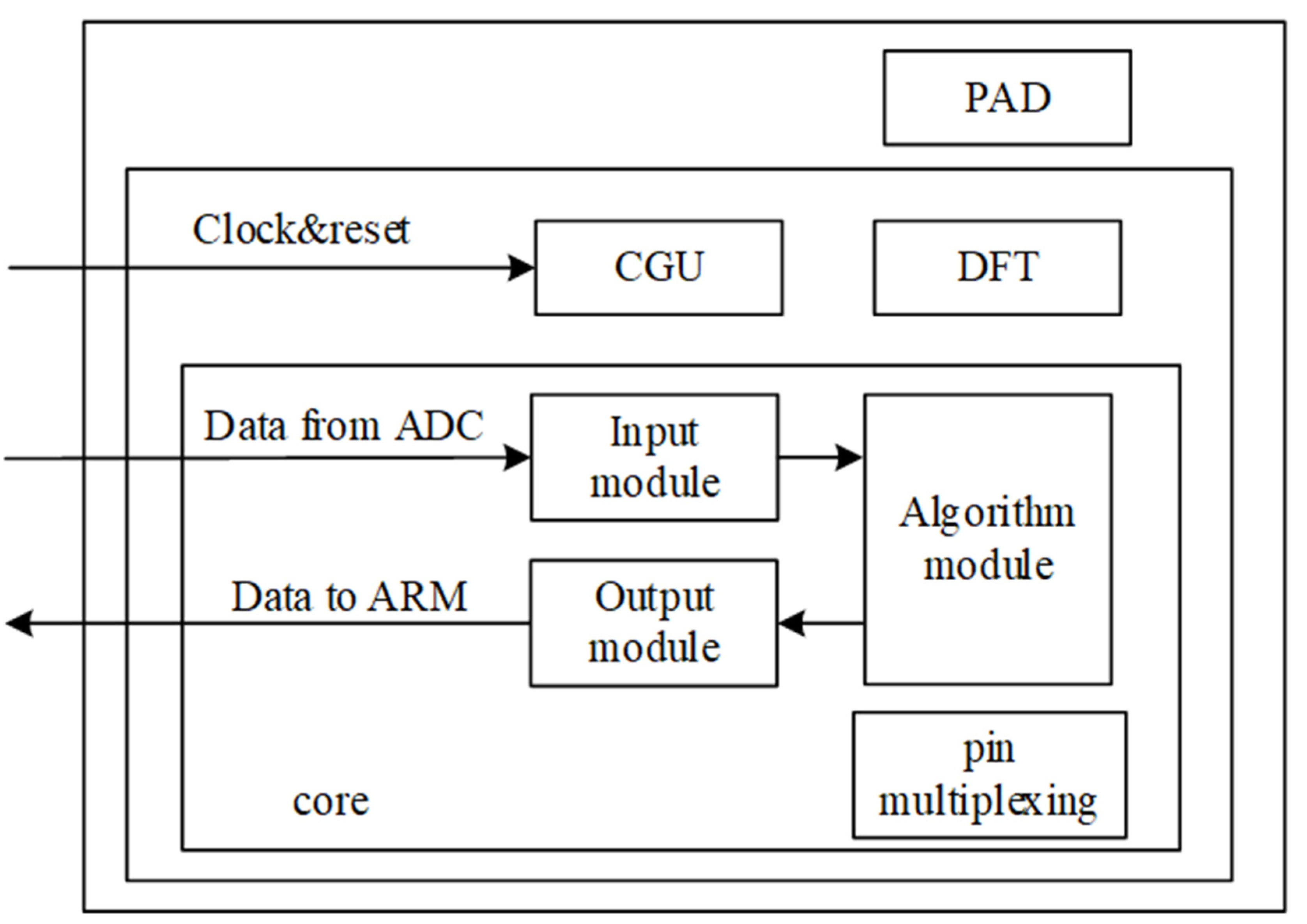

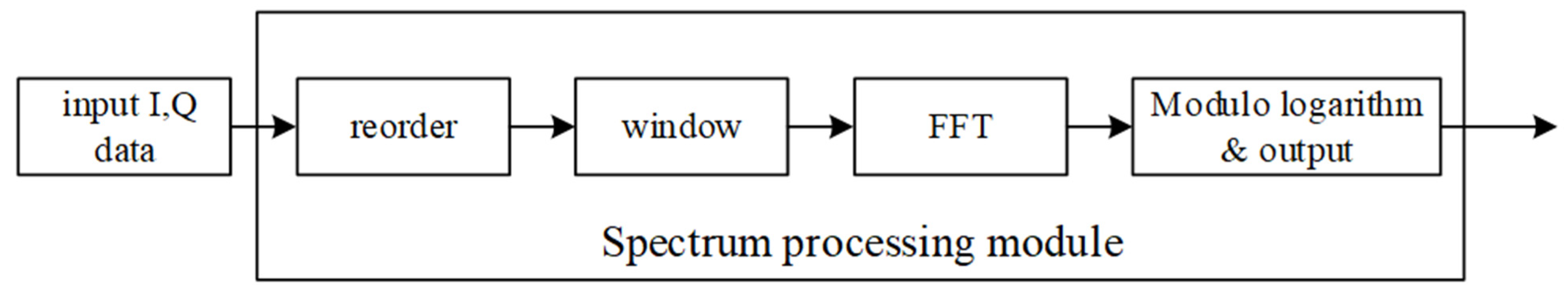

2. System Architecture

2.1. FFT Introduction and Implementation

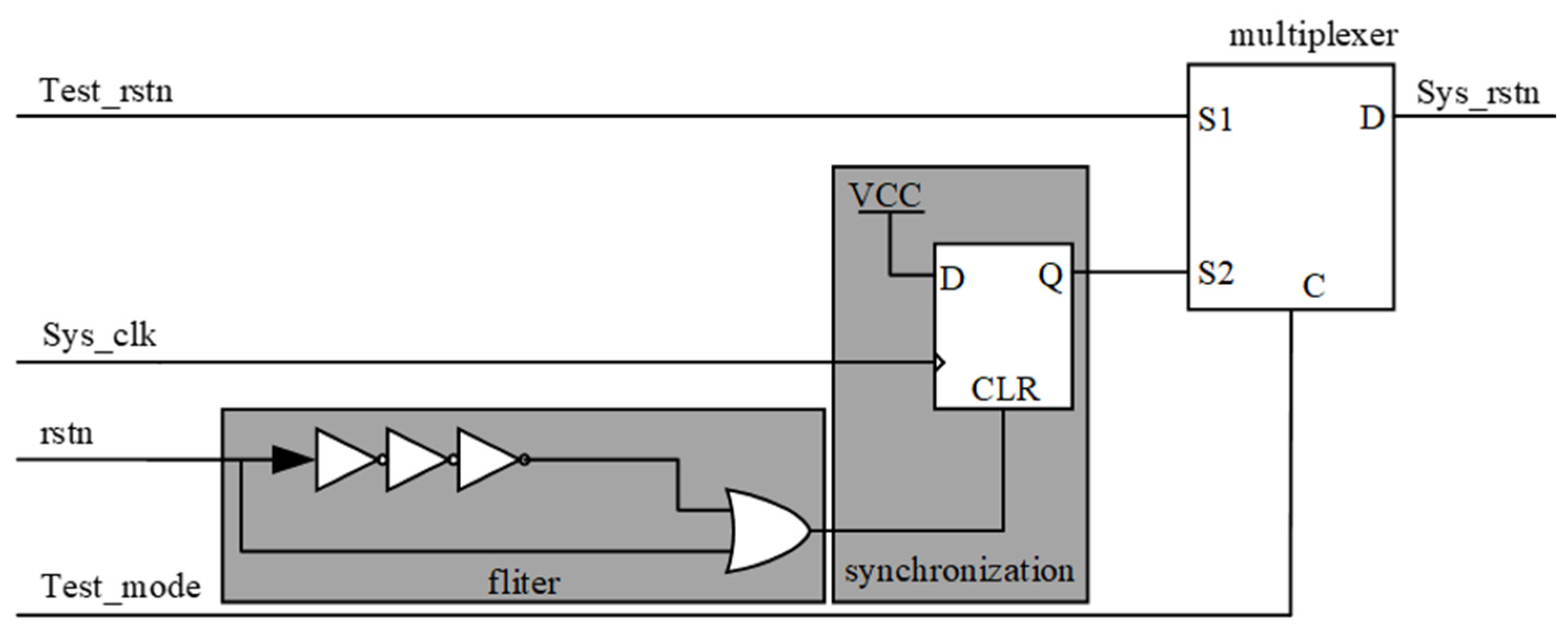

2.2. Hardware Division and Low-Power Design

3. Critical Module Design

3.1. Reordering Module Design

3.2. Data Windowing Module Design

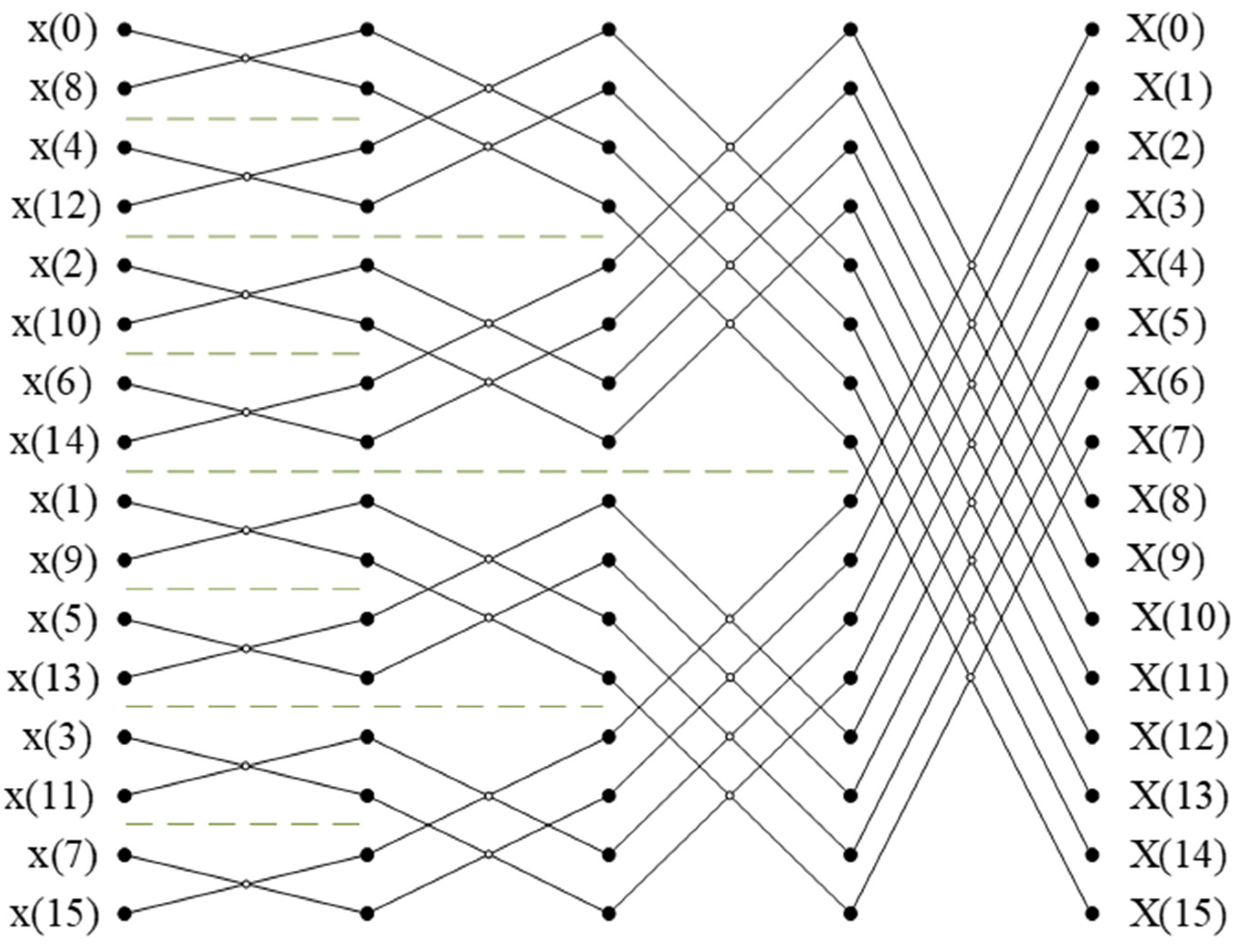

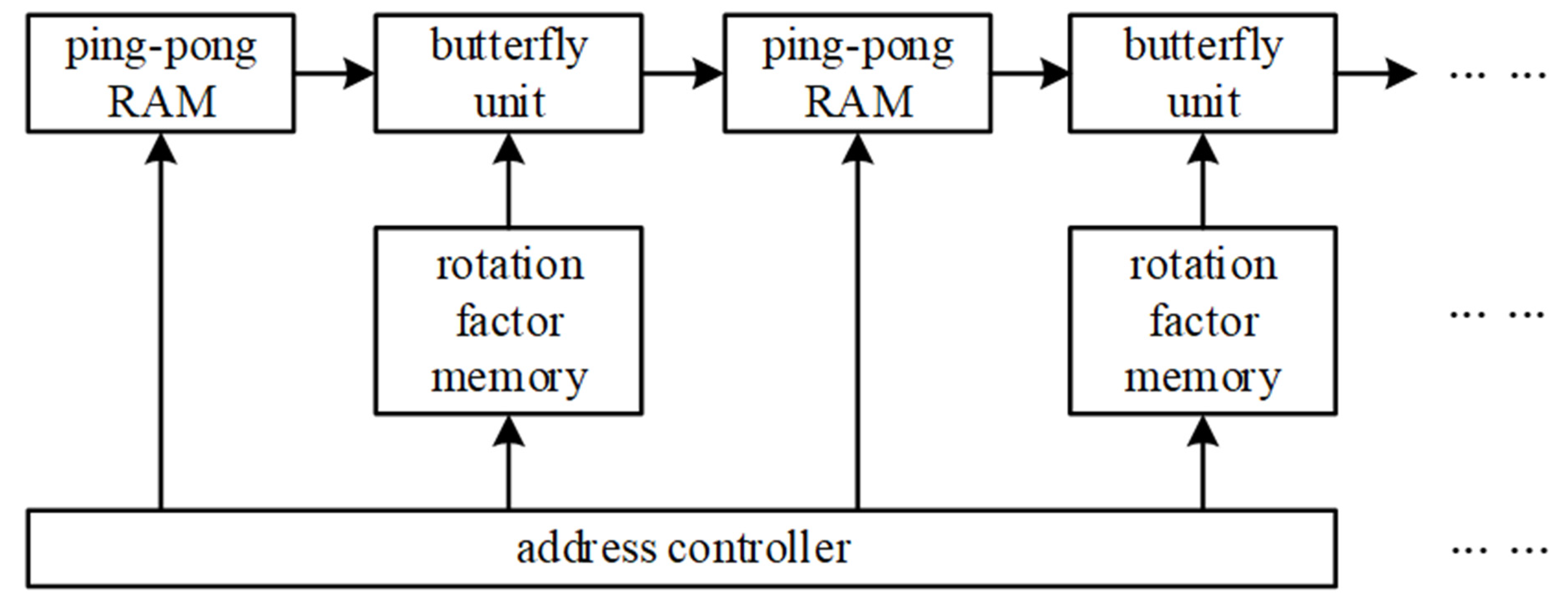

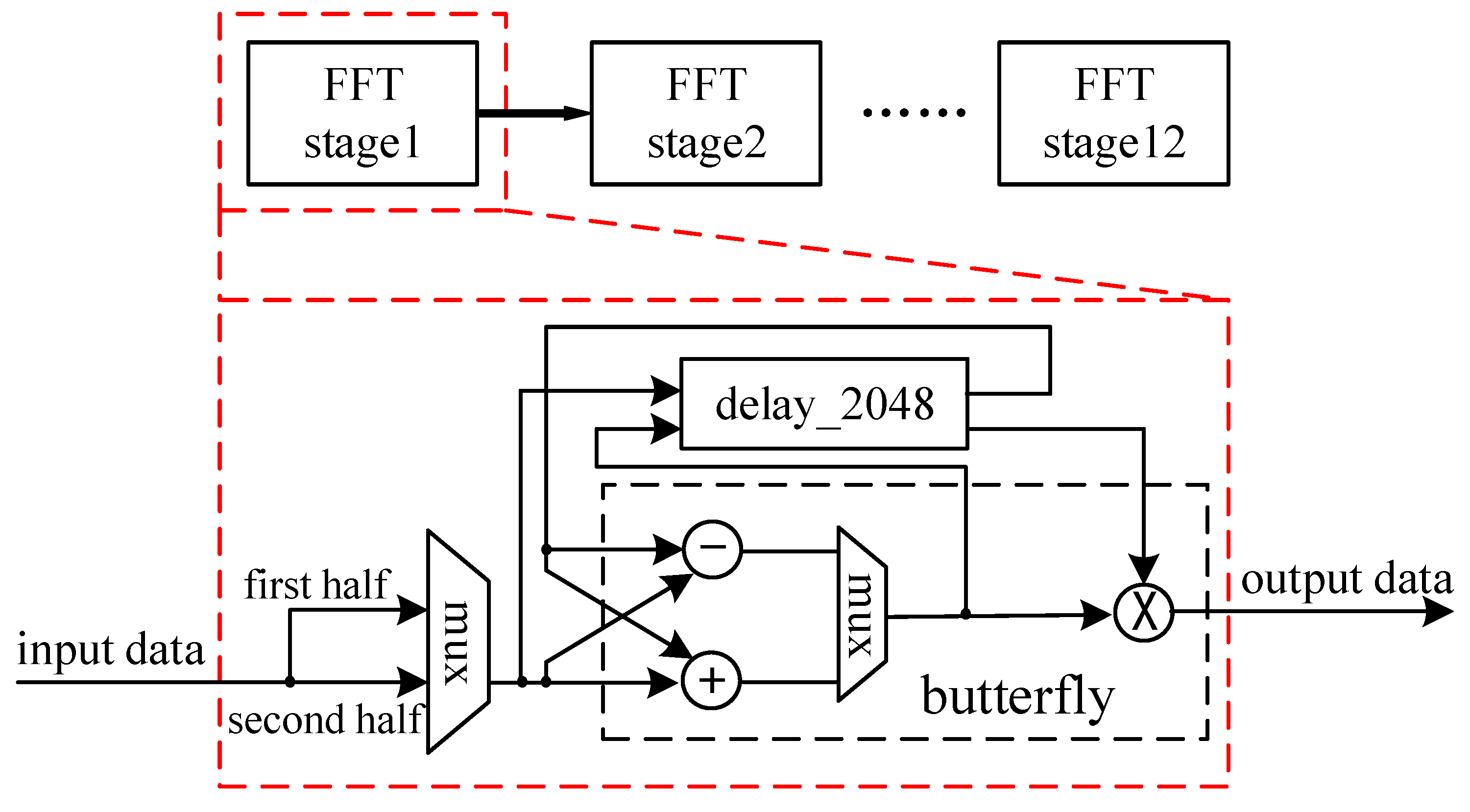

3.3. FFT Module Design

- It consists of 12 cascaded stages; each stage contains a Radix-2 butterfly computing unit;

- Each stage has a set of FIFOs. The length of the FIFO is determined by the location of the stage. The depth is selected according to the time-domain extracted signals; the circular buffer unit and the shift register are combined to achieve different series of butterfly operations;

- Due to the use of cascade structure, the FFT calculation module can obtain very strong throughput;

- The FFT calculation module uses the selector to select data between the FIFO and the butterfly unit.

3.4. Plural Modulo and Logarithmic Computation Module Design

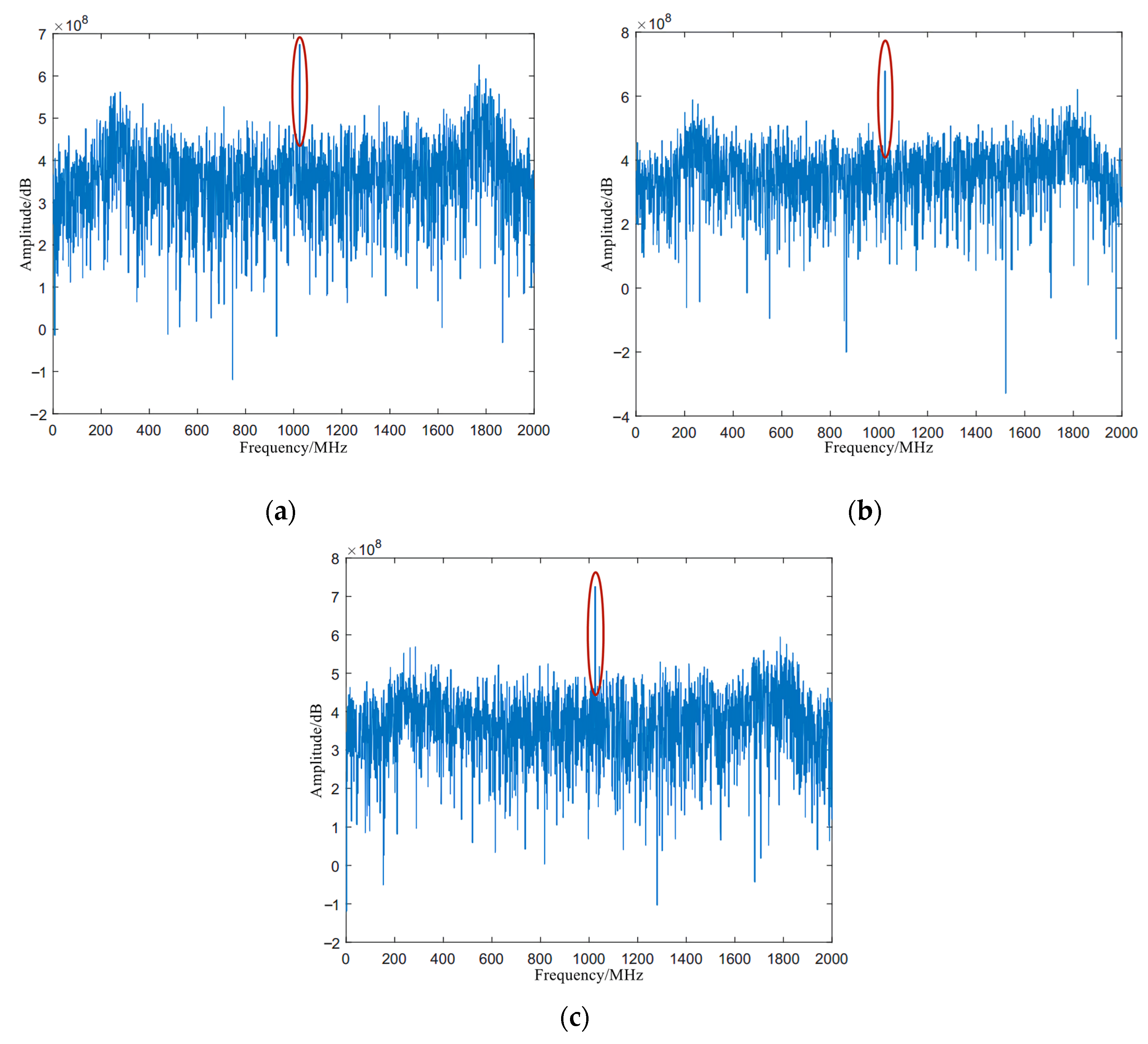

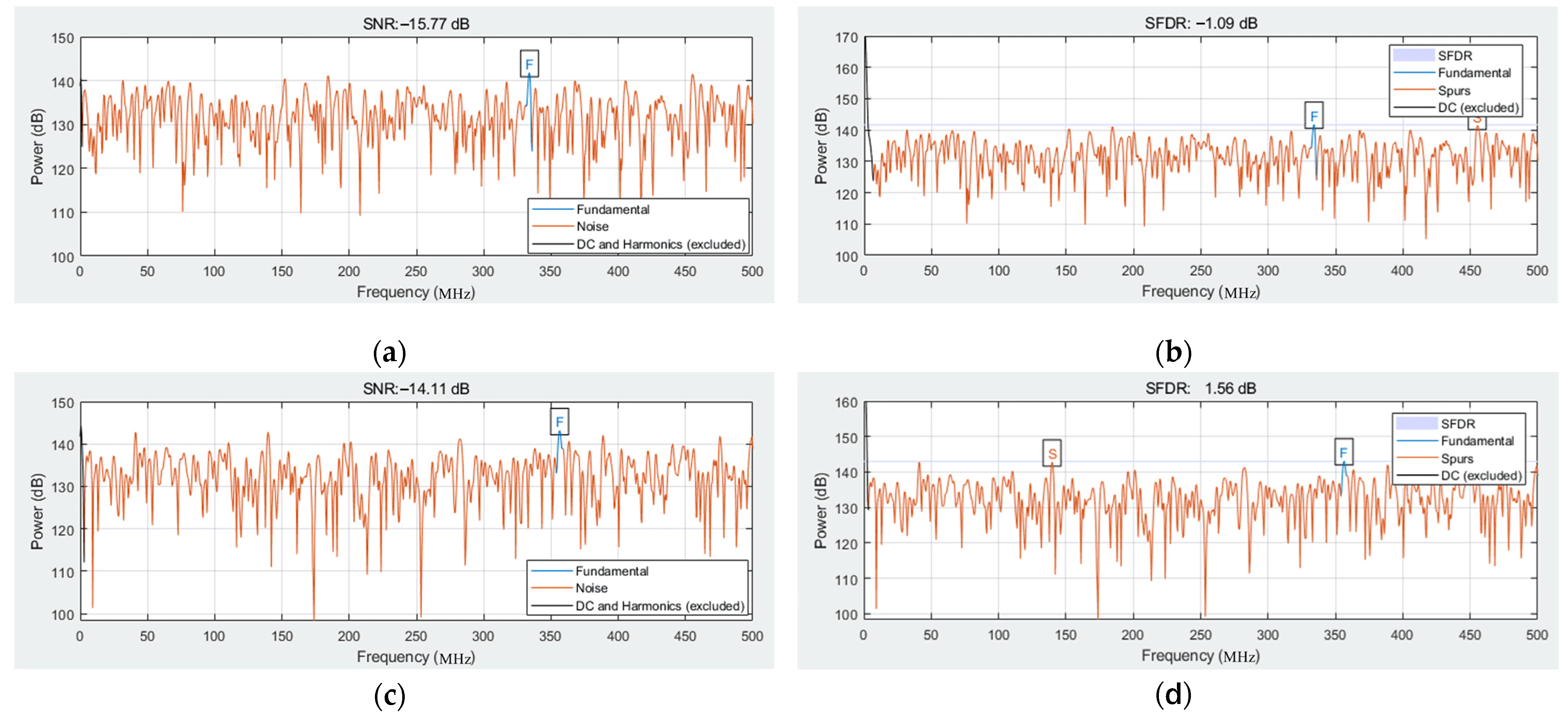

4. Analysis of Simulation Results

5. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Yin, S.; Chen, D.; Zhang, Q.; Liu, M.; Li, S. Mining Spectrum Usage Data: A Large-Scale Spectrum Measurement Study. IEEE. Trans. Mob. Comput. 2012, 11, 1033–1046. [Google Scholar] [CrossRef]

- Chen, Z.; Zhang, Y. Offshore Electromagnetic Spectrum Detection System Based on Self-Organizing Network. IEEE Sens. J. 2021, 21, 8650–8661. [Google Scholar] [CrossRef]

- Wang, W.L.; Giddings, R.P.; Zhang, Q.W.; Peng, J.J.; Chen, J.; Tang, J.M. Analytical Solution of Stage-Dependent Bit Resolution of Full Parallel Variable Point FFTs for Real-Time DSP Implementation. J. Light. Technol. 2018, 36, 5177–5187. [Google Scholar] [CrossRef]

- Xia, J.L.; Liang, Z.Y.; Cui, L.Z. Large Point FFT and IFFT Design Based on Multicore Parallel Processing. J. Fire Control Radar Technol. 2016, 45, 64–68. [Google Scholar] [CrossRef]

- Polat, G.; Ozturk, S.; Yakut, M. Design and Implementation of 256-Point Radix-4 100 Gbit/s FFT Algorithm into FPGA for High-Speed Applications. ETRI J. 2015, 37, 667–676. [Google Scholar] [CrossRef]

- Sankaran, A.; Reddy, M.S.; Arunkumar, K.; Bhaskar, M. Design and Implementation of 1024 Point Pipelined Radix 4 FFT Processor on FPGA for Biomedical Signal Processing Applications. In Proceedings of the 2020 6th IEEE International Symposium on Smart Electronic Systems (iSES 2020) (Formerly iNiS), Chennai, India, 14–16 December 2020; IEEE Computer Society: Los Alamitos, CA, USA, 2020; pp. 1–6. [Google Scholar]

- Li, Y.; Chen, H.; Xie, Y. An FPGA-Based Four-Channel 128k-Point FFT Processor Suitable for Spaceborne SAR. Electronics 2021, 10, 816. [Google Scholar] [CrossRef]

- Lecuyer, C. Driving Semiconductor Innovation: Moore’s Law at Fairchild and Intel. Enterp. Soc. 2022, 23, 133–163. [Google Scholar] [CrossRef]

- Samudrala, H.K.; Qadeer, S.; Azeemuddin, S.; Khan, Z. Parallel and Pipelined VLSI Implementation of the New Radix-2 DIT FFT Algorithm. In Proceedings of the 2018 IEEE International Symposium on Smart Electronic Systems (iSES) (Formerly iNiS), Hyderabad, India, 17–19 December 2018; pp. 21–26. [Google Scholar]

- Li, T.; Hou, J.; Yan, J.; Liu, R.; Yang, H.; Sun, Z. Chiplet Heterogeneous Integration Technology—Status and Challenges. Electronics 2020, 9, 670. [Google Scholar] [CrossRef]

- Shan, G.; Zheng, Y.; Xing, C.; Chen, D.; Li, G.; Yang, Y. Architecture of Computing System Based on Chiplet. Micromachines 2022, 13, 205. [Google Scholar] [CrossRef] [PubMed]

- Meng, B.P.; Shan, G.B.; Zheng, Y.W.; Xiang, H. Design of Spectrum Processing Chiplet-based on FFT Algorithm. In Proceedings of the 8th International Conference on Sensors Engineering and Electronics Instrumentation Advances (SEIA’ 2022), Corfu Holiday Palace, Corfu, Greece, 21–23 September 2022; pp. 196–202. [Google Scholar]

- Cooley, J.; Lewis, P.; Welch, P. Application of the Fast Fourier Transform to Computation of Fourier Integrals, Fourier Series, and Convolution Integrals. IEEE Trans. Audio Electroacoust. 1967, 15, 79–84. [Google Scholar] [CrossRef]

- Cooley, J.W.; Tukey, J.W. An Algorithm for the Machine Calculation of Complex Fourier Series. Math. Comput. 1965, 19, 297–301. [Google Scholar] [CrossRef]

- Valencia, D.; Alimohammad, A. Compact and High-Throughput Parameterisable Architectures for Memory-Based FFT Algorithms. IET Circuits Devices Syst. 2019, 13, 696–703. [Google Scholar] [CrossRef]

- Jiang, H.; Luo, H.; Tian, J.; Song, W. Design of an Efficient FFT Processor for OFDM Systems. IEEE Trans. Consum. Electron. 2005, 51, 1099–1103. [Google Scholar] [CrossRef]

- Kulkarni, R.G. Synthesis of a New Signal Processing Window. Electron. Lett. 2019, 55, 1108–1110. [Google Scholar] [CrossRef]

| Type of Window | Window Length | Main-Lobe Width | Maximum Side-Lobe Level/(dB) | Side-Lobe Fall-Off/(dB/oct) |

|---|---|---|---|---|

| Rectangle window | N | 4π/N | −13 | 6 |

| Hann window | N | 8π/N | −31 | 18 |

| Hamming window | N | 8π/N | −43 | 6 |

| Blackman window | N | 12π/N | −58 | 18 |

| Parameter | [6] | This Work |

|---|---|---|

| Verification Platform | Virtex-7 | ZYNQ 7035 |

| FFT Size | 1024 | 4096 |

| Algorithm | Radix-4 | Radix-2 |

| Operating Frequency | 117 MHz | 61.44 MHz |

| Execution Time | 0.22 ms | 0.368 ms |

| Frequency (MHz) | SNR (dB) | SFDR (dB) |

|---|---|---|

| 4780 | −15.8 | −1.0 |

| 4820 | −14.1 | 1.56 |

| 4900 | −11.98 | 2.70 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Meng, B.; Shan, G.; Zheng, Y. Design of Spectrum Processing Chiplet Based on FFT Algorithm. Micromachines 2023, 14, 402. https://doi.org/10.3390/mi14020402

Meng B, Shan G, Zheng Y. Design of Spectrum Processing Chiplet Based on FFT Algorithm. Micromachines. 2023; 14(2):402. https://doi.org/10.3390/mi14020402

Chicago/Turabian StyleMeng, Baoping, Guangbao Shan, and Yanwen Zheng. 2023. "Design of Spectrum Processing Chiplet Based on FFT Algorithm" Micromachines 14, no. 2: 402. https://doi.org/10.3390/mi14020402

APA StyleMeng, B., Shan, G., & Zheng, Y. (2023). Design of Spectrum Processing Chiplet Based on FFT Algorithm. Micromachines, 14(2), 402. https://doi.org/10.3390/mi14020402