Study on ESD Protection Circuit by TCAD Simulation and TLP Experiment

Abstract

1. Introduction

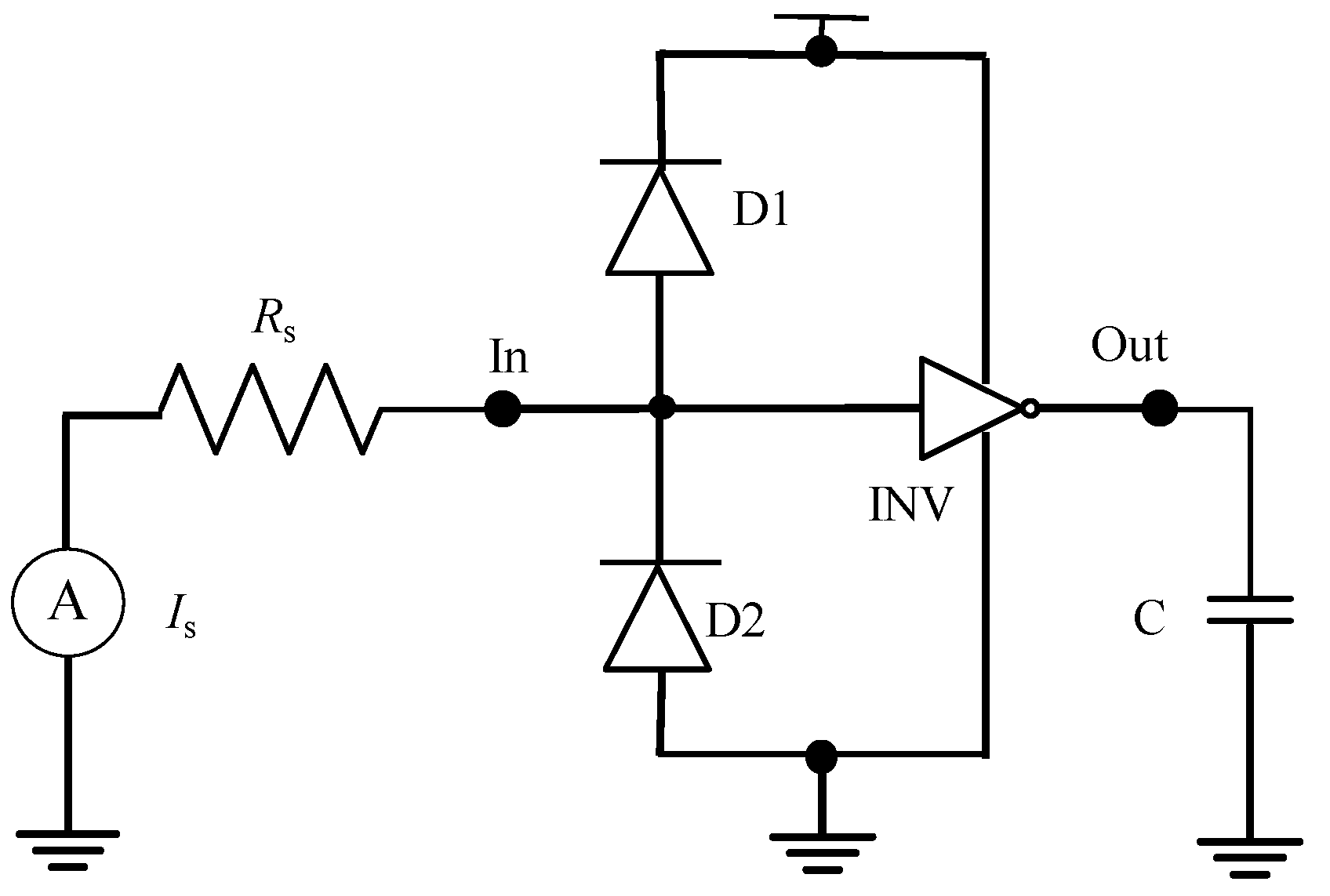

2. ESD Protection Circuit Model

2.1. The Structure of Circuits and Devices

2.2. Physical Models Involved in the Model

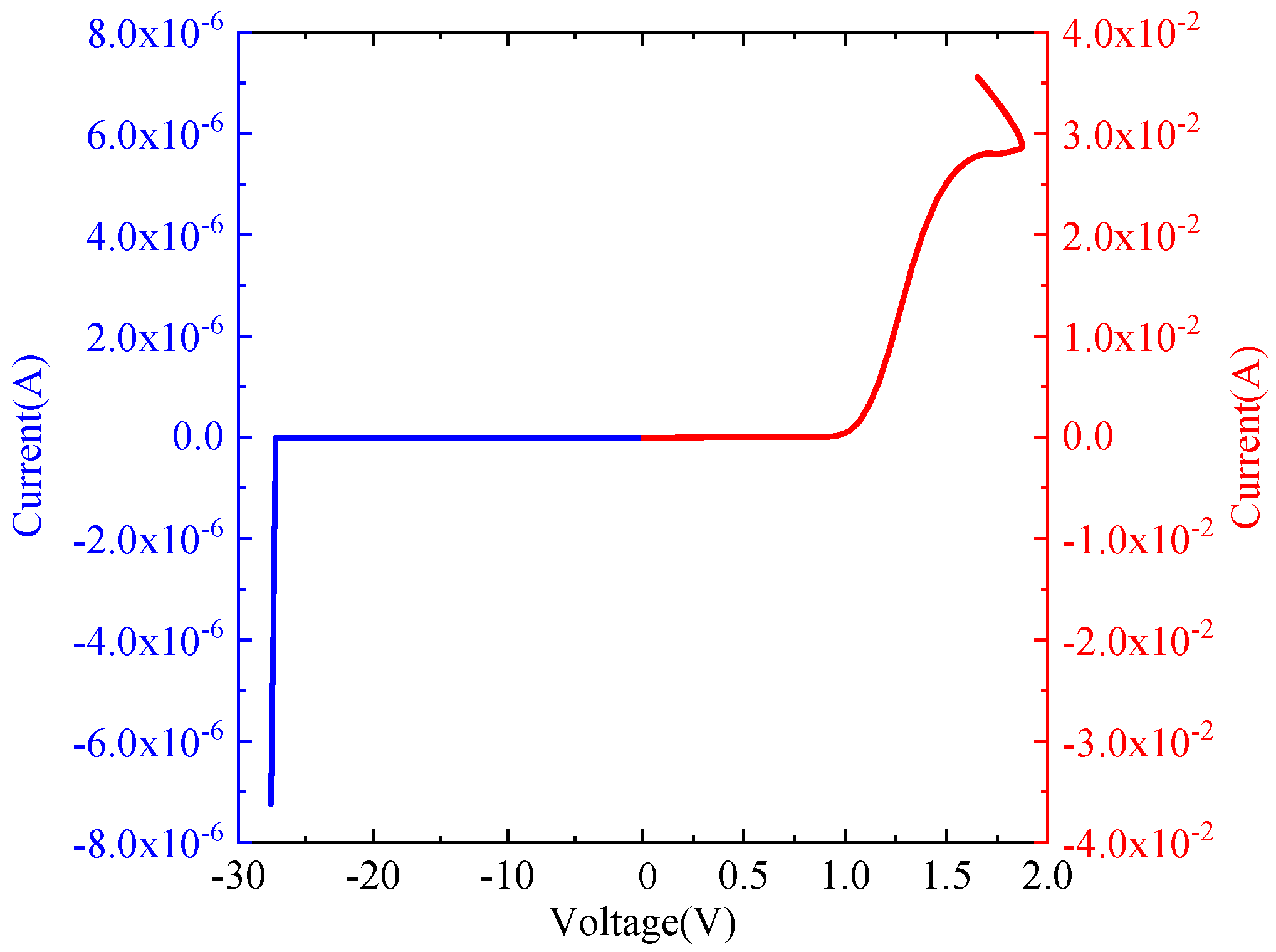

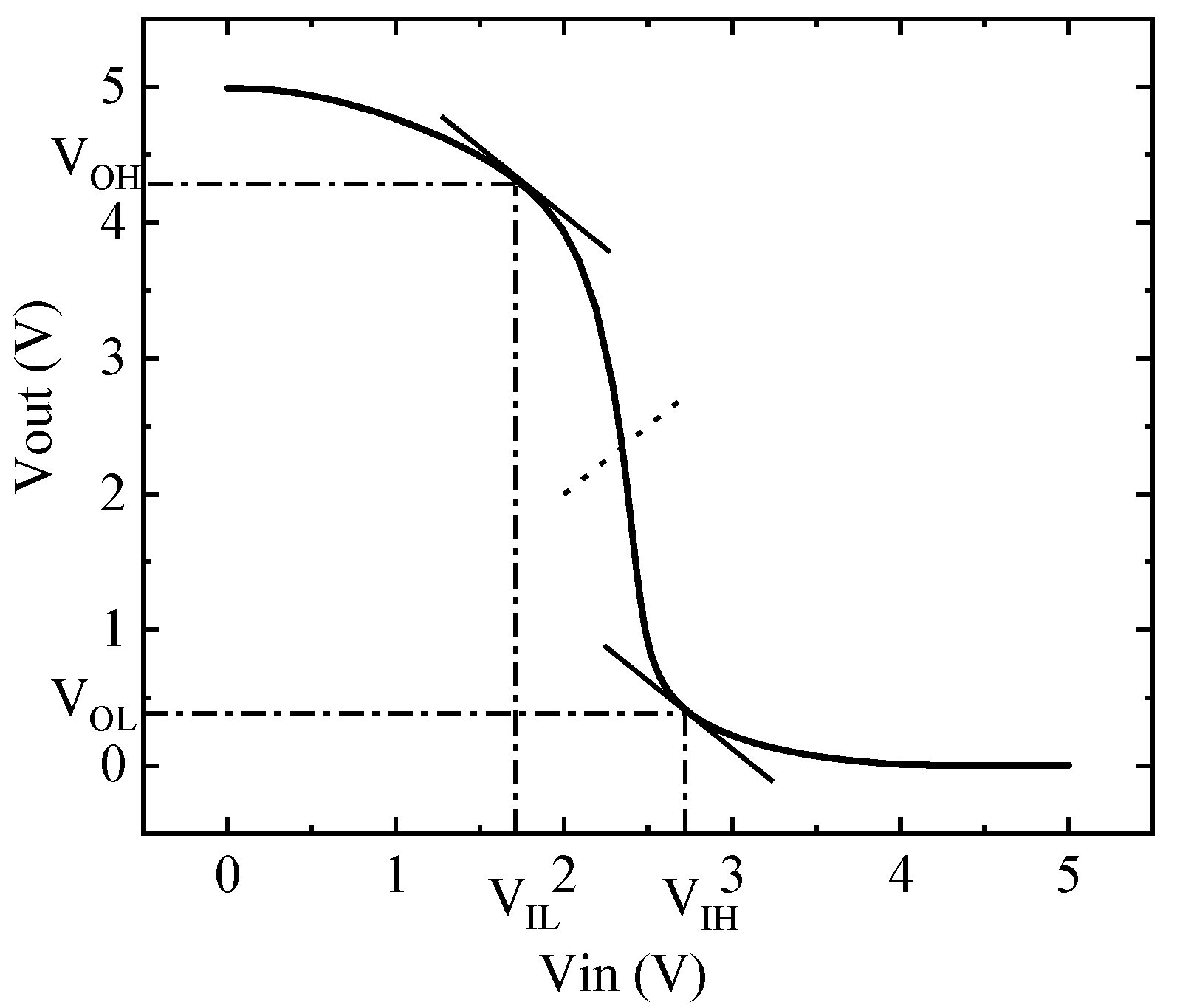

2.3. Electrical Characteristics Simulation of the Model

3. Simulation and Result Discuss

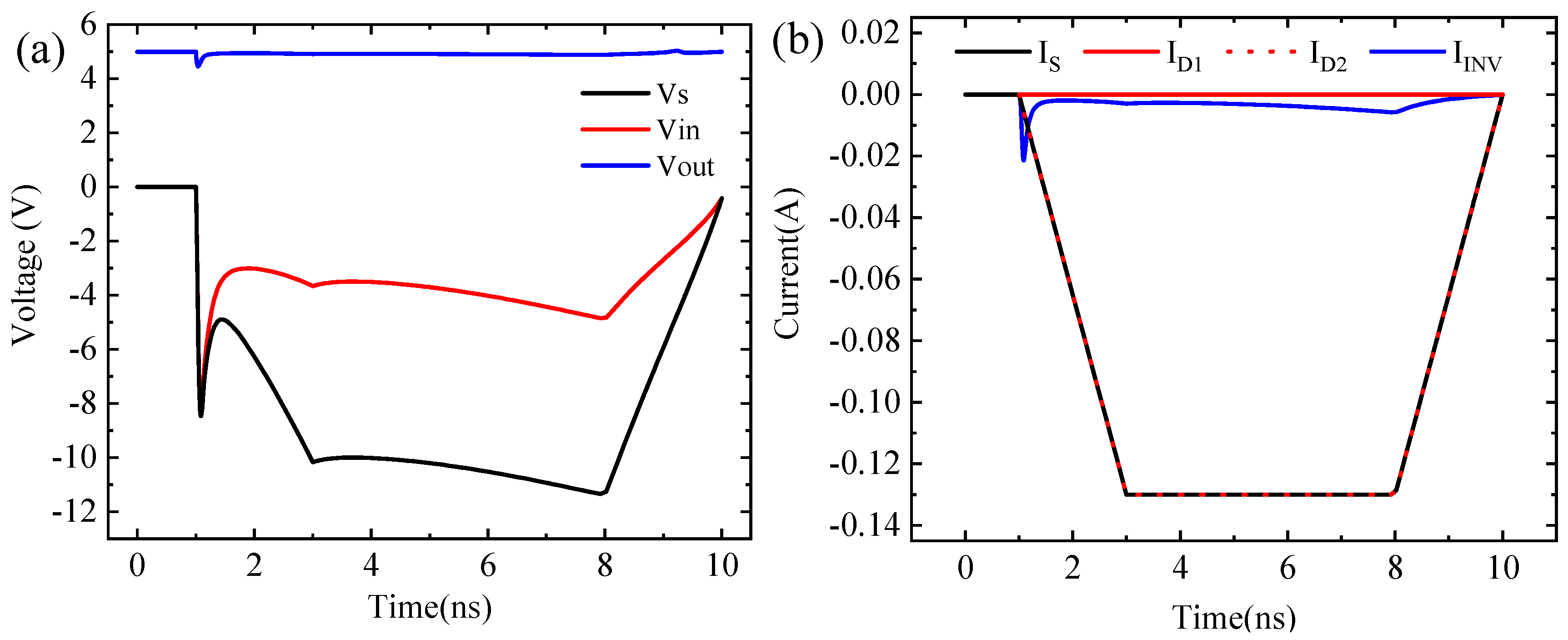

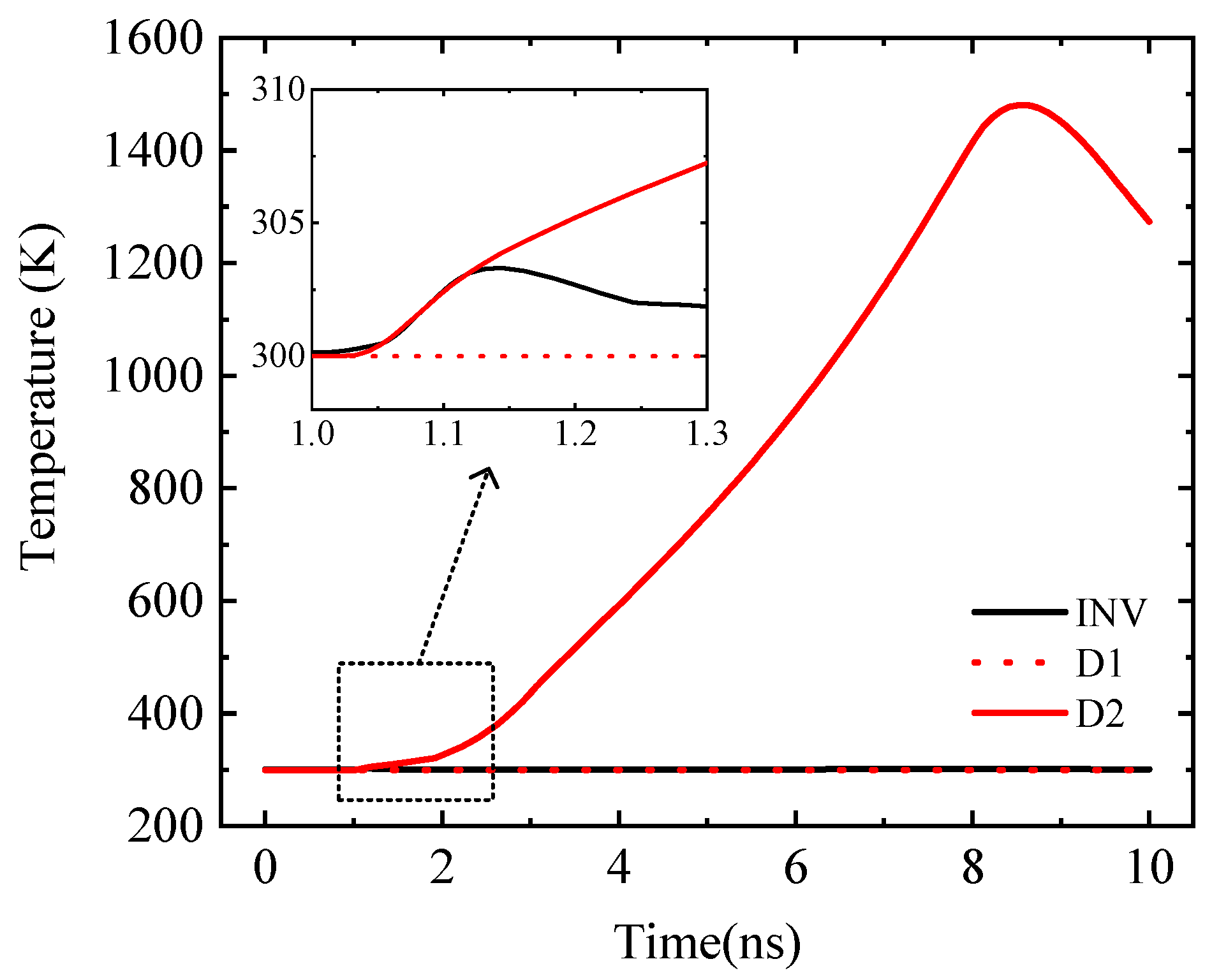

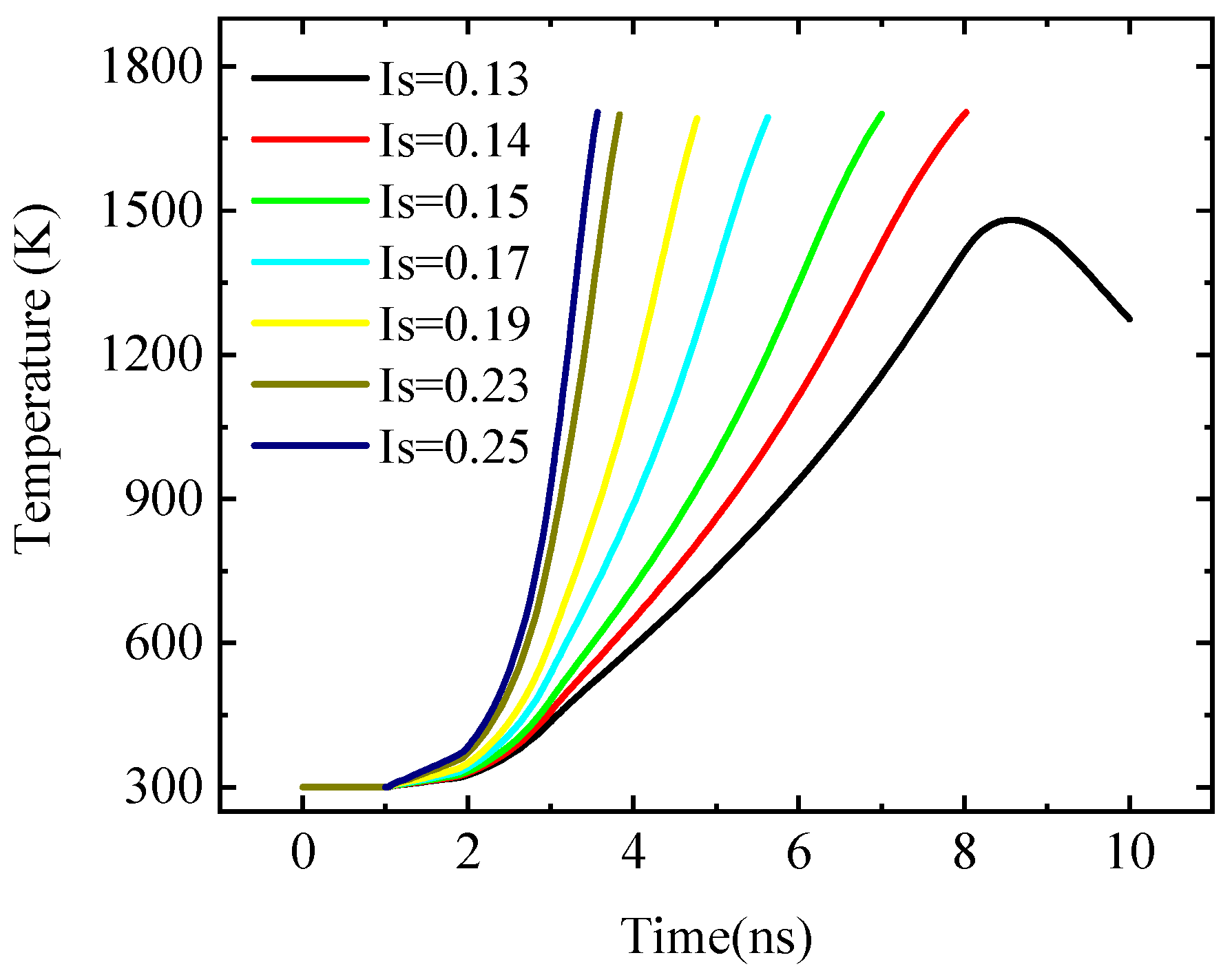

3.1. Transient Simulation Analysis of the Model

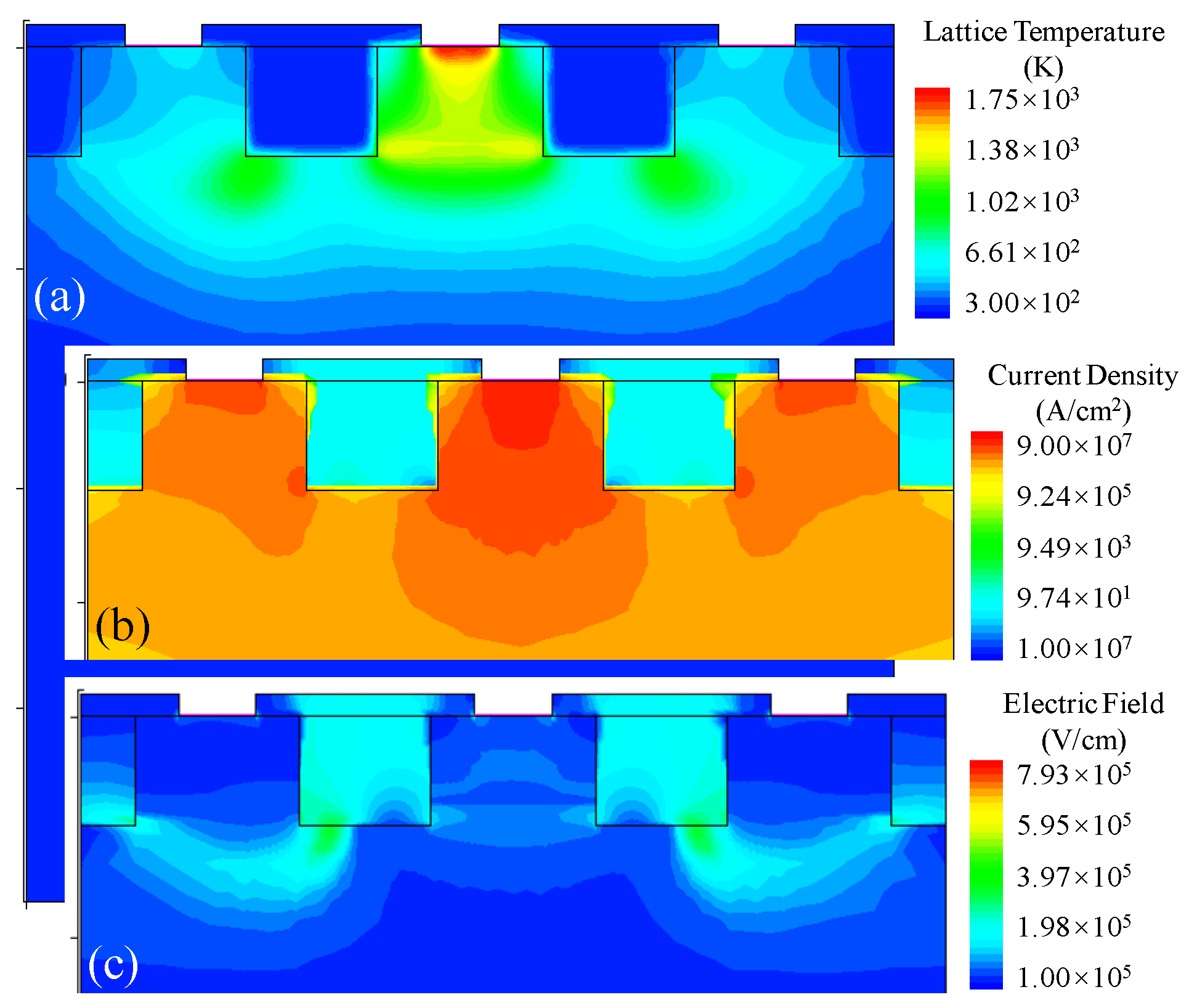

3.2. Mechanism Analysis of Burning Damage

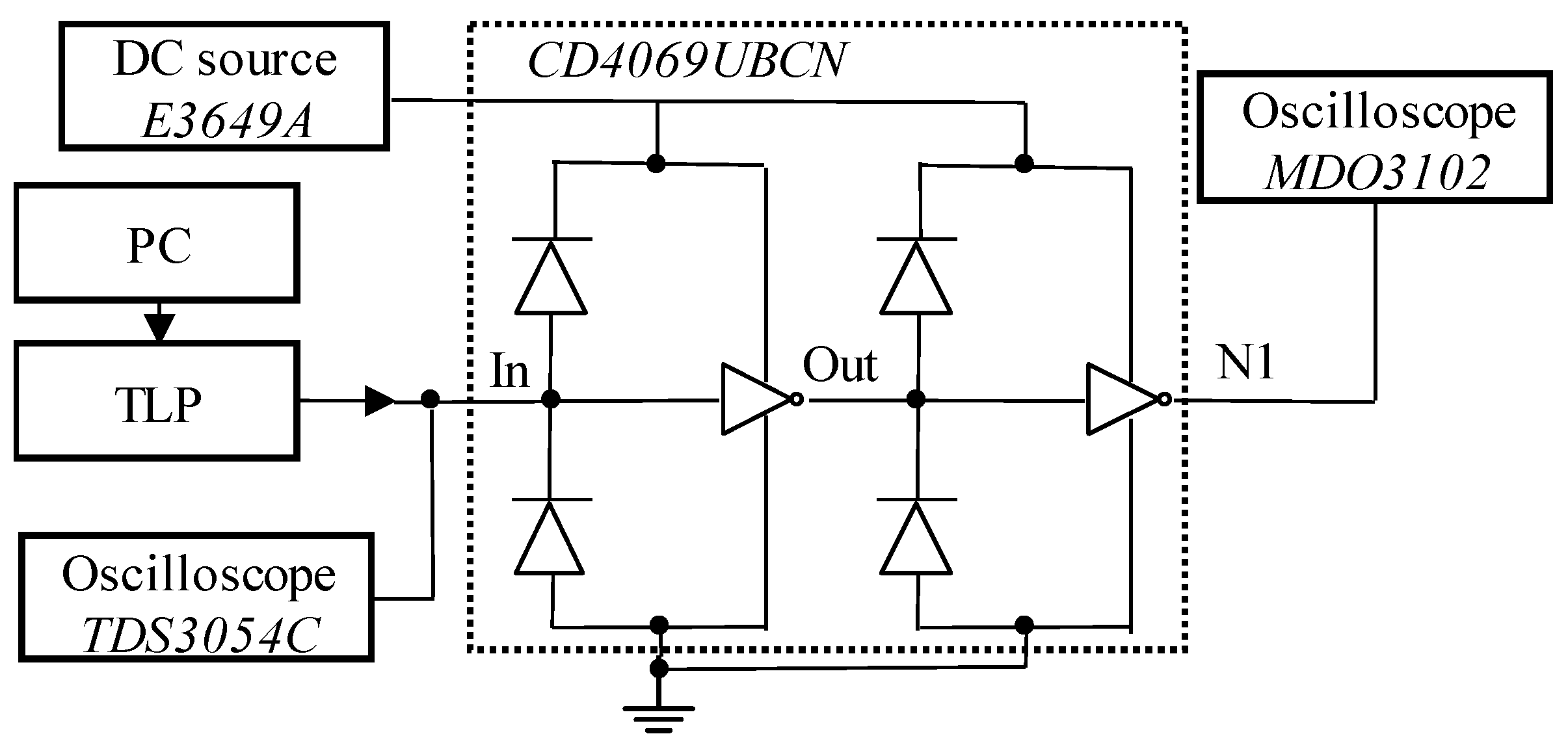

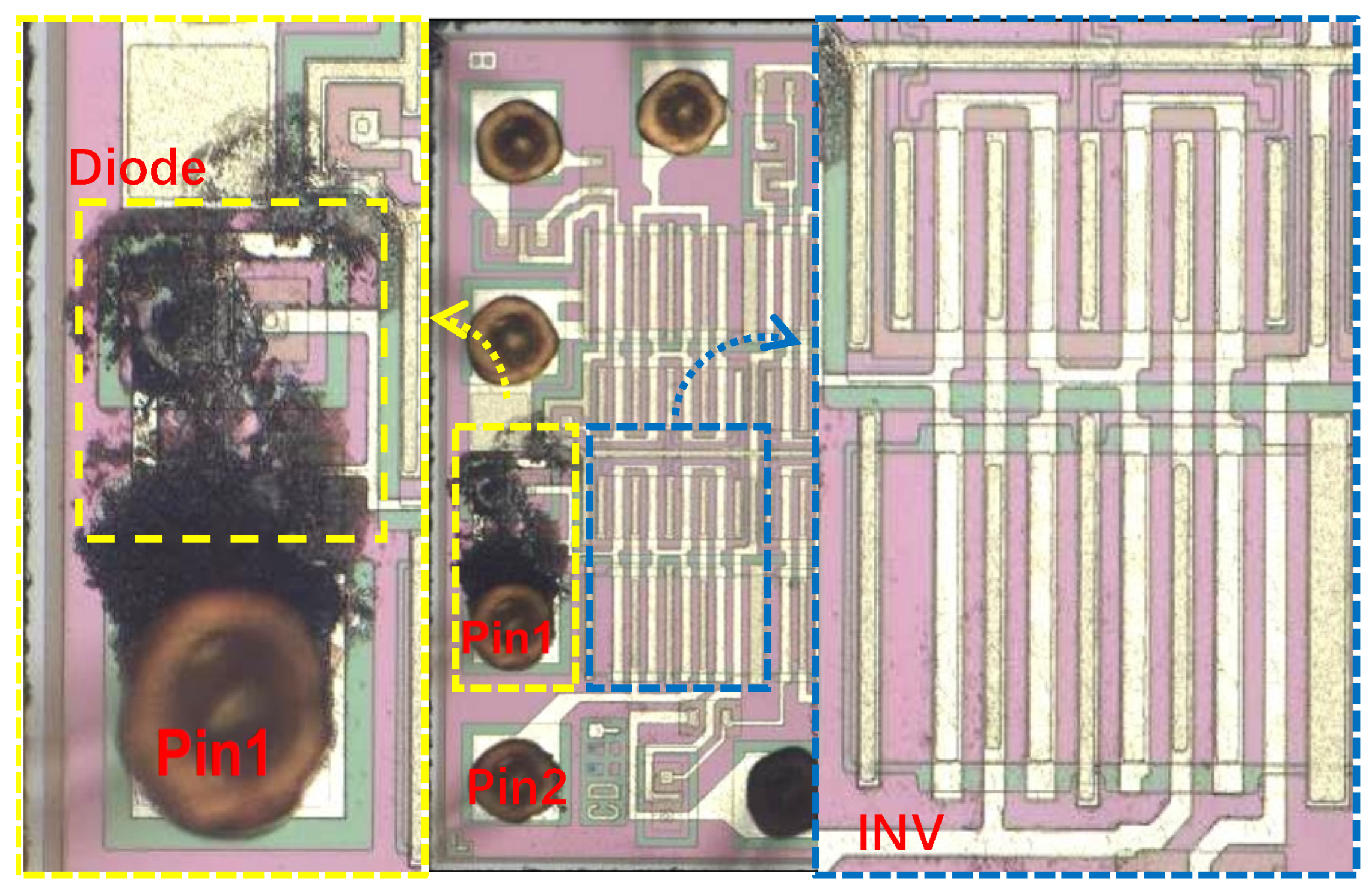

4. TLP Experiment and Result Analysis

4.1. TLP Experiment Process

- E3649A DC source used to supply power to the device under test (DUT);

- System PC used to complete TLP pulse parameter setting, data storage, and other operations;

- A TLP pulse generator module for generating the required TLP pulse signal and a small signal to detect leakage current;

- The peak injection pulse collected by the TDS3054C oscilloscope;

- The MDO3102 oscilloscope is used to record the response voltage waveform at the output port of DUT monitoring.

4.2. The Result Analysis

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Wang, X.; Fan, S.; Zhao, H.; Lin, L.; Fang, Q.; Tang, H.; Wang, A. Whole-Chip ESD protection design for RF and AMS ICs. Tsinghua Sci. Technol. 2010, 15, 265–274. [Google Scholar] [CrossRef]

- Hill, I.; Chanawala, P.; Singh, R.; Sheikholeslam, S.A.; Ivanov, A. CMOS Reliability From Past to Future: A Survey of Requirements, Trends, and Prediction Methods. IEEE Trans. Device Mater. Reliab. 2022, 22, 1–18. [Google Scholar] [CrossRef]

- Meiguni, J.S.; Zhou, J.; Maghlakelidze, G.; Xu, Y.; Izadi, O.H.; Marathe, S.; Shen, L.; Bub, S.; Holland, S.; Beetner, D.G.; et al. Transient Analysis of ESD Protection Circuits for High-Speed ICs. IEEE Trans. Electromagn. Compat. 2021, 63, 1312–1321. [Google Scholar] [CrossRef]

- Haigang, F.; Guang, C.; Rouying, Z.; Qiong, W.; Xiaokang, G.; Haolu, X.; Wang, A.Z.H.; Gafiteanu, R. A mixed-mode esd protection circuit simulation-design methodology. IEEE J. Solid-State Circuits 2003, 38, 995–1006. [Google Scholar] [CrossRef]

- Ker, M.D.; Yen, C.C. Investigation and Design of On-Chip Power-Rail ESD Clamp Circuits Without Suffering Latchup-Like Failure During System-Level ESD Test. IEEE J. Solid-State Circuits 2008, 43, 2533–2545. [Google Scholar] [CrossRef]

- ISO 10605; Road Vehicles—Test Methods for Electrical Disturbances From Electrostatic Discharge. ISO Standard: Geneva, Switzerland, 2008.

- Zhang, F.; Wang, C.; Lu, F.; Chen, Q.; Li, C.; Wang, X.S.; Li, D.; Wang, A. A Full-Chip ESD Protection Circuit Simulation and Fast Dynamic Checking Method Using SPICE and ESD Behavior Models. IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst. 2019, 38, 489–498. [Google Scholar] [CrossRef]

- Ammer, M.; Rupp, A.; Glaser, U.; Cao, Y.Q.; Sauter, M.; Maurer, L. Application Example of a Novel Methodology to Generate IC Models for System ESD and Electrical Stress Simulation out of the Design Data. In Proceedings of the 41st Annual EOS/ESD Symposium (EOS/ESD), Riverside, CA, USA, 15–20 September 2019. [Google Scholar]

- LI, Z.; Zhu, B.; Nath, A. Understanding ESD Induced Thermal Mechanism in FinFETs Through Predictive TCAD Simulation. In Proceedings of the 2020 IEEE International Reliability Physics Symposium (IRPS), Dallas, TX, USA, 30 June 2020. [Google Scholar]

- Negri, S.; Spadacini, G.; Grassi, F.; Pignari, S.A. Black-Box Modeling of EMI Filters for Frequency and Time-Domain Simulations. IEEE Trans. Electromagn. Compat. 2022, 64, 119–128. [Google Scholar] [CrossRef]

- Venugopalan, S.; Dandu, K.; Martin, S.; Taylor, R.; Cirba, C.; Zhang, X.; Niknejad, A.M.; Hu, C. A non-iterative physical procedure for RF CMOS compact model extraction using BSIM6. In Proceedings of the Proceedings of the IEEE 2012 Custom Integrated Circuits Conference, San Jose, CA, USA, 9–12 September 2012; pp. 1–4. [Google Scholar]

- Park, M.; Park, J.; Choi, J.; Kim, J.; Jeong, S.; Seung, M.; Lee, S.; Kim, J. Measurement and Analysis of Statistical IC Operation Errors in a Memory Module Due to System-Level ESD Noise. IEEE Trans. Electromagn. Compat. 2019, 61, 29–39. [Google Scholar] [CrossRef]

- Yang, S.; Pommerenke, D.J. Effect of Different Load Impedances on ESD Generators and ESD Generator SPICE Models. IEEE Trans. Electromagn. Compat. 2018, 60, 1726–1733. [Google Scholar] [CrossRef]

- Morozzi, A.; Moscatelli, F.; Croci, T.; Passeri, D. TCAD Modeling of Surface Radiation Damage Effects: A State-Of-The-Art Review. Front. Phys. 2021, 9, 617322. [Google Scholar] [CrossRef]

- Fichtner, W. Overview of technology computer-aided design tools and applications in technology development, manufacturing and design. J. Comput. Theor. Nanosci. 2008, 5, 1089–1105. [Google Scholar] [CrossRef]

- Qin, Y.; Chai, C.; Li, F.; Liang, Q.; Wu, H.; Yang, Y. Study of Self-Heating and High-Power Microwave Effects for Enhancement-Mode p-Gate GaN HEMT. Micromachines 2022, 13, 106. [Google Scholar] [CrossRef] [PubMed]

- Di, M.; Pan, Z.; Li, C.; Wang, A. ESD Design Verification Aided by Mixed-Mode Multiple-Stimuli ESD Simulation. IEEE J. Electron. Devices Soc. 2021, 9, 1194–1201. [Google Scholar] [CrossRef]

- Li, F.X.; Chai, C.C.; Wu, H.; Lei, L.; Liang, Q.S.; An, Q.; Yang, Y.T. Study on high power microwave nonlinear effects and degradation characteristics of C-band low noise amplifier. Microelectron. Reliab. 2022, 128, 114427. [Google Scholar] [CrossRef]

- Au, T.; Syrzycki, M. Investigation of STI diodes as electrostatic discharge (ESD) protection devices in deep submicron (DSM) CMOS process. In Proceedings of the 2013 26th IEEE Canadian Conference on Electrical and Computer Engineering (CCECE), Regina, Canada, 5–8 May 2013; pp. 1–5. [Google Scholar]

- Pan, Z.; Li, C.; Di, M.; Zhang, F.; Wang, A. 3D TCAD Analysis Enabling ESD Layout Design Optimization. IEEE J. Electron. Devices Soc. 2020, 8, 1289–1296. [Google Scholar] [CrossRef]

- Synopsys. 2016 Sentaurus-Tcad Dessis Simulation User’s Manual; Synopsys: Mountain View, CA, USA, 2016. [Google Scholar]

- Kampen, C.; Burenkov, A.; Lorenz, J. Challenges in TCAD Simulations of Tunneling Field Effect Transistors. In Proceedings of the 2011 Proceedings of the European Solid-State Device Research Conference, Helsinki, Finland, 12–16 September 2011; pp. 139–142. [Google Scholar]

- Blaho, M.; Zullino, L.; Wolf, H.; Stella, R.; Andreini, A.; Gieser, H.A.; Pogany, D.; Gornik, E. Internal behavior of BCD ESD protection devices under TLP and very-fast TLP stress. IEEE Trans. Device Mater. Reliab. 2004, 4, 535–541. [Google Scholar] [CrossRef]

- Wang, Y.; Wang, Y. Modeling Study of Power-On and Power-Off System-Level Electrostatic Discharge Protection. IEEE Trans. Electromagn. Compat. 2021, 63, 979–987. [Google Scholar] [CrossRef]

- Liu, Y.-Q.; Chai, C.-C.; Zhang, Y.-H.; Shi, C.-L.; Liu, Y.; Fan, Q.-Y.; Yang, Y.-T. Physics-based analysis and simulation model of electromagnetic interference induced soft logic upset in CMOS inverter. Chin. Phys. B 2018, 27, 068505. [Google Scholar] [CrossRef]

- Li, Y.; Chai, C.C.; Liu, Y.Q.; Li, Y.; Wu, H.; Zhang, W.; Li, F.Z.; Yang, Y.T. Upset and damage mechanisms of the three-dimensional silicon device induced by high power microwave interference. IEICE Electron. Express 2019, 16, 20190498. [Google Scholar] [CrossRef]

- Galy, P.; Schoenmaker, W. In-Depth Electromagnetic Analysis of ESD Protection for Advanced CMOS Technology During Fast Transient and High-Current Surge. IEEE Trans. Electron Devices 2014, 61, 1900–1906. [Google Scholar] [CrossRef]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Li, F.; Chai, C.; Liu, Y.; Song, Y.; Wang, L.; Yang, Y. Study on ESD Protection Circuit by TCAD Simulation and TLP Experiment. Micromachines 2023, 14, 600. https://doi.org/10.3390/mi14030600

Li F, Chai C, Liu Y, Song Y, Wang L, Yang Y. Study on ESD Protection Circuit by TCAD Simulation and TLP Experiment. Micromachines. 2023; 14(3):600. https://doi.org/10.3390/mi14030600

Chicago/Turabian StyleLi, Fuxing, Changchun Chai, Yuqian Liu, Yanxing Song, Lei Wang, and Yintang Yang. 2023. "Study on ESD Protection Circuit by TCAD Simulation and TLP Experiment" Micromachines 14, no. 3: 600. https://doi.org/10.3390/mi14030600

APA StyleLi, F., Chai, C., Liu, Y., Song, Y., Wang, L., & Yang, Y. (2023). Study on ESD Protection Circuit by TCAD Simulation and TLP Experiment. Micromachines, 14(3), 600. https://doi.org/10.3390/mi14030600