Assessment of the Risk of Crack Formation at a Hybrid Bonding Interface Using Numerical Analysis

Abstract

:1. Introduction

2. Theoretical Background

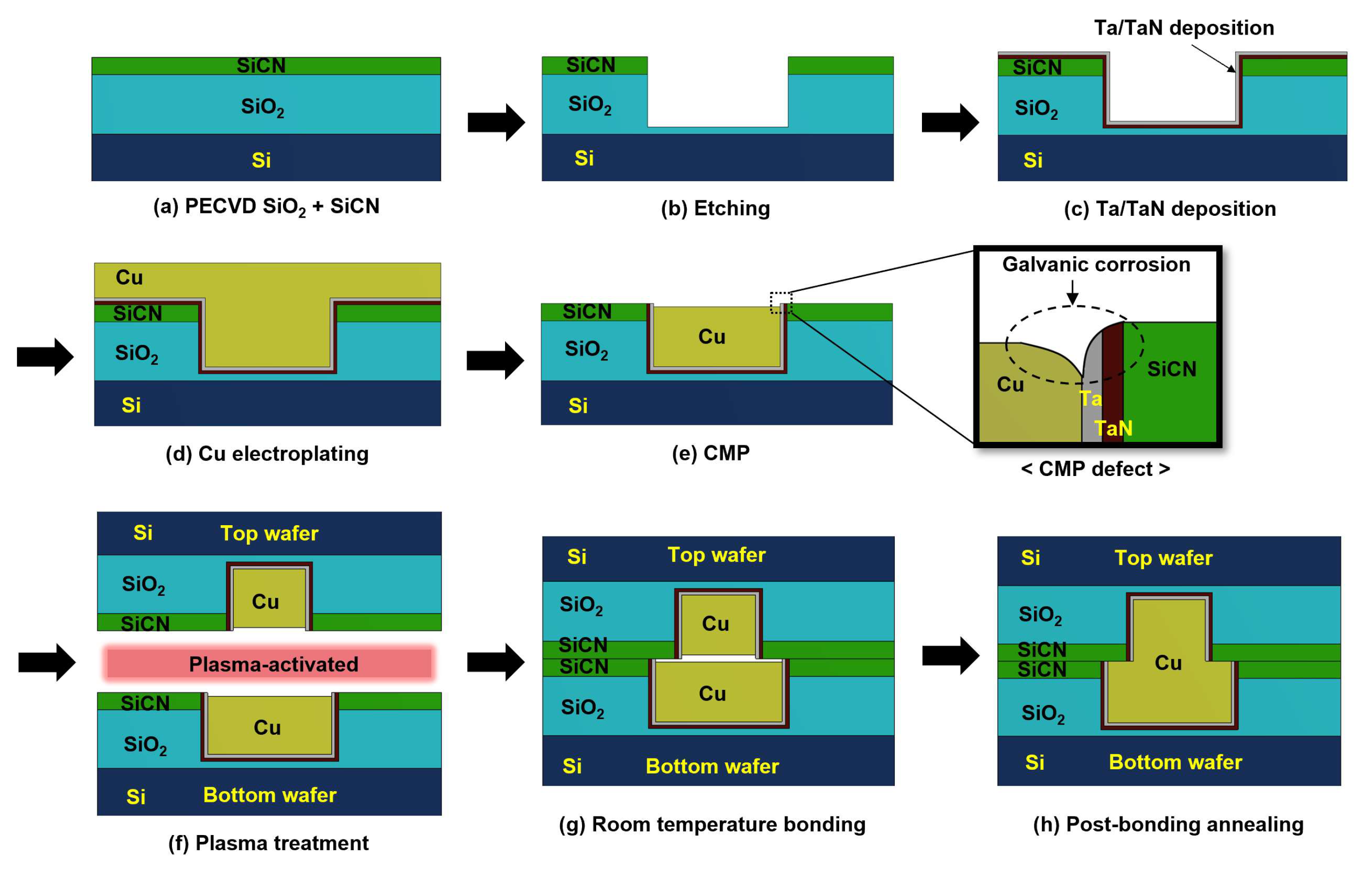

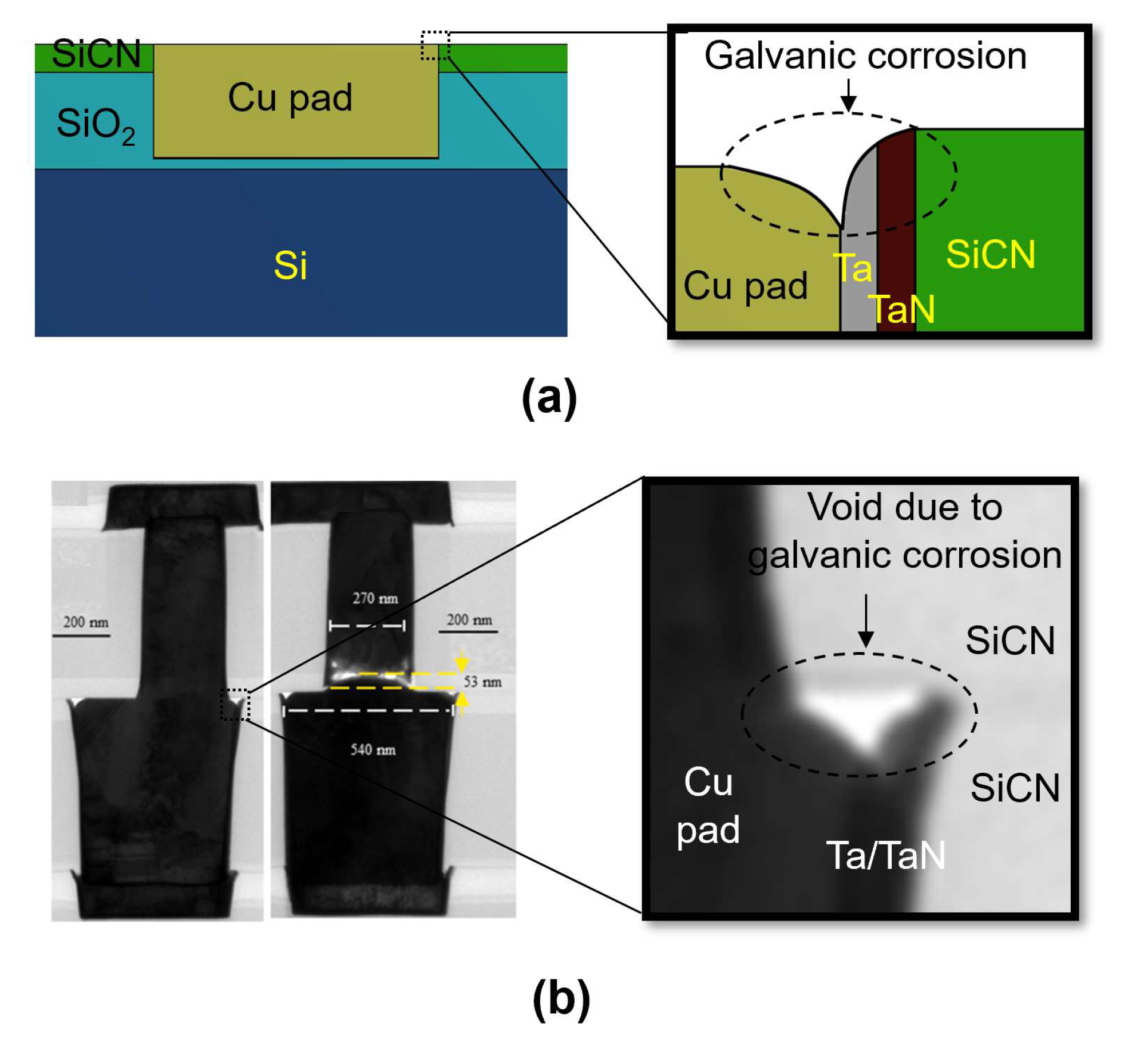

2.1. CMP Defects in Hybrid Bonding

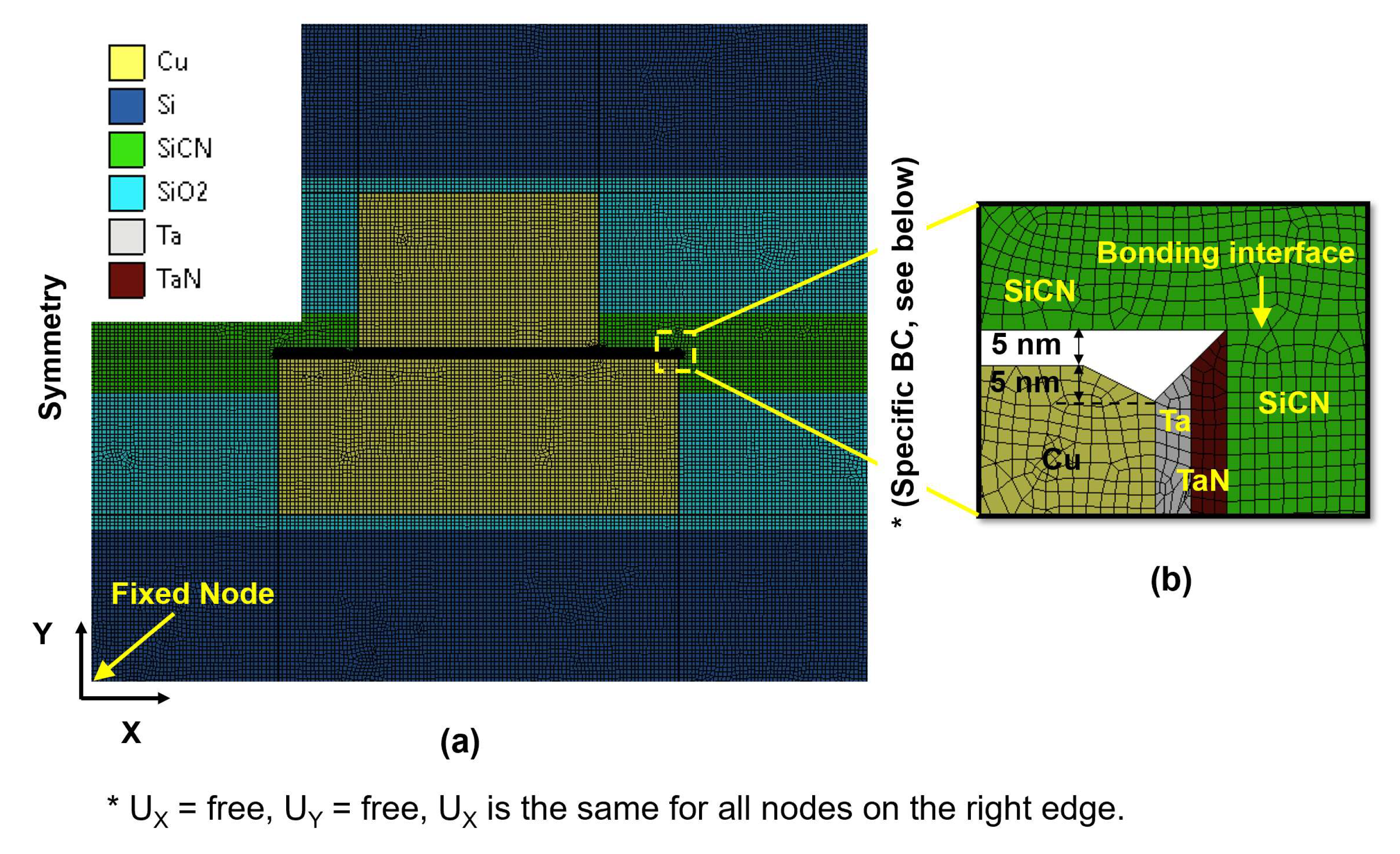

2.2. Numerical Modeling

- Share nodes were used at the boundaries of the Cu/barrier layer surfaces.

- The SiCN-to-SiCN bonds formed before the post-bonding annealing process were considered ‘bonded type’ contact.

- For the Cu-to-Cu interface and SiCN-to-Cu interface, ‘rough type’ contact was applied during the heating period. ‘Bonded type’ contact was applied during the cooling period with a contact radius of 4 Å. In other words, during the heating period, the distance between the Cu (or SiCN) of the top wafer and the Cu (or SiCN) of the bottom wafer smaller than 4 Å was considered to be ‘bonded type’ contact during the cooling period.

3. Results and Discussion

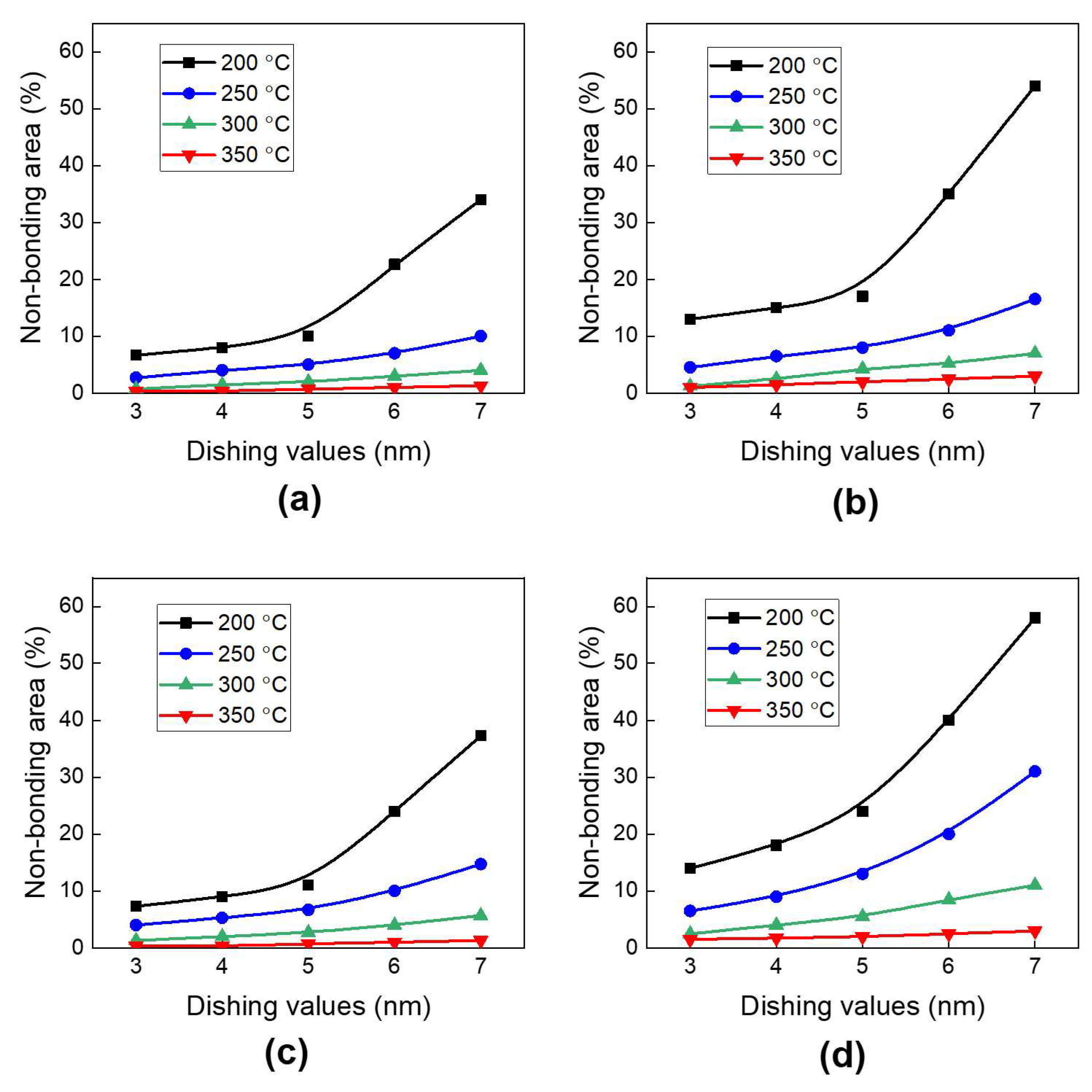

3.1. Analysis of Deformation Behavior and Non-Bonding Area

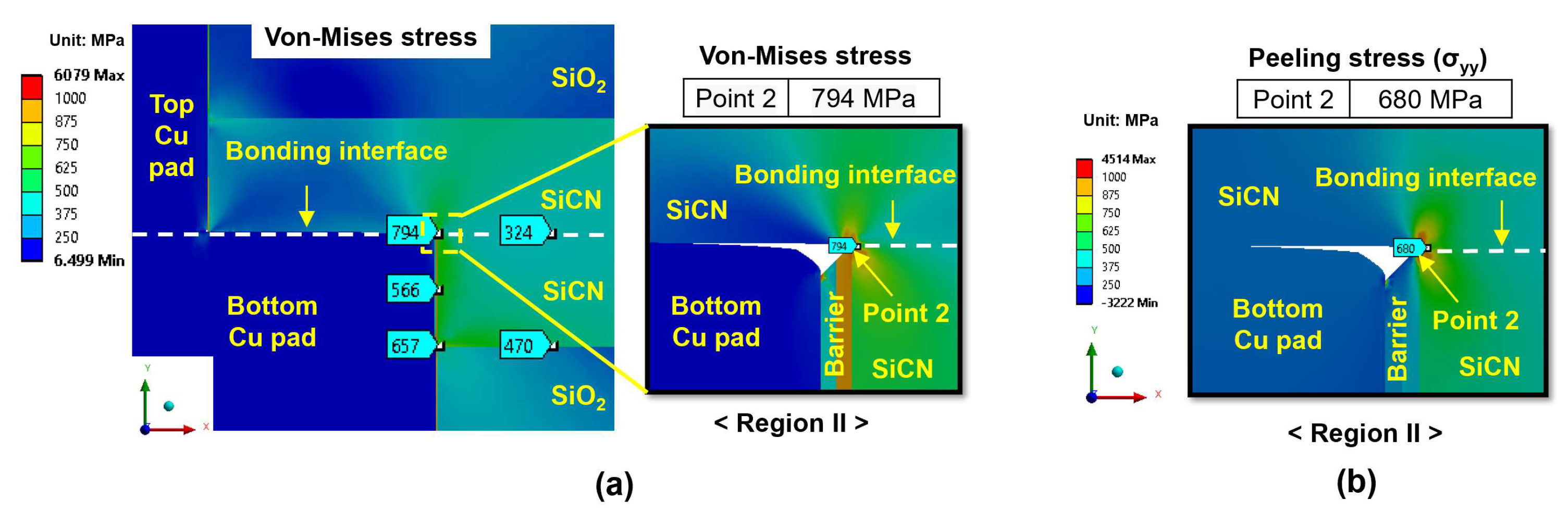

3.2. Analysis of the Effect of Bonding Conditions on Crack Formation

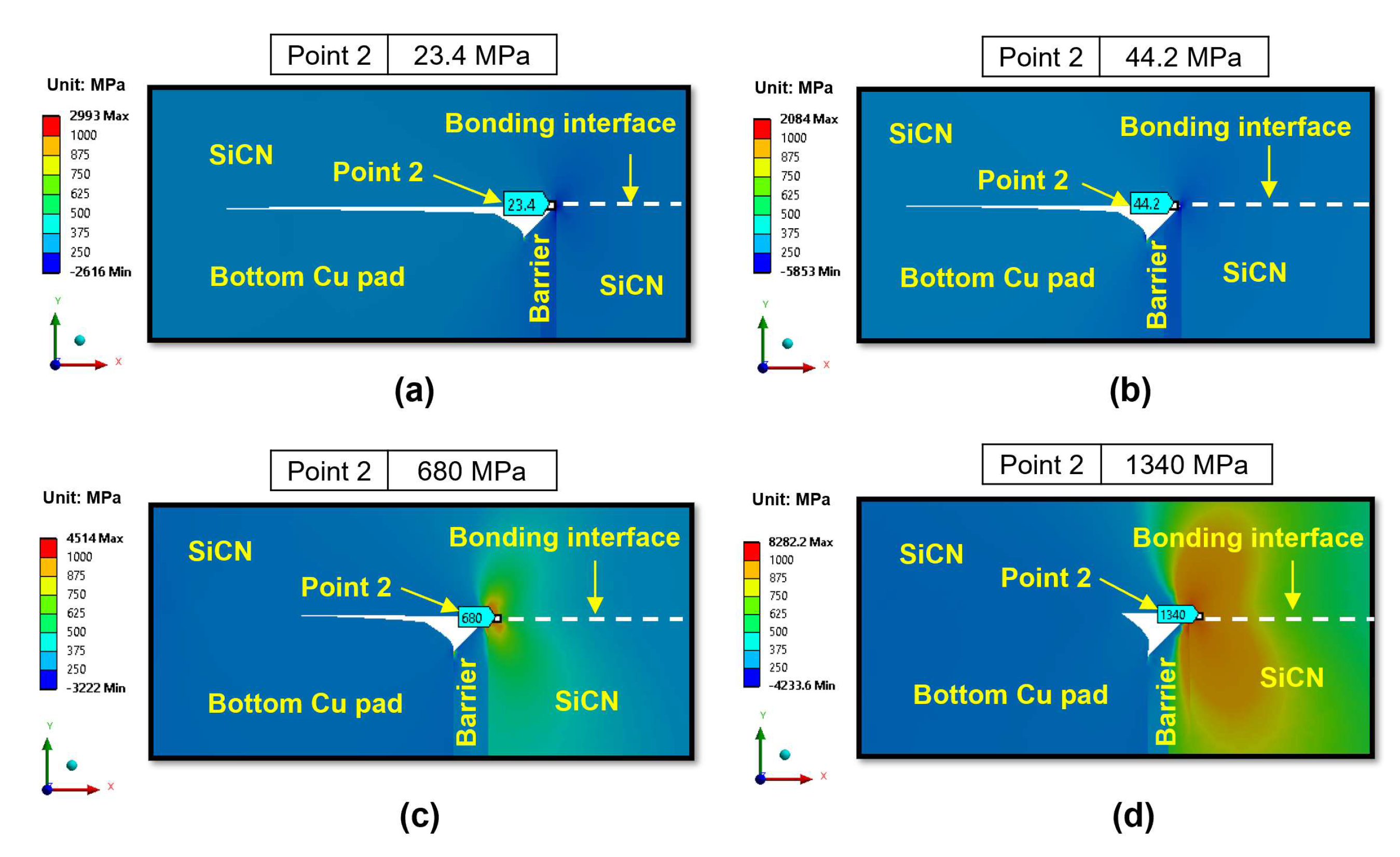

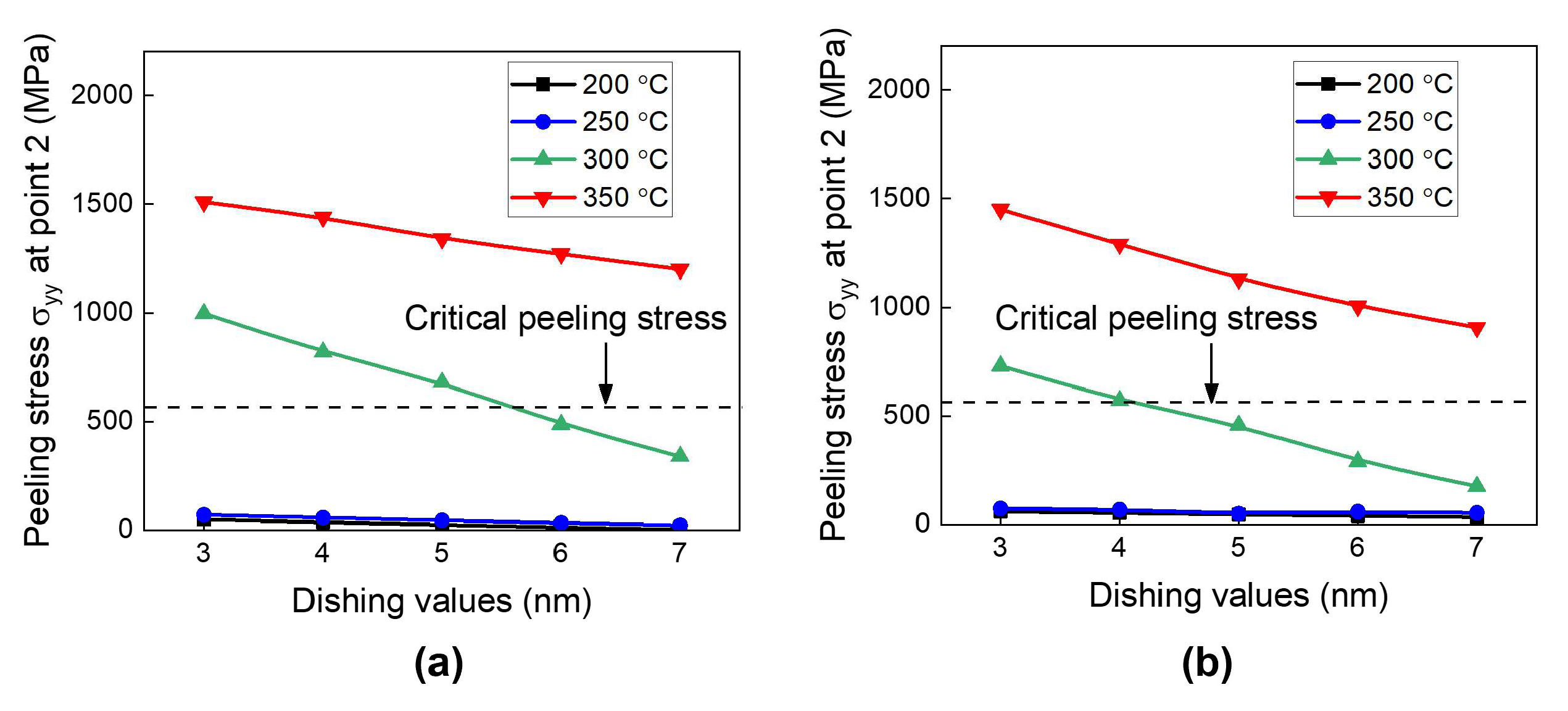

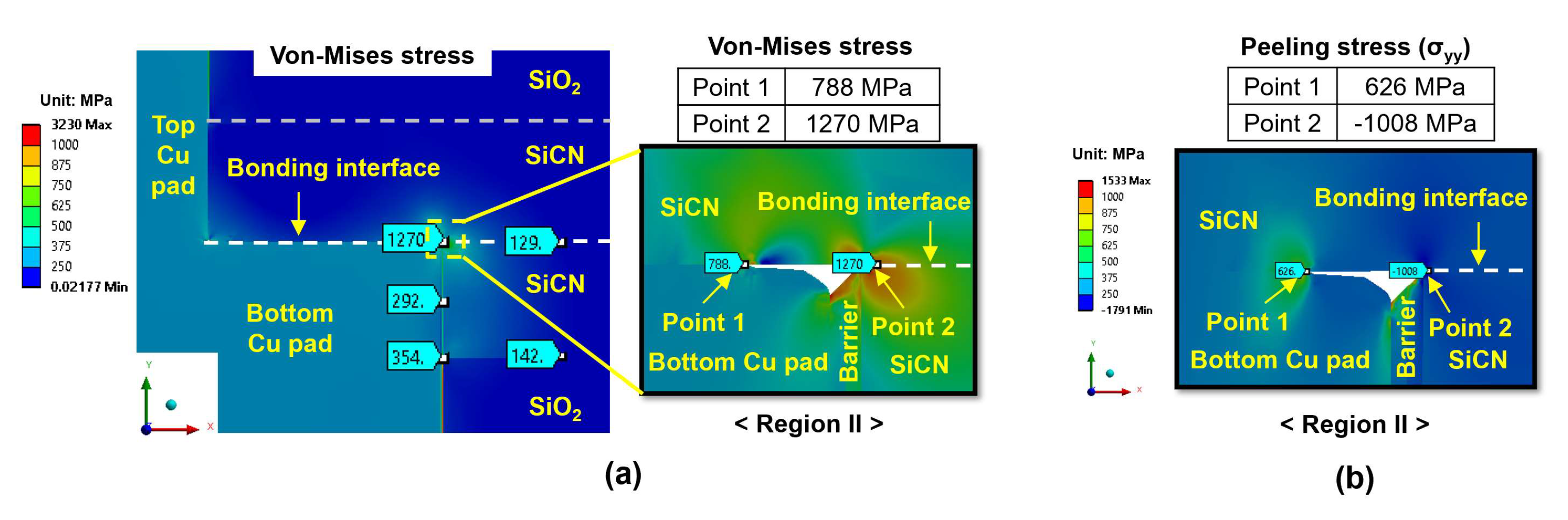

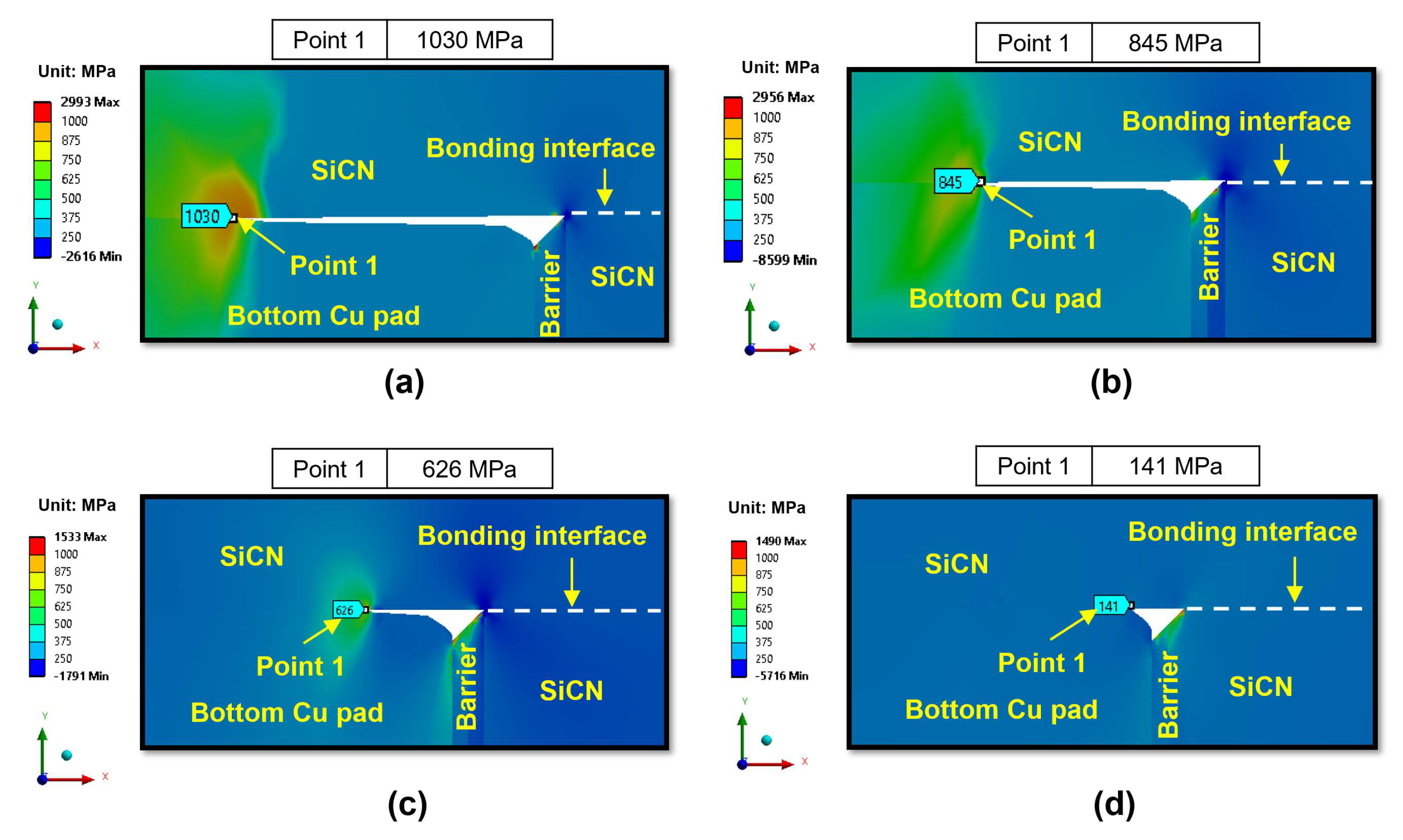

3.2.1. Effect of Bonding Conditions During the Heating Period

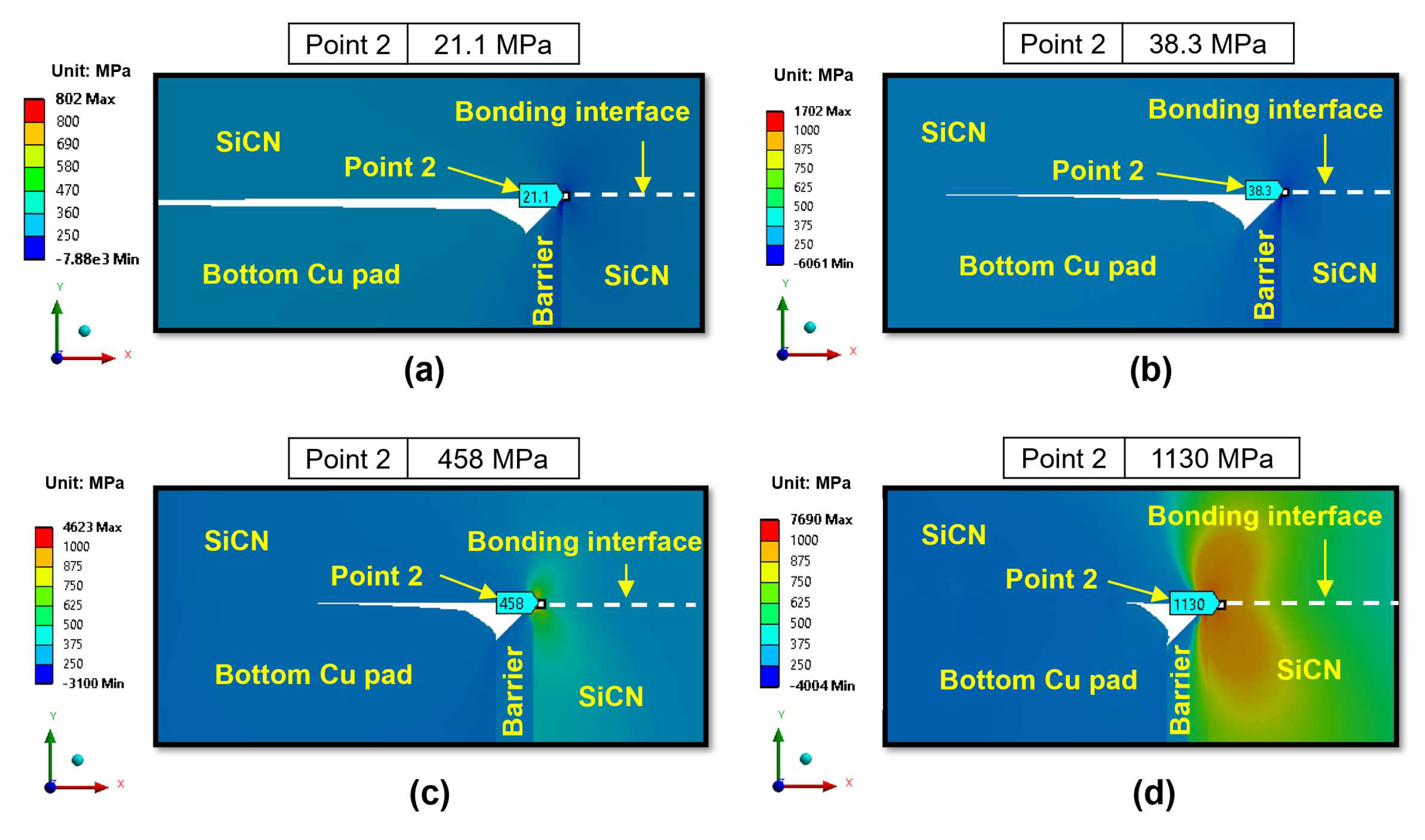

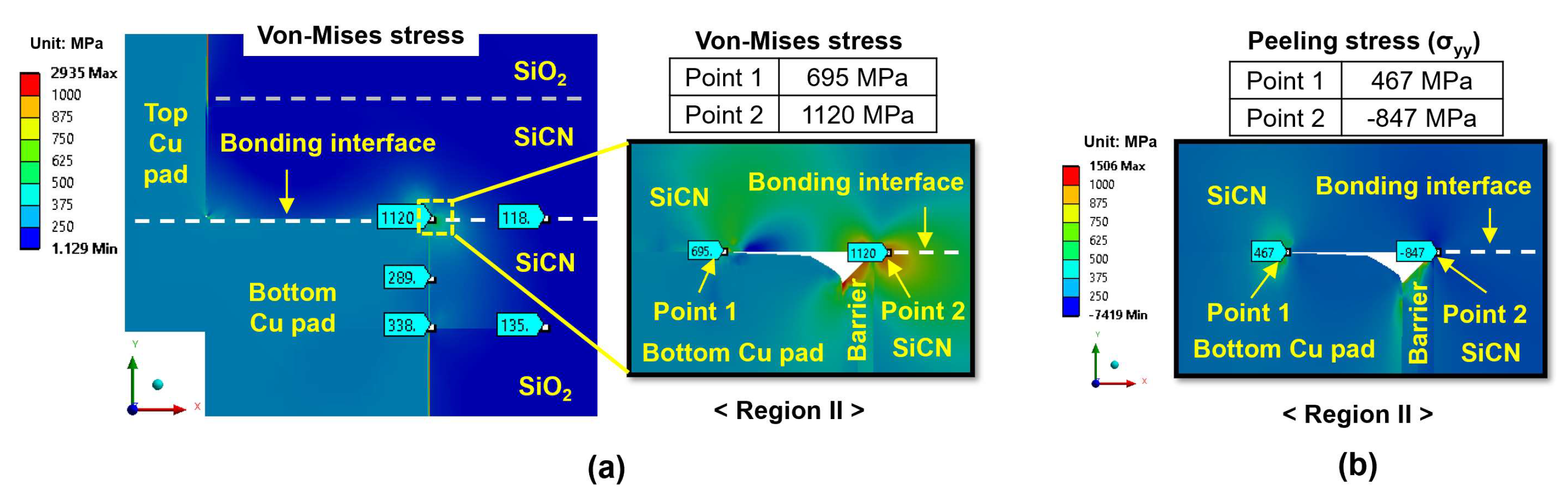

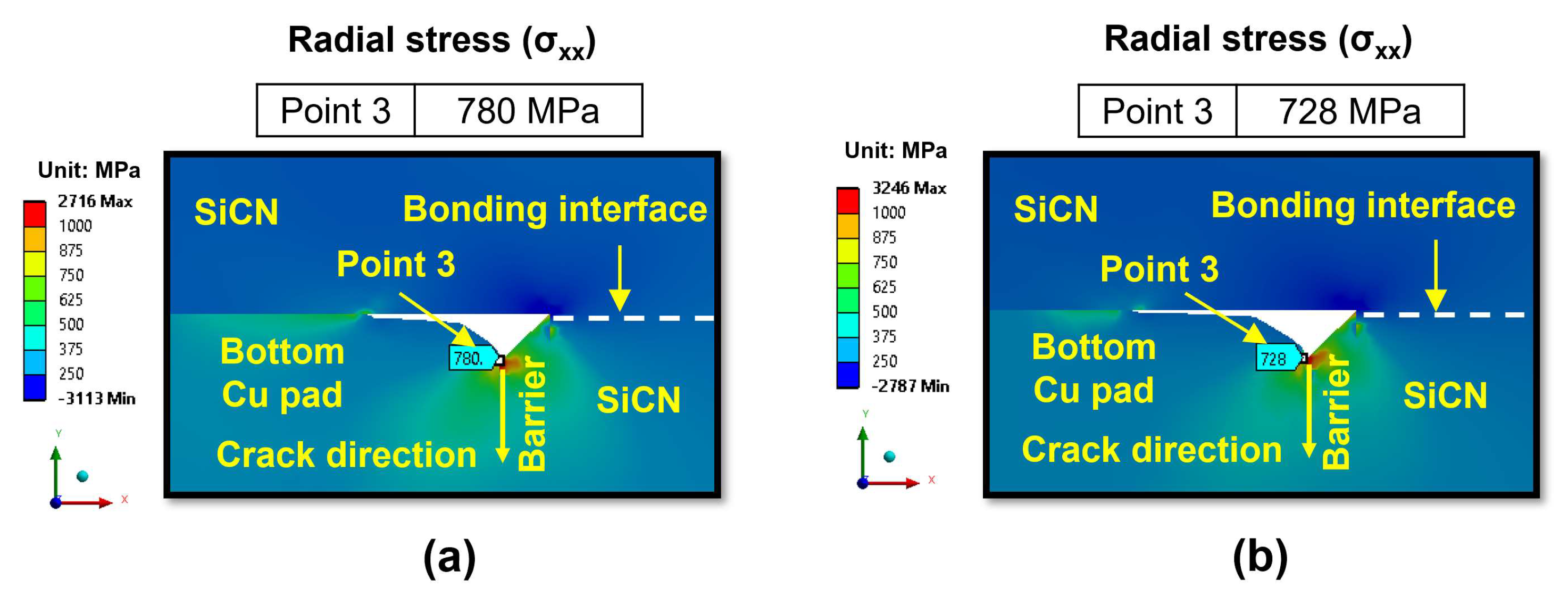

3.2.2. Effect of Bonding Conditions During the Cooling Period

4. Conclusions

- The non-bonding area in the bonding structure increases with a decreasing annealing temperature and an increasing dishing value. To achieve a non-bonding area of less than 10%, the annealing temperature should be greater than 200 °C. When the annealing temperature reaches 300 °C or higher, the non-bonding area will be less than 10% for all dishing values.

- During the heating period, the SiCN-to-SiCN bonding interface is the most vulnerable cracking site with the highest peeling stress. The annealing temperature of 350 °C presents a significant risk of cracking. On the other hand, annealing temperature lower than 250 °C will minimize the risk of cracking. The SiCN-to-SiO2 bonding interface, which has the lowest adhesion energy and a large CTE mismatch, is another possible cracking site.

- During the cooling period, the SiCN-to-Cu bonding interface is the most vulnerable point with the highest stress. Decreasing the annealing temperature or increasing the dishing value will increase the peeling stress. The peeling stress is highest at an annealing temperature of 200 °C. However, the simulated peeling stresses are lower than the adhesion strength of the SiCN-to-Cu interface regardless of the annealing temperatures and dishing values, indicating that the probability of cracking during the cooling process is very low. There is also a possibility of crack formation at the Cu-to-barrier interface in the vertical direction. However, the chance of cracking is expected be very low due to the high adhesion strength between the metal films.

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Yipeng, X.; Yanping, Z.; Yi, Z.; Choonghyun, L.; Minhui, H.; Zongfang, L. A Review of Mechanism and Technology of Hy-brid Bonding. J. Electron. Packag. 2024, 147, 010801. [Google Scholar] [CrossRef]

- Arnaud, L.; Karam, C.; Bresson, N.; Dubarry, C.; Borel, S.; Assous, M.; Mauguen, G.; Fournel, F.; Gottardi, M.; Mourier, T.; et al. Three-dimensional hybrid bonding integration challenges and solutions toward multi-wafer stacking. MRS Commun. 2020, 10, 549–557. [Google Scholar] [CrossRef]

- Lau, J.H. Recent Advances and Trends in Cu-Cu Hybrid Bonding. IEEE Trans. Compon. Packag. Manuf. Technol. 2023, 13, 399–425. [Google Scholar] [CrossRef]

- Khurana, G.; Panchenko, I. Improvement in Wafer-to-Wafer Hybrid Bonding Using Optimized Chemical Mechanical Planarization Process for Cu Dishing. In Proceedings of the 25th Electronics Packaging Technology Conference, EPTC 2023, Singapore, 5–8 December 2023; Institute of Electrical and Electronics Engineers Inc.: Piscataway, NJ, USA, 2023; pp. 373–380. [Google Scholar] [CrossRef]

- Tippabhotla, S.K.; Ji, L.; Han, Y. Numerical Simulation of Cu/Polymer-Dielectric Hybrid Bonding Process using Finite Element Analysis. In Proceedings of the Electronic Components and Technology Conference, San Diego, CA, USA, 31 May–3 June 2022; Institute of Electrical and Electronics Engineers Inc.: Piscataway, NJ, USA, 2022; pp. 1695–1703. [Google Scholar] [CrossRef]

- Lau, J.H.; Zhang, Q.; Li, M.; Yeung, K.M.; Cheung, Y.M.; Fan, N.; Wong, Y.M.; Zahn, M.; Koh, M. Stencil Printing of Underfill for Flip Chips on Organic-Panel and Si-Wafer Substrates. IEEE Trans. Compon Packag. Manuf. Technol. 2015, 7, 1027–1035. [Google Scholar] [CrossRef]

- Ma, K.; Bekiaris, N.; Hsu, C.H.; Xue, L.; Ramaswami, S.; Ding, T.; Probst, G.; Wernicke, T.; Uhrmann, T.; Wimplinger, M. 0.5 μm Pitch Wafer-to-wafer Hybrid Bonding at Low Temperatures with SiCN Bond Layer. In Proceedings of the Electronic Components and Technology Conference, Denver, CO, USA, 28–31 May 2024; Institute of Electrical and Electronics Engineers Inc.: Piscataway, NJ, USA, 2024; pp. 331–336. [Google Scholar] [CrossRef]

- Ma, K.; Bekiaris, N.; Ramaswami, S.; Ding, T.; Probst, G.; Burggraf, J.; Uhrmann, T. 0.5 µm Pitch Wafer-to-wafer Hybrid Bonding with SiCN Bonding Interface for Advanced Memory. In Proceedings of the Electronic Components and Technology Conference, Orlando, FL, USA, 30 May–2 June 2023; Institute of Electrical and Electronics Engineers Inc.: Piscataway, NJ, USA, 2023; pp. 1110–1114. [Google Scholar] [CrossRef]

- Netzband, C.; Ryan, K.; Mimura, Y.; Ilseok, S.; Aizawa, H.; Ip, N.; Chen, X.; Fukushima, H.; Tan, S. 0.5 µm Pitch Next Generation Hybrid Bonding with High Alignment Accuracy for 3D Integration. In Proceedings of the Electronic Components and Technology Conference, Orlando, FL, USA, 30 May–2 June 2023; Institute of Electrical and Electronics Engineers Inc.: Piscataway, NJ, USA, 2023; pp. 1100–1104. [Google Scholar] [CrossRef]

- Chew, S.A.; Iacovo, S.; Fordor, F.; Dewilde, S.; Devriendt, K.; De Vos, J.; Miller, A.; Beyer, G.; Beyne, E. 700nm pitch Cu/SiCN wafer-to-wafer hybrid bonding. In Proceedings of the 24th Electronics Packaging Technology Conference, EPTC 2022, Singapore, 7–9 December 2022; Institute of Electrical and Electronics Engineers Inc.: Piscataway, NJ, USA, 2022; pp. 334–337. [Google Scholar] [CrossRef]

- Inoue, F.; Iacovo, S.; El-Mekki, Z.; Kim, S.W.; Struyf, H.; Beyne, E. Area-Selective Electroless Deposition of Cu for Hy-brid Bonding. IEEE Electron. Device Lett. 2021, 42, 1826–1829. [Google Scholar] [CrossRef]

- Ji, L.; Che, F.X.; Ji, H.M.; Li, H.Y.; Kawano, M. Wafer-to-Wafer Hybrid Bonding Development by Advanced Finite El-ement Modeling for 3-D IC Packages. IEEE Trans. Compon. Packag. Manuf. Technol. 2020, 10, 2106–2117. [Google Scholar] [CrossRef]

- Ji, L.; Che, F.X.; Ji, H.M.; Li, H.Y.; Kawano, M. Bonding integrity enhancement in wafer to wafer fine pitch hybrid bonding by advanced numerical modelling. In Proceedings of the Electronic Components and Technology Conference, Orlando, FL, USA, 3–30 June 2020; Institute of Electrical and Electronics Engineers Inc.: Piscataway, NJ, USA, 2020; pp. 568–575. [Google Scholar] [CrossRef]

- Jourdon, J.; Lhostis, S.; Moreau, S.; Chossat, J.; Arnoux, M.; Sart, C.; Henrion, Y.; Lamontagne, P.; Arnaud, L.; Bresson, N.; et al. Hybrid bonding for 3D stacked image sensors: Impact of pitch shrinkage on interconnect robustness. In Proceedings of the 2018 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 1–5 December 2018; IEEE: Piscataway, NJ, USA, 2018. [Google Scholar] [CrossRef]

- Kim, Y.S.; Nguyen, T.H.; Choa, S.H. Enhancement of the Bond Strength and Reduction of Wafer Edge Voids in Hybrid Bonding. Micromachines 2022, 13, 537. [Google Scholar] [CrossRef]

- Luan, X.; Liu, Y.; Zhang, B.; Wang, S.; Niu, X.; Wang, C.; Wang, J. Investigation of the barrier slurry with better defect performance and facilitating post-CMP cleaning. Microelectron. Eng. 2017, 170, 21–28. [Google Scholar] [CrossRef]

- Fujino, M.; Takahashi, K.; Araga, Y.; Kikuchi, K. 300 mm wafer-level hybrid bonding for Cu/interlayer dielectric bonding in vacuum. Jpn. J. Appl. Phys. 2020, 59, SBBA02. [Google Scholar] [CrossRef]

- Kim, S.W.; Fodor, F.; Heylen, N.; Iacovo, S.; De Vos, J.; Miller, A.; Beyer, G.; Beyne, E. Novel Cu/SiCN surface topography control for 1 μm pitch hybrid wafer-to-wafer bonding. In Proceedings of the Electronic Components and Technology Conference, Orlando, FL, USA, 3–30 June 2020; Institute of Electrical and Electronics Engineers Inc.: Piscataway, NJ, USA, 2020; pp. 216–222. [Google Scholar] [CrossRef]

- Park, J.; Kang, S.; Kim, M.E.; Kim, N.J.; Kim, J.; Kim, S.; Kim, K.M. Advanced Cu/Polymer Hybrid Bonding System for Fine-Pitch 3D Stacking Devices. Adv. Mater. Technol. 2023, 8, 2202134. [Google Scholar] [CrossRef]

- Zhou, A.; Zhang, Y.; Ding, F.; Lian, Z.; Jin, R.; Yang, Y.; Wang, Q.; Cao, L. Research progress of hybrid bonding technology for three-dimensional integration. Microelectron. Reliab. 2024, 155, 115372. [Google Scholar] [CrossRef]

- Assiongbon, K.A.; Emery, S.B.; Gorantla, V.R.K.; Babu, S.V.; Roy, D. Electrochemical impedance characteristics of Ta/Cu contact regions in polishing slurries used for chemical mechanical planarization of Ta and Cu: Considerations of galvanic corrosion. Corros. Sci. 2006, 48, 372–388. [Google Scholar] [CrossRef]

- Maruyama, K.; Shiohara, M.; Yamada, K.; Kondo, S.; Saito, S. Galvanic corrosion control in chemical mechanical polishing of Cu interconnects with ruthenium barrier metal film. Jpn. J. Appl. Phys. 2009, 48, 04C022. [Google Scholar] [CrossRef]

- Tsau, Y.W.; De Messemaeker, J.; Salahouelhadj, A.; Gonzalez, M.; Witters, L.; Zhang, B.; Seefeldt, M.; Beyne, E.; De Wolf, I. Simulation of Cu pad expansion in wafer-to-wafer Cu/SiCN hybrid bonding. Microelectron. Reliab. 2022, 138, 114716. [Google Scholar] [CrossRef]

- Ji, H.M.; Ji, L.; Che, F.X.; Li, H.Y.; Chui, K.J.; Kawano, M. Wafer Level High Density Hybrid Bonding for High Performance Computing. In Proceedings of the International Symposium on the Physical and Failure Analysis of Integrated Circuits, IPFA, Suzhou, China, 15–19 July 2013; Institute of Electrical and Electronics Engineers Inc.: Piscataway, NJ, USA, 2020. [Google Scholar] [CrossRef]

- Tippabhotla, S.K.; Ji, L.; Choong, C.S. Evaluation of C2W hybrid bonding performance with SiO2/SiCN passivation layers at the interface using finite element simulations. In Proceedings of the 25th Electronics Packaging Technology Conference, EPTC 2023, Singapore, 5–8 December 2023; Institute of Electrical and Electronics Engineers Inc.: Piscataway, NJ, USA, 2023; pp. 1053–1058. [Google Scholar] [CrossRef]

- Ou, J.C.; Tsai, Y.Y.; Lin, T.C.; Kao, C.L.; Hsiao, S.C.; Huang, F.Y.; Kuo, J.C. Thermal stability and bonding interface in Cu/SiO2 hybrid bonding on nano-Twinned copper. AIP Adv. 2022, 12, 065201. [Google Scholar] [CrossRef]

- Sherwood, T.; Patlolla, R.; Salfelder, J.; Kasbauer, T.; Sreenivasan, R.; Li, K.; Ley, R.; Probst, G.; Appell, J.; Ahn, K.C.; et al. Aggressive Pitch Scaling (sub-0.5 µm) of W2W Hybrid Bonding Through Process Innovations. In Proceedings of the Electronic Components and Technology Conference, Singapore, 5–8 December 2023; Institute of Electrical and Electronics Engineers Inc.: Piscataway, NJ, USA, 2023; pp. 13–18. [Google Scholar] [CrossRef]

- Brun, X.F.; Hasan, M.M.; Yang, Y.; Carazzetti, P.; Drechsel, C.; Strolz, E. Characterization of 300 mm Low Temperature SiCN PVD Films for Hybrid Bonding application. In Proceedings of the Electronic Components and Technology Conference, Singapore, 5–8 December 2023; Institute of Electrical and Electronics Engineers Inc.: Piscataway, NJ, USA, 2023; pp. 548–555. [Google Scholar] [CrossRef]

- Inoue, F.; Peng, L.; Iacovo, S.; Phommahaxay, A.; Verdonck, P.; Meersschaut, J.; Dara, P.; Sleeckx, E.; Miller, A.; Beyer, G.; et al. Influence of Composition of SiCN as Interfacial Layer on Plasma Activated Direct Bonding. ECS J. Solid. State Sci. Technol. 2019, 8, 346–350. [Google Scholar] [CrossRef]

- Beyne, E.; Kim, S.W.; Peng, L.; Heylen, N.; De Messemaeker, J.; Okudur, O.O.; Phommahaxay, A.; Kim, T.G.; Stucchi, M.; Velenis, D.; et al. Scalable, sub 2μm pitch, Cu/SiCN to Cu/SiCN hybrid wafer-to-wafer bonding technology. In Proceedings of the 2017 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2–6 December 2017; IEEE: Piscataway, NJ, USA, 2017. [Google Scholar] [CrossRef]

- Park, A.Y.; Chaparala, S.C.; Park, S.B. Risk assessment of the crack propagation and delamination of the Cu-to-Cu direct bonded (CuDB) interface. Microelectron. Reliab. 2016, 66, 113–121. [Google Scholar] [CrossRef]

- Le, X.B.; Choa, S.H. A comprehensive numerical analysis for preventing cracks in 2.5D glass interposer. J. Mech. Sci. Technol. 2024, 38, 3027–3037. [Google Scholar] [CrossRef]

- Mukhopadhyay, P.; Wenzel, L.; Rudolph, C.; Tuchman, A.; Ryan, K.; Gildea, A.; Nichols, C.; Allgair, J.; Arkalgud, S.; deVilliers, A.; et al. Annealing Effects in Sub-8 μm Pitch Die-to-Wafer Hybrid Bonding. In Proceedings of the Electronic Components and Technology Conference, Denver, CO, USA, 28–31 May 2024; Institute of Electrical and Electronics Engineers Inc.: Piscataway, NJ, USA, 2024; pp. 1923–1928. [Google Scholar] [CrossRef]

- Wenzel, L.; Rudolph, C.; Shehzad, A.; Mukhopadhyay, P.; Fulford, H.J.; Junghaehnel, M.; Panchenko, J. Influence of Heat Treatment on the Quality of Die-to-Wafer Hybrid Bond Interconnects. In Proceedings of the Electronic Components and Technology Conference, Denver, CO, USA, 28–31 May 2024; Institute of Electrical and Electronics Engineers Inc.: Piscataway, NJ, USA, 2024; pp. 1830–1836. [Google Scholar] [CrossRef]

- Ji, H.M.; Chen, G.G.; Chui, K.J. Cu CMP Dishing Control for Fine Pitch Wafer-to-Wafer (W2W) Hybrid Bonding. In Proceedings of the 24th Electronics Packaging Technology Conference, EPTC 2022, Singapore, 7–9 December 2022; Institute of Electrical and Electronics Engineers Inc.: Piscataway, NJ, USA, 2022; pp. 951–954. [Google Scholar] [CrossRef]

- Kumar, M.D.; Sekhar, V.N.; Choong, C.S.; Rao, B.S.S.C.; Chui, K.J.; Rao, V.S. Evaluation of Low Tem-perature Inorganic Dielectric Materials for Hybrid Bonding Applications. In Proceedings of the 25th Electronics Packaging Technology Conference, EPTC 2023, Singapore, 5–8 December 2023; Institute of Electrical and Electronics Engineers Inc.: Piscataway, NJ, USA, 2023; pp. 354–358. [Google Scholar] [CrossRef]

- Heryanto, A.; Putra, W.N.; Trigg, A.; Gao, S.; Kwon, W.S.; Che, F.X.; Ang, X.F.; Wei, J.; IMade, R.; Gan, C.L.; et al. Effect of copper TSV annealing on via protrusion for TSV wafer fabrication. J. Electron. Mater. 2012, 41, 2533–2542. [Google Scholar] [CrossRef]

- Li, G.; Thomas, B.G.; Stubbins, J.F. Modeling creep and fatigue of copper alloys. Metall. Mater. Trans. A 2000, 31, 2491–2502. [Google Scholar] [CrossRef]

- Jung, H.S.; Jang, Y.J.; Choa, S.H.; Jung, J.P. Lower protrusion of a Copper-Nickel Alloy in a through-silicon via and its numerical simulation. Mater. Trans. 2015, 56, 2034–2041. [Google Scholar] [CrossRef]

- Wang, S.; Liu, T.; Dong, F.; Sun, Y.; Xue, L.; Li, R.; Han, X.; Tian, Z.; Liu, S. Surface action mechanism and design considerations for the mechanical integrity of cu/low K BEOL inter-connect during chemical mechanical polishing process. Microelectron. Reliab. 2022, 134, 114565. [Google Scholar] [CrossRef]

- Wlanis, T.; Hammer, R.; Ecker, W.; Lhostis, S.; Sart, C.; Gallois-Garreignot, S.; Rebhan, B.; Maier, G.A. Cu-SiO2 hybrid bonding simulation including surface roughness and viscoplastic material modeling: A critical comparison of 2D and 3D modeling approach. Microelectron. Reliab. 2018, 86, 1–9. [Google Scholar] [CrossRef]

- Yang, Y.; Liao, N.; Zhang, M.; Li, F. Numerical investigation on the bond strength of a SiCN-based multi-layer coating system. J. Alloys Compd. 2017, 710, 468–471. [Google Scholar] [CrossRef]

- Raj, R. Developing an Ab-Initio Human-Machine Interface for an Ultrahigh Temperature MEMS Sensor made from a Novel Polymer Derived Ceramic. In Proceedings of the 9th AIAA/ISSMO Symposium on Multidisciplinary Analysis and Optimization, Atlanta, Georgia, 4–6 September 2002. [Google Scholar] [CrossRef]

- Lau, J.H. Recent Advances and Trends in Advanced Packaging. IEEE Trans. Compon. Packag. Manuf. Technol. 2022, 12, 228–252. [Google Scholar] [CrossRef]

- Lu, M.C. Hybrid Bonding for Ultra-High-Density Interconnect. J. Electron. Packag. 2024, 146, 030802. [Google Scholar] [CrossRef]

- Inoue, F.; Nagata, A.; Fuse, J.; Ebiko, S.; Sato, R.; Saito, K.; Kondo, Y.; Kawauchi, T.; Park, J.; Ahn, C.; et al. Low Temperature Wafer Level Hybrid Bonding Enabled by Advanced SiCN and Surface Activation. In Proceedings of the Electronic Components and Technology Conference, Denver, CO, USA, 28–31 May 2024; Institute of Electrical and Electronics Engineers Inc.: Piscataway, NJ, USA, 2024; pp. 69–75. [Google Scholar] [CrossRef]

- Iacovo, S.; Phommahaxay, A.; Inoue, F.; Verdonck, P.; Kim, S.W.; Sleeckx, E.; Miller, A.; Beyer, G.; Beyne, E. Direct Bonding of low Temperature Heterogeneous Dielectrics. In Proceedings of the Electronic Components and Technology Conference, Las Vegas, NV, USA, 28–31 May 2019; Institute of Electrical and Electronics Engineers Inc.: Piscataway, NJ, USA, 2019; pp. 2206–2212. [Google Scholar] [CrossRef]

- Chang, S.-Y.; Lee, Y.-S.; Lu, C.-L. Effect of Plasma Treatments on the Interface Chemistry and Adhesion Strength Be-tween Cu Metallization and SiCN Etch Stop Layer. J. Electrochem. Soc. 2007, 154, D241. [Google Scholar] [CrossRef]

- Chang, S.Y.; Lee, Y.S. Analyses of interface adhesion between Cu and SiCN etch stop layers by nanoindentation and nanoscratch tests. Jpn. J. Appl. Phys. 2007, 46, 1955–1960. [Google Scholar] [CrossRef]

- Che, F.X.; Putra, W.N.; Heryanto, A.; Trigg, A.; Zhang, X.; Gan, C.L. Study on Cu protrusion of through-silicon via. IEEE Trans. Compon. Packag. Manuf. Technol. 2013, 3, 732–739. [Google Scholar] [CrossRef]

- Wang, H.; Chen, H.; Xiang, J.; Yang, X. Research on simulation of Cu/SiO2 hybrid bonding process and interface failure mechanism by Finite Element Analysis. In Proceedings of the 2023 24th International Conference on Electronic Packaging Technology, ICEPT 2023, Shihezi, China, 8–11 August 2023; Institute of Electrical and Electronics Engineers Inc.: Piscataway, NJ, USA, 2023. [Google Scholar] [CrossRef]

- Janakiraman, N.; Burghard, Z.; Aldinger, F. Fracture toughness evaluation of precursor-derived Si-C-N ceramics using the crack opening displacement approach. J. Non Cryst. Solids 2009, 355, 2102–2113. [Google Scholar] [CrossRef]

- Zehnder, A.T. Fracture Mechanics; Springer Science & Business Media: Berlin, Germany, 2012; Volume 62. [Google Scholar]

- Anderson, T.L. Fracture Mechanics: Fundamentals and Applications; CRC Press: Boca Raton, FL, USA, 2005. [Google Scholar]

| Design Parameters | Values |

|---|---|

| Dishing values | 3~7 nm |

| Top Cu pad diameter of type A structure | 3 μm |

| Bottom Cu pad diameter of type A structure | 5 μm |

| Cu pads diameter of type B structure | 4 μm |

| Cu pad thickness | 2 μm |

| SiCN thickness | 0.5 μm |

| SiO2 thickness | 1.7 μm |

| Si thickness | 20 μm |

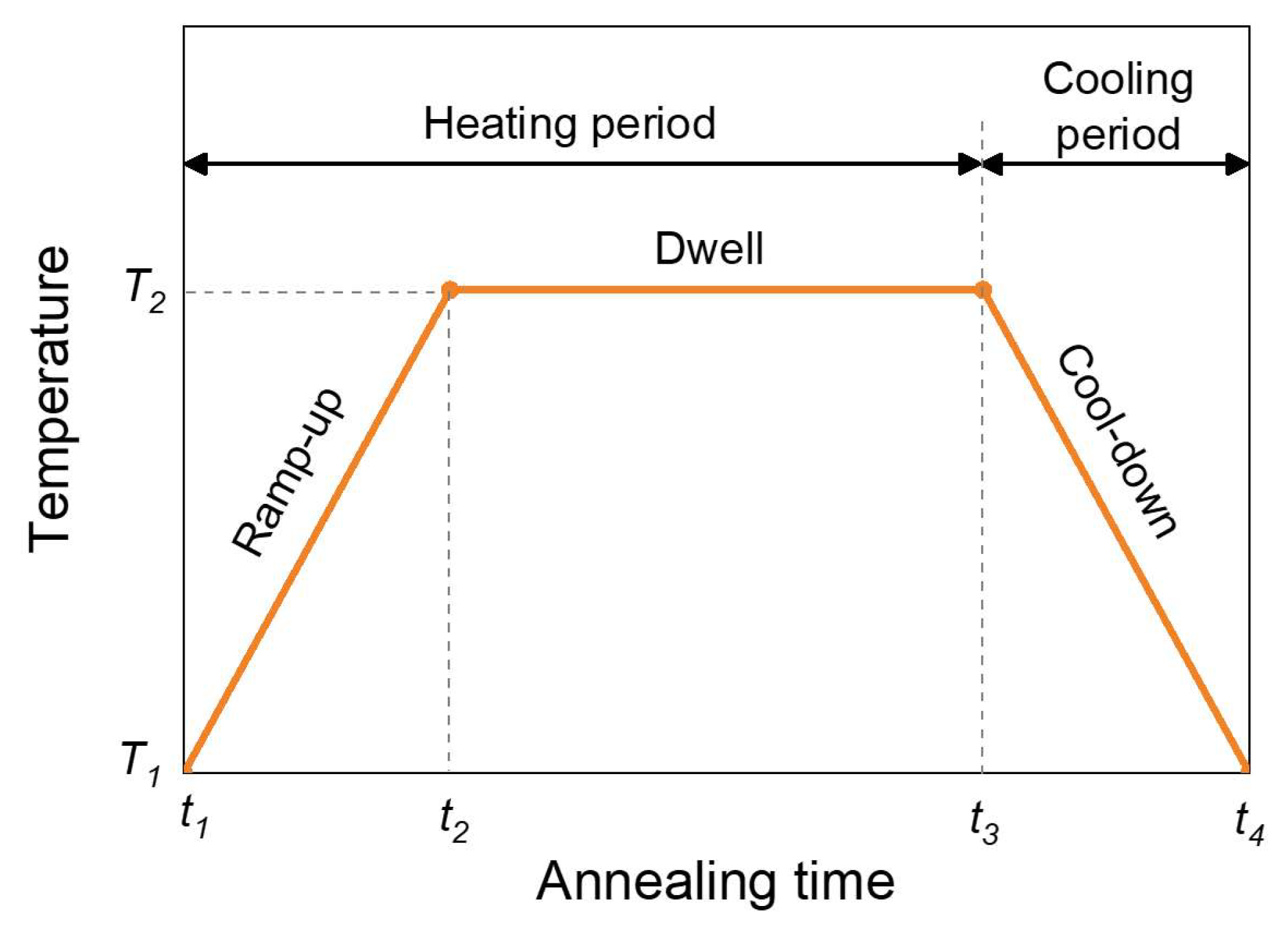

| Annealing Parameters | Values |

|---|---|

| Initial/end temperature T1 | 25 °C |

| Annealing temperature T2 | 200, 250, 300, 350 °C |

| Ramp-up/cool-down duration | 0.5 h |

| Annealing dwell duration | 1 h |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Le, X.-B.; Choa, S.-H. Assessment of the Risk of Crack Formation at a Hybrid Bonding Interface Using Numerical Analysis. Micromachines 2024, 15, 1332. https://doi.org/10.3390/mi15111332

Le X-B, Choa S-H. Assessment of the Risk of Crack Formation at a Hybrid Bonding Interface Using Numerical Analysis. Micromachines. 2024; 15(11):1332. https://doi.org/10.3390/mi15111332

Chicago/Turabian StyleLe, Xuan-Bach, and Sung-Hoon Choa. 2024. "Assessment of the Risk of Crack Formation at a Hybrid Bonding Interface Using Numerical Analysis" Micromachines 15, no. 11: 1332. https://doi.org/10.3390/mi15111332

APA StyleLe, X.-B., & Choa, S.-H. (2024). Assessment of the Risk of Crack Formation at a Hybrid Bonding Interface Using Numerical Analysis. Micromachines, 15(11), 1332. https://doi.org/10.3390/mi15111332