750 V Breakdown in GaN Buffer on 200 mm SOI Substrates Using Reverse-Stepped Superlattice Layers

Abstract

1. Introduction

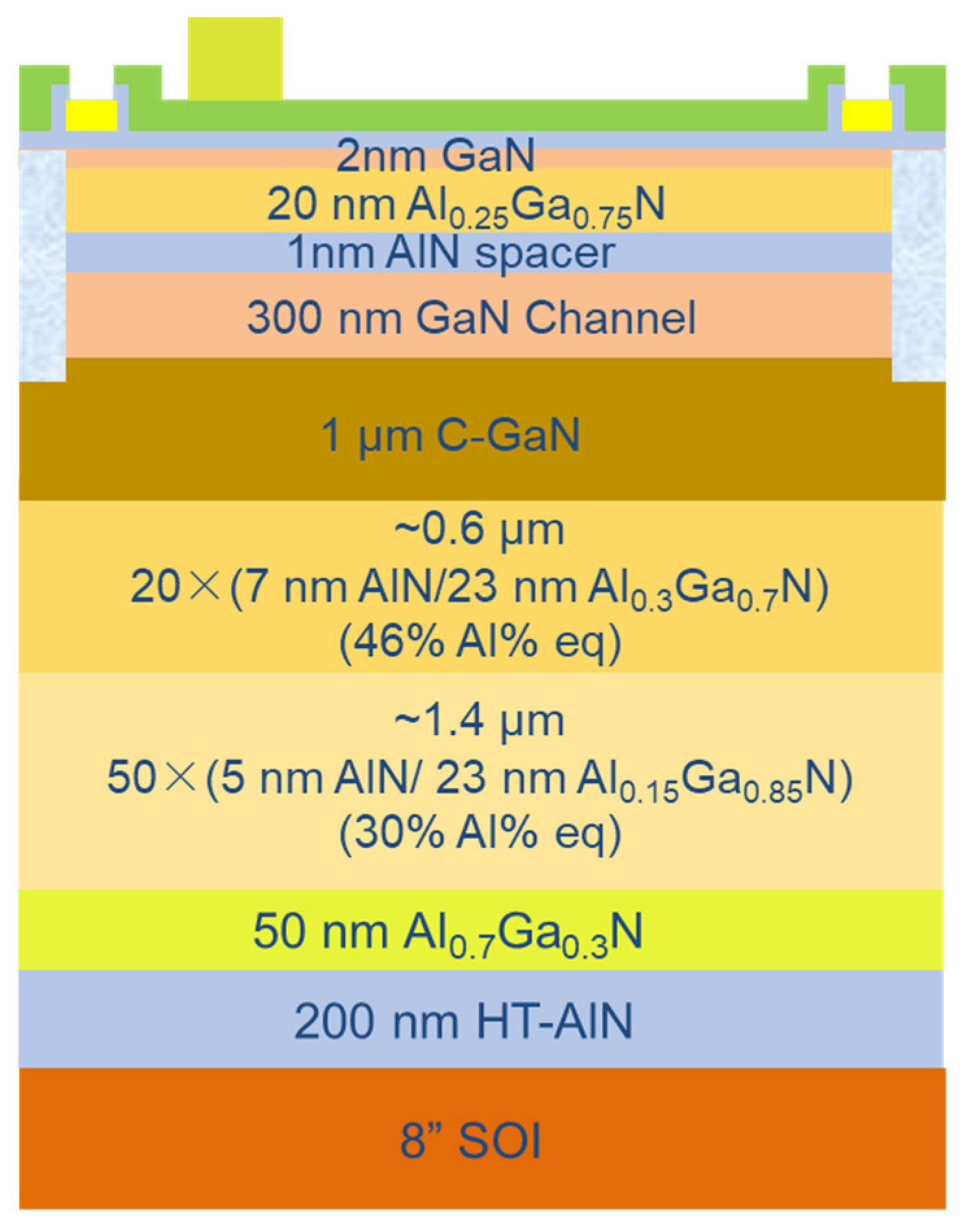

2. Epitaxy and Device Fabrication

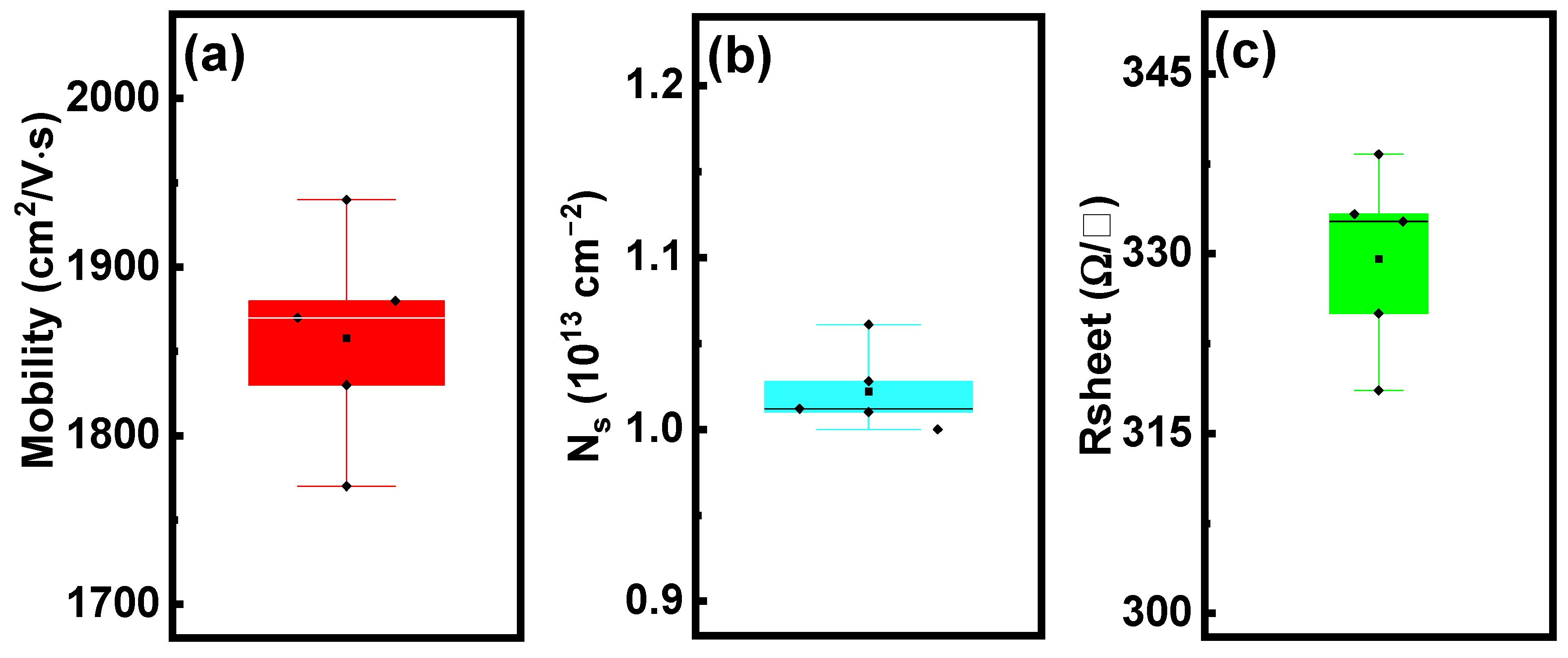

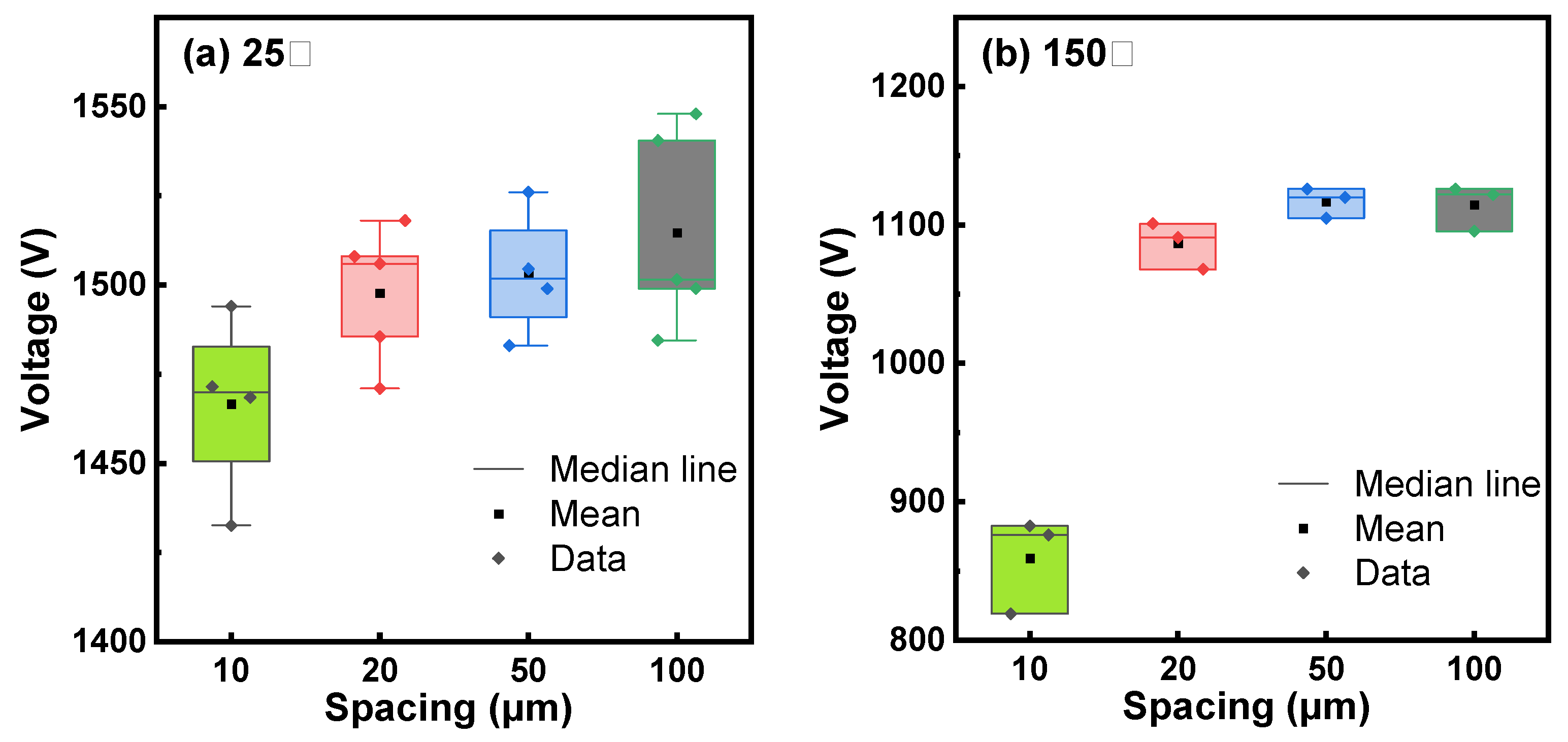

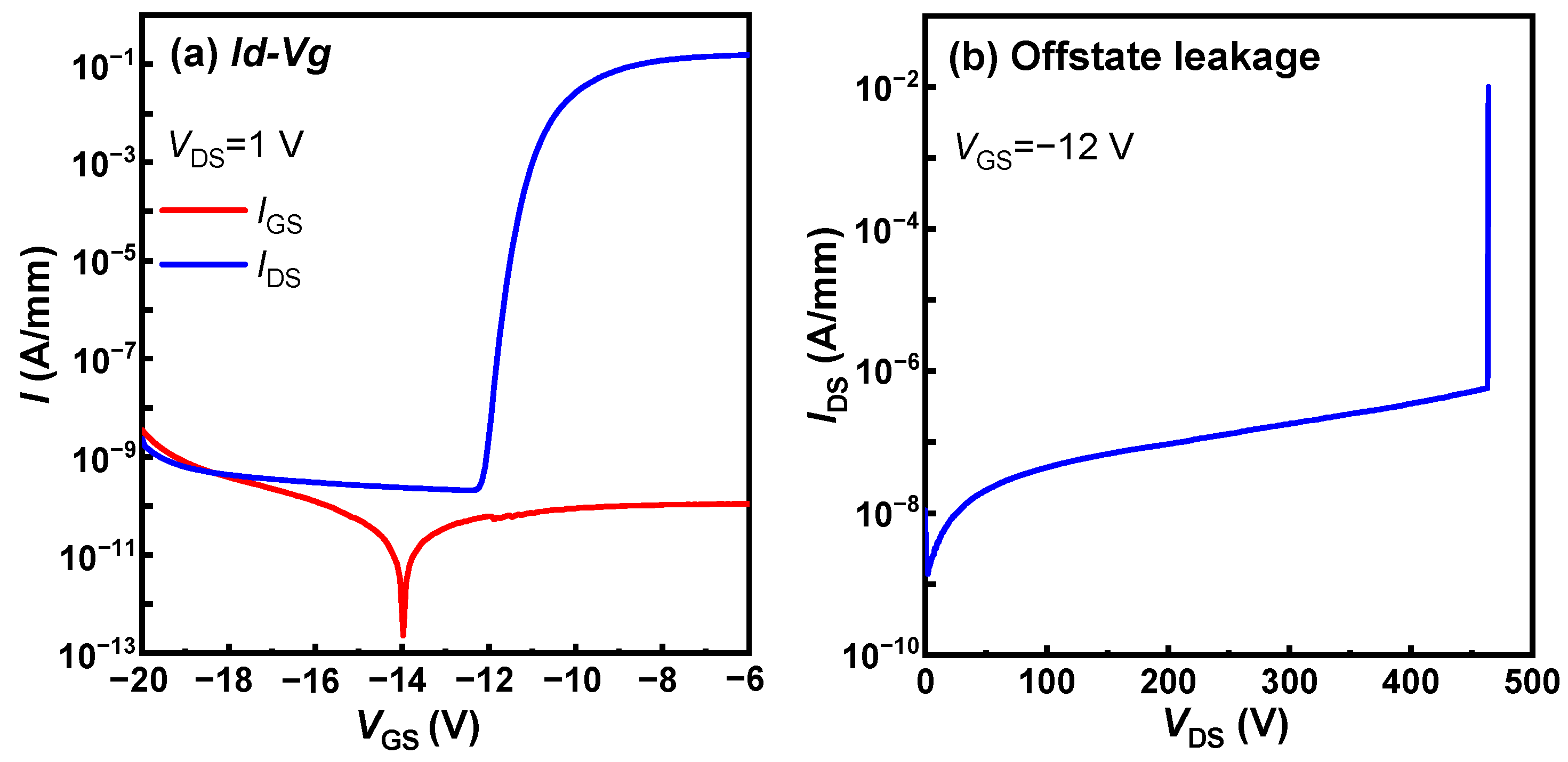

3. Results and Discussion

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Ma, C.-T.; Gu, Z.-H. Review of GaN HEMT Applications in Power Converters over 500 W. Electronics 2019, 8, 1401. [Google Scholar] [CrossRef]

- Flack, T.; Pushpakaran, B.; Bayne, S. GaN Technology for Power Electronic Applications: A Review. J. Electron. Mater. 2016, 45, 2673–2682. [Google Scholar] [CrossRef]

- Sun, R.; Lai, J.; Chen, W.; Zhang, B. GaN Power Integration for High Frequency and High Efficiency Power Applications: A Review. IEEE Access 2020, 8, 15529–15542. [Google Scholar] [CrossRef]

- Li, S.; Ercan, B.; Ren, C.; Ikeda, H.; Chowdhury, S. A Study on the Impact of Dislocation Density on Leakage Current in Vertical GaN-on-GaN p-n Diodes. IEEE Trans. Electron Devices 2022, 69, 4206–4211. [Google Scholar] [CrossRef]

- Lee, K.; So, B.; Lee, K.; Heo, C.; Ko, K.; Jang, J.; Nam, O. GaN Growth on SiC (0001) Substrates by Metal-Organic Chemical Vapor Deposition. J. Nanosci. Nanotechnol. 2016, 16, 11802–11806. [Google Scholar] [CrossRef]

- Li, X.; Zhao, M.; Bakeroot, B.; Geens, K.; Guo, W.; You, S.; Stoffels, S.; Lempinen, V.; Sormunen, J.; Groeseneken, G.; et al. Buffer Vertical Leakage Mechanism and Reliability of 200-mm GaN-on-SOI. IEEE Trans. Electron Devices 2019, 66, 553–560. [Google Scholar] [CrossRef]

- Li, X.; Hove, M.V.; Zhao, M.; Geens, K.; Lempinen, V.; Sormunen, J.; Groeseneken, G.; Decoutere, S. 200 V Enhancement-Mode p-GaN HEMTs Fabricated on 200 mm GaN-on-SOI With Trench Isolation for Monolithic Integration. IEEE Electron Device Lett. 2017, 38, 918–921. [Google Scholar] [CrossRef]

- Weiss, B.; Reiner, R.; Polyakov, V.; Waltereit, P.; Ouay, R.; Ambacher, O.; Maksimovic, D. Substrate biasing effects in a high-voltage, monolithically-integrated half bridge GaN-Chip. In Proceedings of the IEEE Workshop Wide Bandgap Power Devices Appl. (WiPDA), Albuquerque, NM, USA, 30 October–1 November 2017; pp. 265–272. [Google Scholar] [CrossRef]

- Luna, L.E.; Anderson, T.J.; Koehler, A.D.; Tadjer, M.J.; Aktaş, Ö.; Hobart, K.D.; Kub, F.J. Vertical and Lateral GaN Power Devices Enabled by Engineered GaN Substrates. ECS Trans. 2018, 86, 3. [Google Scholar] [CrossRef]

- Huang, C.; Chiu, H.; Liu, C.; Wang, H.; Kao, H.; Chen, C.; Chang, K. Characteristic Analysis of AlGaN/GaN HEMT with Composited Buffer Layer on High-Heat Dissipation Poly-AlN Substrates. Membranes 2021, 11, 848. [Google Scholar] [CrossRef]

- Hsu, L.H.; Lai, Y.Y.; Tu, P.T.; Langpoklakpam, C.; Chang, Y.T.; Huang, Y.W.; Lee, W.C.; Tzou, A.J.; Cheng, Y.J.; Lin, C.H.; et al. Development of GaN HEMTs Fabricated on Silicon, Silicon-on-Insulator, and Engineered Substrates and the Heterogeneous Integration. Micromachines 2021, 12, 1159. [Google Scholar] [CrossRef]

- Basceri, C.; Odnoblyudov, V.; Aktas, O.; Wohlmuth, W.; Geens, K.; Vohra, A.; Bakeroot, B.; Hahn, H.; Fahle, D.; Heuken, M.; et al. Propelling the Power Electronics Revolution: 200 mm Diameter 100 V to 1800 V and Beyond GaN-on-QST High Volume Device Manufacturing Platform. In Proceedings of the CS MANTECH Conference, Monterey, CA, USA, 9–12 May 2022; Available online: https://csmantech.org/wp-content/uploads/2022/03/13.2.2022-Propelling-the-Power-Electronics-Revolution.pdf (accessed on 23 May 2024).

- Mohd-Yusuf, Y.; Samsudin, M.E.A.; Taib, M.I.M.; Ahmad, M.A.; Mohamed, M.F.P.; Kawarada, H.; Falina, S.; Zainal, N.; Syamsul, M. Two-Step GaN Layer Growth for High-Voltage Lateral AlGaN/GaN HEMT. Crystals 2023, 13, 90. [Google Scholar] [CrossRef]

- Zhang, H.; Sun, Y.; Song, K.I.; Xing, C.; Yang, L.; Wang, D.; Yu, H.; Xiang, X.; Gao, N.; Xu, G.; et al. Demonstration of AlGaN/GaN HEMTs on vicinal sapphire substrates with large misoriented angles. Appl. Phys. Lett. 2021, 119, 072104. [Google Scholar] [CrossRef]

- Shao, Y.; Hu, H.; Zhang, B.; Hao, X.; Wu, Y. Crystallographic Orientation and Strain in GaN Crystals Grown on 6H-SiC and Sapphire Substrates. Crystals 2023, 13, 1694. [Google Scholar] [CrossRef]

- Cao, J.; Pavlidis, D.; Park, Y.; Singh, J.; Eisenbach, A. Improved quality GaN by growth on compliant silicon-on-insulator substrates using metalorganic chemical vapor deposition. J. Appl. Phys. 1998, 83, 3829–3834. [Google Scholar] [CrossRef]

- Simoen, E.; Zhang, W.; Zhang, J.; Claeys, C.; Zhao, M. Defect Assessment in AlN Nucleation Layers Grown on Silicon and Silicon-on-Insulator Substrates. In Proceedings of the 2019 China Semiconductor Technology International Conference (CSTIC), Shanghai, China, 18–19 March 2019; IEEE: Piscataway, NJ, USA, 2019; pp. 1–4. [Google Scholar] [CrossRef]

- Kong, W.; Jiao, W.; Li, J.C.; Collar, K.; Kim, T.H.; Leach, J.H.; Brown, A.S. Effect of strain in sputtered AlN buffer layers on the growth of GaN by molecular beam epitaxy. Appl. Phys. Lett. 2015, 107, 032102. [Google Scholar] [CrossRef]

- Yang, Y.; Xiang, P.; Liu, M.; Chen, W.; He, Z.; Han, X.; Ni, Y.; Yang, F.; Yao, Y.; Wu, Z.; et al. Effect of compositionally graded AlGaN buffer layer grown by different functions of trimethylaluminum flow rates on the properties of GaN on Si (111) substrates. J. Cryst. Growth 2013, 376, 23–27. [Google Scholar] [CrossRef]

- Dalapati, P.; Urata, S.; Egawa, T. Investigation of AlGaN/GaN high electron mobility transistors on Silicon (111) substrates employing multi-stacked strained layer superlattice structures. Superlattices Microstruct. 2020, 147, 106709. [Google Scholar] [CrossRef]

- Zhao, M.; Guo, W. Formation of a III-N Semiconductor Structure. U.S. Patent 16423274, 27 October 2020. [Google Scholar]

- Zhao, M. III-N Based Substrate for Power Electronic Devices and Method for Manufacturing Same. U.S. Patent 15817343, 29 January 2019. [Google Scholar]

- Vohra, A.; Geens, K.; Zhao, M.; Syshchyk, O.; Hahn, H.; Fahle, D.; Bakeroot, B.; Wellekens, D.; Vanhove, B.; Langer, R.; et al. Epitaxial buffer structures grown on 200 mm engineering substrates for 1200 V E-mode HEMT application. Appl. Phys. Lett. 2020, 120, 261902. [Google Scholar] [CrossRef]

- Borga, M.; Meneghini, M.; Benazzi, D.; Canato, E.; Püsche, R.; Derluyn, J.; Abid, I.; Medjdoub, F.; Meneghesso, G.; Zanoni, E. Buffer breakdown in GaN-on-Si HEMTs: A comprehensive study based on a sequential growth experiment. Microelectron. Reliab. 2019, 100–101, 113461. [Google Scholar] [CrossRef]

- Amano, H.; Baines, Y.; Beam, E.; Borga, M.; Bouchet, T.; Chalker, P.R.; Charles, M.; Chen, K.J.; Chowdhury, N.; Chu, R.; et al. The 2018 GaN power electronics roadmap. J. Phys. D Appl. Phys. 2018, 51, 163001. [Google Scholar] [CrossRef]

- Cornigli, D.; Monti, F.; Reggiani, S.; Gnani, E.; Gnudi, A.; Baccarani, G. TCAD analysis of the leakage current and breakdown versus temperature of GaN-on-Silicon vertical structures. Solid-State Electron. 2016, 115, 173–178. [Google Scholar] [CrossRef]

- Stoffels, S.; Zhao, M.; Venegas, R.; Kandaswamy, P.; You, S.; Novak, T.; Saripalli, Y.; Van Hove, M.; Decoutere, S. The physical mechanism of dispersion caused by AlGaN/GaN buffers on Si and optimization for low dispersion. In Proceedings of the 2015 IEEE International Electron Devices Meeting (IEDM), Washington, DC, USA, 7–9 December 2015; IEEE: Piscataway, NJ, USA, 2015; pp. 35.4.1–35.4.4. [Google Scholar] [CrossRef]

| Directions | Bowing Value [µm] |

|---|---|

| Bowing X | 11.947 |

| Bowing Y | −44.812 |

| Center Bowing | 17.135 |

| Positions | GaN (002) | GaN (102) |

|---|---|---|

| Left-up | 590 arcsec | 756 arcsec |

| Left-down | 591 arcsec | 792 arcsec |

| Right-up | 595 arcsec | 919 arcsec |

| Right-down | 594 arcsec | 766 arcsec |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

You, S.; Lei, Y.; Wang, L.; Chen, X.; Zhou, T.; Wang, Y.; Wang, J.; Liu, T.; Li, X.; Zhao, S.; et al. 750 V Breakdown in GaN Buffer on 200 mm SOI Substrates Using Reverse-Stepped Superlattice Layers. Micromachines 2024, 15, 1460. https://doi.org/10.3390/mi15121460

You S, Lei Y, Wang L, Chen X, Zhou T, Wang Y, Wang J, Liu T, Li X, Zhao S, et al. 750 V Breakdown in GaN Buffer on 200 mm SOI Substrates Using Reverse-Stepped Superlattice Layers. Micromachines. 2024; 15(12):1460. https://doi.org/10.3390/mi15121460

Chicago/Turabian StyleYou, Shuzhen, Yilong Lei, Liang Wang, Xing Chen, Ting Zhou, Yi Wang, Junbo Wang, Tong Liu, Xiangdong Li, Shenglei Zhao, and et al. 2024. "750 V Breakdown in GaN Buffer on 200 mm SOI Substrates Using Reverse-Stepped Superlattice Layers" Micromachines 15, no. 12: 1460. https://doi.org/10.3390/mi15121460

APA StyleYou, S., Lei, Y., Wang, L., Chen, X., Zhou, T., Wang, Y., Wang, J., Liu, T., Li, X., Zhao, S., Zhang, J., & Hao, Y. (2024). 750 V Breakdown in GaN Buffer on 200 mm SOI Substrates Using Reverse-Stepped Superlattice Layers. Micromachines, 15(12), 1460. https://doi.org/10.3390/mi15121460