Abstract

A single photon avalanche diode (SPAD) cell using N-channel extended-drain metal oxide semiconductor (N-EDMOS) is tested for its hot-carrier damage (HCD) resistance. The stressing gate-voltage (VGS) dependence is compared to hot-hole (HH) injection, positive bias temperature (PBT) instability and off-mode (VGS = 0). The goal was to check an accurate device lifetime extraction using accelerated DC to AC stressing by applying the quasi-static (QS) lifetime technique. N-EDMOS device is devoted to 3D bonding with CMOS imagers obtained by an optimized process with an effective gate-length Leff = 0.25 µm and a SiO2 gate-oxide thickness Tox = 5 nm. The operating frequency is 10 MHz at maximum supply voltage VDDmax = 5.5 V. TCAD simulations are used to determine the real voltage and timing configurations for the device in a mixed structure of the SPAD cell. AC device lifetime is obtained using worst-case DC accelerating degradation, which is transferred by QS technique to the AC waveforms applied to N-EDMOS device. This allows us to accurately obtain the AC device lifetime as a function of the delay and load for a fixed pulse shape. It shows the predominance of the high energy hot-carriers involved in the first substrate current peak during transients.

1. Introduction

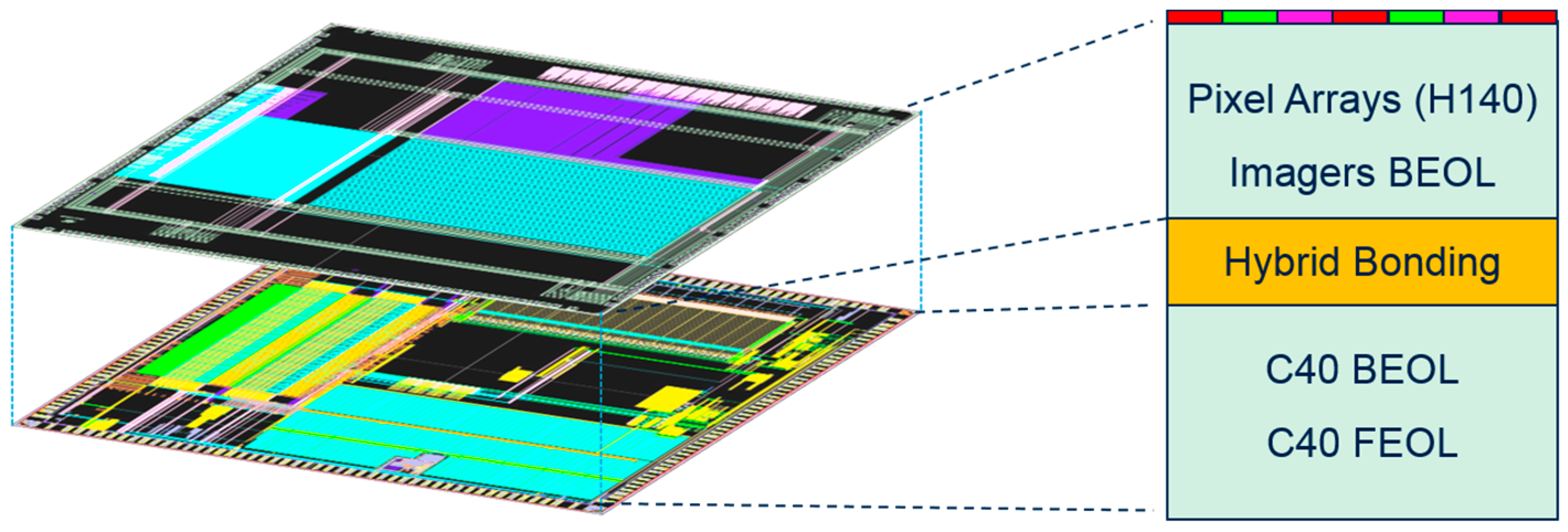

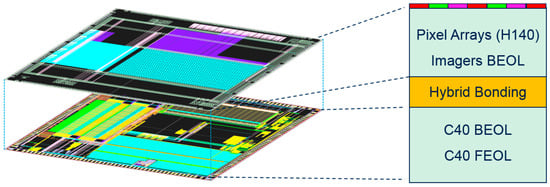

Single photon avalanche diodes (SPAD) are prone to better integration with the down scaling of circuits for high sensitivity imagers [1], widely used in embedded submicronic systems [2]. With the limitations induced by the pitch reduction and the increase in the number of horizontal interconnections, the die architecture has moved to 3D stacking of heterogeneous systems [3]. The architecture is composed (Figure 1) of the vertical assembly of the pixel arrays, the image signal processor and the logic parts. The hybrid bonding through silicon via (TSV) allows the SPAD to gain in BEOL density with the stacking of different CMOS technologies. It can include a memory chip inserted as a third tier between the pixel array and logic chip, which enables high speed readout [4]. Stronger integration has been proposed with an ultra-thin body (UTB) and a fully depleted silicon on insulator (FDSOI) node [2], which shows a good sensitivity for sensing activity. In this case, a better trade-off between performance and consumption is obtained [3]. However, the need for reliability evaluation is required with the use of different processing options. This can be studied by focusing on the benefits of using thin/thick gate-oxide (GO1/GO2), a proper gate-length (LG) and supply voltage (VDD) [5]. A controlled lateral field (ELat) is needed [6], alongside an adapted source/drain terminal [7]. Hot-carrier damage (HCD) [8], bias temperature instability (BTI) [9] and hard breakdown (HBD) [10] are the most limiting wear out mechanisms that reduce MOSFET lifetime [11] regarding AC voltage and environment impact [12].

Figure 1.

3D integration of pixel arrays and CMOS image sensors at the top tier H140 (Lnom = 140 nm) stacked by hybrid bonding with a bottom tier in C40 (Lnom = 40 nm) for the logic part of the image sensor with back end of the line (BEOL) and front end of the line (FEOL) parts.

For device lifetime determination in N-EDMOS, the use of DC stressing first facilitates the distinction between worst-case damage mechanisms [8,9,10]. However, this presents the need to obtain the real AC accelerating degradation rate with bias and timing corresponding to the voltage conditions applied to the device in its cell environment [11,12]. A better approach can be obtained by using the quasi-static (QS) technique once the AC voltage conditions have been checked by ELDO simulations.

After the introduction of the SPAD cell in Section 2, we give the description of the devices and experiments in Section 3. The aim of this work is to show that N-channel EDMOS reliability can be obtained by determining the high energy HCD that remains the dominant mechanism under On-mode (Section 4) with respect to BTI damage, HH injection and Off-mode damage. DC characteristics of substrate current ISUB vs. VGS exhibit a second hump due to 2nd impact ionization into the drift region. However, the DC-AC transfer using QS technique shows in Section 5 that the first ISUB peak dominates the damage during AC transients. This is done according to an adaptive waveform shaping based on the ELDO simulations, which corresponds to the true signals applied to N-EDMOS device placed into the SPAD cell. Even if one considers hot-hole (HH) damage at low VGS for QS lifetime extraction, it does not lead to a lifetime reduction in EDMOS device. This is due to the reduced ELat (VDD) condition in this EDMOS structure. It originates from the optimized N-EDMOS GO2 device (Leff = 0.25 µm, Tox = 5 nm) with maximum voltages VDSmax at 10% of the nominal supply voltage VDDnom = 5 V, while limiting VGSmax = VDSmax/2.

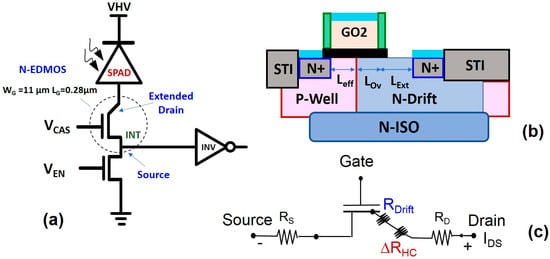

2. The SPAD Cell with EDMOS Transistor

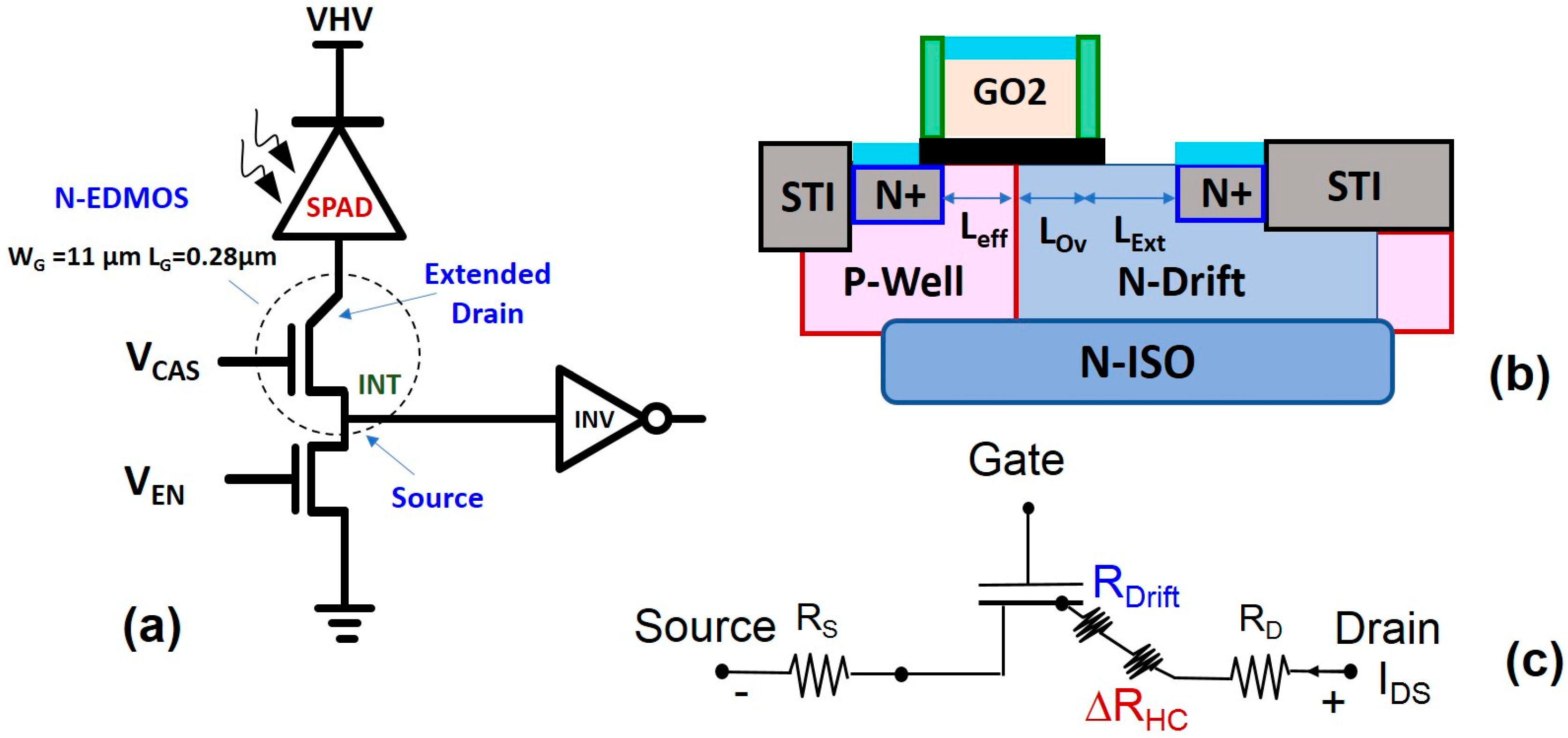

The logic part of a SPAD cell has different processed devices; one is a drain-extended N-channel (N-EDMOS) transistor (Figure 2a), used for its switching capability. This results in a small on resistance (ROn), a bias range with a sustainable large drain voltage (VDS), while the gate-voltage (VGS) is limited to VDS/2 to avoid breakdown of gate-oxide. This is related to the N-drift region (with respect to p-well) designed (Figure 2b) as a drain extension in series with channel, with an overlap length (Lov) with the gate and an extension (Lext) to the drain terminal. The optimization of the EDMOS architecture depends on several factors, such as the gate-oxide thickness (Tox), the lateral isolation by locally oxidized silicon (LOCOS) or by a shallow trench isolation (STI) [13,14]. It is also strongly related to the silicon [11] or silicon on insulator (SOI) substrate [15,16], the presence of a body buried layer [17] and the use of super junction [18]. These parameters lead to a different tradeoff between performance and device reliability. HCD can be used as it tests the N-EDMOS robustness due to the reduction in current drivability and device lifetime, induced by the source-drain resistance increase (RSD) (Figure 2c) in the drift region [14,15].

Figure 2.

(a) Schematics of the SPAD cell with a N-channel EDMOS transistor inserted into the logic block. (b) Cut of the transistor structure composed of the N-Drift/p-well, N-ISO socket and lateral isolation by STI. (c) Illustration of the distinct resistance of the EDMOS transistor with RS, RD from the source/drain terminal, the drift resistance RDrift related to the overlap and extension length regions. HCD contribution from the gate-drain region leads to an additional resistance increase (ΔRHC) induced by interface traps and trapped charges.

3. Devices and Experiments

The tested n-channel EDMOS devices originate from a third batch of advanced CMOS processing (Figure 2b) on a 300 mm wafer before the 3D bonding with the photodiodes. The transistor geometry is with nominal gate length (LG = 0.5 µm) and gate-width (WG = 11 µm), and gate oxide thickness (Tox = 5 nm) (GO2) of SiO2. N-type (ISO) layer is used to isolate the channel from the substrate and the lateral isolation is conducted with shallow oxide trenches (STI). The effective channel-length is consequently Leff = 0.25 µm = LG/2 while N-drift has an extended length defined by LDrift = Lov + Lext where Lov = 0.25 µm. Supply voltage is optimized for smart power application between VDDnom = 5 V and VDSmax = 5.5 V, where VGS is limited to VGS = VDS/2 into the voltage range. Standard I-V characterizations are used with A4156C analyzer controlled in temperature, where DC and AC stressing are followed by I-V characterizations as measurement-stress-measurement (MSM) sequences. When history and recovery effects are studied, we use fast switching experiments with (low leakage) E5250A switching boxes and an 8110A pulse generator using a single linear mode IDS-VGS characteristics in order to maximize the possible effect of recovery. As this latter was observed in 40 nm CMOS (C40) with very thin SiON gate-oxide (Tox = 1.7 nm) [19] and in high-K metal gate (HKMG) with HfO2-SiON with small equivalent oxide thickness EOT = 1.6-2.2 nm [20], we have verified that no significant recovery occurs in GO2 N-EDMOS. This indicates that the use of medium gate-oxide Tox = 5 nm (GO2) is appropriate for reducing the impact of the vertical electric field in the supply voltage range. Lifetime extraction is carried out for 10% in the reduction of saturated drain current measured at VDS = VGS = VDDnom/2. This is intentionally chosen here as it represents the worst case of measurement bias under HCD in N-EDMOS. This lifetime criterion is also required because it remains a relevant bias point regarding the switching activity under AC operation, in direct relation to the transistor delay and frequency impact involved in the digital cell environment [6].

4. Worst Case DC Degradation in N-EDMOS

One specificity of extended drain transistors is that the region of the high electric field is moved to the drift region, out of the channel, where carriers generated from impact ionization (II) are further accelerated in the overlap and extension lengths. This may generate a second hot spot, susceptible to defects creation in this zone to the STI region in LDMOS [7,13], or mainly in the overlap zone of EDMOS [14]. The multiple hot spots found around the STI and near LOCOS show a net impact on the linear on-resistance (ROn = VDS/IDS) depending on the VGS value with respect to VDS. This can be explained by the contribution of HCD under single particle (SP) at medium VGS and under multiple particle (MP) degradation at larger VGS [13], which may involve self-heating when VGS ≥ VDS [14,21]. Recent works have shown that the contribution of secondary holes generated by II leads to additional HCD effect in high voltage (HV) devices [22,23,24]. In this case, the SP (hot carriers) and MP (cold carriers) degradation mechanisms induce a cumulative effect showing that cold holes take a significant role in damaged high-voltage LDMOS [25]. Low power digital applications using thin gate-oxide devices have shown that HC and BTI damage follow an interplay that can be described by a full VGS, VDS mapping [26], modelled by an extended nonradiative multiphonon (NMPeq.+II) framework. This physical modeling has demonstrated the importance of secondary carriers and history effects with alternating HC, BTI and recovery effects at high VGS [26,27]. This was observed particularly in the p-channel MOSFET (Si bulk) structure when hot holes are involved at high |VGS| > |VDS| [26].

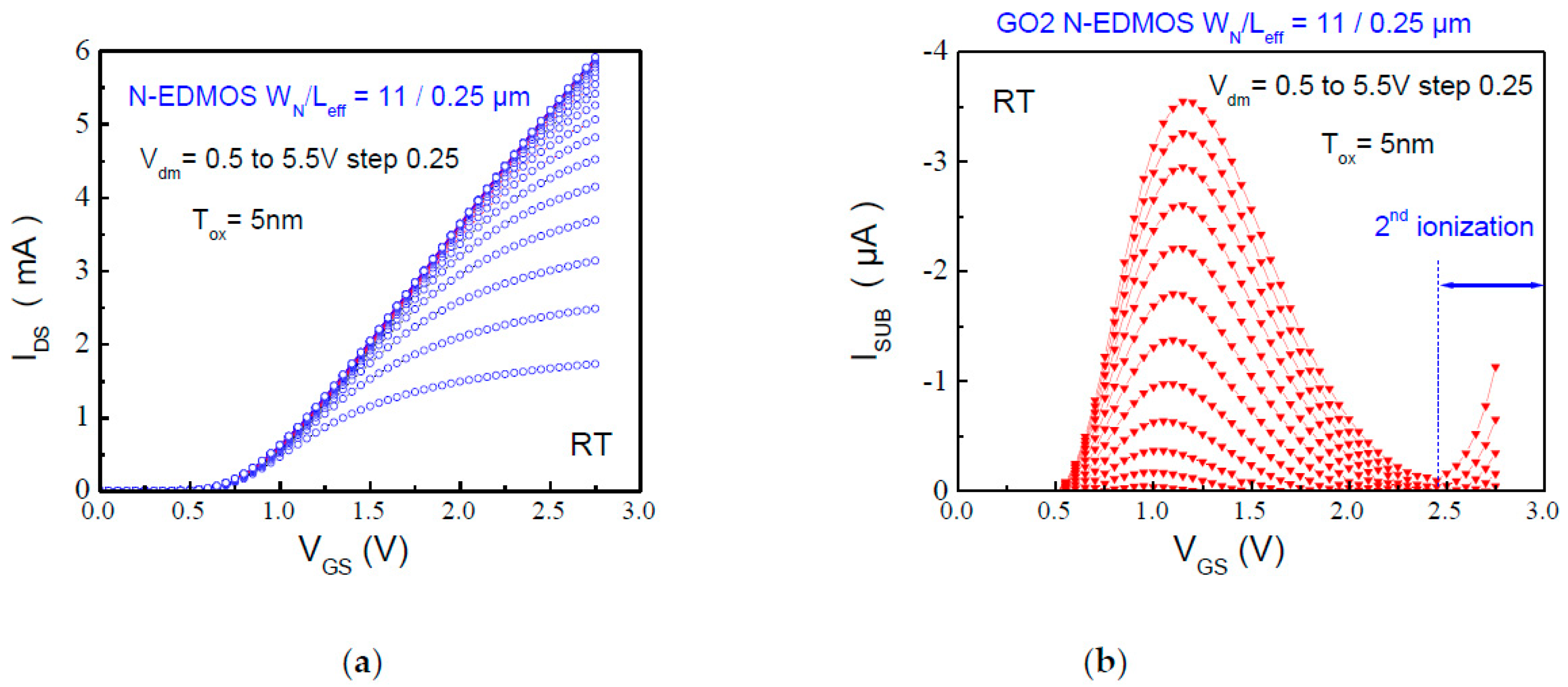

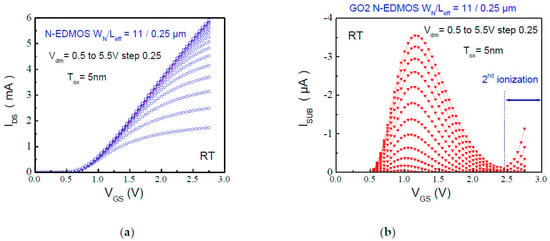

As we want to deploy the QS technique to the special case of N-EDMOS placed into the SPAD cell, the first step is to characterize the substrate (ISUB) and drain current (IDS) dependence. It is conducted as a function of VGS, VDS for all DC voltage conditions seen by the device in its AC environment. Figure 3a,b shows the IDS and ISUB currents representative of the II phenomenon in the transistor for a small incremental step of bias condition. We observe the channel current (Figure 3a) as the source of carriers able to trigger II at the drain, which is measured through the first hump of ISUB (Figure 3b). These humps appear at much lower VGS than in standard MOSFET and have a symmetrical source/drain structure. This intrinsic ISUB curve is generally composed by the hot-hole population induced by the first (II) electron-hole pairs generation at the (first) peak lateral field entering the drain (N-Drift).

Figure 3.

First step of the QS technique in Leff = 0.25 µm N-EDMOS (a) Measurement of the IDS-VGS curves done with a small VDS step (VDS = 0.5 V to 5.5 V step 0.25 V) in order to cover all the DC bias points submitted to a fresh device under (AC) operation. (b) Measurement of the substrate current ISUB—(VGS, VDS) for the same voltage range that shows the second hump at high VGS due to 2nd impact ionization occurrence, that can reach avalanche mode depending on VGS (VDS) magnitude.

The departure of a second hump through the rise in ISUB increasing VGS (Figure 3b) indicates the existence of a second II hot spot located into the N-Drift, combined by the high IDS value. This leads to an exponential rise in ISUB in correlation to the Kirk effect [28]. The high electric field that peaks at the drift-drain junction induces ISUB current rise, which has been recently modelled in a compact model for LDMOS transistor with similar structure [29]. We show in Figure 3b that ISUB magnitude is much higher for the first ISUB peak as a function of VDS than its values obtained at VGSmax increasing VDS. It indicates that the electric field is not as high as the one at low VGS (1st ISUB peak) in contrast to what was observed in LDMOS [29]; this is due to the limited voltage range in our N-EDMOS device.

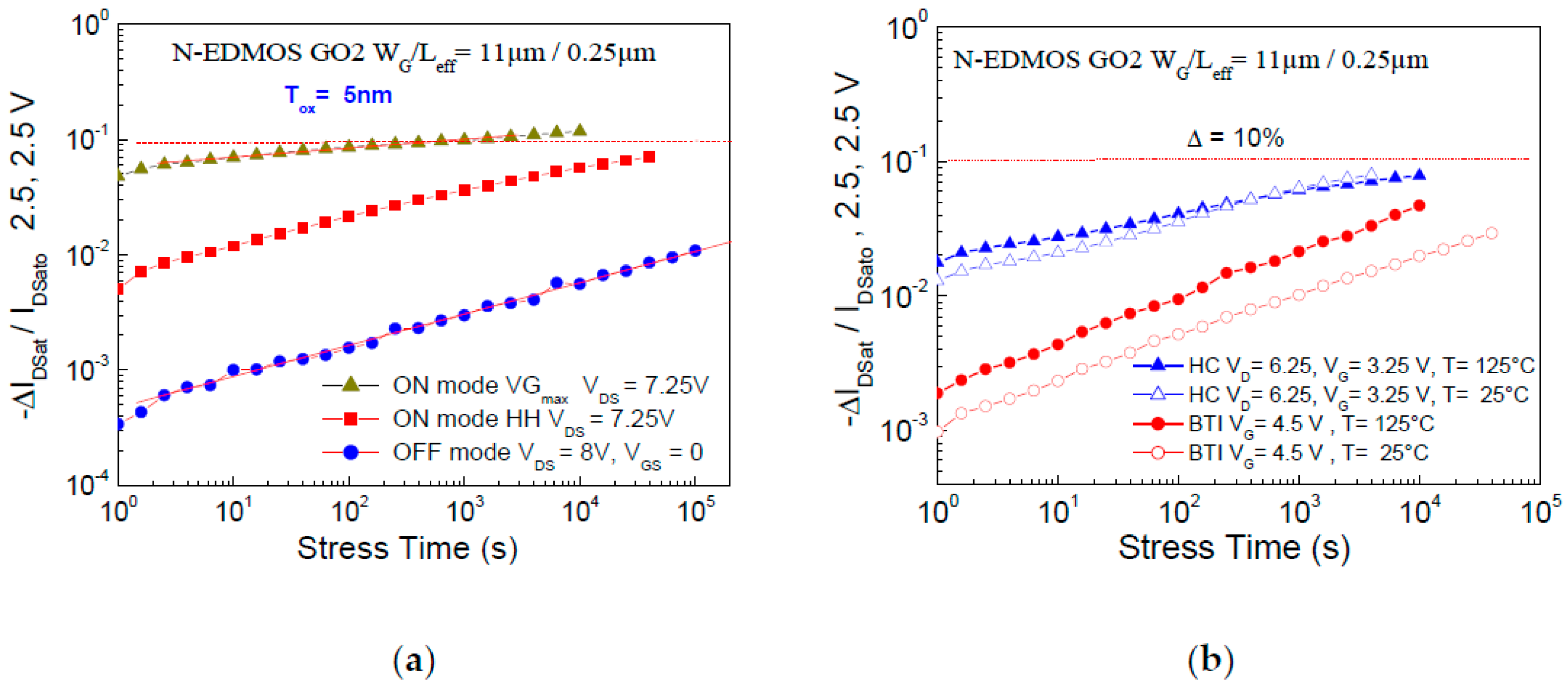

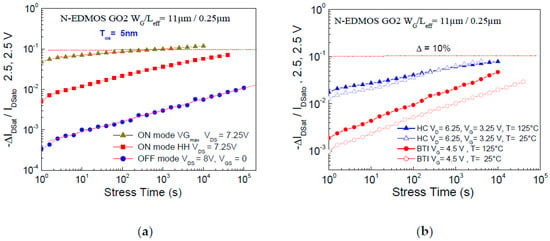

In previous works [10,11,12], it has been shown that hot-hole (HH) damage at low VGS stress and Off-mode damage at VGS = 0 (high VDS) may trigger HBD in thin gate-oxide N-EDMOS localized in the gate-drain region above the N-Drift [10,11]. We have ensured that these behaviors are avoided in this present N-EDMOS device using thicker gate-oxide (5 nm) and longer gate-length [11]. HBD has been evidenced in this batch at VDS = 16.5 V (VGS = 0), which represents a much higher voltage condition than those used for On-mode damage (HCD and BTI) and Off-mode damage in this present work. It is shown in Figure 4a that VGSmax condition is the worst-case for HCD in N-EDMOS in comparison to HH damage (VTh ≤ VGS ≤ 1.2 V) and Off-mode at VGS = 0 (VDS = 8 V) using long term DC stressing [30]. The comparison to positive BTI (PBTI) confirms, in Figure 4b, the lower degradation rate under BTI in N-channel EDMOS. Hence, choosing the classical VGSmax = VDSmax/2 or a low VGS for HH stressing condition [6,11] leads to a large difference in DC lifetime determination [30]. We show in the next section that the full QS technique applied to N-EDMOS is mainly based on the first ISUB transients when one considers the real timing and voltage configurations submitted to the device placed into the SPAD cell.

Figure 4.

(a) Saturated drain current reduction at room temperature (RT) plotted as a function of VGS stress between On mode at VDS = 7.25 V under HH condition, VGSmax = VDS/2 and Off mode at VDS = 8 V and VGS = 0. (b) Same criterion used to compare On mode damage at VGSmax (VDS = 6.25 V) and PBTI for VGS = 4.5 V (VDS = 0) between room temperature (RT = 25 °C) and 125 °C (DC) stressing.

5. Quasi-Static Lifetime Extraction

Accurate lifetime determination is known to be strongly dependent on the involved mechanisms in the device under operation [22,23,24,25,26] when one damage takes the lead, or several damages compete in parallel as a function of time. This is typically encountered between Off mode (VGS = 0) and On-mode, whereas some damage may dominate for a short time and the others over the long term [8,9,10,11]. This depends on the progression of each mechanism (its nature, defect density and extension length) with time [8] and its possible effect on the accelerating degradation rate [9,10,11]. It may originate from interacting driven phenomena as the electric field [9,19] channel current [6,25] and thermal effects [26,27]. These effects can contribute to aggravation or relief in the device due to cumulating/compensating damage mechanisms that complicate the lifetime evaluation. This trend is generally observed in very thin gate-oxide as a history effect and recovery effect, which both depend on the gate and source/drain processing and device dimensions. It leads to specific behaviors that must be checked using AC stressing very close to the circuit functioning [30].

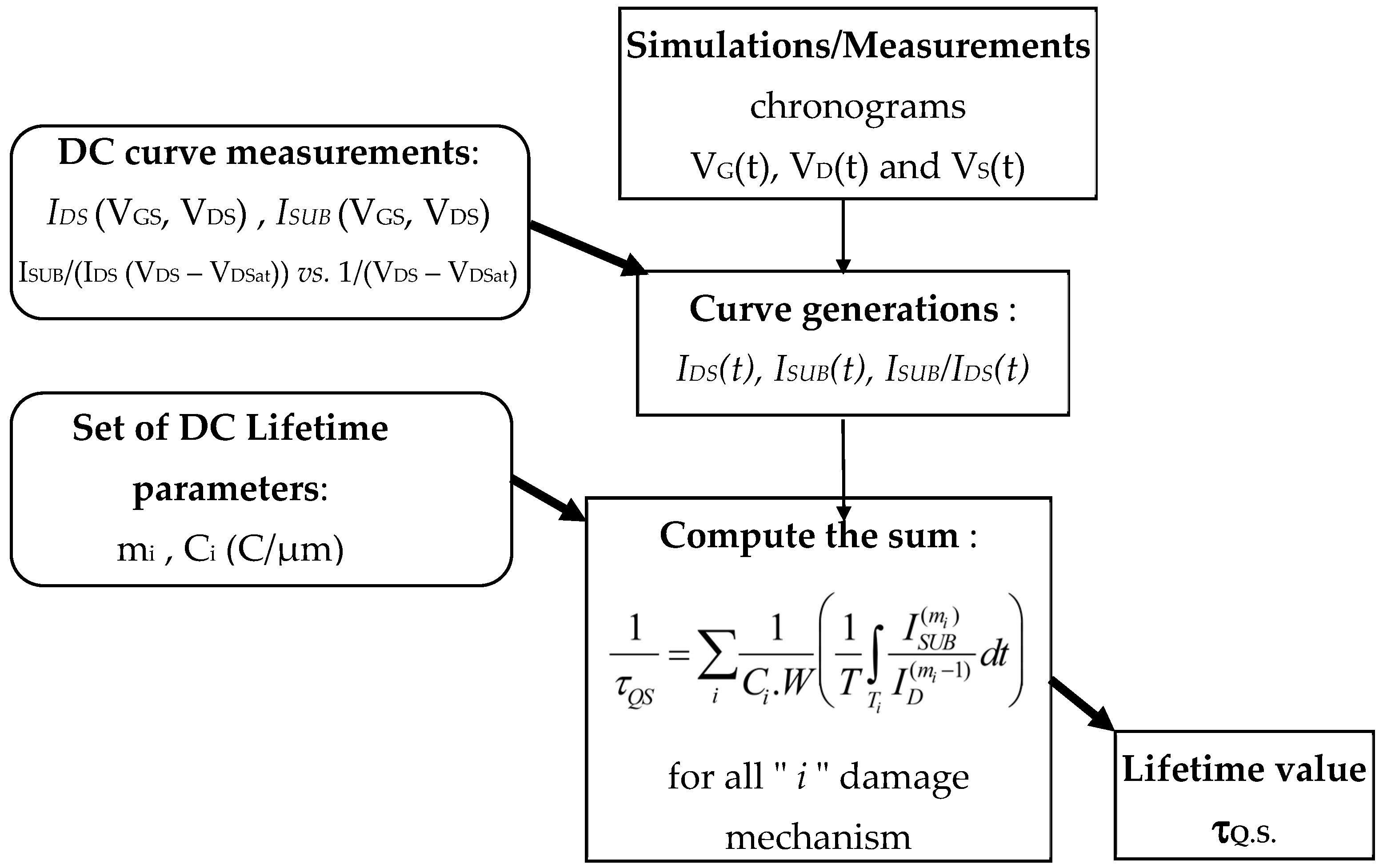

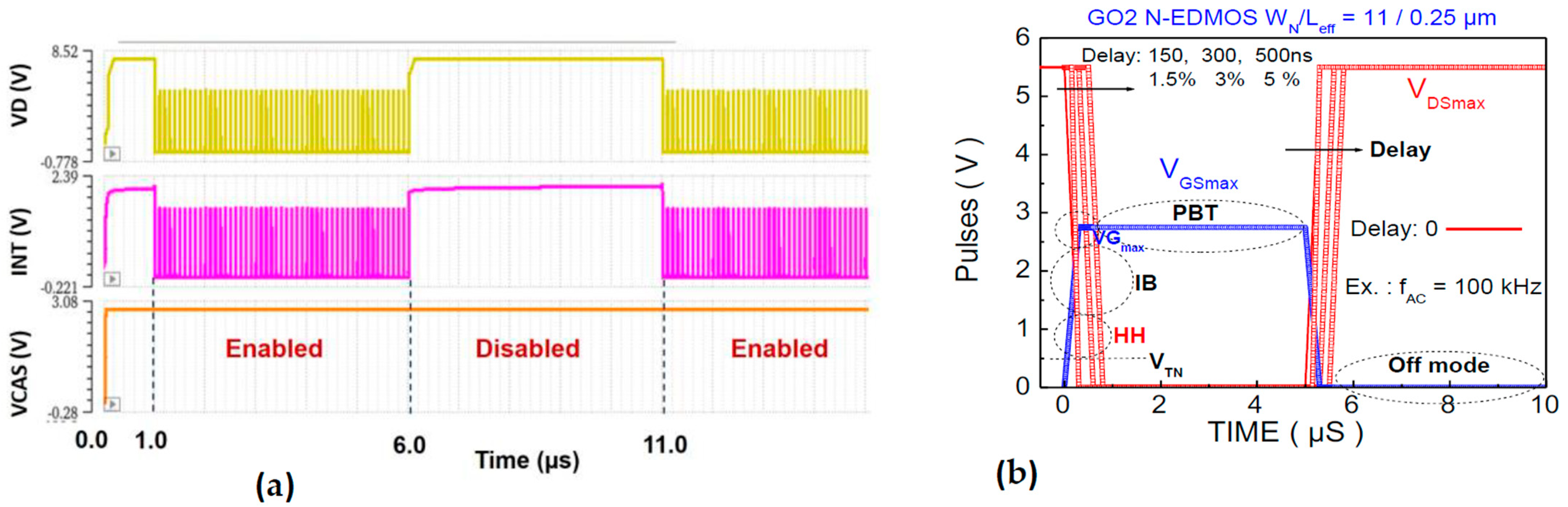

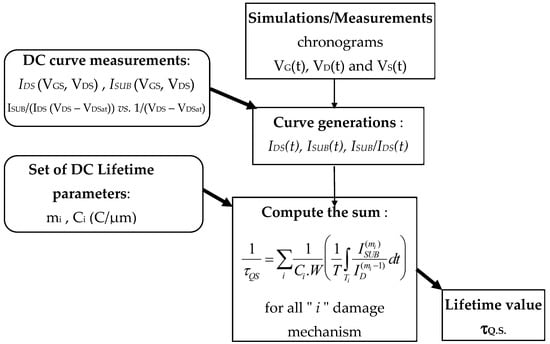

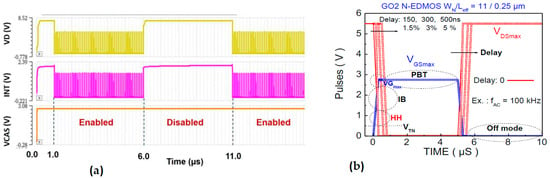

We have applied the QS technique [31,32,33], illustrated in Figure 5, by considering the timing results obtained by TCAD simulation (shown in Figure 6a) for the N-EDMOS device in the SPAD cell (Figure 2a). N-EDMOS device is switched in the cell with the potential variation of photodiode detector at its drain during enabled/disabled cycles [2], here with a frequency (fAC) of 100 kHz. Since the N-EDMOS source is switched by INT potential (Figure 2a), it varies VDS, VGS applied to the transistor where VGS = VDS/2 under the low SPAD illumination duration (Figure 6a), with a frequency of 10 MHz. This effect switches the transistor between On- and Off- mode through body effect on VTh despite VG (VCAS) being constant. Hence, the On-mode frequency (Figure 6a) chosen for TCAD is 10 MHz, while the longer Off mode is implied with 5 µs duration under low illumination. This enables us to obtain the low to high frequency range (Figure 6a,b), which would imply the possible influence of recovery effect (when VDS = 0). This latter has not been observed using constant pulse shape experiments [30]. Therefore, we obtained AC results (Figure 6b) that conformed to the EDMOS waveforms independently of the frequency by fixing the pulse shape αshape = tr,f/TAC for a given delay. This enabled us to obtain the load variation range between the output and input of the pulsed transistor (i.e., between VDS and VGS) into the SPAD cell.

Figure 5.

Program sequence of the QS lifetime extraction based on (1) VD, VG, VS signal timing as a function of the N-EDMOS waveforms (2) the generation of the experimental curves from the DC IDS (VGS, VDS) ISUB (VGS, VDS) from Figure 3a,b which are transferred to every voltage condition found at each timing point of the chronogram. (3) Calculation of the QS lifetime with the set of lifetime parameters (mi, Ci) as the sum of each damage mechanism “i”, of duration Xi. This is moved automatically to the waveforms, i.e., as a function of VDS = VD − INT and VGS = VCAS − INT (Figure 2a), for Off-mode (0 ≤ VGS < VTh), HH stress (VTh ≤ VGS < 0.18 VDS), ISUB stress (0.2 VDS ≤ VGS < 0.44 VDS) and VGSmax stress (corresponding to 0.46 VDS ≤ VGS < 0.5 VDS). This enables in the final step to calculate the QS lifetime considering the duty cycle factor αduty and pulse shape αshape of the waveforms.

Figure 6.

(a) ELDO potential simulation of timings for VD, VS (INT) and VG (VCAS) in N-EDMOS into the SPAD cell (b) Waveforms obtained from QS extraction as a function of delay = 0 to 5%, taking into account the corresponding VGS (t) VDS (t) variation allocated to each damage mechanism phase.

The real waveform shape applied to N-EDMOS device into the SPAD cell has been simulated (Figure 6a) with the TCAD (ELDO) tool. This enables us to set up the parameters used for the VGS, VDS pulse shaping and timing periods used by the QS methodology [32,33], as shown in Figure 5. The distinct damaging phases can be successively considered (Figure 6b) in order to assess the QS lifetime calculation. For each “i” damage mechanism effective in each duration phase, we compute τDC,i calculation under On-mode operation with:

with:

- (mHH, CHH) corresponding to time duration under HH degradation where voltage satisfies VTh ≤ VGS < 0.18 VDS

- (mIB, CIB) corresponding to time duration under ISUB peak degradation where we have 0.2 VDS ≤ VGS < 0.44 VDS

- (mVgmax, CVgmax) corresponding to time duration under VGSmax degradation where we have 0.46 VDS ≤ VGS < 0.5 VDS

The calculation of the complete QS device lifetime is the sum of the integrated lifetime values obtained from each DC lifetime considered independently (with neither history effect nor recovery). Considering the dominant effect of high energy hot-carriers, the discretization of the (VGS, VDS) pulses is thus computed by the program with:

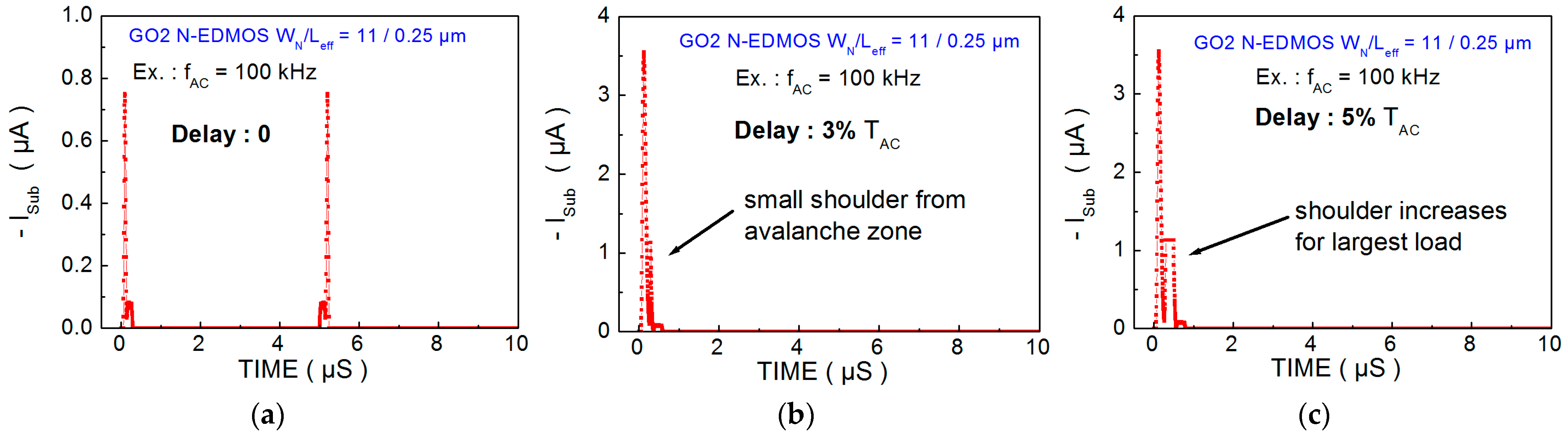

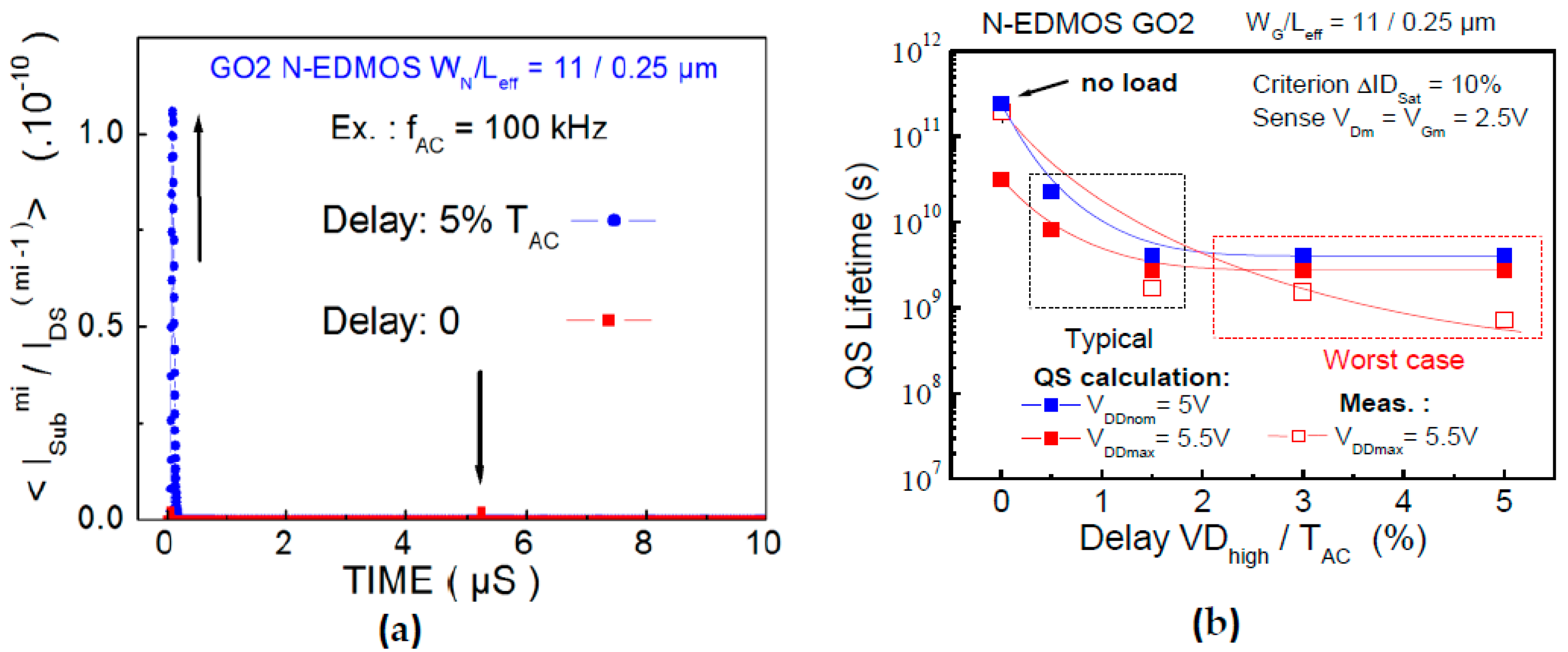

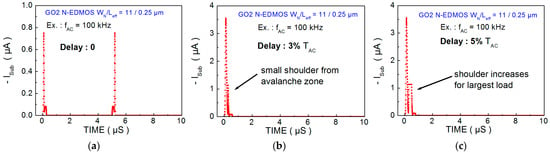

Then, the program (Figure 5) builds up the IDS, ISUB and (ISUB/IDS) time dependences, which one can loop for each delay value (Figure 6b). Results in Figure 7a show the symmetrical peaks of ISUB (t) when no delay is involved (intrinsic case). For 3% delay value (typical digital application) and for 5% value at large load (Figure 7b,c), it induces ISUB peaks only in the VGS rising when VDS is high. Since VGS is limited to VDS/2, it makes the second ISUB peak disappear. We note that a shoulder grows with the delay on the right side of the first ISUB peak due to the increase in ISUB (VGS) in the VGSmax region, as previously shown in Figure 3b, in relation to ELat increase in the N-drift to drain contact region (Section 4).

Figure 7.

ISUB (VGS, VDS, time) from a fresh N-EDMOS device transferred to the pulse waveforms as a function of the signal period (fAC = 100 kHz) corresponding to the biased EDMOS placed into the SPAD cell (a) for no delay (b) for 3% delay and (c) for 5% delay.

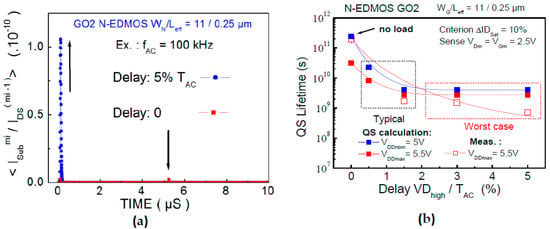

Our previous results on lifetime extraction in the same technology [30] have used a simplification for the QS technique using the τDC calculation based on the power-law dependence with VDS. This was performed in order to compare the On-mode to Off-mode damage by its lifetime dependence expressed as τDC,i ∝ Ci VDS −mi. In this case, we have shown that the Off-mode and PBTI at VGSmax stressing do not lead to a significant impact in the QS lifetime calculation [30], whereas the On-mode dominates the QS device lifetime. We have considered, here, the full QS modeling during On-mode (Figure 8a,b) based on the complete calculation with (1)–(2), i.e., for HH, ISUB and VGSmax stressing phases. The delay range is set between no load and large load (5% delay) to enhance HCD. QS lifetime plot obtained by the single (ISUB mi/IDS (mi−1)) peak at the VGS rising front, and it contains no additional shoulder, as seen in ISUB (Figure 7b,c). This indicates the lack of the weighting lifetime factors (mi, Ci) effect in (2) for these timings in the VGSmax voltage region. This suggests no significant incidence of HH sequence throughout the AC pulsing. This consequently leads to the QS lifetime calculation (Figure 8b), which is mainly dependent on (mIB, CIB) as a function of delay, whereas device lifetime is clearly reduced for 3–5% delay (worst case). In contrast, the QS result for no load is far less degrading, showing a limited scatter between the QS lifetime extraction and the measurements performed at the voltage condition VDSmax, VGSmax. These results confirm the validity of the QS technique for lifetime determination in the target [VDDnom,VDDmax] applied to the N-EDMOS placed into the SPAD cell.

Figure 8.

(a) Integrated (ISUB/IDS) ratio to the power of lifetime parameter (mi) with (1)–(2) for each damage region, which are plotted as a function of no delay and 5% delay. (b) Lifetime extraction for the full pulse waveform based on ΔIDSat = 10% compared between QS calculation and the measurements in N-EDMOS into the SPAD cell, biased at VDDnom and VDDmax.

With the help of the timing simulation by TCAD, there is a benefit to accurately matching the real configuration of voltage conditions of the N-EDMOS device that exceeds the 10-year lifetime under AC operation.

6. Conclusions

N-EDMOS device used in SPAD cell for future 3D stacking of CMOS imagers has been studied under AC stressing corresponding to its real AC operation configuration. The application of the QS technique shows that the device lifetime expressed as a function of each DC degradation mechanisms involved during VGS, VDS pulsing leads to the predominance of the first ISUB peak related to high energy hot-carriers. With the use of TCAD simulations for determining the real timing and voltage configurations, the QS technique shows that AC device lifetime is mainly dependent on the HCD that lies during VGS rising transients. This indicates a much smaller contribution of cold carriers, HH damage and Off-mode damage during VGS pulsing due to a limited voltage range VGSmax = VDSmax/2. The main reason is the small effect of the weighting factors (mi, Ci) in the full QS lifetime calculation, due to the real voltage and timing span involved during N-EDMOS device operation. It is thus confirmed that this processed N-EDMOS device (Leff = 0.25 µm, Tox = 5 nm, VDDmax = 5.5 V) exceeds the 10-year AC lifetime for this mission profile. This guaranties that the designed N-EDMOS placed in SPAD cell is a good candidate for the future 3D stacking of CMOS imagers using hybrid bonding with the logic circuits.

Author Contributions

Conceptualization, A.B. and H.P.; methodology, A.B.; software, A.B.; validation, A.B., H.P., X.F. and F.C.; formal analysis, X.F.; investigation, A.B. and H.P.; resources, X.F.; data curation, A.B.; writing—original draft preparation, A.B.; writing—review and editing, A.B.; visualization, A.B.; supervision, X.F.; project administration, F.C. All authors have read and agreed to the published version of the manuscript.

Funding

This research received no external funding.

Data Availability Statement

Data available on request.

Acknowledgments

The authors (1) are deeply grateful for all the supports of ST Microelectronics Crolles (2) for their helps in the TCAD results, the discussions and the supply of the wafers and test structures.

Conflicts of Interest

The authors declare no conflicts of interest.

Abbreviations

| BEOL | Back-End of the Line |

| BTI | Bias Temperature Instability |

| EDMOS | Extended-Drain Metal Oxide Semiconductor |

| HBD | Hard Breakdown |

| HCD | Hot-Carrier Damage |

| HH | Hot Hole |

| HKMG | High-K Metal Gate |

| II | Impact Ionization |

| LOCOS | Locally Oxidized Silicon |

| MOSFET | Metal-Oxide-Semiconductor Field Effect Transistor |

| PBTI | Positive Bias Temperature Instability |

| QS | Quasi-Static |

| STI | Shallow Trench Isolation |

| SPAD | Single Photon Avalanche Diode |

| FDSOI | Fully Depleted Silicon on Insulator |

| TSV | Through Silicon Via |

References

- Lee, M.-J.; Charbon, E. Progress in single-photon avalanche diode image sensors in standard CMOS: From two-dimensional monolithic to three dimensional-stacked technology. Jpn. J. Appl. Phys. 2018, 57, 1002A3-1–1002A3-6. [Google Scholar] [CrossRef]

- Chaves, T.A.; Issartel, D.; Clerc, R.; Pittet, P.; Cellier, R.; Uhring, W.; Cathelin, A.; Calmon, F. Body-biasing considerations with SPAD FDSOI: Advantages and drawbacks. In Proceedings of the European Solid-State Device Research Conference Proc (ESSDERC), Krakow, Poland, 23–26 September 2019; pp. 210–213. [Google Scholar] [CrossRef]

- Ayoub, B.; Moreau, S.; Lhostis, S.; Frémont, H.; Mermoz, S.; Souchier, E.; Deloffre, E.; Escoubas, S.; Cornelius, T.; Thomas, O. In-situ characterization of thermomechanical behavior of copper nano-interconnect for 3D integration. Microelectron. Eng. 2022, 261, 111809. [Google Scholar] [CrossRef]

- Haruta, T.; Nakajima, T.; Hashizume, J.; Umebayashi, T.; Takahashi, H.; Taniguchi, K.; Kuroda, M.; Sumihiro, H.; Enoki, K.; Yamasaki, T. 4.6 a 1/2.3 inch 20mpixel 3-layer stacked CMOS image sensor with DRAM. In Proceedings of the IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 5–9 February 2017; pp. 76–77. [Google Scholar] [CrossRef]

- Skotnicki, T.; Fenouillet-Beranger, C.; Gallon, C.; Bœuf, F.; Monfray, S.; Payet, F.; Pouydebasque, A.; Szczap, M.; Farcy, A.; Arnaud, F.; et al. Innovative Materials, Devices, and CMOS Technologies for Low-Power Mobile Multimedia. IEEE Trans. Electron Dev. 2008, 55, 96–130. [Google Scholar] [CrossRef]

- Bravaix, A.; Guérin, C.; Huard, V.; Roy, D.; Roux, J.-M.; Vincent, E. Hot-Carrier Acceleration Factors for Low Power Management in DC-AC stressed 40 nm NMOS node at High Temperature. In Proceedings of the IEEE International Reliability Physics Symposium (IRPS), Montreal, QC, Canada, 26–30 April 2009; pp. 531–548. [Google Scholar] [CrossRef]

- Tsai, H.-C.; Yadav, Y.; Liou, R.-H.; Wu, K.-M.; Lin, Y.-C. Breakdown voltage model and electrical characteristics of CMOS compatible RESURF STI drain extended MOS transistors. IEEE Trans. Electron Devices 2015, 62, 1958–1963. [Google Scholar] [CrossRef]

- Tyaginov, S.; Bina, M.; Franco, J.; Osintsev, D.; Triebl, O.; Kaczer, B.; Grasser, T. Physical Modeling of Hot-Carrier Degradation for Short- and Long-Channel MOSFETs. In Proceedings of the International Reliability Physics Symposium (IRPS), Waikoloa, HI, USA, 1–5 June 2014; pp. XT.16.1–XT.16.8. [Google Scholar] [CrossRef]

- Grasser, T.; Stampfer, B.; Waltl, M.; Rzepa, G.; Rupp, K.; Schanovsky, F.; Pobegen, G.; Puschkarsky, K.; Reisinger, H.; O’Sullivan, B.; et al. Characterization and physical modeling of the temporal evolution of near-interfacial states resulting from NBTI/PBTI stress in nMOS/pMOS transistors. In Proceedings of the IEEE International Reliability Physics Symposium (IRPS), Burlingame, CA, USA, 11–15 March 2018; pp. 2A.2.1–2A.2.10. [Google Scholar] [CrossRef]

- Varghese, D.; Kufluoglu, H.; Reddy, V.; Shichijo, H.; Mosher, D.; Krishnan, S.; Ashraful Alam, M. Off-State Degradation in Drain-Extended NMOS Transistors: Interface Damage and Correlation to Dielectric Breakdown. IEEE Trans. Electron Devices 2007, 54, 2669–2678. [Google Scholar] [CrossRef]

- Li, S.; Bravaix, A.; Kussener, E.; Ney, D.; Federspiel, X.; Cacho, F. Hot-Carrier Degradation in P- and N-Channel EDMOS for Smart Power Application. Microelectron. Reliab. 2020, 114, 113811. [Google Scholar] [CrossRef]

- Arabi, M.; Federspiel, X.; Cacho, F.; Rafik, M.; Nguyen, A.P.; Garros, X.; Ghibaudo, G. New Insights on Device Level TDDB at GHz Speed in Advanced CMOS Nodes. IEEE Trans. Device Mater. Reliab. 2019, 19, 255–261. [Google Scholar] [CrossRef]

- Tallarico, A.N.; Reggiani, S.; Depetro, R.; Torti, A.M.; Croce, G.; Sangiorgi, E.; Fiegna, C. Hot-Carrier Degradation in Power LDMOS: Selective LOCOS- Versus STI-Based Architecture. IEEE J. Electron Devices Soc. (JEDS) 2018, 6, 219–226. [Google Scholar] [CrossRef]

- Liu, S.; Sun, W.; Qian, Q.; Wei, J.; Fang, J.; Li, T.; Zhang, C.; Shi, L. A Review on Hot-Carrier-Induced Degradation of Lateral DMOS Transistor. IEEE Trans. Device Mater. Reliab. 2018, 18, 298–312. [Google Scholar] [CrossRef]

- Okawa, T.; Eguchi, H.; Taki, M.; Hamada, K. 2000 V SOI LDMOS with new drift structure for HVICs. In Proceedings of the International Symposium on Power Semiconductor Devices and Ics (ISPSD), Prague, Czech Republic, 12–16 June 2016; pp. 435–438. [Google Scholar] [CrossRef]

- Mansoori, H.A.; Orouji, A.A.; Dideban, A. New technique to extend the vertical depletion region at SOI-LDMOSFETs. J. Comput. Electron. 2017, 16, 666–675. [Google Scholar] [CrossRef]

- Disney, D.; Lin, W.-C.; Liu, X.X.; Pandey, S.; Kim, J. 180nm HVIC technology for digital AC/DC power conversion. In Proceedings of the International Symposium on Power Semiconductor Devices and Ics (ISPSD), Sapporo, Japan, 28 May–1 June 2017; pp. 287–290. [Google Scholar]

- Tsai, J.-Y.; Hu, H.-H. Novel poly-Si SJ-LDMOS for system on-panel application. IEEE Trans. Electron Devices 2016, 63, 2482–2487. [Google Scholar] [CrossRef]

- Denais, M.; Bravaix, A.; Huard, V.; Parthasarathy, C.; Ribes, G.; Perrier, F.; Revil, N.; Rey-Tauriac, Y. “On-the-fly” Characterization of NBTI in ultra-thin gate-oxide PMOSFET’s. In Proceedings of the IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 13–15 December 2004; pp. 109–112. [Google Scholar] [CrossRef]

- Kerber, A.; Cartier, E.A. Reliability Challenges for CMOS Technology Qualifications With Hafnium Oxide/Titanium Nitride Gate Stacks. IEEE Trans. Devices Mater. Reliab. 2009, 9, 147–162. [Google Scholar] [CrossRef]

- Sasse, G.T.; Claes, J.A.M.; De Vries, B. An LDMOS hot carrier model for circuit reliability simulation. In Proceedings of the IEEE International Reliability Physics Symposium (IRPS), Waikoloa, HI, USA, 1–5 June 2014; pp. 5D.5.1–5D.5.6. [Google Scholar] [CrossRef]

- Tyaginov, S.; Bury, E.; Grill, A.; Yu, Z.; Makarov, A.; De Keersgieter, A.; Vexler, M.I.; Vandemaele, M.; Wang, R.; Spessot, A.; et al. On the Contribution of Secondary Holes in Hot-Carrier Degradation—A Compact Physics Modeling Perspective. In Proceedings of the IEEE Electron Devices Technology & Manufacturing Conference (EDTM), Seoul, Republic of Korea, 7–10 March 2023; pp. 1–3. [Google Scholar] [CrossRef]

- Starkov, I.; Enichlmair, H.; Tyaginov, S.; Grasser, T. Analysis of the threshold voltage turn-around effect in high-voltage n-MOSFETs due to hot-carrier stress. In Proceedings of the IEEE International Reliability Physics Symposium (IRPS), Anaheim, CA, USA, 15–19 April 2012; pp. XT.7.1–XT.7.6. [Google Scholar] [CrossRef]

- Tyaginov, S.; Starkov, I.; Triebl, O.; Ceric, H.; Grasser, T.; Enichlmair, H.; Park, J.-M.; Jungemann, C. Secondary generated holes as a crucial component for modeling of HC degradation in high-voltage n-MOSFET. In Proceedings of the International Conference on Simulation of Semiconductor Processes and Devices (SISPAD), Osaka, Japan, 8–10 September 2011; pp. 123–126. [Google Scholar] [CrossRef]

- Sharma, P.; Tyaginov, S.; Jech, M.; Wimmer, Y.; Rudolf, F.; Enichlmair, H.; Bina, M.; Enichlmair, H.; Park, J.-M.; Ceric, H.; et al. The role of cold carriers and the multiple-carrier process of Si–H bond dissociation for hot-carrier degradation in n- and p-channel LDMOS devices. Solid-State Electron. 2016, 115, 185–191. [Google Scholar] [CrossRef]

- Jech, M.; Rott, G.; Reisinger, H.; Tyaginov, S.; Rzepa, G.; Grill, A.; Jabs, D.; Jungemann, C.; Waltl, M.; Grasser, T. Mixed Hot-Carrier/Bias Temperature Instability Degradation Regimes in Full {VG, VD} Bias Space: Implications and Peculiarities. IEEE Trans. Electron Devices 2020, 67, 3315–3322. [Google Scholar] [CrossRef]

- Federspiel, X.; Rafik, M.; Angot, D.; Cacho, F.; Roy, D. Interaction between BTI and HCI degradation in high-K devices. In Proceedings of the IEEE International Reliability Physics Symposium (IRPS), Monterey, CA, USA, 14–18 April 2013; pp. XT.9.1–XT.9.4. [Google Scholar] [CrossRef]

- Wang, J.; Li, R.; Dong, Y.; Zou, X.; Shao, L.; Shiau, W.T. Substrate current characterization and optimization of high voltage LDMOS transistors. Solid-State Electron. 2008, 52, 886–891. [Google Scholar] [CrossRef]

- Gill, G.; Singhal, A.; Pahwa, G.; Hu, C.; Agarwal, H. Compact Modeling of Impact Ionization in High-Voltage Devices. IEEE Trans. Electron Devices 2023, 70, 2389–2394. [Google Scholar] [CrossRef]

- Pitard, H.; Bravaix, A.; Kussener, E.; Federspiel, X.; Fillon, R.; Cacho, F. DC to AC Analysis of HC vs. BTI damage in N-EDMOS used in Single Photon Avalanche Diode cell. Microelectron. Reliab. 2023, 150, 115111. [Google Scholar] [CrossRef]

- Scholten, A.J.; Stephens, D.; Smit, G.D.J.; Sasse, G.T.; Bisschop, J. The Relation Between Degradation Under DC and RF Stress Conditions. IEEE Trans. Electron Devices 2011, 58, 2721–2728. [Google Scholar] [CrossRef]

- Mistry, K.R.; Doyle, B. AC versus DC Hot-Carrier Degradation in n-Channel MOSFET’s. IEEE Trans. Electron Devices 1993, 40, 96–104. [Google Scholar] [CrossRef]

- Quader, K.N.; Fang, P.; Yue, J.T.; Ko, P.K.; Hu, C. Hot-Carrier-Reliability Design Rules for Translating Device Degradation to CMOS Digital Circuit Degradation. IEEE Trans. Electron Devices 1994, 41, 681–691. [Google Scholar] [CrossRef]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).