A Comprehensive Analysis of Unclamped-Inductive-Switching-Induced Electrical Parameter Degradations and Optimizations for 4H-SiC Trench Metal-Oxide-Semiconductor Field-Effect Transistor Structures

Abstract

:1. Introduction

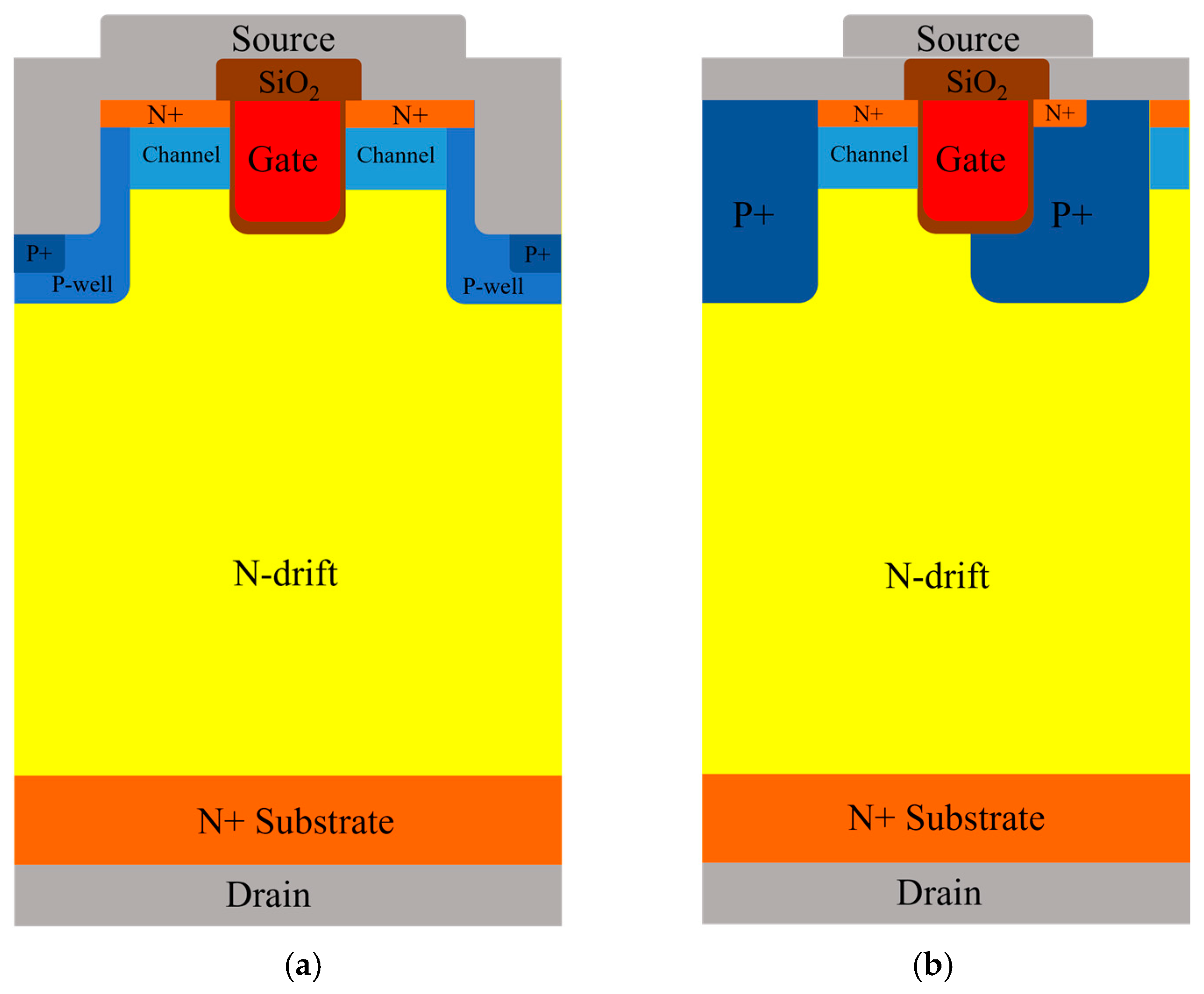

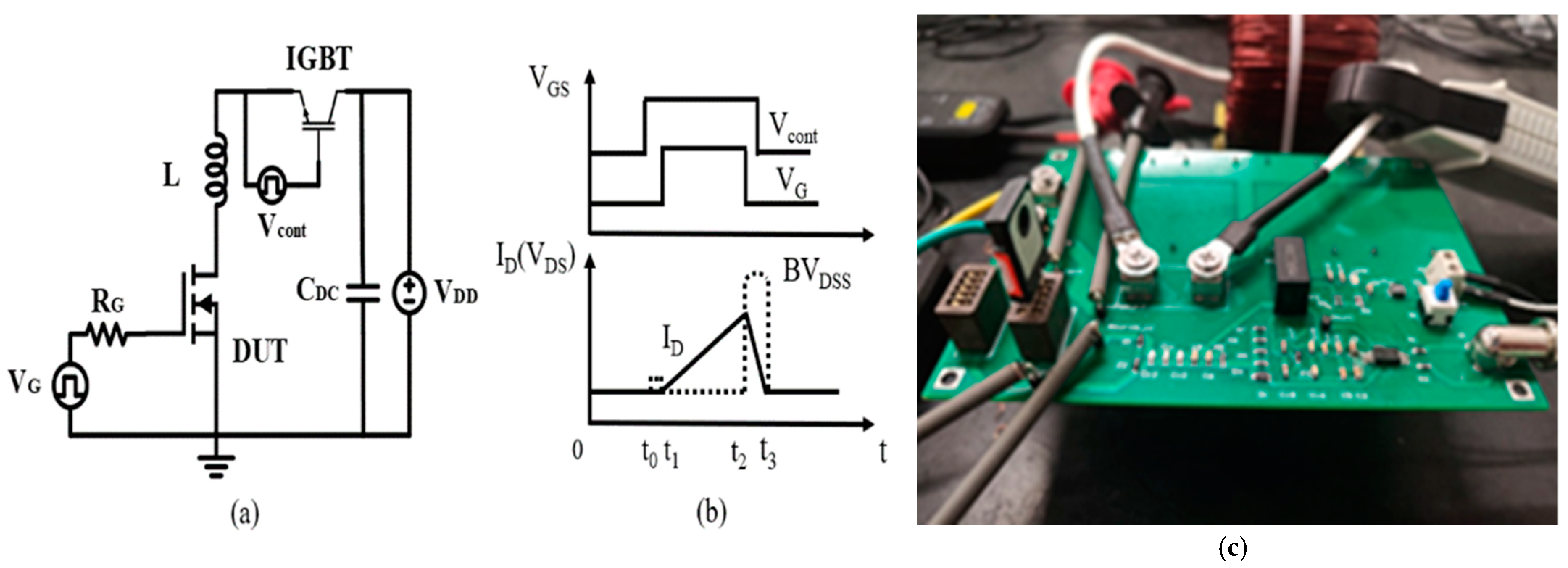

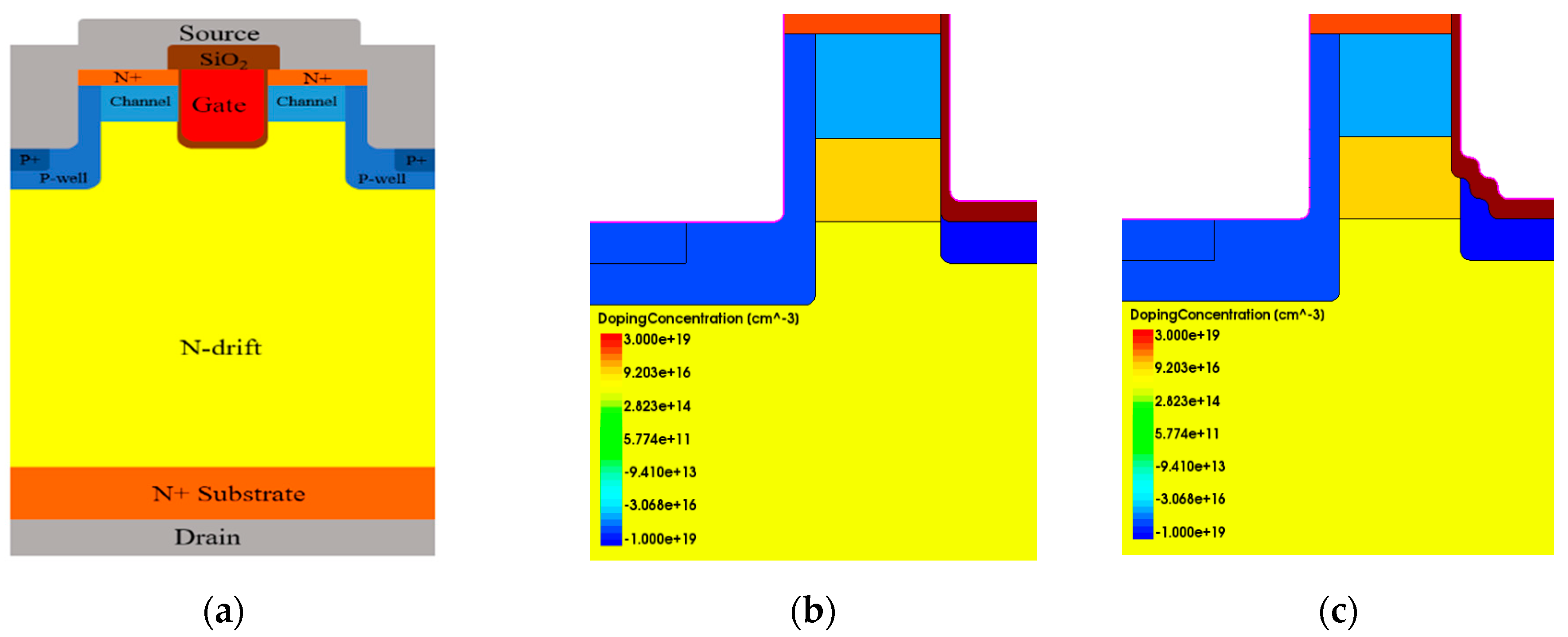

2. Device Structures and Experimental Setup

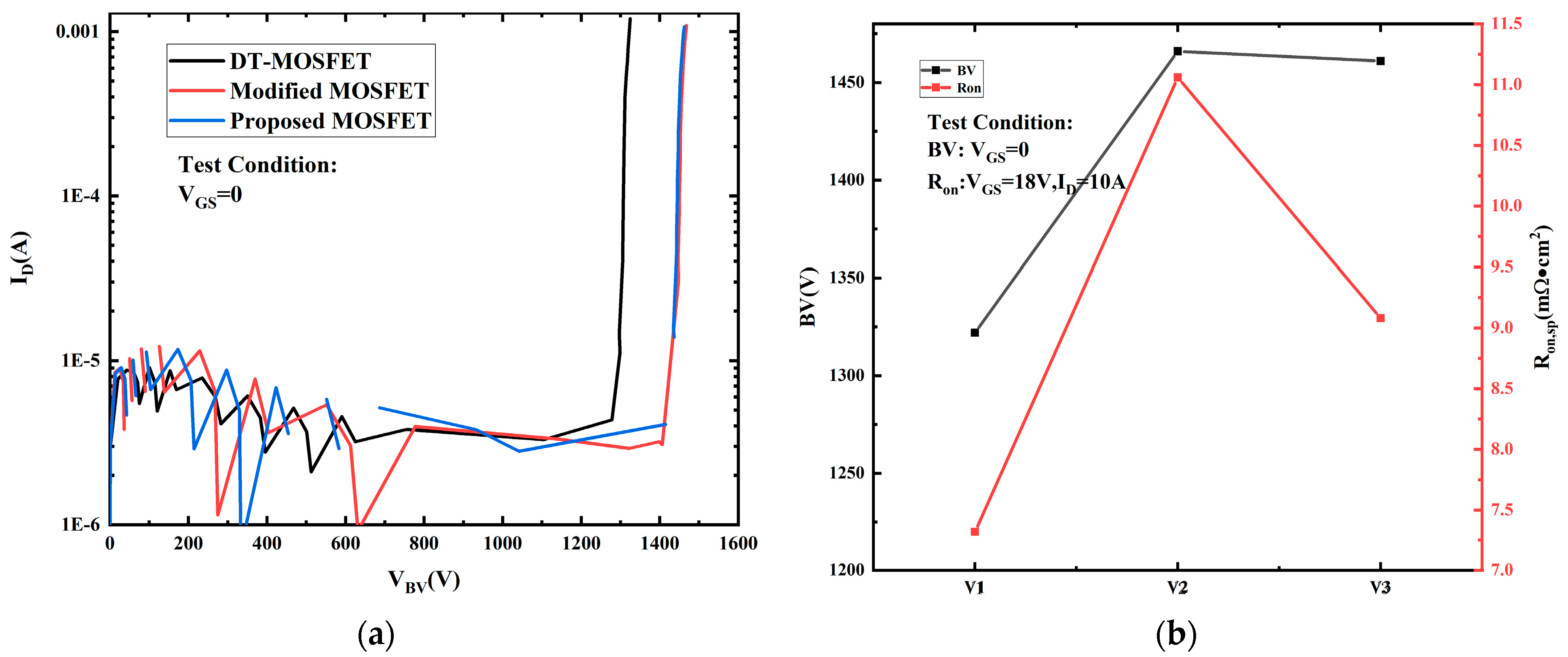

3. Parameter Degradation and Avalanche Ruggedness Analysis

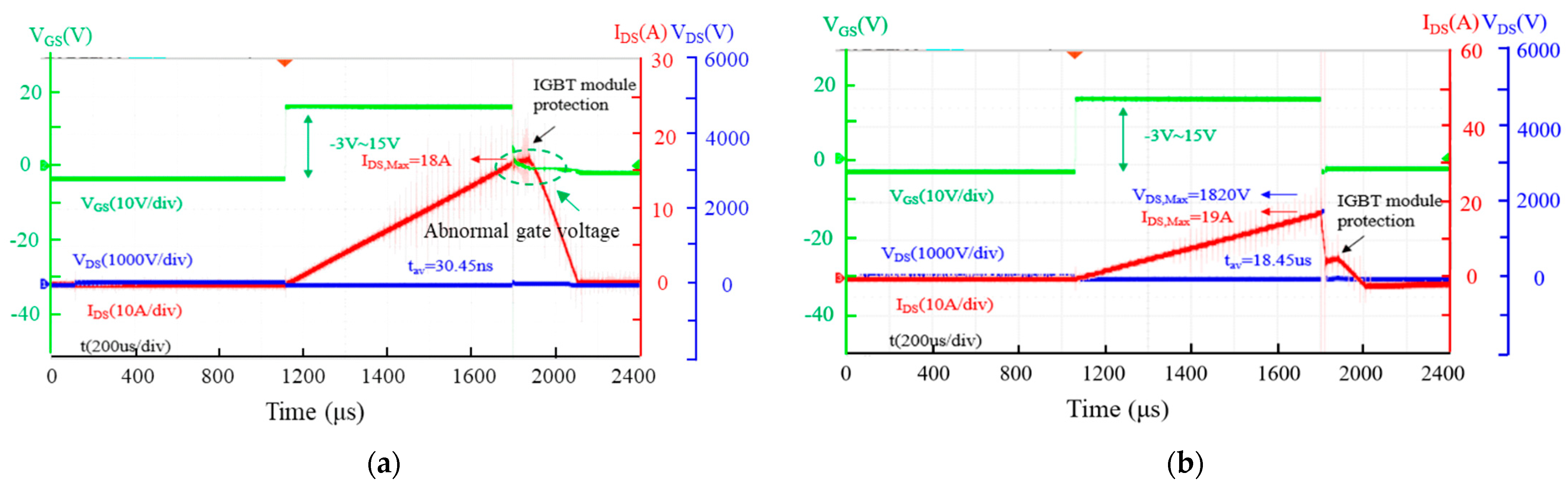

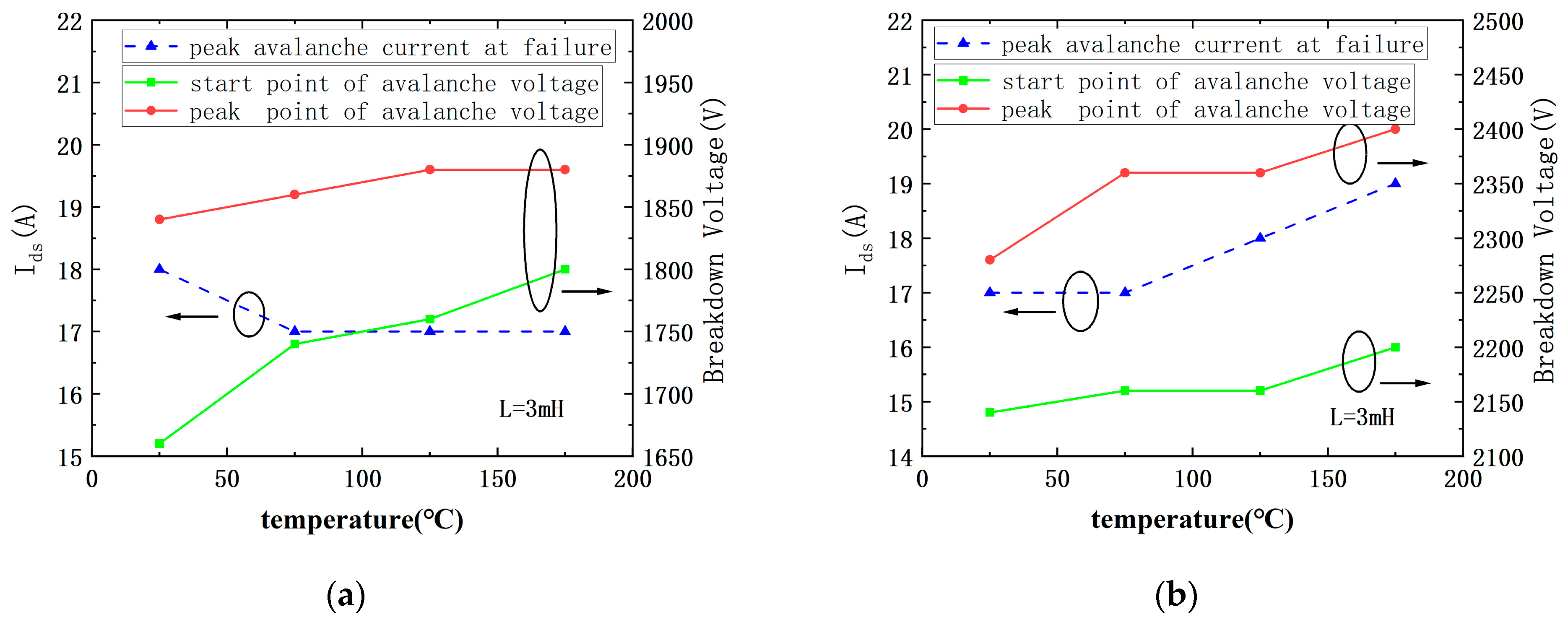

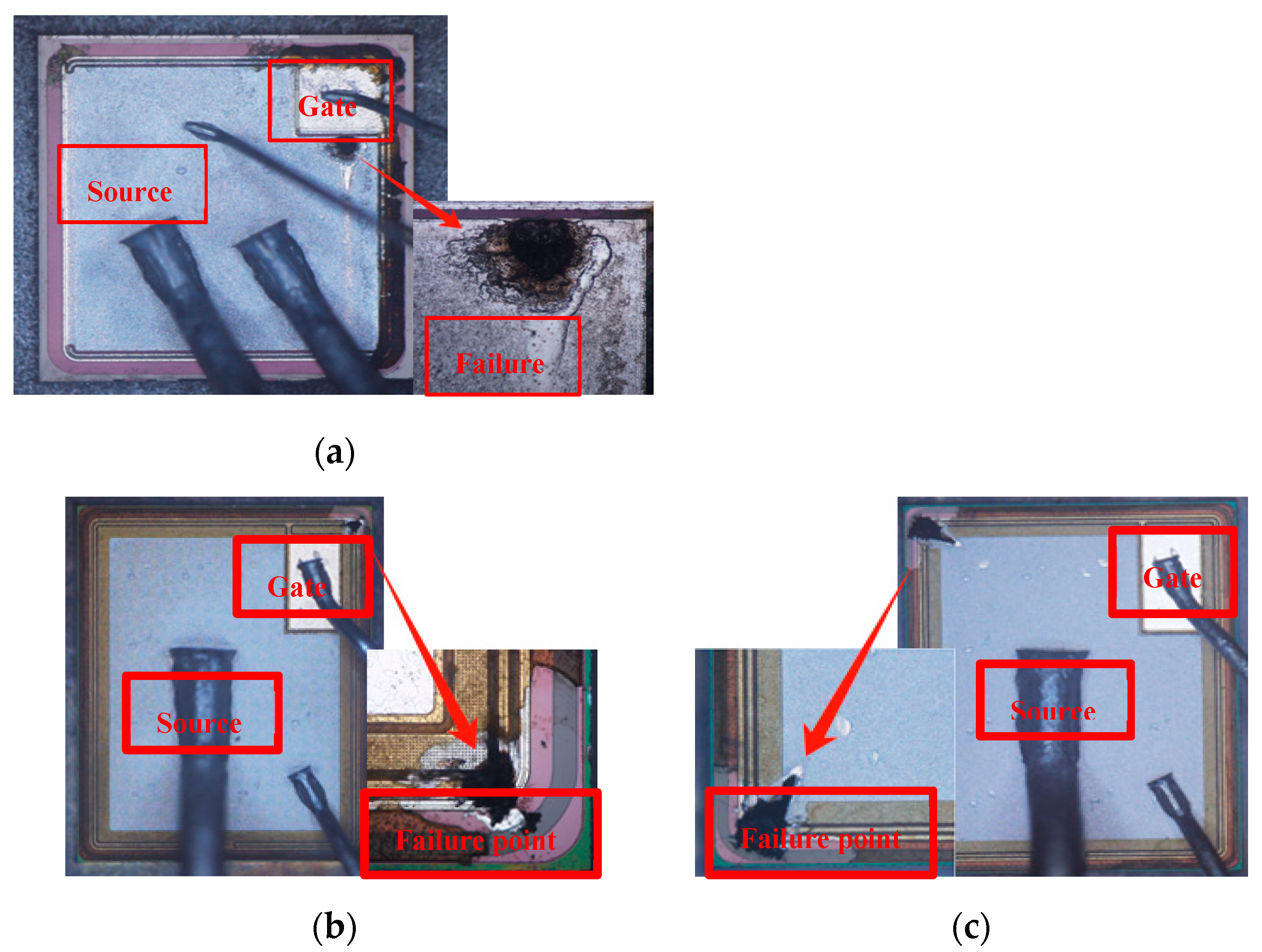

3.1. Single UIS Test

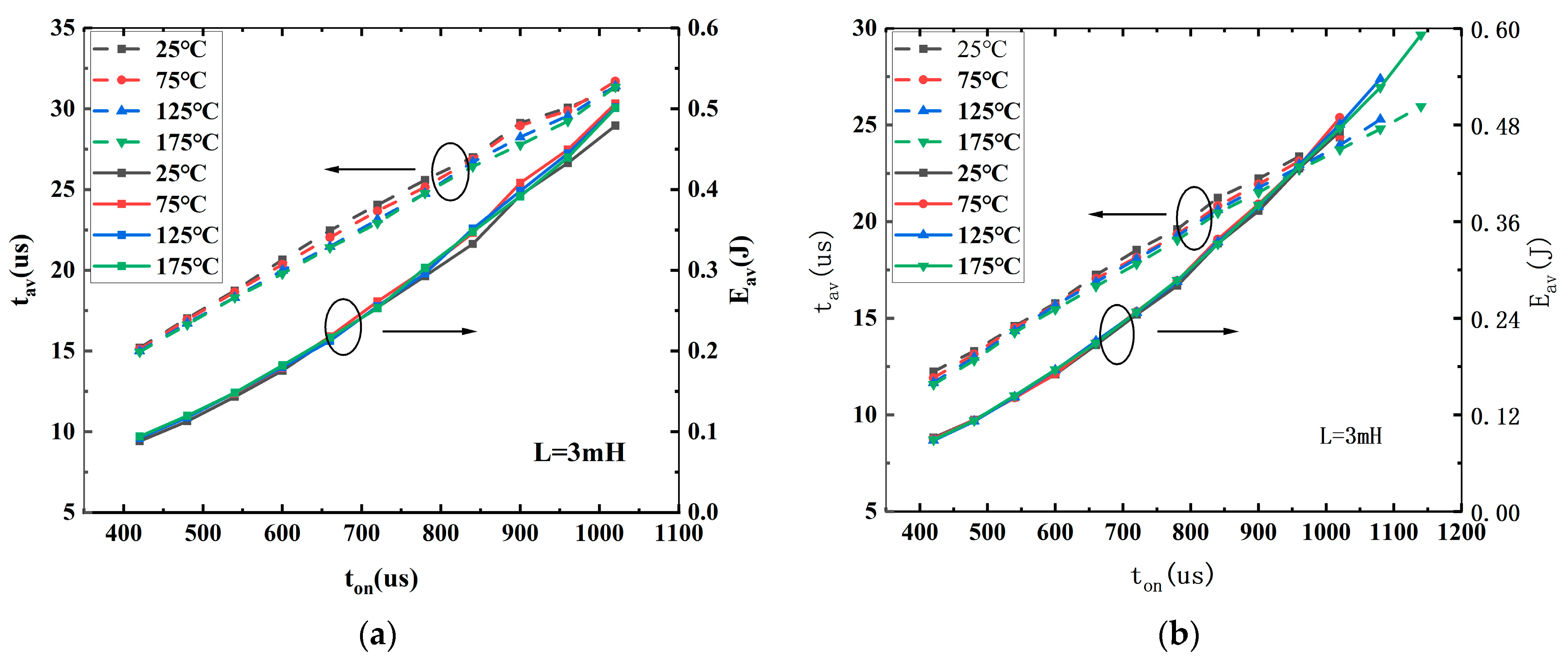

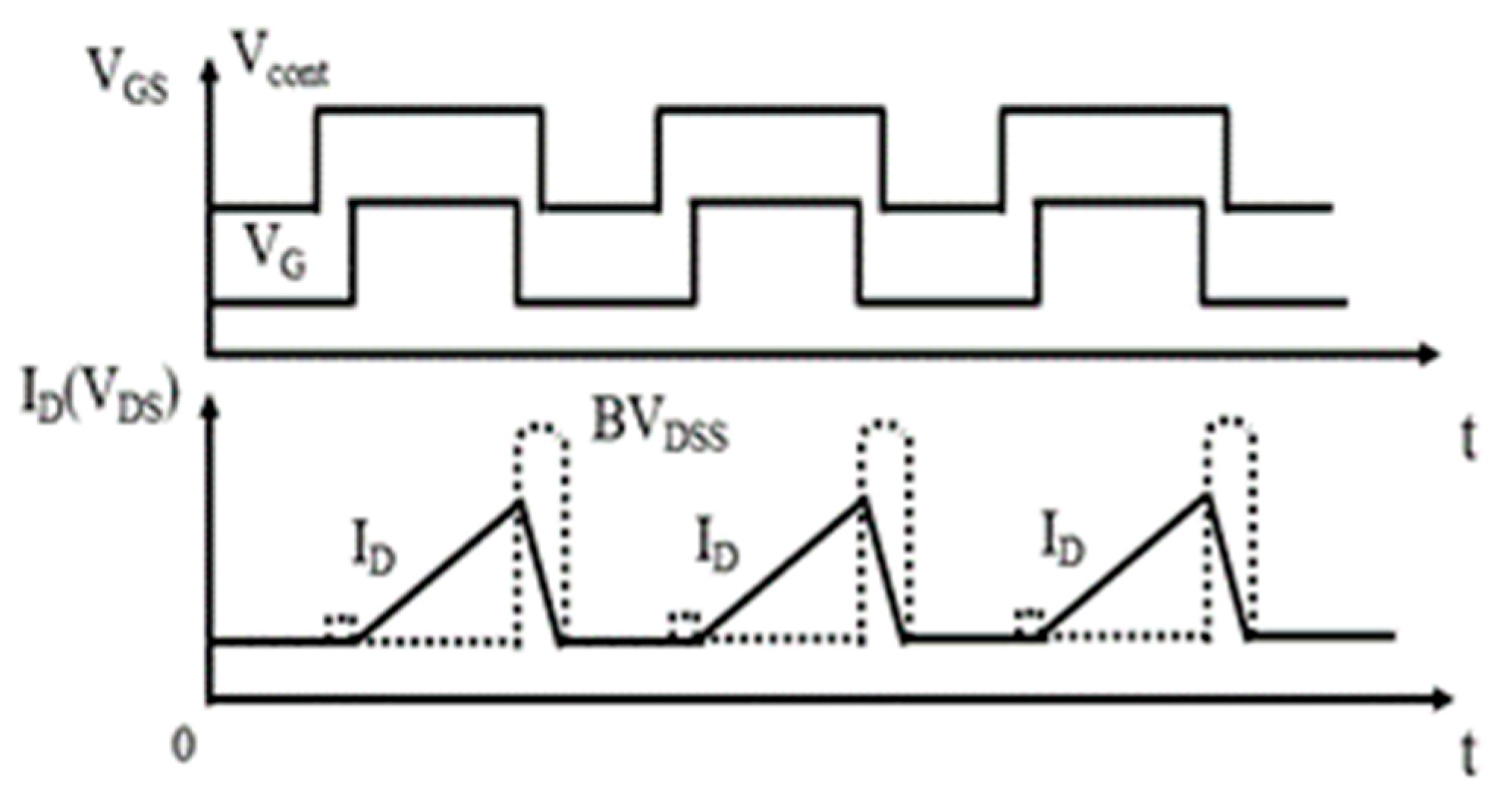

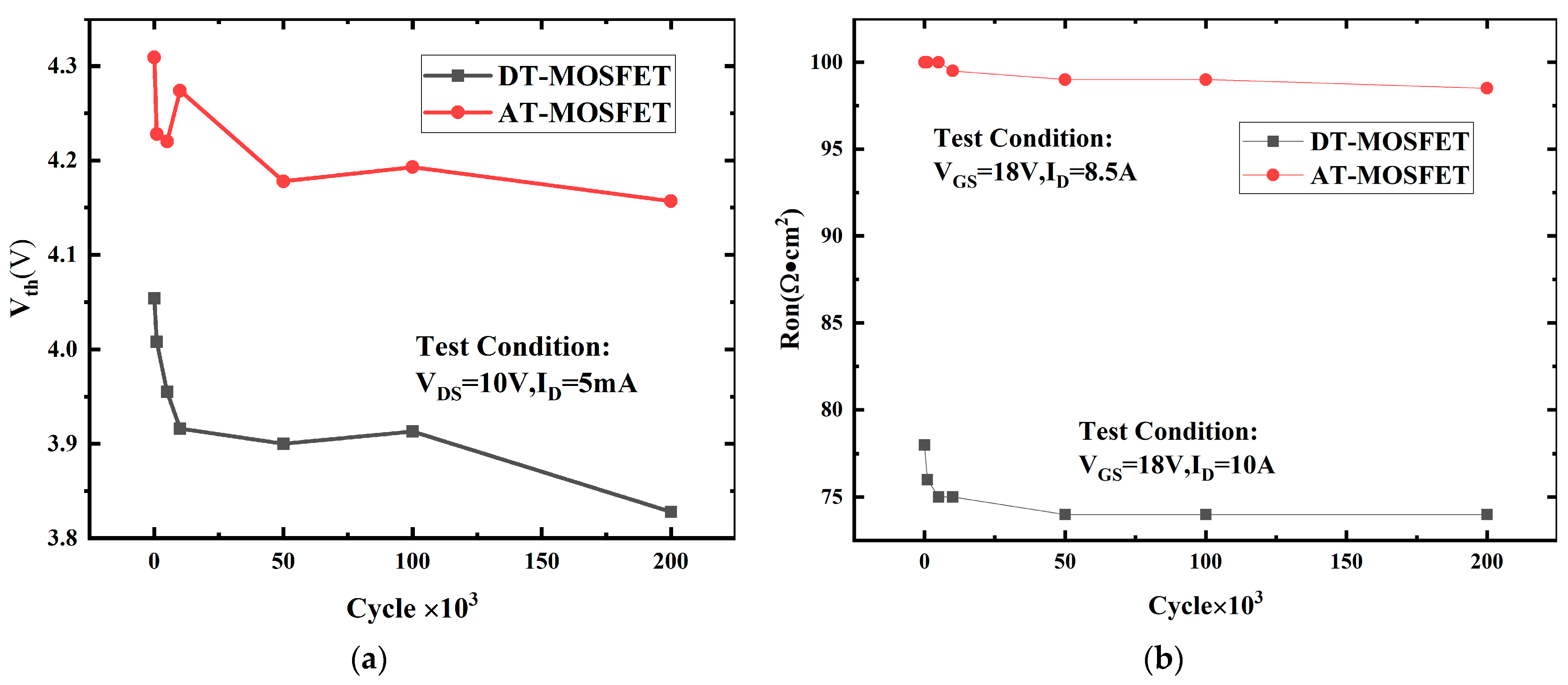

3.2. Repetitive Avalanche Stress

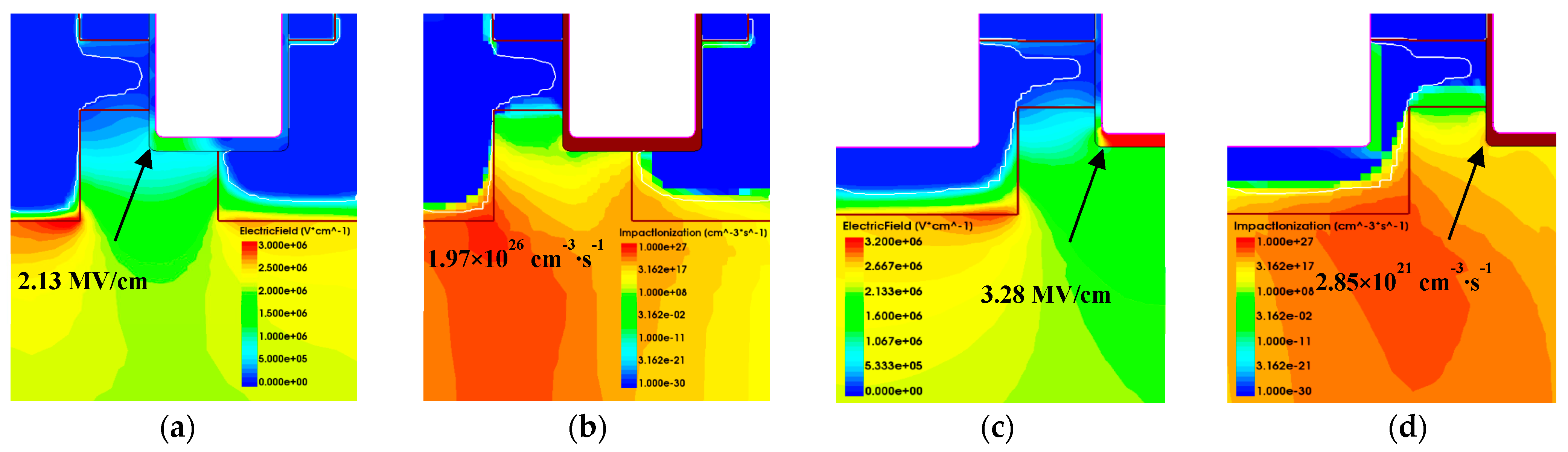

3.3. TCAD Simulation under Repetitive UIS Stress

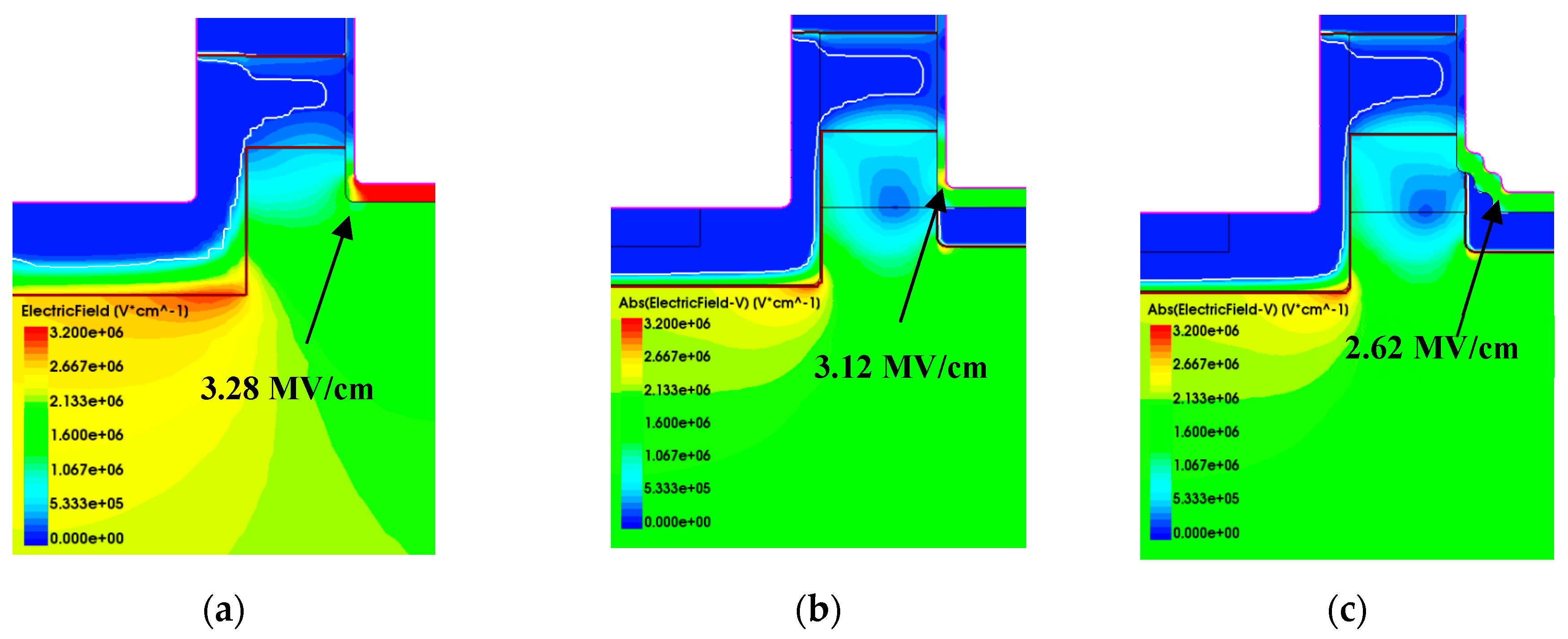

4. Optimization and Simulation

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Feil, M.W.; Waschneck, K.; Reisinger, H.; Berens, J.; Aichinger, T.; Prigann, S.; Pobegen, G.; Salmen, P.; Rescher, G.; Waldhoer, D.; et al. Gate Switching Instability in Silicon Carbide MOSFETs—Part I: Experimental. IEEE Trans. Electron Devices 2024. [Google Scholar] [CrossRef]

- Wang, H.; Lai, P.; Islam, M.Z.; Hasan, A.S.; Di Mauro, A.; Russell, R.; Feng, Z.; Chen, K.; Faruque, A.; White, T.; et al. A review of silicon carbide CMOS technology for harsh environments. Mater. Sci. Semicond. Process. 2024, 178, 108422. [Google Scholar] [CrossRef]

- Grome, C.A.; Ji, W. A Brief Review of Single-Event Burnout Failure Mechanisms and Design Tolerances of Silicon Carbide Power MOSFETs. Electronics 2024, 13, 1414. [Google Scholar] [CrossRef]

- Liu, T.; Ning, R.; Wong, T.T.Y.; Shen, Z.J. Equivalent circuit models and model validation of SiC MOSFET oscillation phenomenon. In Proceedings of the 2016 IEEE Energy Conversion Congress and Exposition (ECCE), Milwaukee, WI, USA, 18–22 September 2016; pp. 1–8. [Google Scholar]

- Schleisser, D.; Ahlers, D.; Eicher, M.; Pürschel, M. Repetitive avalanche of automotive MOSFETs. In Proceedings of the 15th European Conference on Power Electronics and Applications (EPE), Lille, France, 2–6 September 2013; pp. 1–7. [Google Scholar]

- Chou, W.; Kempitiya, A.; Vodyakho, O. Reduction of Power Losses of SiC MOSFET Based Power Modules in Automotive Traction Inverter Applications. In Proceedings of the IEEE Transportation Electrification Conference and Expo (ITEC), Long Beach, CA, USA, 13–15 June 2018; pp. 1035–1038. [Google Scholar]

- Qi, J.; Yang, X.; Li, X.; Chen, W.; Long, T.; Tian, K.; Hou, X.; Wang, X. Comprehensive Assessment of Avalanche Operating Boundary of SiC Planar/Trench MOSFET in Cryogenic Applications. IEEE Trans. Power Electron. 2021, 36, 6954–6966. [Google Scholar] [CrossRef]

- Fu, H.; Wei, J.; Liu, S.; Wu, W.; Sun, W. Repetitive-avalanche-induced Electrical Degradation and Optimization for 1.2 kV 4H-SiC MOSFETs. In Proceedings of the IEEE 26th International Symposium on Physical and Failure Analysis of Integrated Circuits (IPFA), Hangzhou, China, 2–5 July 2019; pp. 1–4. [Google Scholar]

- Liu, S.; Gu, C.; Wei, J.; Qian, Q.; Sun, W.; Huang, A.Q. Repetitive Unclamped-Inductive-Switching-Induced Electrical Parameters Degradations and Simulation Optimizations for 4H-SiC MOSFETs. IEEE Trans. Electron Devices 2016, 63, 4331–4338. [Google Scholar] [CrossRef]

- Fayyaz, A.; Castellazzi, A.; Romano, G.; Riccio, M.; Irace, A.; Urresti, J.; Wright, N. UIS failure mechanism of SiC power MOSFETs. In Proceedings of the IEEE 4th Workshop on Wide Bandgap Power Devices and Applications (WiPDA), Fayetteville, AR, USA, 7–9 November 2016; pp. 118–122. [Google Scholar]

- Gao, Z.; Guo, Q.; Ren, N.; Sheng, K. Experimental Investigation on Failure Mechanism of SiC Power MOSFETs under Single Pulse Avalanche Stress. In Proceedings of the IEEE Workshop on Wide Bandgap Power Devices and Applications in Asia (WiPDA Asia), Suita, Japan, 23–25 September 2020; pp. 1–5. [Google Scholar]

- Chen, H.; Wang, J.; Dong, R.; Yao, J.; Liang, S. Investigation on Single Pulse Avalanche Failure of 3.3 kV planar-SiC power MOSFETs. In Proceedings of the IEEE PELS Students and Young Professionals Symposium (SYPS), Shanghai, China, 27–29 August 2023; pp. 1–5. [Google Scholar]

- Ren, N.; Wang, K.L.; Wu, J.; Xu, H.; Sheng, K. Failure Mechanism Analysis of SiC MOSFETs in Unclamped Inductive Switching Conditions. In Proceedings of the 31st International Symposium on Power Semiconductor Devices and ICs (ISPSD), Shanghai, China, 19–23 May 2019; pp. 183–186. [Google Scholar]

- Kumar, A.; Parashar, S.; Baliga, J.; Bhattacharya, S. Single shot avalanche energy characterization of 10 kV, 10A 4H-SiC MOSFETs. In Proceedings of the IEEE Applied Power Electronics Conference and Exposition (APEC), San Antonio, TX, USA, 4–8 March 2018; pp. 2737–2742. [Google Scholar]

- Kelley, M.D.; Pushpakaran, B.N.; Bayne, S.B. Single-Pulse Avalanche Mode Robustness of Commercial 1200 V/80 mΩ SiC MOSFETs. IEEE Trans. Power Electron. 2017, 32, 6405–6415. [Google Scholar] [CrossRef]

- Dchar, I.; Zolkos, M.; Buttay, C.; Morel, H. Robustness of SiC MOSFET under avalanche conditions. In Proceedings of the IEEE Applied Power Electronics Conference and Exposition (APEC), Tampa, FL, USA, 26–30 March 2017; pp. 2263–2268. [Google Scholar]

- Li, K.; Sun, P.; Wu, S.; He, Z. Experimental Investigation on Avalanche Robustness of SiC MOSFETs in the Aging Process. In Proceedings of the 4th International Conference on Power and Energy Technology (ICPET), Beijing, China, 28–31 July 2022; pp. 1227–1231. [Google Scholar]

- Bai, Z.; Tang, X.; Xie, S.; He, Y.; Yuan, H.; Song, Q.; Zhang, Y. Investigation on Single Pulse Avalanche Failure of 1200-V SiC MOSFETs via Optimized Thermoelectric Simulation. IEEE Trans. Electron Devices 2021, 68, 1168–1175. [Google Scholar] [CrossRef]

- Wang, J.; Jiang, X. Review and analysis of SiC MOSFETs’ ruggedness and reliability. IET Power Electron. 2020, 13, 445–455. [Google Scholar] [CrossRef]

- Wei, J.; Liu, S.; Yang, L.; Tang, L.; Lou, R.; Li, T.; Fang, J.; Li, S.; Zhang, C.; Sun, W. Investigations on the Degradations of Double-Trench SiC Power MOSFETs under Repetitive Avalanche Stress. IEEE Trans. Electron Devices 2019, 66, 546–552. [Google Scholar] [CrossRef]

- Wei, J.; Wei, Z.; Fu, H.; Cao, J.; Wu, T.; Sun, J.; Zhu, X.; Li, S.; Zhang, L.; Liu, S.; et al. Review on the Reliability Mechanisms of SiC Power MOSFETs: A Comparison between Planar-Gate and Trench-Gate Structures. IEEE Trans. Power Electron. 2023, 38, 8990–9005. [Google Scholar] [CrossRef]

- Yao, K.; Yano, H.; Iwamuro, N. Impact of Negative Gate Bias and Inductive Load on the Single-Pulse Avalanche Capability of 1200-V SiC Trench MOSFETs. IEEE Trans. Electron Devices 2022, 69, 637–643. [Google Scholar] [CrossRef]

- Tsuji, T.; Iwamuro, N. An investigation of avalanche ruggedness and failure mechanisms of 4H SiC trench MOSFETs in unclamped inductive switching by varying load inductances over a wide range. Jpn. J. Appl. Phys. 2023, 62, 041001. [Google Scholar] [CrossRef]

- Hu, J.; Alatise, O.; Gonzalez, J.A.O.; Bonyadi, R.; Alexakis, P.; Ran, L.; Mawby, P. Robustness and Balancing of Parallel-Connected Power Devices: SiC Versus CoolMOS. IEEE Trans. Ind. Electron. 2016, 63, 2092–2102. [Google Scholar] [CrossRef]

- Deng, X.; Zhu, H.; Li, X.; Tong, X.; Gao, S.; Wen, Y.; Bai, S.; Chen, W.; Zhou, K.; Zhang, B. Investigation and Failure Mode of Asymmetric and Double Trench SiC MOSFETs under Avalanche Conditions. IEEE Trans. Power Electron. 2020, 35, 8524–8531. [Google Scholar] [CrossRef]

| Parameters | DT-MOSFET | AT-MOSFET | ||||

|---|---|---|---|---|---|---|

| 1 mH | 3 mH | 10 mH | 1 mH | 3 mH | 10 mH | |

| EAV | 0.19 J | 0.47 J | 0.57 J | 0.46 J | 0.53 J | 0.67 J |

| IDS,max | 19 A | 18 A | 10.5 A | 30 A | 19 A | 11 A |

| VDS,Max | 2240 V | 2280 V | 2320 V | 1840 V | 1820 V | 1800 V |

| tAV | 3.13 μs | 30.45 ns | 49.35 μs | 15.23 μs | 18.45 μs | 40 μs |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Liu, L.; Guo, J.; Shi, Y.; Zeng, K.; Li, G. A Comprehensive Analysis of Unclamped-Inductive-Switching-Induced Electrical Parameter Degradations and Optimizations for 4H-SiC Trench Metal-Oxide-Semiconductor Field-Effect Transistor Structures. Micromachines 2024, 15, 772. https://doi.org/10.3390/mi15060772

Liu L, Guo J, Shi Y, Zeng K, Li G. A Comprehensive Analysis of Unclamped-Inductive-Switching-Induced Electrical Parameter Degradations and Optimizations for 4H-SiC Trench Metal-Oxide-Semiconductor Field-Effect Transistor Structures. Micromachines. 2024; 15(6):772. https://doi.org/10.3390/mi15060772

Chicago/Turabian StyleLiu, Li, Jingqi Guo, Yiheng Shi, Kai Zeng, and Gangpeng Li. 2024. "A Comprehensive Analysis of Unclamped-Inductive-Switching-Induced Electrical Parameter Degradations and Optimizations for 4H-SiC Trench Metal-Oxide-Semiconductor Field-Effect Transistor Structures" Micromachines 15, no. 6: 772. https://doi.org/10.3390/mi15060772