Positive Bias Temperature Instability in SiC-Based Power MOSFETs

Abstract

1. Introduction

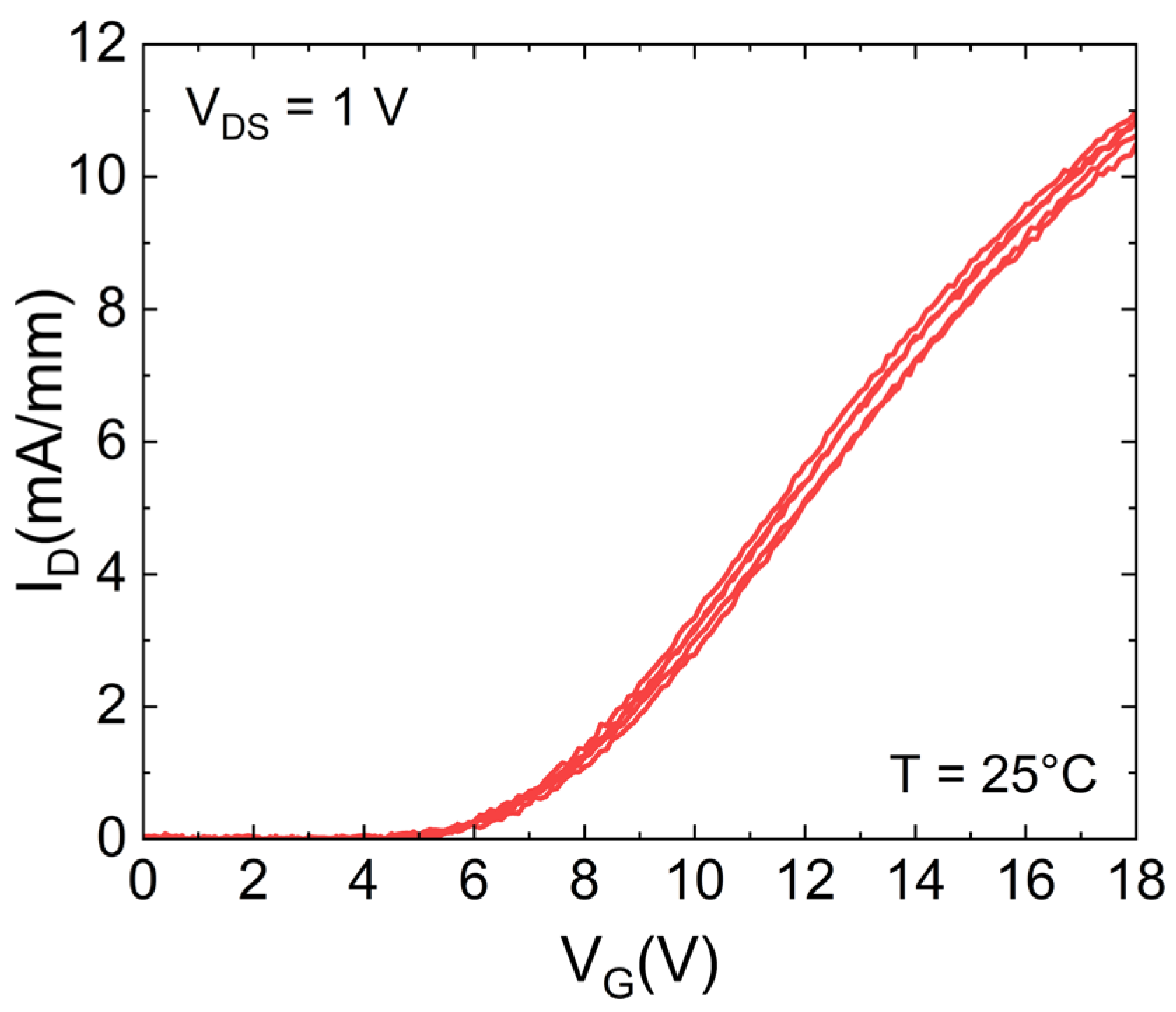

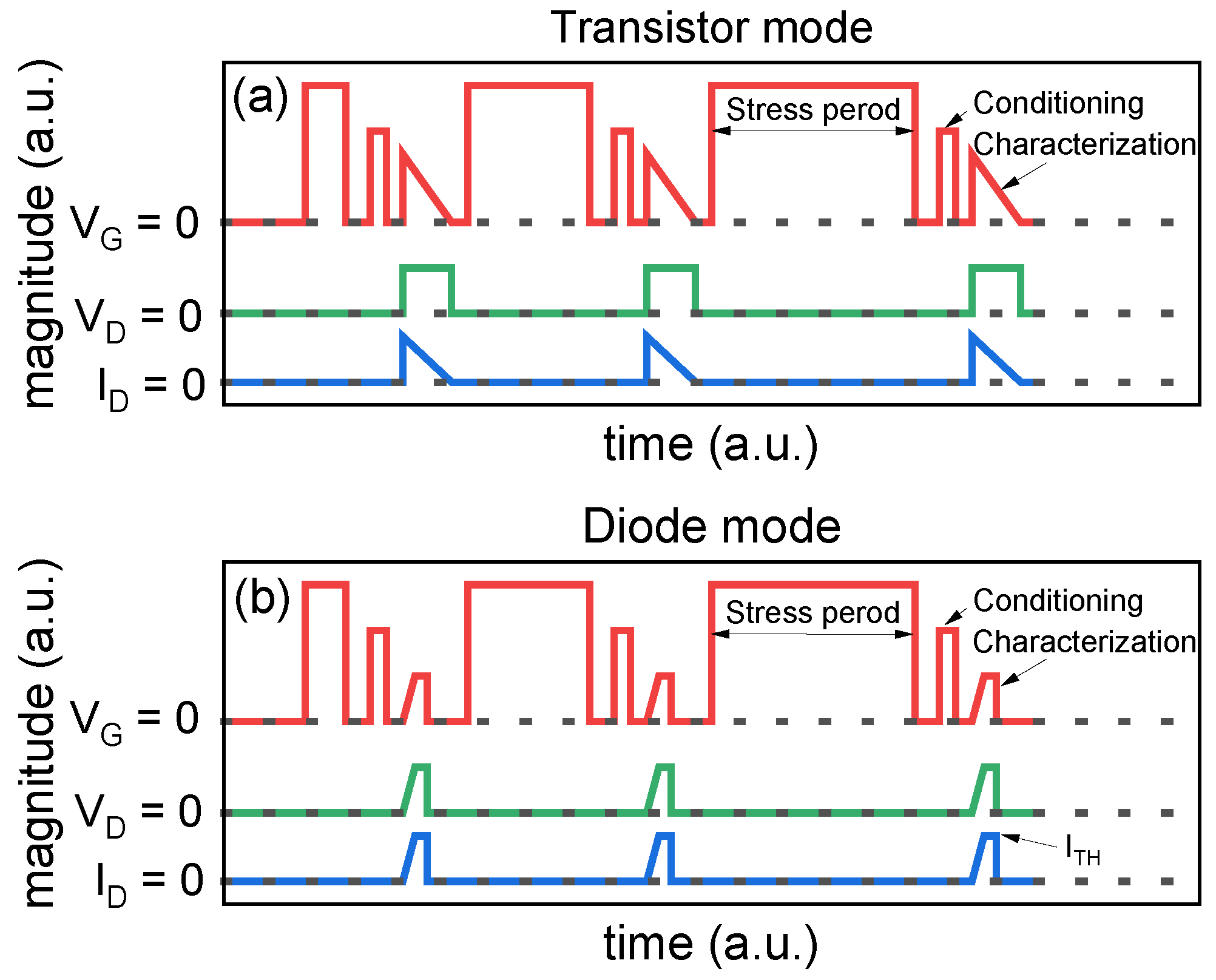

2. Devices under Test (DUTs) and BTI Characterization Techniques

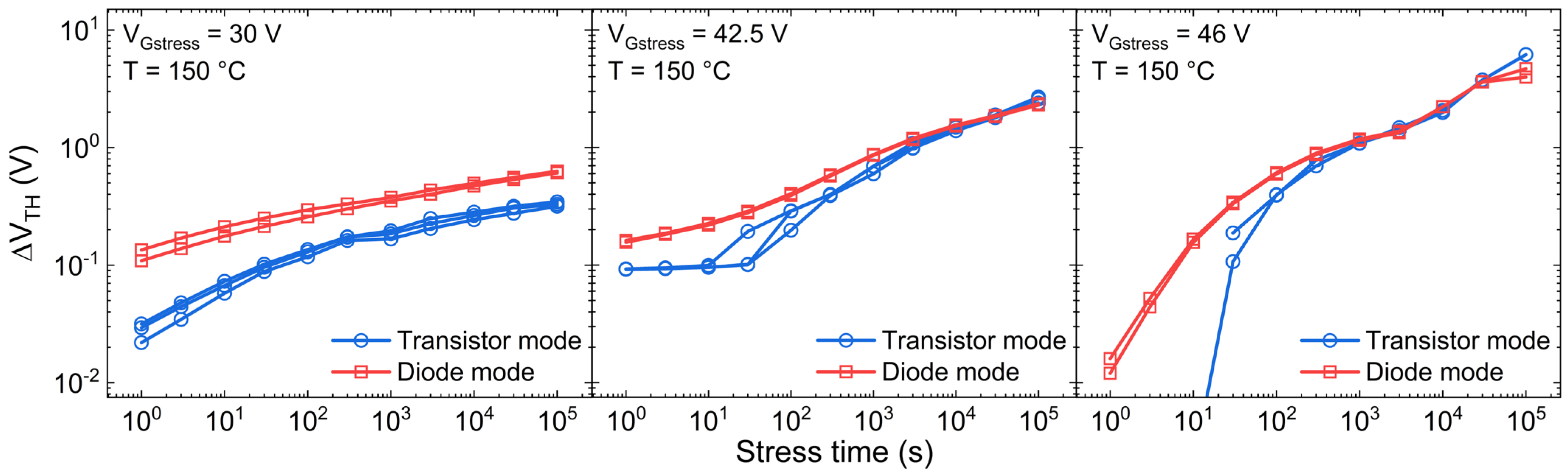

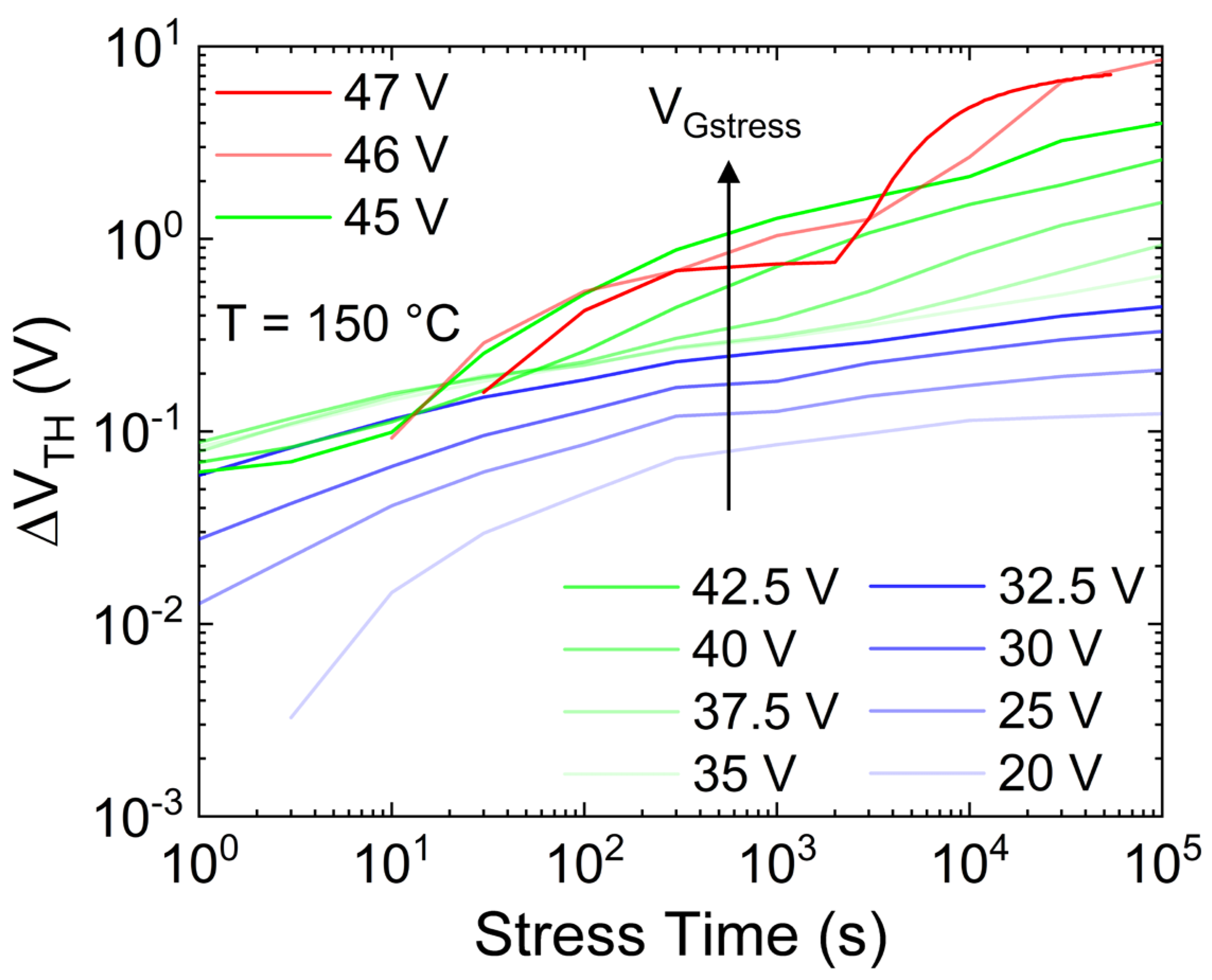

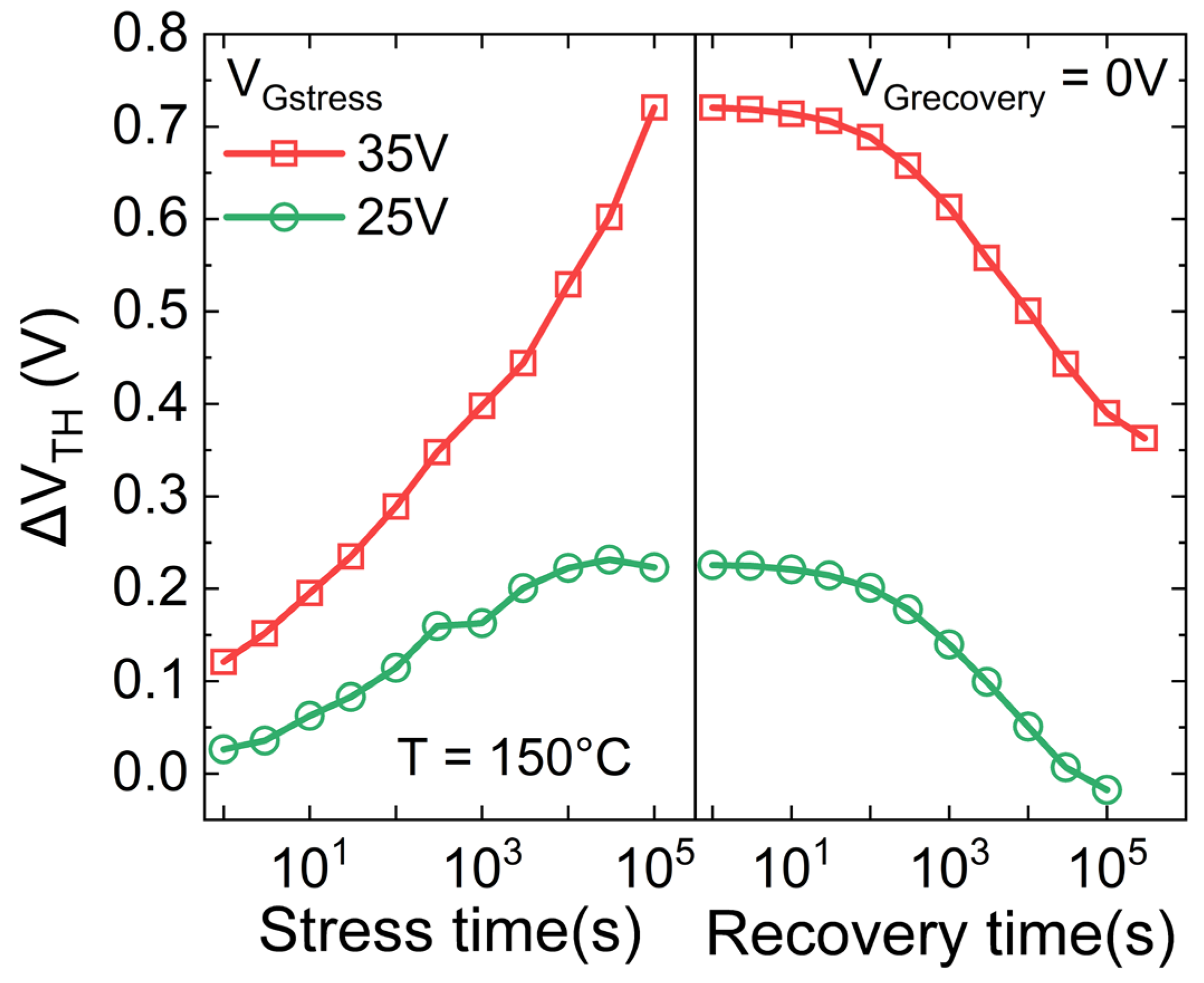

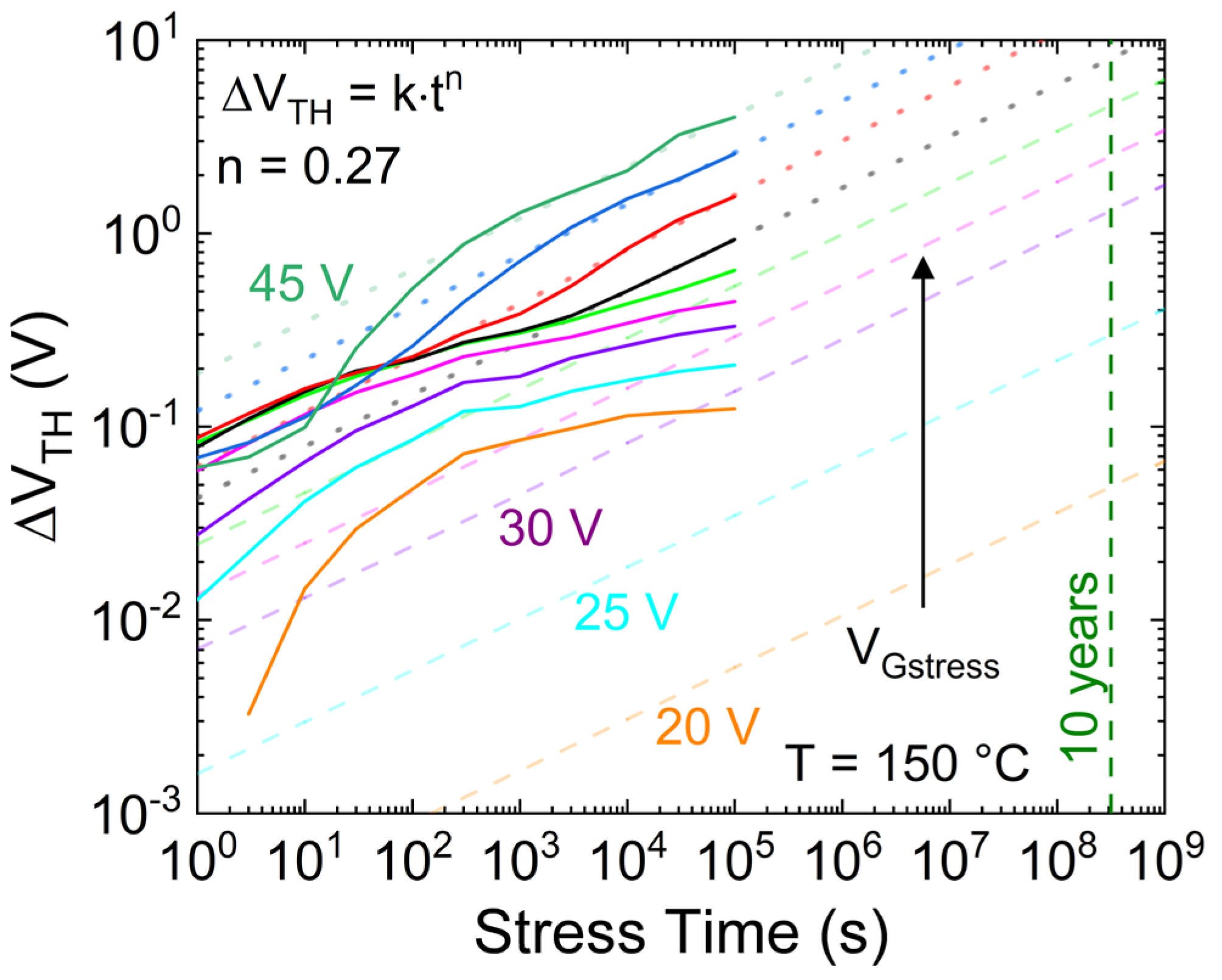

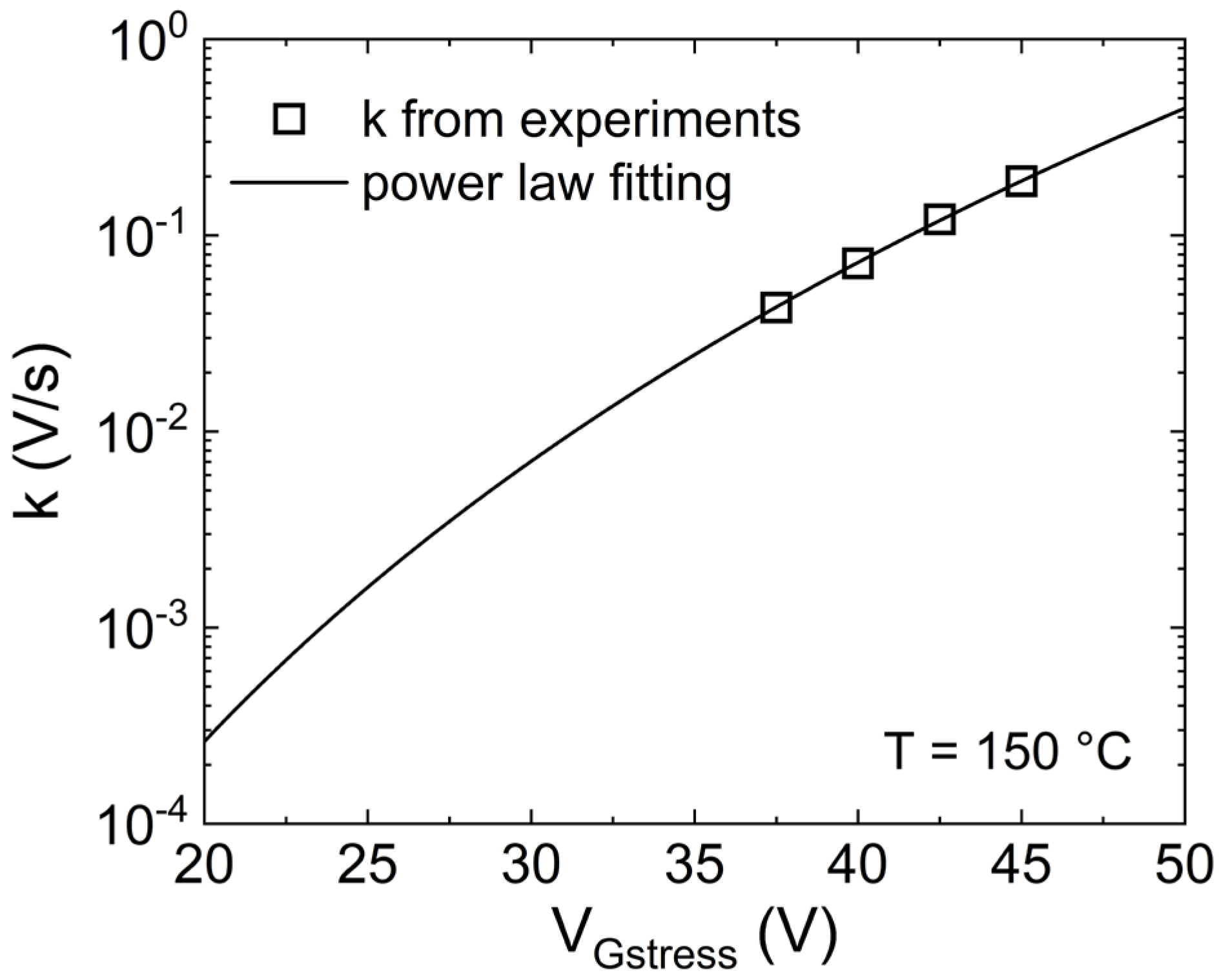

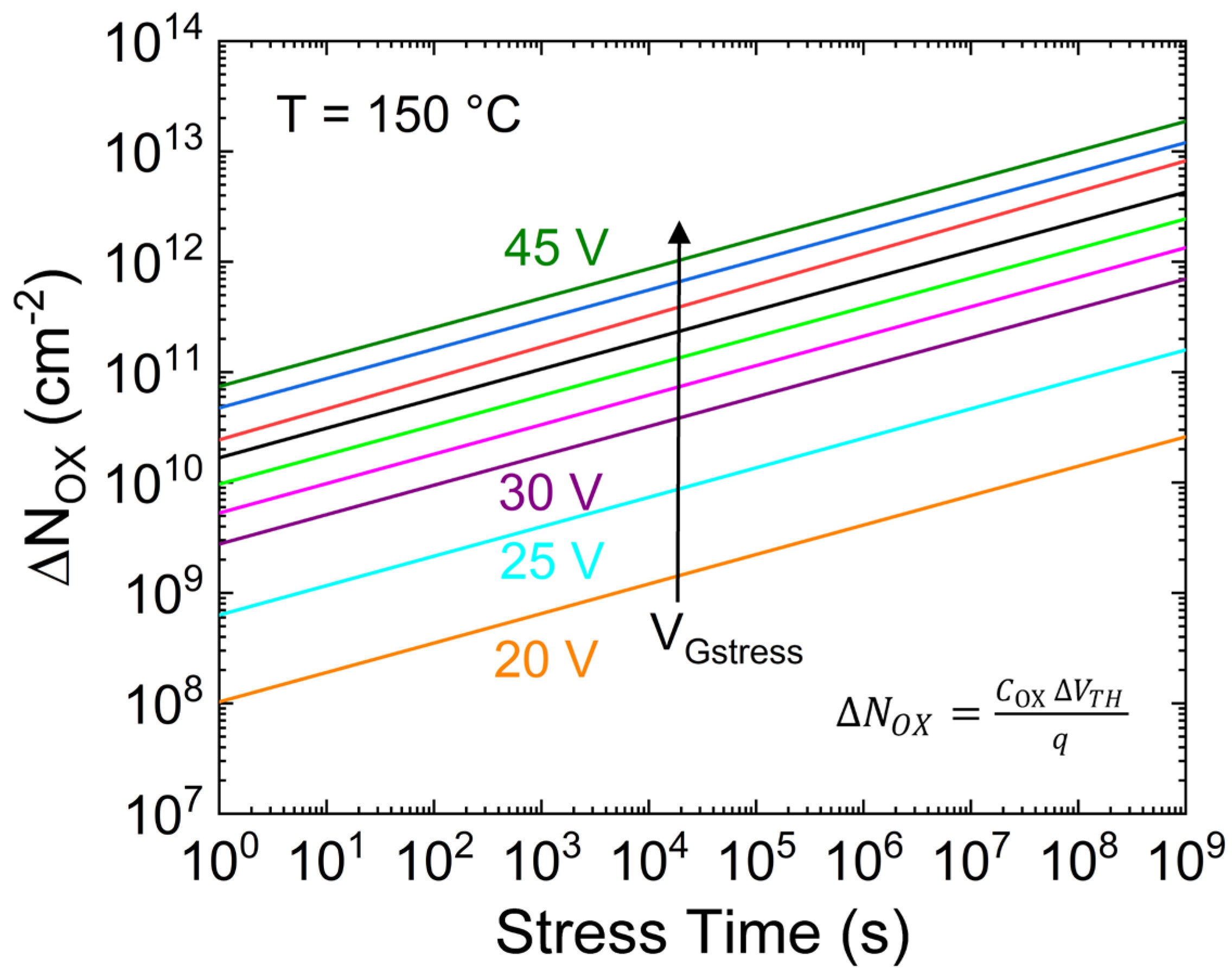

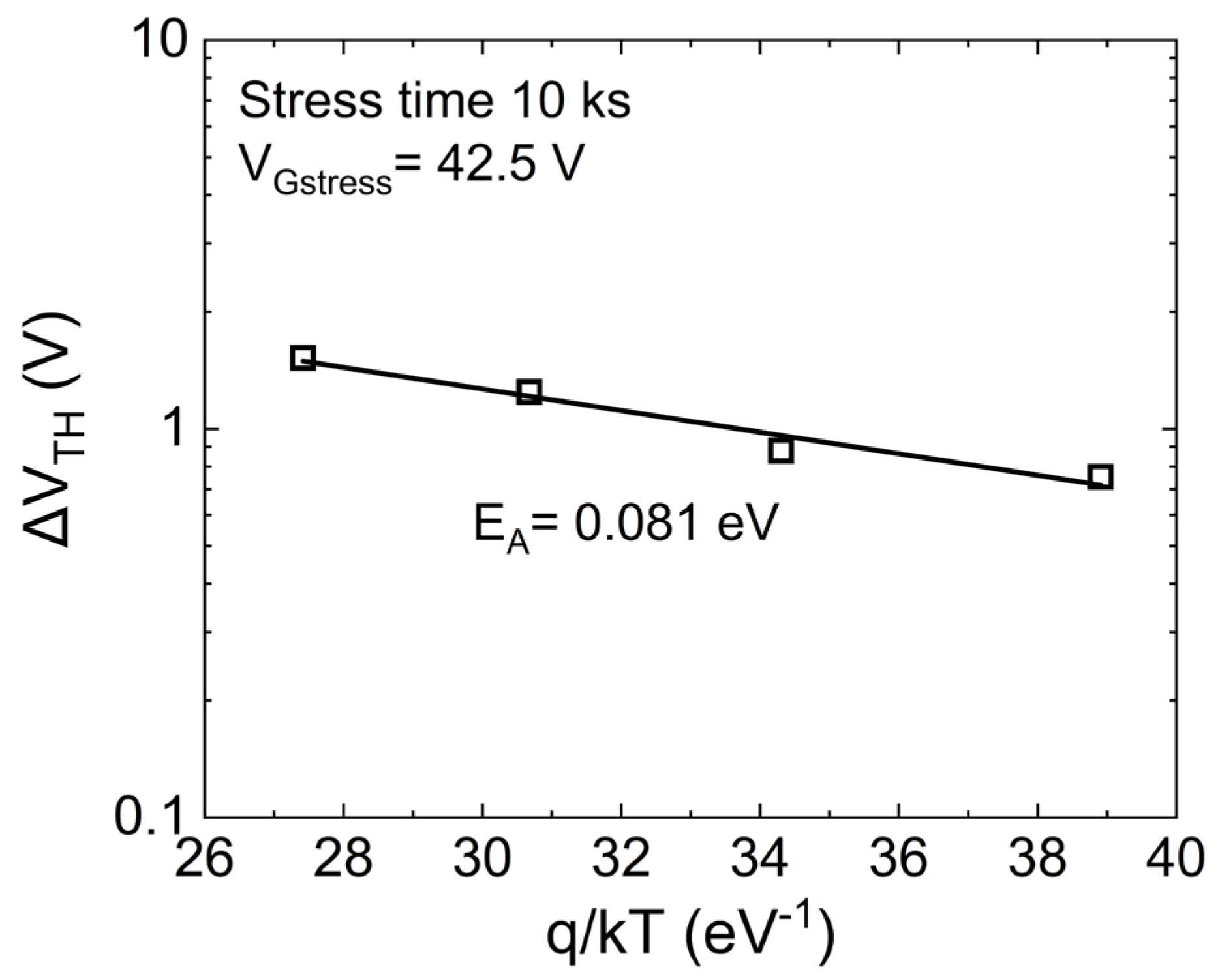

3. Results and Discussion

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Mysiński, W. SiC mosfet transistors in power analog application. In Proceedings of the 2017 19th European Conference on Power Electronics and Applications (EPE’17 ECCE Europe), Warsaw, Poland, 11–14 September 2017; pp. P.1–P.7. [Google Scholar] [CrossRef]

- Kumar, K.; Bertoluzzo, M.; Buja, G. Impact of SiC MOSFET traction inverters on compact-class electric car range. In Proceedings of the 2014 IEEE International Conference on Power Electronics, Drives and Energy Systems (PEDES), Mumbai, India, 16–19 December 2014; pp. 1–6. [Google Scholar] [CrossRef]

- Hatanaka, A.; Kageyama, H.; Masuda, T. A 160-kW high-efficiency photovoltaic inverter with paralleled SiC-MOSFET modules for large-scale solar power. In Proceedings of the 2015 IEEE International Telecommunications Energy Conference (INTELEC), Osaka, Japan, 18–22 October 2015; pp. 1–5. [Google Scholar] [CrossRef]

- Marcuzzi, A.; Favero, D.; Santi, C.D.; Meneghesso, G.; Zanoni, E.; Meneghini, M. A Review of SiC Commercial Devices for Automotive: Properties and Challenges. In Proceedings of the 2023 AEIT International Conference on Electrical and Electronic Technologies for Automotive (AEIT AUTOMOTIVE), Modena, Italy, 17–19 July 2023; pp. 1–6. [Google Scholar] [CrossRef]

- Alharbi, S.S.; Alharbi, S.S.; Al-bayati, A.M.S.; Matin, M. A comparative performance evaluation of Si IGBT, SiC JFET, and SiC MOSFET power devices for a non-isolated DC-DC boost converter. In Proceedings of the 2017 North American Power Symposium (NAPS), Morgantown, WV, USA, 17–19 September 2017; pp. 1–6. [Google Scholar] [CrossRef]

- Liu, T.; Hu, S.; Wang, J.A.; Guo, G.; Luo, J.; Wang, Y.; Guo, J.; Huo, Y. An Investigation of Electric Field and Breakdown Voltage Models for a Deep Trench Superjunction SiC VDMOS. IEEE Access 2019, 7, 145118–145123. [Google Scholar] [CrossRef]

- Yu, H.; Jiang, X.; Chen, J.; Shen, Z.J.; Wang, J. Comparative Study of Temperature Sensitive Electrical Parameters for Junction Temperature Monitoring in SiC MOSFET and Si IGBT. In Proceedings of the 2020 IEEE 9th International Power Electronics and Motion Control Conference (IPEMC2020-ECCE Asia), Nanjing, China, 29 November–2 December 2020; pp. 905–909. [Google Scholar] [CrossRef]

- Karami, M.; Tallam, R. Thermal Characterization of SiC Modules for Variable Frequency Drives. In Proceedings of the 2019 IEEE Energy Conversion Congress and Exposition (ECCE), Baltimore, MD, USA, 29 September–3 October 2019; pp. 4944–4949. [Google Scholar] [CrossRef]

- Biela, J.; Schweizer, M.; Waffler, S.; Kolar, J.W. SiC versus Si—Evaluation of Potentials for Performance Improvement of Inverter and DC–DC Converter Systems by SiC Power Semiconductors. IEEE Trans. Ind. Electron. 2011, 58, 2872–2882. [Google Scholar] [CrossRef]

- Bashar, E.; Wu, R.; Agbo, N.; Mendy, S.; Jahdi, S.; Gonzalez, J.O.; Alatise, O. Comparison of Short Circuit Failure Modes in SiC Planar MOSFETs, SiC Trench MOSFETs and SiC Cascode JFETs. In Proceedings of the 2021 IEEE 8th Workshop on Wide Bandgap Power Devices and Applications (WiPDA), Redondo Beach, CA, USA, 7–11 November 2021; pp. 384–388. [Google Scholar] [CrossRef]

- Singh, R.; Grummel, B.; Sundaresan, S. Short circuit robustness of 1200 V SiC switches. In Proceedings of the 2015 IEEE 3rd Workshop on Wide Bandgap Power Devices and Applications (WiPDA), Blacksburg, VA, USA, 2–4 November 2015; pp. 1–4. [Google Scholar] [CrossRef]

- Puschkarsky, K.; Grasser, T.; Aichinger, T.; Gustin, W.; Reisinger, H. Review on SiC MOSFETs High-Voltage Device Reliability Focusing on Threshold Voltage Instability. IEEE Trans. Electron Devices 2019, 66, 4604–4616. [Google Scholar] [CrossRef]

- Ghosh, A.K.; Hao, J.; Cook, M.; Suliman, S.A.; Wang, X.; Awadelkarim, O.O. Threshold-voltage bias-instability in SiC MOSFETs: Effects of stress temperature and level on oxide charge buildup and recovery. Semicond. Sci. Technol. 2022, 37. [Google Scholar] [CrossRef]

- Aichinger, T.; Rescher, G.; Pobegen, G. Threshold voltage peculiarities and bias temperature instabilities of SiC MOSFETs. Microelectron. Reliab. 2018, 80, 68–78. [Google Scholar] [CrossRef]

- Fiorenza, P.; Giannazzo, F.; Cascino, S.; Saggio, M.; Roccaforte, F. Identification of two trapping mechanisms responsible of the threshold voltage variation in SiO2/4H-SiC MOSFETs. Appl. Phys. Lett. 2020, 117, 103502. [Google Scholar] [CrossRef]

- Moghadam, H.A.; Dimitrijev, S.; Han, J.; Haasmann, D.; Aminbeidokhti, A. Transient-Current Method for Measurement of Active Near-Interface Oxide Traps in 4H-SiC MOS Capacitors and MOSFETs. IEEE Trans. Electron Devices 2015, 62, 2670–2674. [Google Scholar] [CrossRef]

- Carangelo, G.; Reggiani, S.; Consentino, G.; Crupi, F.; Meneghesso, G. TCAD modeling of bias temperature instabilities in SiC MOSFETs. Solid-State Electron. 2021, 185, 108067. [Google Scholar] [CrossRef]

- Miccoli, C.; Iucolano, F. Study of oxide trapping in SiC MOSFETs by means of TCAD simulations. Mater. Sci. Semicond. Process. 2019, 97, 40–43, ISSN 1369-8001. [Google Scholar] [CrossRef]

- Liang, Y.; Zhang, Y.; Zhang, J.; He, X.; Zhao, Y.; Cui, M.; Wen, H.; Wang, M.; Liu, W. Characterization of Oxide Trapping in SiC MOSFETs Under Positive Gate Bias. IEEE J. Electron Devices Soc. 2022, 10, 920–926. [Google Scholar] [CrossRef]

- Pande, P.; Dimitrijev, S.; Haasmann, D.; Amini Moghadam, H.; Tanner, P.; Han, J. Energy-Localized Near-Interface Traps Active in the Strong-Accumulation Region of 4H-SiC MOS Capacitors. IEEE Trans. Electron Devices 2019, 66, 1704–1709. [Google Scholar] [CrossRef]

- Cai, Y.; Xu, H.; Sun, P.; Zhao, Z.; Chen, Z. Influence of the Interface Traps Distribution on I-V and C-V Characteristics of SiC MOSFET Evaluated by TCAD Simulations. In Proceedings of the 2021 IEEE Workshop on Wide Bandgap Power Devices and Applications in Asia (WiPDA Asia), Wuhan, China, 25–27 August 2021; pp. 398–402. [Google Scholar] [CrossRef]

- Nayak, S.; Lodha, S.; Ganguly, S. Effect of interface traps on SiC-based power D-MOSFET transient behaviour. In Proceedings of the 2021 International Semiconductor Conference (CAS), Sinaia, Romania, 6–8 October 2021; pp. 179–182. [Google Scholar] [CrossRef]

- Spejo, L.B.; Lucidi, S.; Puydinger Dos Santos, M.V.; Diniz, J.A.; Minamisawa, R.A. Interface Trap Density of Commercial 1.7 kV SiC Power MOSFETs. In Proceedings of the 2023 37th Symposium on Microelectronics Technology and Devices (SBMicro), Rio de Janeiro, Brazil, 28 August–1 September 2023; pp. 1–4. [Google Scholar] [CrossRef]

- Gurfinkel, M.; Xiong, H.; Cheung, K.; Suehle, J.; Bernstein, J.; Shapira, Y.; Lelis, A.; Habersat, D.; Goldsman, N. Characterization of Transient Gate Oxide Trapping in SiC MOSFETs Using Fast I–V Techniques. IEEE Trans. Electron Devices 2008, 55, 2004–2012. [Google Scholar] [CrossRef]

- Lelis, A.J.; Green, R.; Habersat, D.B. SiC MOSFET threshold-stability issues. Mater. Sci. Semicond. Process. 2018, 78, 32–37. [Google Scholar] [CrossRef]

- Ghosh, A.; Hao, J.; Cook, M.; Kendrick, C.; Suliman, S.A.; Hall, G.D.; Kopley, T.; Awadelkarim, O.O. Studies of Bias Temperature Instabilities in 4H-SiC DMOSFETs. In Proceedings of the 2020 IEEE International Reliability Physics Symposium (IRPS), Dallas, TX, USA, 28 April–30 May 2020; pp. 1–4. [Google Scholar] [CrossRef]

- Volosov, V.; Cascino, S.; Saggio, M.; Imbruglia, A.; Di Giovanni, F.; Fiegna, C.; Sangiorgi, E.; Tallarico, A.N. Role of interface/border traps on the threshold voltage instability of SiC power transistors. Solid-State Electron. 2023, 207, 108699. [Google Scholar] [CrossRef]

- JEP 184; Guideline for Evaluating Bias Temperature Instability of Silicon Carbide Metal-Oxide-Semiconductor Devices for Power Electronic Conversion. JEDEC: Arlington, VA, USA, 2021.

- Available online: https://www.st.com/resource/en/datasheet/sctw35n65g2vag.pdf (accessed on 1 June 2024).

- JEP 183; Guidelines for Measuring the Threshold Voltage (VT) of SiC MOSFETs. JEDEC: Arlington, VA, USA, 2023.

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Volosov, V.; Bevilacqua, S.; Anoldo, L.; Tosto, G.; Fontana, E.; Russo, A.-l.; Fiegna, C.; Sangiorgi, E.; Tallarico, A.N. Positive Bias Temperature Instability in SiC-Based Power MOSFETs. Micromachines 2024, 15, 872. https://doi.org/10.3390/mi15070872

Volosov V, Bevilacqua S, Anoldo L, Tosto G, Fontana E, Russo A-l, Fiegna C, Sangiorgi E, Tallarico AN. Positive Bias Temperature Instability in SiC-Based Power MOSFETs. Micromachines. 2024; 15(7):872. https://doi.org/10.3390/mi15070872

Chicago/Turabian StyleVolosov, Vladislav, Santina Bevilacqua, Laura Anoldo, Giuseppe Tosto, Enzo Fontana, Alfio-lip Russo, Claudio Fiegna, Enrico Sangiorgi, and Andrea Natale Tallarico. 2024. "Positive Bias Temperature Instability in SiC-Based Power MOSFETs" Micromachines 15, no. 7: 872. https://doi.org/10.3390/mi15070872

APA StyleVolosov, V., Bevilacqua, S., Anoldo, L., Tosto, G., Fontana, E., Russo, A.-l., Fiegna, C., Sangiorgi, E., & Tallarico, A. N. (2024). Positive Bias Temperature Instability in SiC-Based Power MOSFETs. Micromachines, 15(7), 872. https://doi.org/10.3390/mi15070872