Abstract

An ultra-low quiescent current output-capacitor-less low dropout (OCL-LDO) regulator for power-sensitive applications is proposed in this paper. To improve the gain of the OCL-LDO feedback loop, the error amplifier employs a combination of a cross-coupled input stage for boosting the equivalent input transconductance and a negative resistance technique to improve the gain. Meanwhile, in order to address the issue of transient response of the ultra-low quiescent current OCL-LDO, a sub-threshold slew-rate enhancement circuit is proposed in this paper, which consists of a transient signal input stage and a slew-rate current increase branch. The proposed OCL-LDO is fabricated in a 0.18 m CMOS process with an effective area of 0.049 mm2. According to the measurement results, the proposed OCL-LDO has a maximum load current of 100 mA and a minimum quiescent current of 640 nA at an input voltage of 1.2 V and an output voltage of 1 V. The overshoot and undershoot voltages are 197 mV and 201 mV, respectively, and the PSR of the OCL-LDO is −72.4 dB at 1 kHz when the load current is 100 A. In addition, the OCL-LDO has a load regulation of 7.6 V/mA and a line regulation of 0.87 mV/V.

1. Introduction

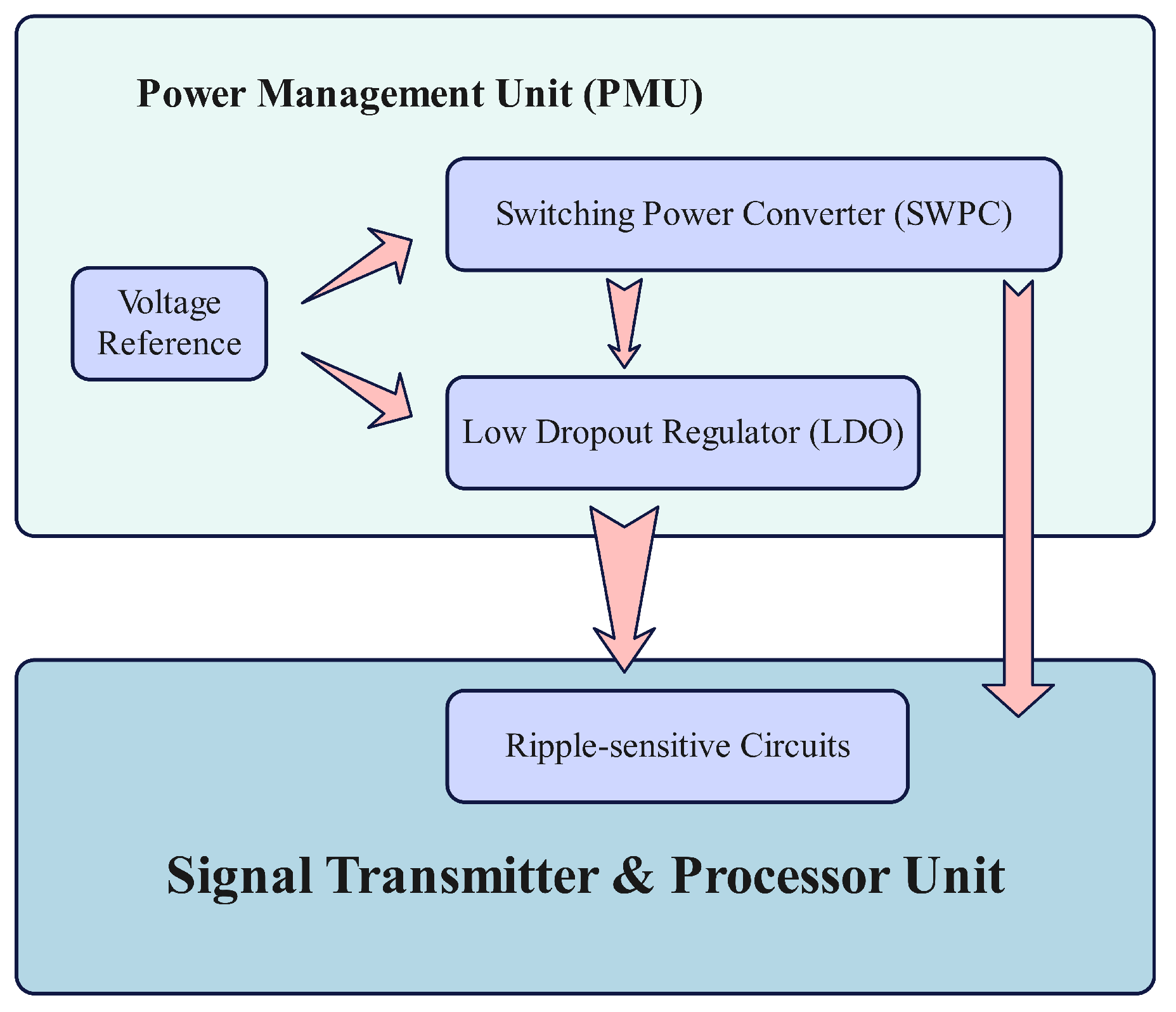

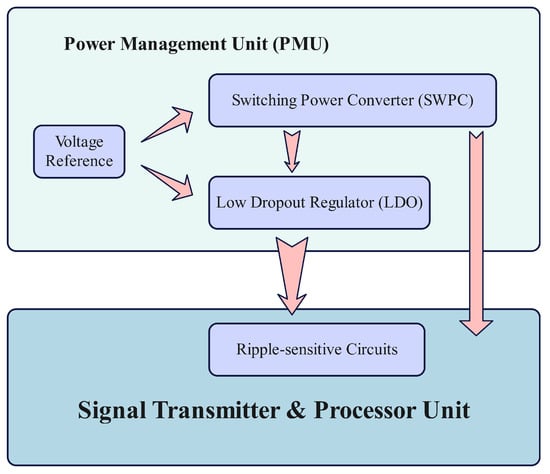

Narrow band Internet of Things (NB-IoT), a critical technology focusing on low-power applications within the IoT field, exhibits great potential for applications in precision medicine, smart transportation, and environmental monitoring, among others [1,2,3,4]. Nevertheless, the challenge of power management units (PMUs) for NB-IoT applications has become increasingly difficult because of the nature of NB-IoT applications in which batteries are difficult to replace frequently. Consequently, it is necessary to reduce the quiescent currents of critical circuits within PMUs, which leads to extended battery life [5,6,7]. Low dropout regulator (LDO) owing to its high ripple immunity is a power management unit (PMU) topology that is placed after the switching power converter (SWPC) to provide a reliable power supply for ripple sensitive circuits as shown in Figure 1 [8,9,10]. Furthermore, in order to improve the current efficiency under ultra-low loads of the LDOs, their quiescent current is supposed to be low (≤1 A).

Figure 1.

The classic composition of an NB-IoT application.

A number of works have been presented on the circuit design of ultra-low quiescent current LDOs, categorized into conventional LDOs with off-chip F-class capacitors [11,12,13] and highly integrated output-capacitor-less LDOs [14,15,16,17]. Although off-chip F-level capacitors are beneficial for system stability and transient response, etc., OCL-LDOs have become a more preferred choice among them, as NB-IoT applications increasingly demand higher levels of integration [18,19,20]. With the development of CMOS process towards the nanoscale, the current consumption of digital cells within NB-IoT applications is able to vary between close to zero and a maximum value in a short time [21,22,23,24]. Thus, the low dropout regulator is expected to have a favorable transient response to counteract large fluctuations in load current over a short time. Since there is no bulky off-chip capacitor to store charge for improving transient response, and the ultra-low quiescent current results in the reduction in the loop bandwidth and an insufficient swing rate required at the gate of the power-FET, the transient response of the ultra-low quiescent current OCL-LDOs is in demand for improvement.

Several nA-level quiescent current OCL-LDO circuit structures have already been presented in previous work. Huang et al. proposed an OCL-LDO with a quiescent current of only 10 nA [14], which utilizes an adaptive biasing scheme to reduce the quiescent current of the OCL-LDO when it is under ultra-low load. Meanwhile, a hybrid of analog and digital transient enhancement has been proposed to improve the transient response of this OCL-LDO. The bias current of the comparator used in the transient enhancement circuit of [14] is only 1.5 nA, so the impact of the delay of the comparator on the recovery time of the transient response is not negligible. In addition to this, the hybrid compensation approach increases the complexity of the circuit design and chip area. Zhao et al. proposed a feed-forward transient enhancement circuit, which couples the variation of the output voltage directly to the current-controlled oscillator via a capacitor for fast transient response [25]. However, the measurement results of its load regulation and line regulation show that this OCL-LDO experiences large variations with changes in the load current or input voltage. The transient enhancement circuits proposed in [14,25] both contain digital circuit components; although they cause no increase in the quiescent current of the OCL-LDO, they demand a high dynamic power consumption of the circuit. An OCL-LDO with a supply voltage of 0.6 V and a quiescent current of only 220 nA was proposed by Zhang et al. which utilizes bulk modulation to reduce the power of the circuit, but its maximum load current is only 10 mA, making it difficult to satisfy the current requirements of high-performance operating states for NB-IoT applications [26]. Tang et al. suggested an embedded slew-rate enhancement circuit for improving the transient response of the OCL-LDO, but the quiescent current of this module is 3.6 A, which is unsuitable for low-power situations [27].

An ultra-low quiescent current output-capacitor-less low dropout voltage regulator is proposed in this paper. With the aim of improving the accuracy of the output voltage of the OCL-LDO, i.e., increasing the gain of the feedback loop without applying a three-stage amplification structure, the error amplifier within this OCL-LDO employs a cross-coupled input stage to increase the equivalent transconductance, and utilizes a negative-resistance technique to increase the gain of the error amplifier. The improvement in loop gain simultaneously improves the ripple immunity, that is to say, the power supply rejection (PSR) of this OCL-LDO. In response to the problem of weak transient response due to ultra-low quiescent current, this paper presents a sub-threshold CMOS-based slew-rate enhancement circuit that incorporates a transient signal introduction and a slew rate current increase branch. An equivalent G-level resistor of the MOSFET connected to the gate and the source is used for the sub-threshold CMOS slew-rate enhancement circuit in order to minimize the area of the chip, and the effect of transient voltage variations on the main loop is also eliminated. The OCL-LDO is fabricated in the TSMC 0.18 m CMOS process with an area of 0.049 mm2. Measurement results show that the minimum quiescent current is 640 nA at an input voltage of 1.2 V and an output voltage of 1 V of the proposed OCL-LDO. The maximum load current of the proposed OCL-LDO is 100 mA since the size of the power transistor is 12 mm/0.2 m. Although the pole at the gate of the power transistor is close to the output pole due to the large size of power-FET, the OCL-LDO remains stable at a load current of 1 A because of the Miller compensation capacitor. Meanwhile, with a certain power transistor size, the wider the bias voltage range, the greater the load current range, i.e., the higher the maximum load current. In order to increase the voltage range at the gate of the power transistor, i.e., the bias voltage of power-FET, the error amplifier employs a Class-AB output stage structure, which has a rail-to-rail output range. With the aid of the sub-threshold CMOS slew-rate enhancement circuit, the overshoot and undershoot voltages of this OCL-LDO are 194 mV and 201 mV, respectively, when the load current is switched between 100 A and 100 mA.

The remainder of this paper is organized as follows. Section 2 presents the OCL-LDO design proposed in this paper and its stability analysis. Section 3 illustrates the circuit implementation and design considerations in detail. Section 4 shows the measurement results, and Section 5 provides a summary of the measurement results and a comparison with prior works. Section 6 gives the conclusion of this paper.

2. Architecture and Stability Analysis of Proposed OCL-LDO

The OCL-LDO is required to be designed with ultra-low quiescent current in NB-IoT applications. As a negative feedback control system, the OCL-LDO firstly requires its loop gain and phase to be analyzed to ensure the stability of the system. Meanwhile, a circuit design with ultra-low quiescent current deteriorates its transient response, which is not able to satisfy the demand of rapidly switching operating states in IoT applications. Hence, a sub-threshold CMOS-based slew-rate enhancement circuit is proposed to optimize the transient response of the OCL-LDO, and the sub-threshold CMOS-based circuit is designed with nA-level quiescent currents, which will not burden the OCL-LDO with excessive quiescent currents as a whole.

2.1. Architecture of Proposed OCL-LDO

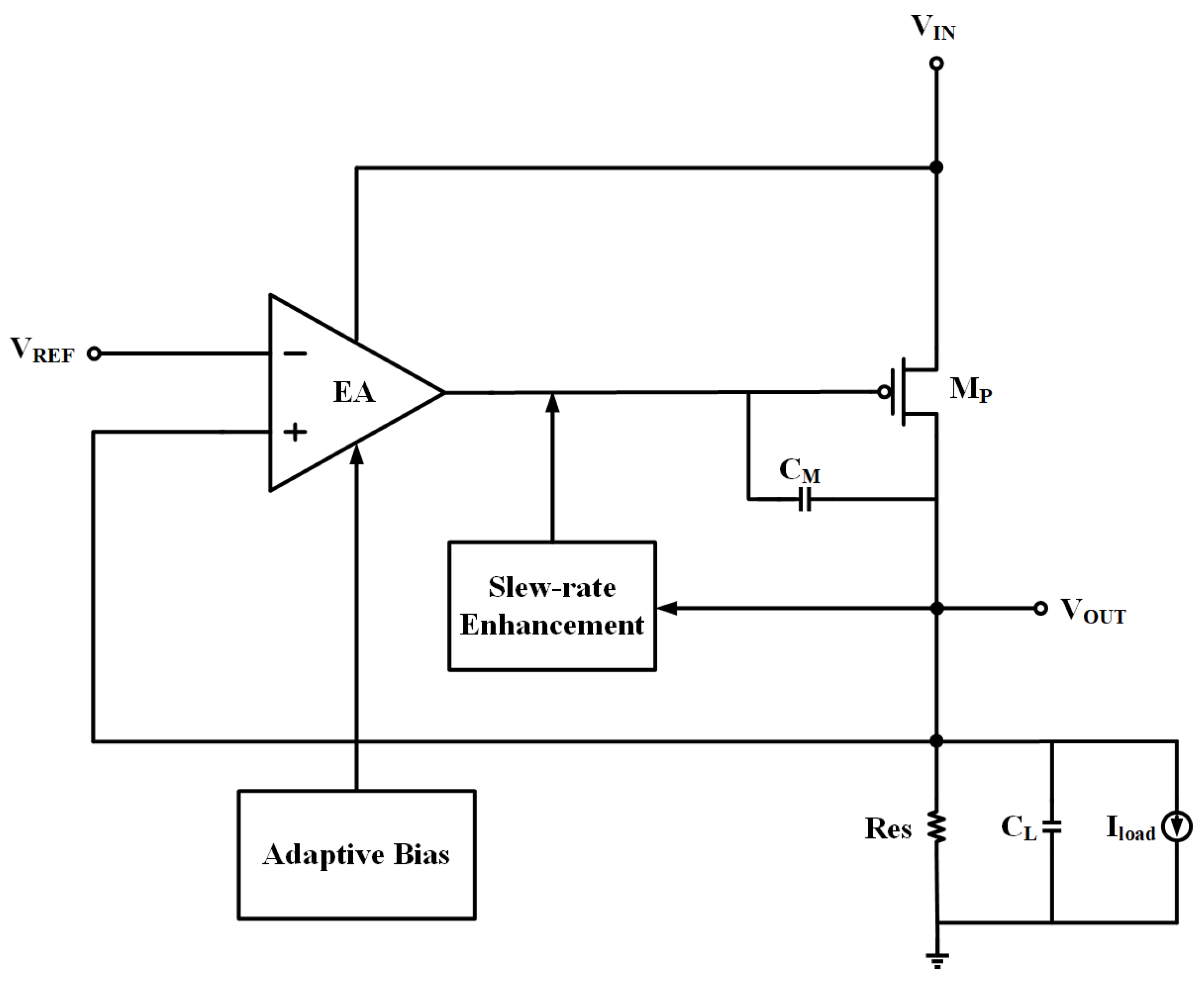

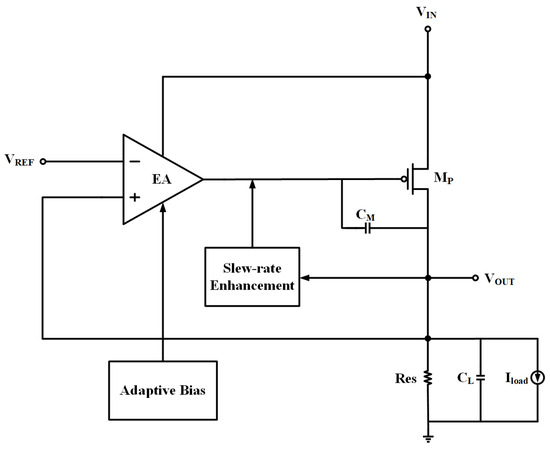

In order to minimize the quiescent current of the output-capacitor-less low-dropout linear regulator (OCL-LDO), the number of current branches in the system should be fewer, so the proposed OCL-LDO in this paper is composed of a two-stage amplification structure, which is shown in Figure 2. The two-stage amplification structure composed of an error amplifier and a power-FET is used to provide a stable voltage output, where the first stage of amplification, i.e., the error amplifier, compares the output voltage with the reference voltage and provides an error signal, and then the output of the error amplifier is connected to the gate of the power-FET because the output voltage is fixed and the load current varies so the gate voltage needs to have a wide range of variation. For this reason, the Class-AB output stage is selected so that the error amplifier has a rail-to-rail output range. In order to make the current efficiency at ultra-low load current and the OCL-LDO performance at heavy load excellent at the same time, the system employs an adaptive biasing scheme. Furthermore, there is a sub-threshold CMOS slew-rate enhancement circuit embedded in the OCL-LDO, which effectively improves the transient response of the OCL-LDO, and its nano-ampere quiescent current does not make the overall quiescent current of the OCL-LDO exceed 1 A.

Figure 2.

Structure of proposed OCL-LDO.

2.2. Stability Analysis

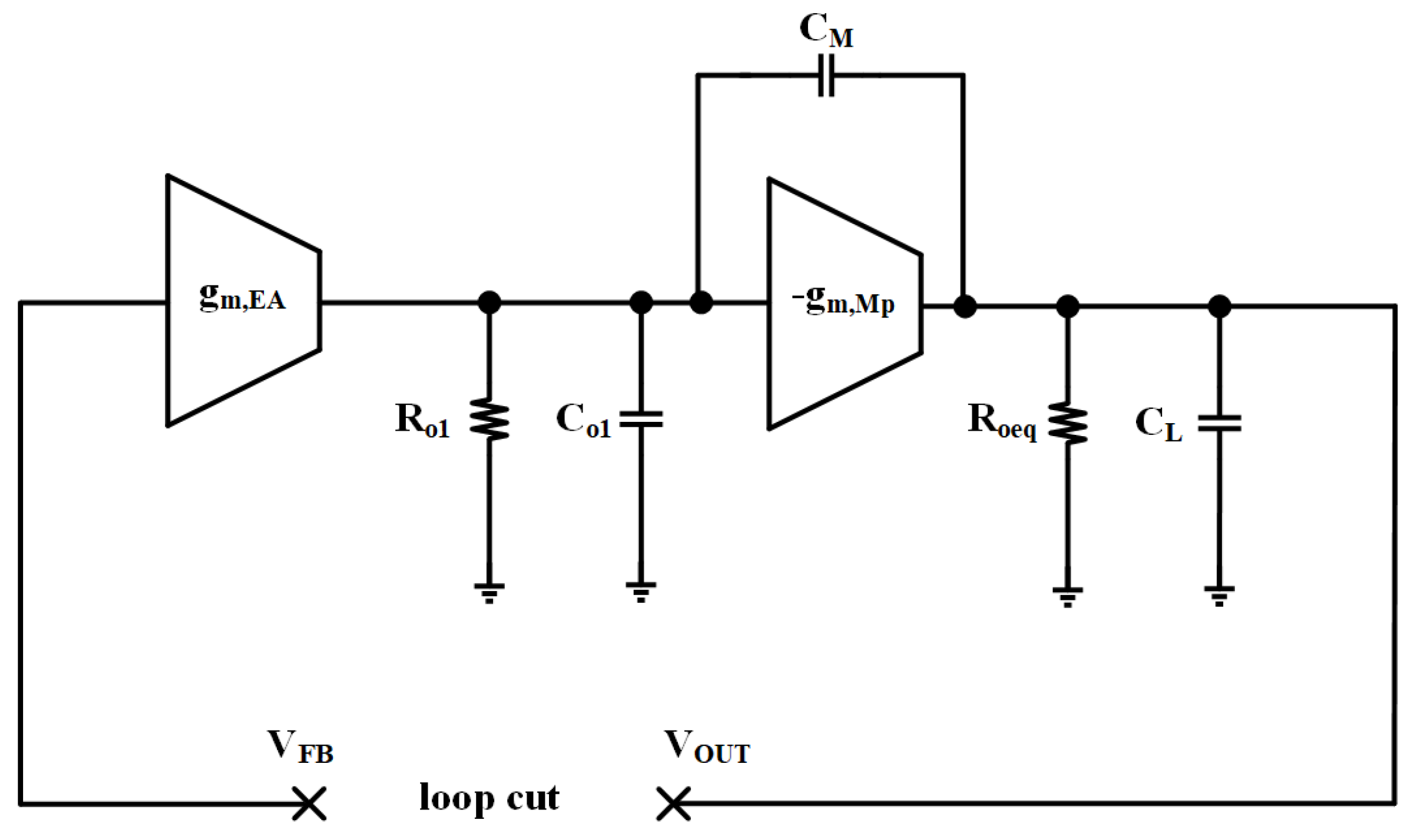

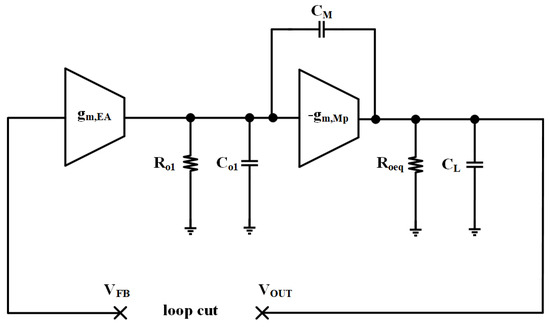

The sub-threshold CMOS slew-rate enhancement circuit is implemented in the proposed LDO. This circuit detects transient changes in the output voltage and quickly provides feedback to the gate of the power field effect transistor. The small-signal model of the proposed OCL-LDO without considering the sub-threshold slew-rate enhancement circuit is shown in Figure 3.

Figure 3.

Small-signal model of proposed OCL-LDO without slew-rate enhancement circuit.

Based on the analysis, the small-signal transfer function of the LDO when there is no compensation network may be represented as follows:

where and denote the transconductance of the error amplifier and the power transistor, respectively, and denote the equivalent output resistance of the error amplifier and the equivalent output resistance of the OCL-LDO, respectively, is the load capacitance, and is the gate parasitic capacitance of power-FET. In the absence of Miller compensation, the transfer function of the OCL-LDO loop displays two poles that are quite near each other in some cases. This closeness leads in a narrow phase margin, which may not fulfill the stability criteria for the system. To address this, the addition of a Miller compensation capacitor, , becomes necessary. The Miller compensation capacitor is used to generate isolation between the primary and secondary poles of the transfer function. By connecting the between the output of the error amplifier and the input of the power transistor, the output of the error amplifier is able to be fixed as the primary pole, which is reduced to a large extent compared to the initial error amplifier output pole, while the may successfully boost the size of the secondary pole, thus enlarging the phase margin. At this stage, the loop transfer function of the OCL-LDO may be stated as:

in which / could be used to approximate the secondary point and 1/ to approximate the primary pole. Regardless of the load current modifications, the secondary point is much greater than the primary pole after Miller compensation.

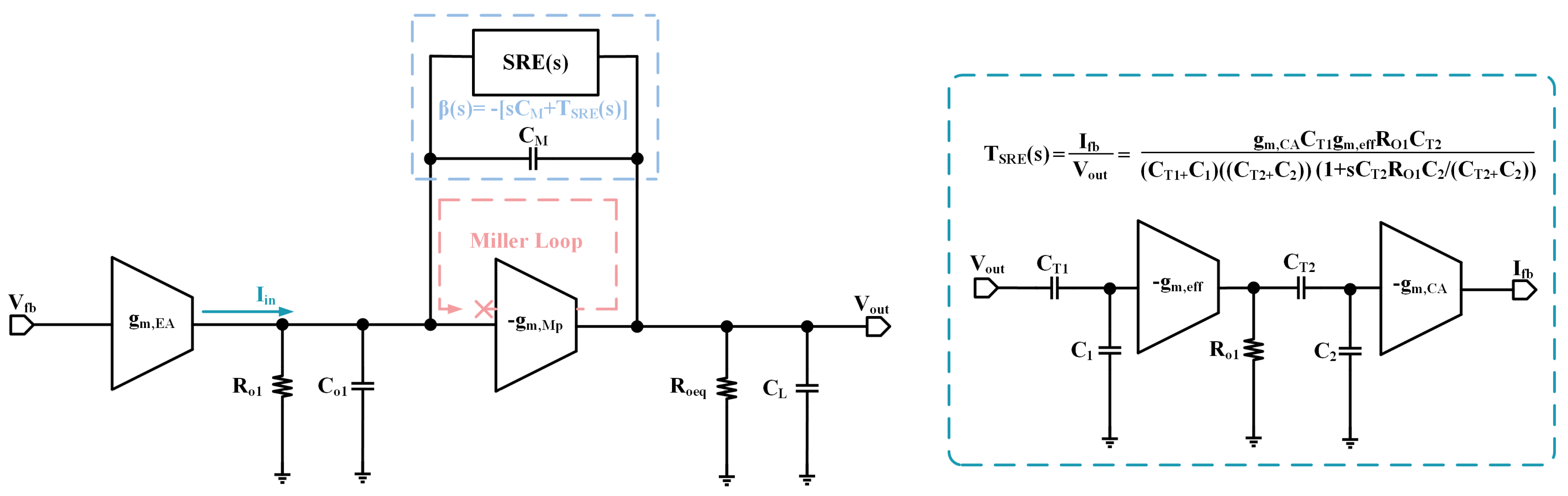

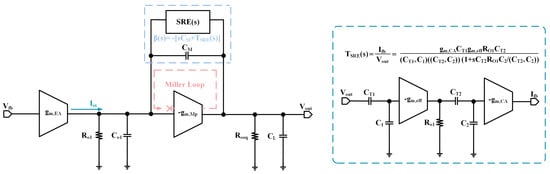

The sub-threshold slew-rate enhancement circuit is designed to sense changes in the output voltage and transfer the resulting signal variation to the gate of the power-FET through a fast feedback loop, which then negatively feeds back the output voltage. When considering the effect of the sub-threshold slew-rate enhancement circuit on the main loop, its small-signal model can be represented as shown in Figure 4. The connection is the same as the Miller capacitor and the transfer function is expressed as:

in which and are couple capacitors to the transient signal input stage and slew-rate enhancement branch. and are the input parasitic capacitance. is the output resistance of the transient signal input stage. and are equivalence transconductance of the transient signal input stage and slew-rate current increase branch.

Figure 4.

Small-signal model of proposed OCL-LDO with slew-rate enhancement circuit.

A design-oriented analysis (DOA) is adopted in this paper to avoid the complexity of transfer functions and to provide a more intuitive understanding of the impact of the zero poles of the OCL-LDO on the stability of this system [28,29,30]. The slew-rate enhancement circuit and together form the Miller loop:

where A is the coefficient and is the combination of the and parasitic capacitance of power-FET:

According to DOA, the transfer function of Miller loop is obtained and can be expressed as:

where is the open loop transfer function of transimpedance amplifier. By simplifying the above equation, it is obtained that:

As a result, the pole positions obtained from Equations (2) and (7) are the same, the primary pole is located at the gate of the power-FET, and the secondary pole is located at the output voltage of the OCL-LDO:

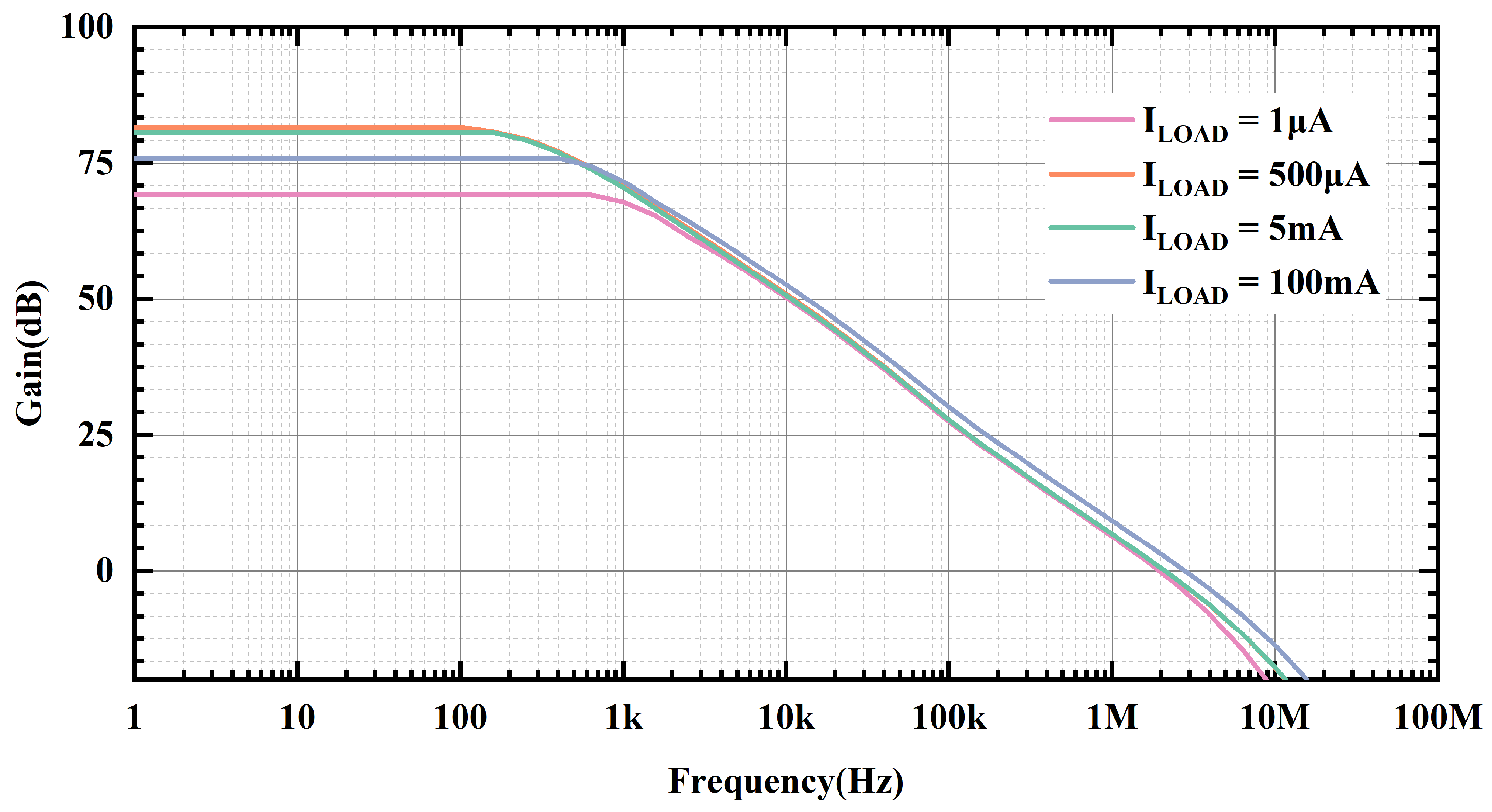

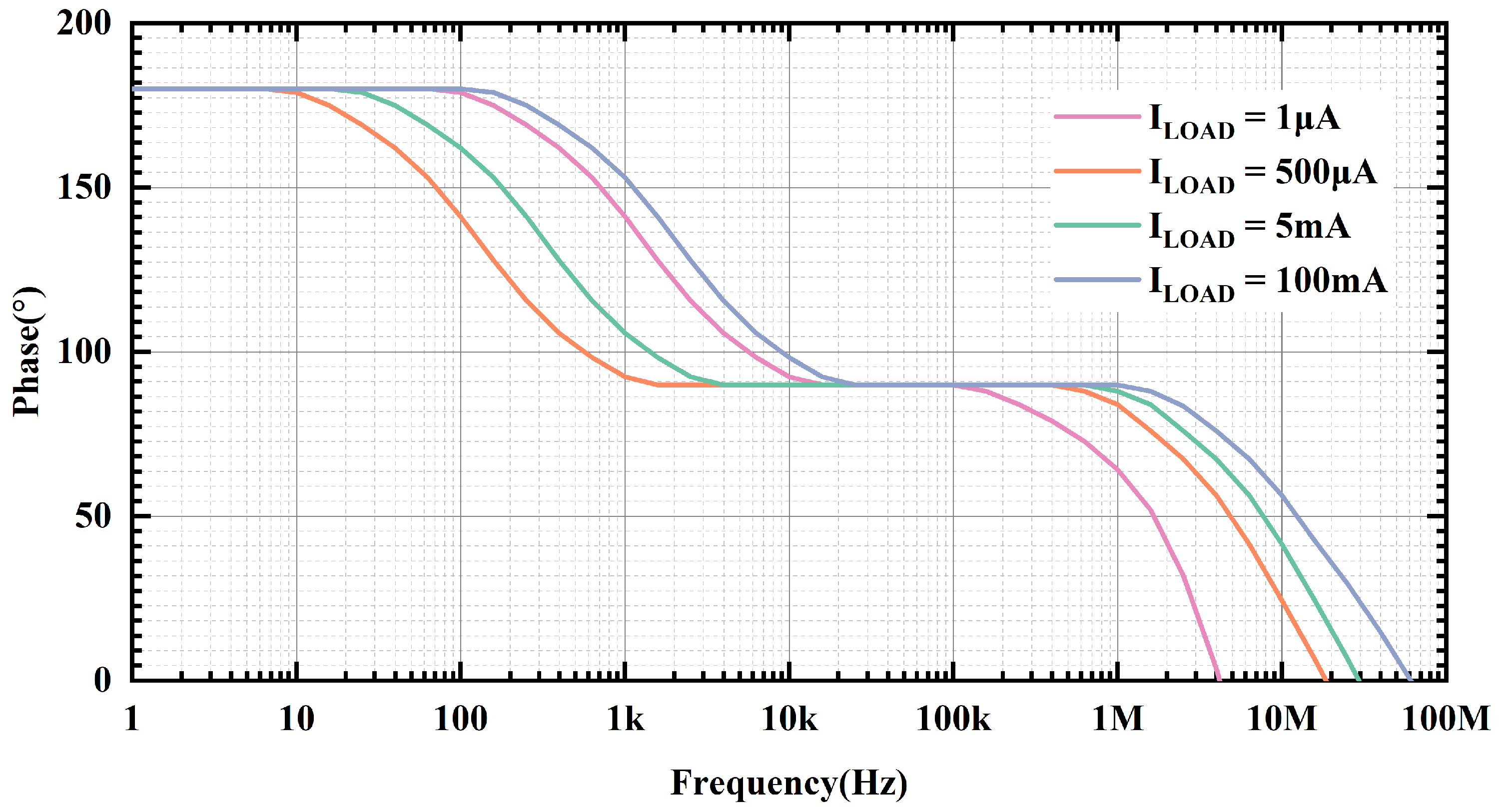

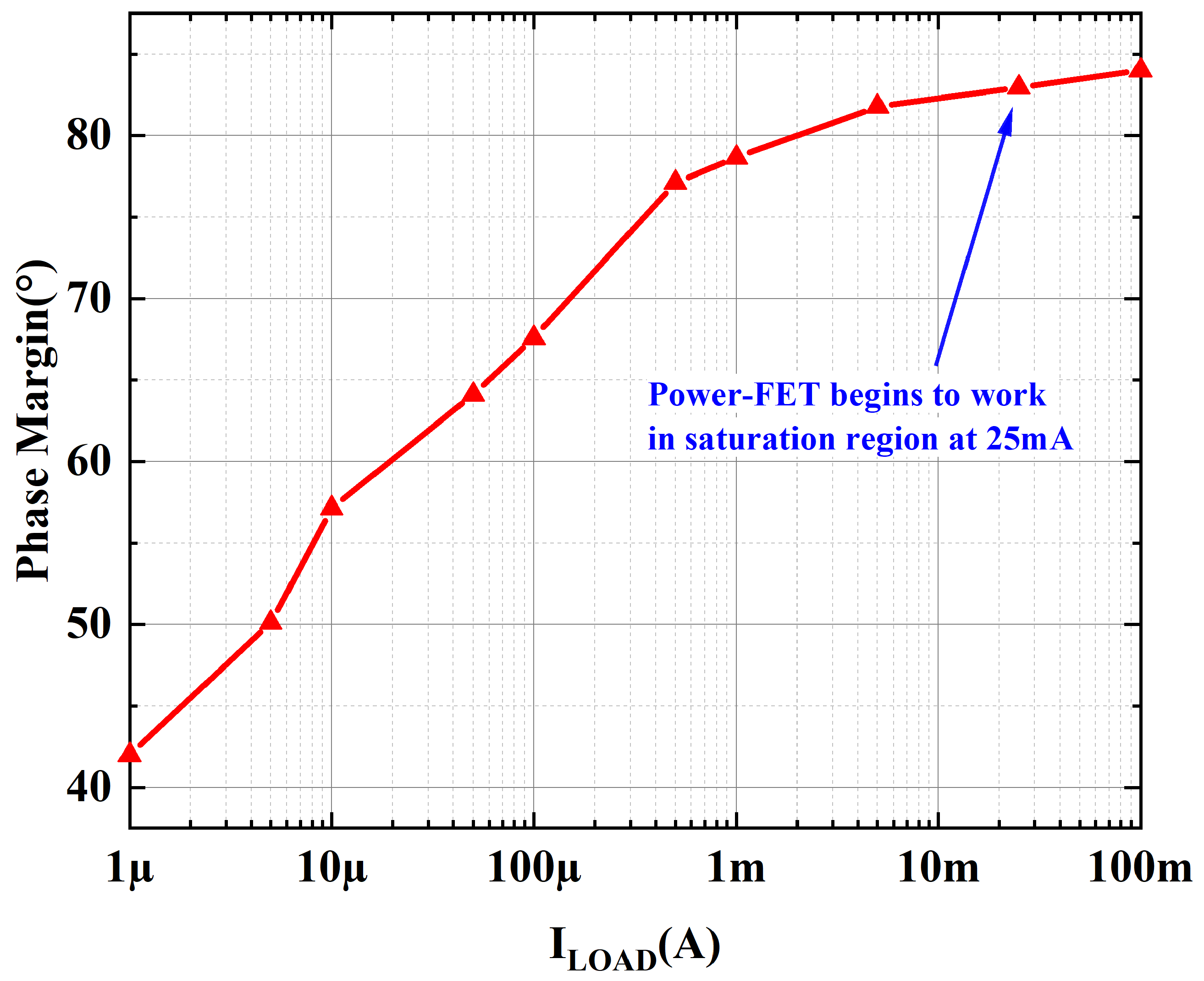

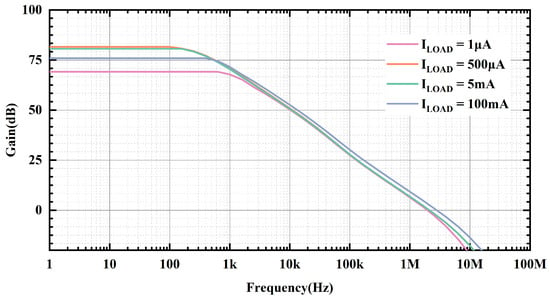

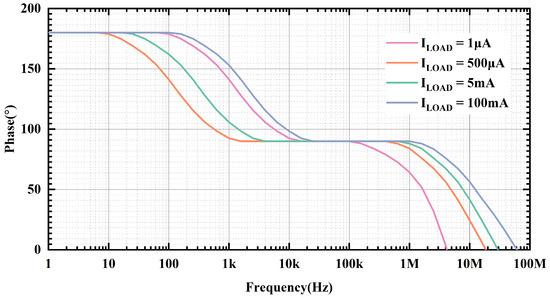

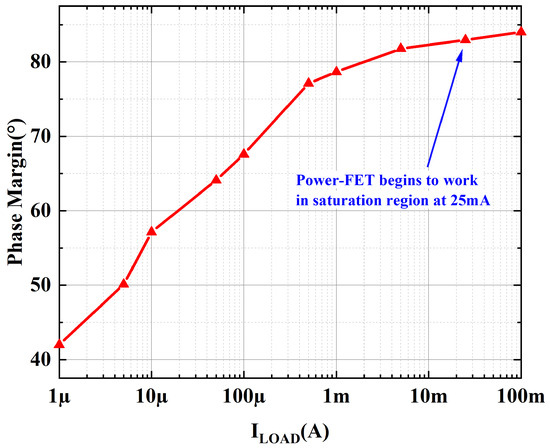

Figure 5 and Figure 6 provide the loop gain and phase simulation results at room temperature, input voltage of 1.2 V and output voltage of 1 V with different load currents, respectively. At ultra-low loads, its secondary poles are close to the main poles. As the load current increases, the output equivalent resistance decreases, so the secondary pole is far away from the main pole, and the phase margin becomes more favorable. Figure 7 presents the phase margin at different load currents when the load capacitance is 100 pF, and the variation trend of the PM is consistent with the previous analysis. The minimum phase margin (PM) is 42.5° when the load current is 1 A. And when the load current is greater than 25 mA, the power-FET begins to operate in the saturation region, at which time the transconductance of the power transistor is greater than the in the sub-threshold region, and the frequency where the secondary poles are located is greater than the GBW of the OCL-LDO; therefore, the phase margin is better during heavy loads.

Figure 5.

Simulated loop gain of proposed OCL-LDO under different load currents when is 100 pF and temperature is room temperature.

Figure 6.

Simulated loop phase of proposed OCL-LDO under different load currents when is 100 pF and temperature is room temperature.

Figure 7.

Simulated phase margin vs. load current.

3. Circuit Implementation and Design Considerations

The OCL-LDO proposed in this paper is capable of operating at nA-level quiescent currents as well as with good transient response characteristics. Its slew-rate enhancement circuit is based on sub-threshold CMOS operation, so even with the addition of a circuit module, the quiescent current of OCL-LDO is still lower than 1 A.

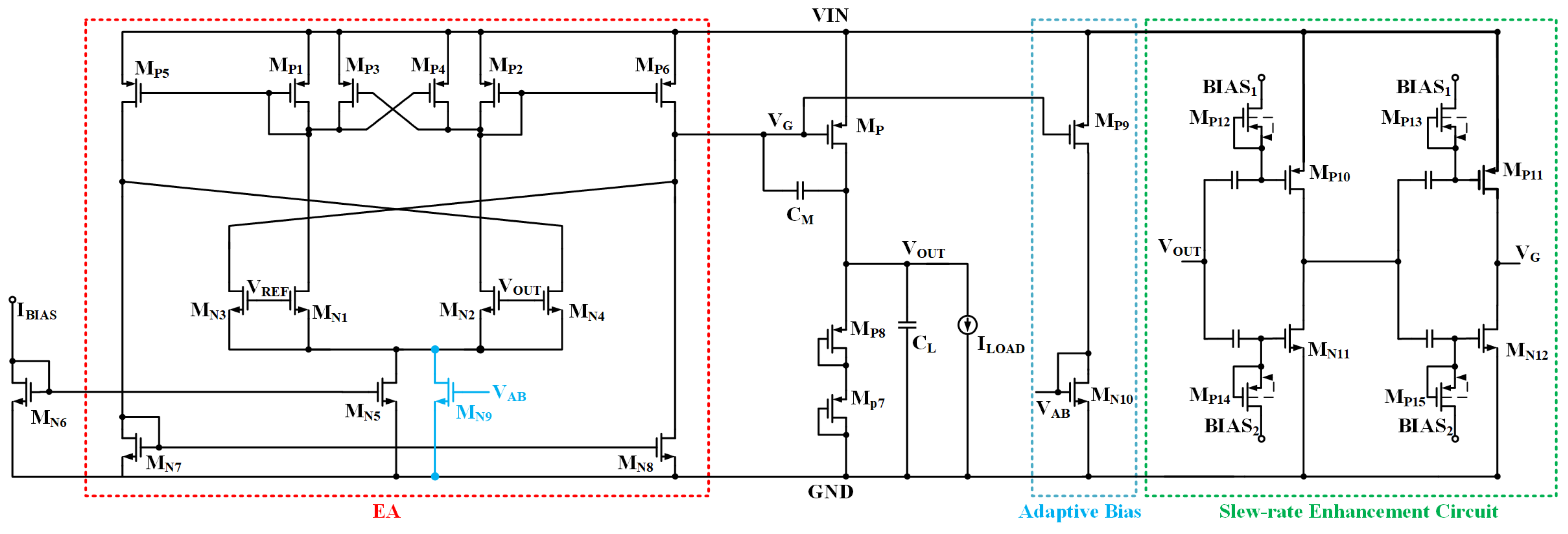

3.1. Overall Circuit of Proposed OCL-LDO

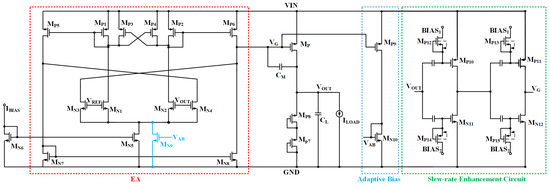

The concrete circuit of the OCL-LDO proposed in this paper is shown in Figure 8, which includes three parts: the main loop composed of error amplifiers and power transistors, the adaptive biasing scheme that adjusts the bias current of the OCL-LDO according to the load current, and the sub-threshold CMOS slew-rate enhancement circuit.

Figure 8.

Overall circuit of proposed OCL-LDO.

To enhance the accuracy of the output voltage so that it is not subject to large fluctuations with changes in the load and input voltage, the gain of the error amplifier is required to be high. And in order to reduce the quiescent current and at the same time reduce the design complexity, the OCL-LDO proposed in this paper is a two-stage structure, which improves the gain of the error amplifier by embedding the cross-coupled input transistors and negative resistance technique. A sub-threshold slew rate enhancement circuit is proposed to alleviate the problem of poor transient response due to ultra-low quiescent current. It includes an RC circuit for coupling the transient changes in the output voltage, i.e., a transient signal input stage, and then the transient changes in the output signal of this module circuit are transferred to the slew-rate current increase branch through capacitive coupling. In this regard, the resistors in the sub-threshold slew-rate enhancement circuit are all implemented by gate and source connected (GSC) MOSFETs, which could be equivalent to a G-level resistor. This makes the transient voltage changes not affect the main loop and reduces the recovery time.

3.2. High-Gain Error Amplifier

In order to minimize the impact of input voltage and load current variations on the output voltage of the proposed OCL-LDO, it is desirable to increase the gain of the error amplifier in the main loop, but the three-stage amplification structure imposes additional quiescent current consumption, while the design complexity of the compensation circuit is increased.

The addition of a negative resistance and cross-coupled input stage requires no additional quiescent current consumption and is also effective in increasing the gain of the error amplifier. The gain of the error amplifier when there is no negative resistance and cross-coupled inputs stage is:

in which is the equivalence transconductance of the error amplifier, and and are the on-resistance of and . When there is a negative resistance in the amplifier, Equation (9) can be expressed as:

where is the difference in transconductance, and is the transconductance of . The cross-coupled input stage makes the equivalent input transconductance of the error amplifier twice as large, and the on-resistance of can be seen as a part of the output impedance of the error amplifier, where and are connected in parallel and then connected in series with , so the impedance as seen from the drain of is:

Thus, the DC gain of the error amplifier at this point may be expressed as:

Since is far greater than and , the gain of the error amplifier is simplified to:

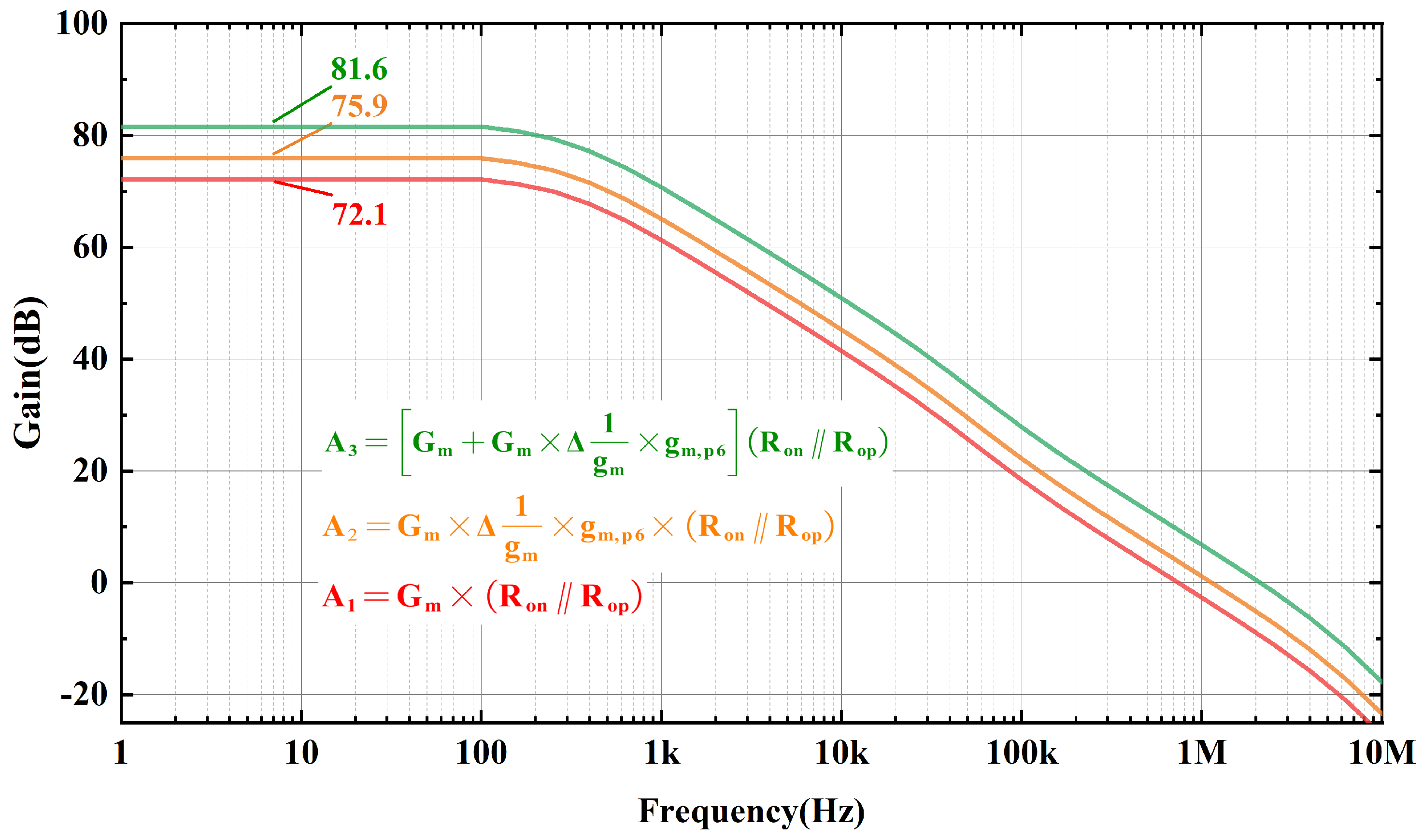

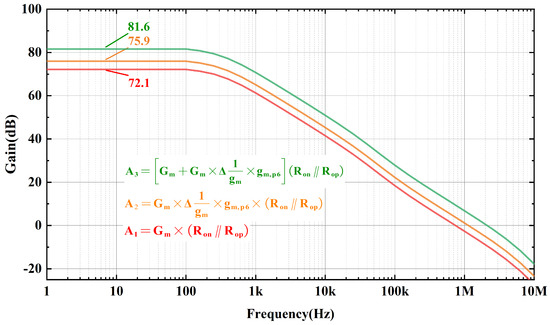

Comparison of simulation results for loop gain at a load current of 500 A is shown in Figure 9, where it is observed that the addition of negative resistance and the utilization of a cross-coupled input stage effectively improves the gain of the error amplifier.

Figure 9.

Loop gain of proposed utilizes different error amplifier.

According to Equations (9), (10) and (13), the DC gain of the error amplifier is calculated approximately, and by multiplying it with the gain of power-FET, the loop gain calculated results in Table 1 are obtained. As seen in Table 1, the calculated results compare well with the simulated results, so the negative resistance and the cross-coupled input stage increase the loop gain of the OCL-LDO by boosting the DC gain of the error amplifier.

Table 1.

Comparison of simulated results and calculated results of DC gain.

3.3. Sub-Threshold CMOS Slew-Rate Enhancement Circuit

The ultra-low quiescent current circuit design makes the loop bandwidth of the OCL-LDO decrease, while the small charge/discharge current required at the gate of the power transistor leads to inferior transient response of the OCL-LDO. Therefore, in order to optimize the transient response of the OCL-LDO proposed in this paper, the first approach is to utilize an adaptive biasing scheme, where the heavy load corresponds to the increase in the quiescent current with the increase in the load current when switching from a low load (which means the load current is 100 A or below it) to a heavy load (which is a load current that is 50 mA or above it), and at this time, both the slew-rate and the loop bandwidth are improved, and thus the adaptive biasing scheme is able to effectively reduce the undershoot voltage and its recovery time.

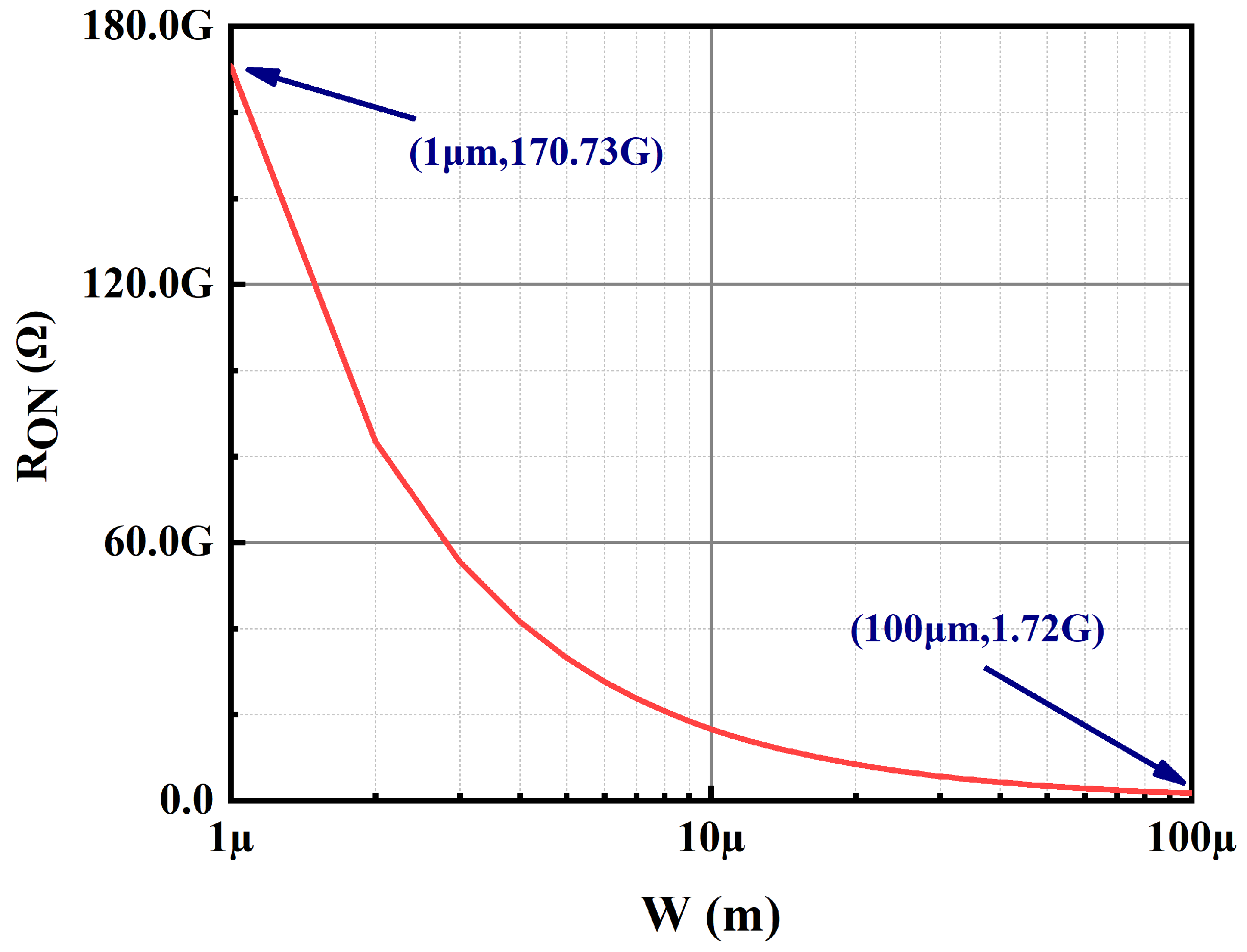

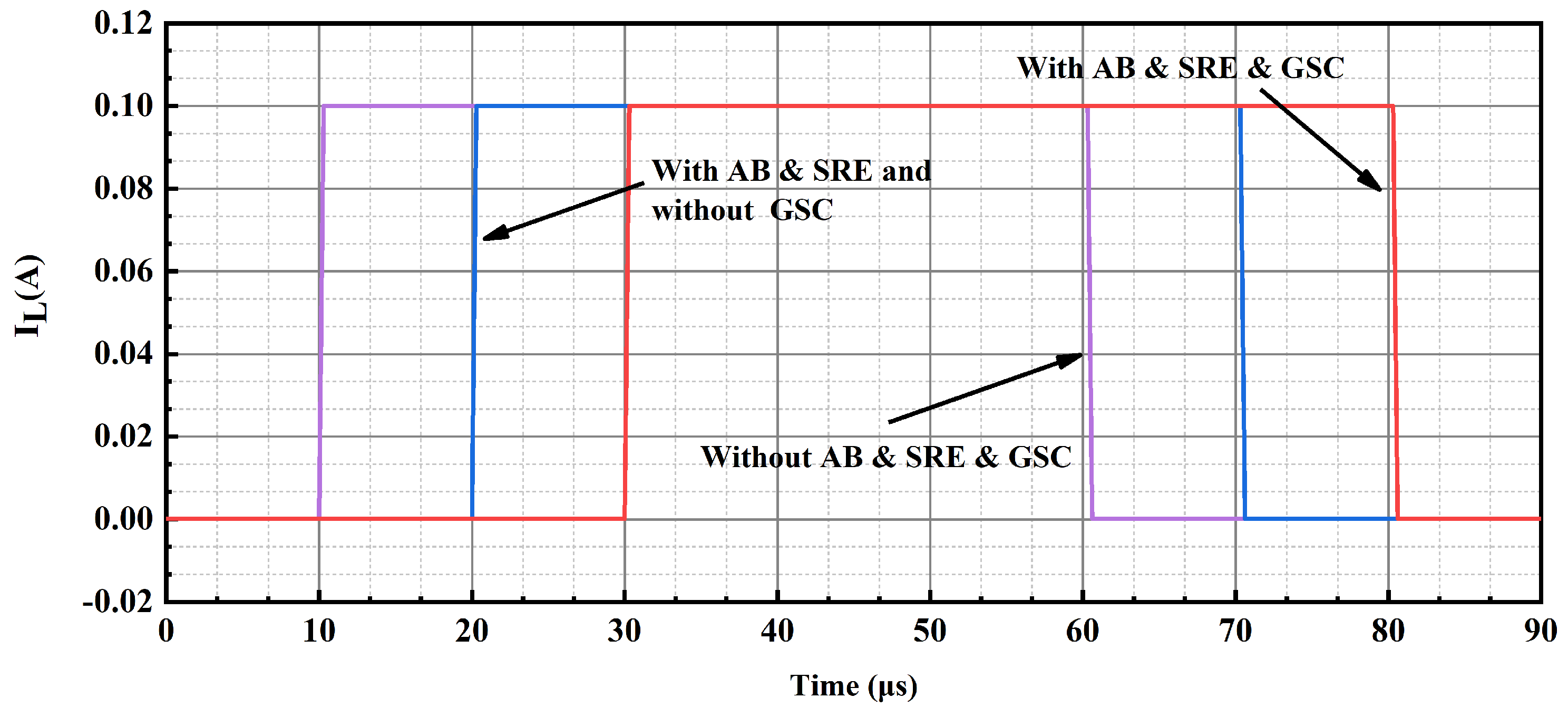

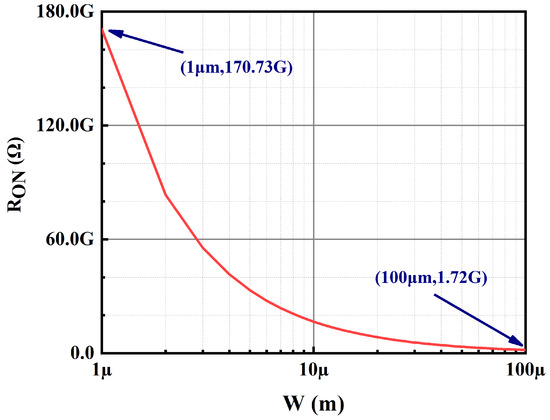

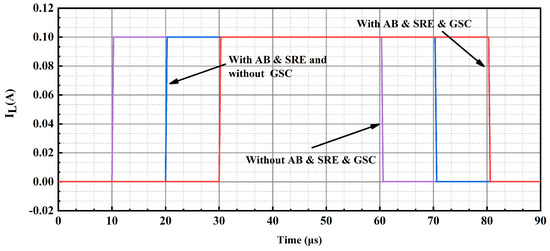

In addition to this, a sub-threshold CMOS-based slew-rate enhancement circuit is proposed to further improve the transient response of the OCL-LDO. – of the slew-rate enhancement are GSC MOSFET, which is employed to supply the bias voltage. The simulation results of versus the width for GSC PMOS with a length of 200 nm is given in Figure 10, where it is observed that the equivalent resistance of the GSC transistor is G-level. Take the low load to heavy load switching as an example; at this time, the output voltage results in the undershoot voltage, and the capacitor couples the same trend to the inputs of and in Figure 8, resulting in the drain voltage of and , i.e., the output voltage of the transient signal introduction stage increases, and the inputs of the slew-rate increasing branch sense through the capacitor the same change as the output of the previous stage, i.e., the gate voltages of and increase simultaneously, and at this time the gate voltage is discharged to make the output voltage reach stability quickly. An inverter-like structure is employed in this slew-rate enhancement circuit with a rail-to-rail output range, but its quiescent current is determined by the bias voltage, while its effect on loop stability has been analyzed above, and it has no impact on the primary and secondary poles of the feedback loop. The simulation conditions for switching load current within 500 ns are given in Figure 11 for an input voltage of 1.2 V and an output voltage of 1 V, and the simulation results shown in Figure 12 are obtained, which show that this sub-threshold slew-rate enhancement circuit could improve the transient response of the proposed OCL-LDO.

Figure 10.

of GSC PMOS when L = 0.2 m.

Figure 11.

Load current changes between 100 A and 100 mA in 500 ns.

Figure 12.

Simulation result of load transient response as = 1.2 V and = 1 V.

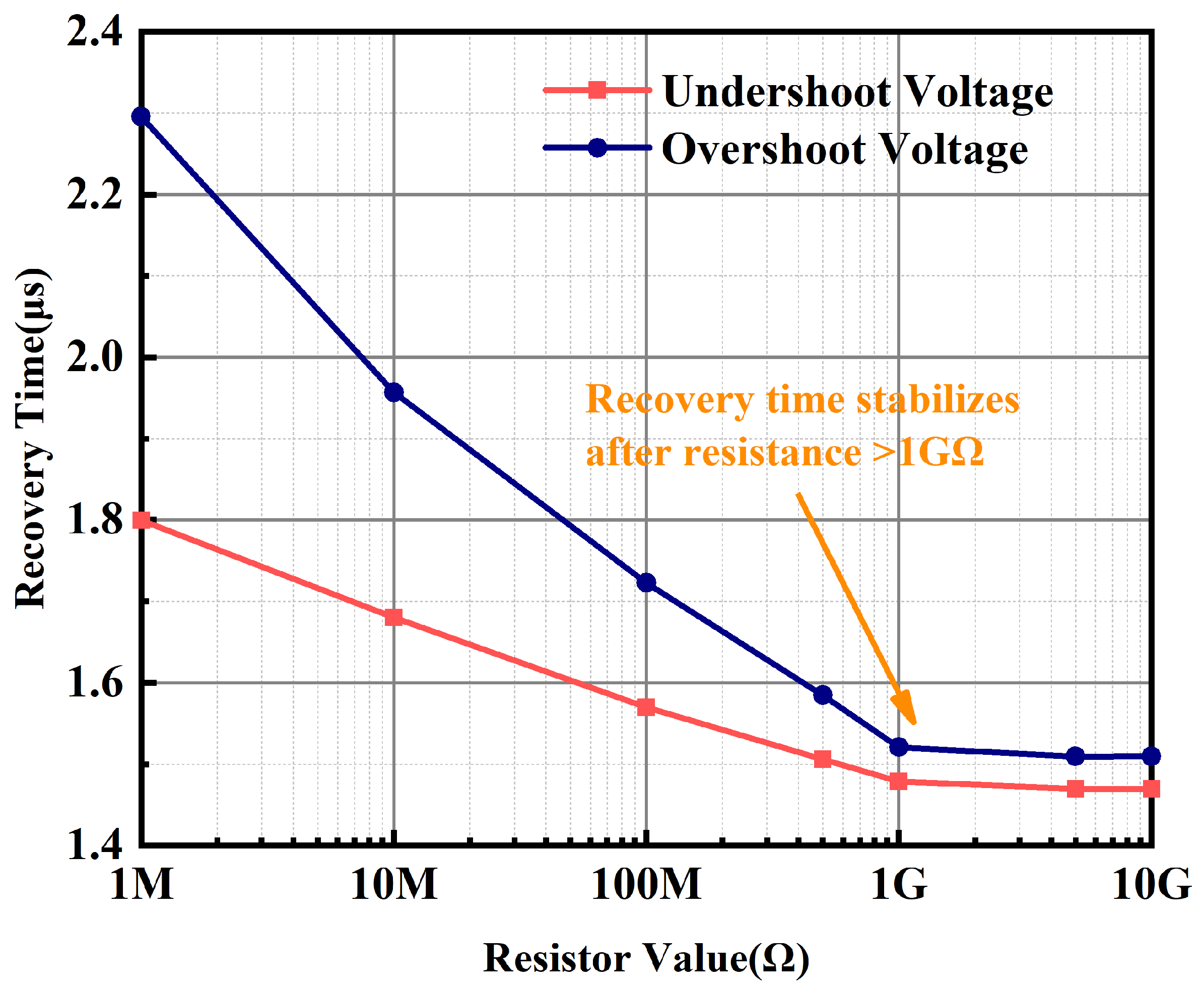

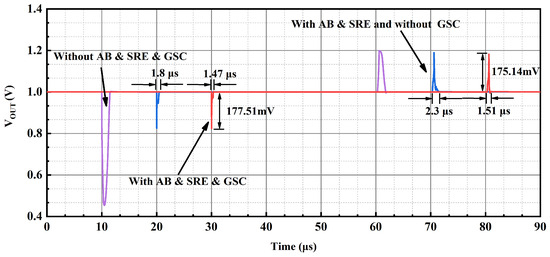

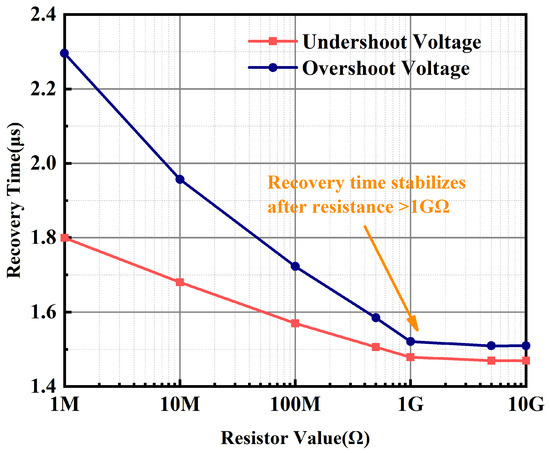

The simulation results of the recovery times corresponding to the overshoot and undershoot voltages of OCL-LDOs as a function of the resistor value are shown in Figure 13. It is observed from Figure 13 that the recovery time of the transient voltage remains basically stable when the resistance is larger than 1 G, that is, the variation in the transient voltage has no effect on the main loop. Because when the transistor width is 100 m, the of GSC PMOS is 1.72 G as shown in Figure 10, i.e., when the length of GSC PMOS is 200 nm, as long as the width of the transistor is less than 100 m, it enables the main loop to be unaffected by the transient voltage change.

Figure 13.

Simulation results of recovery time vs. resistor value.

4. Measurement Results

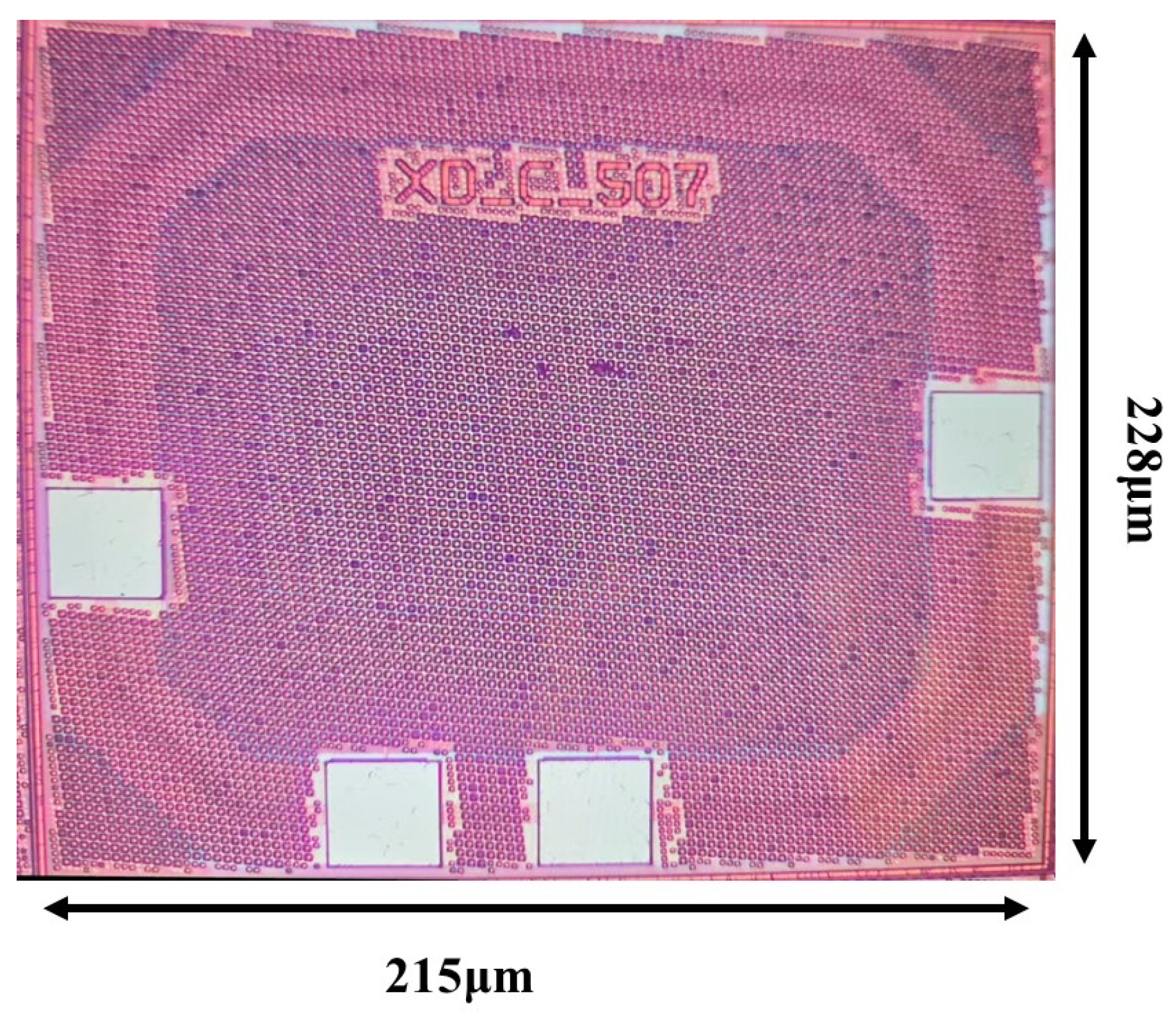

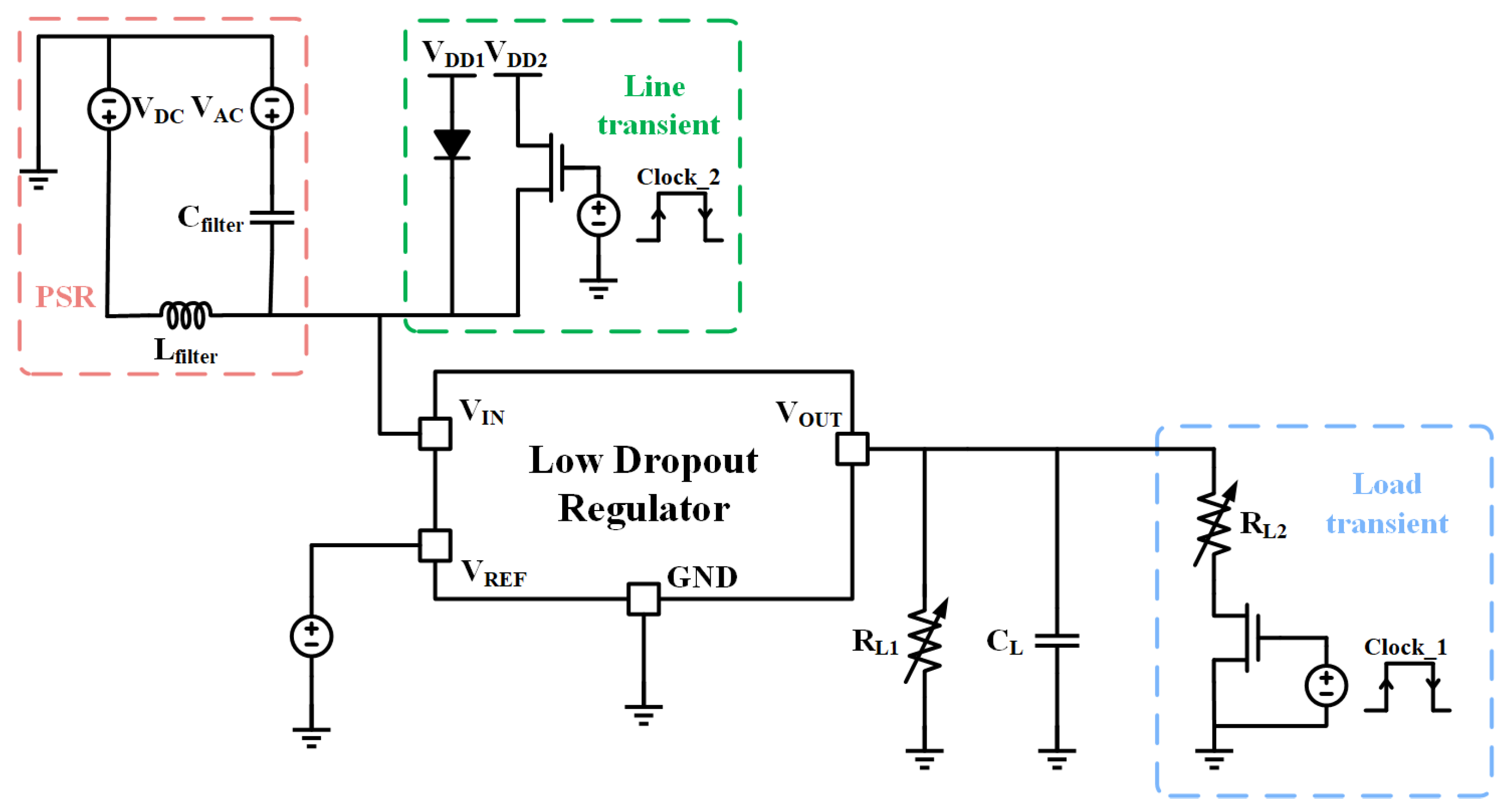

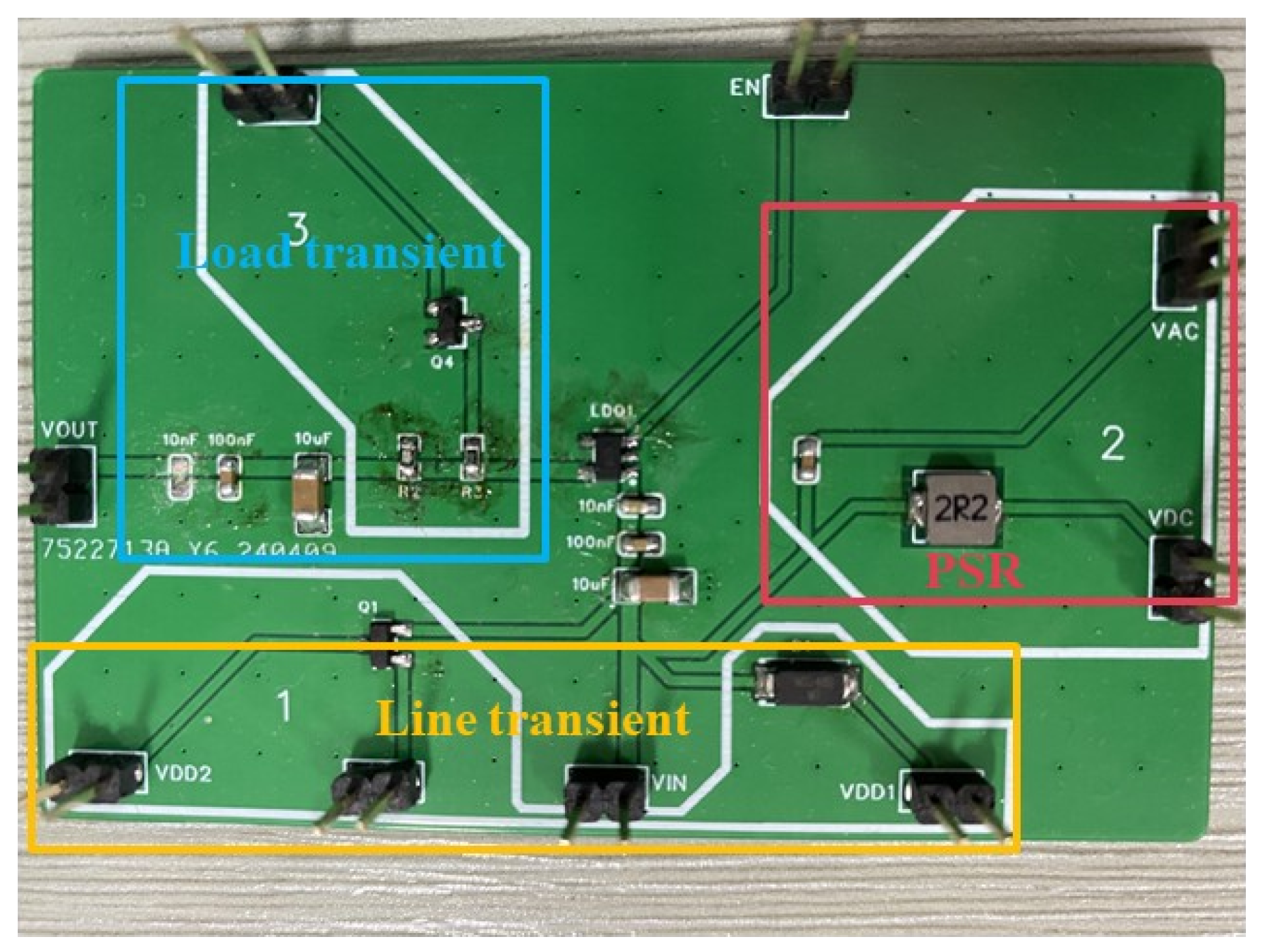

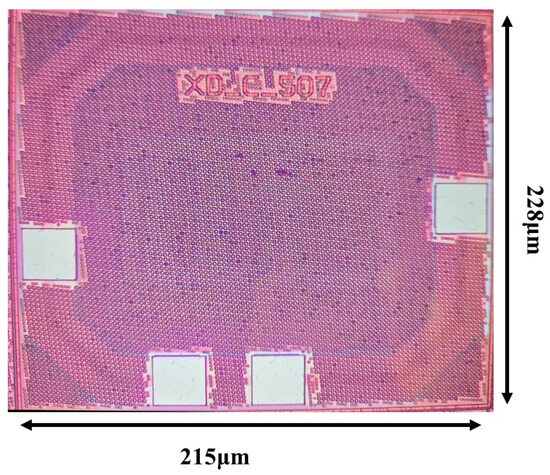

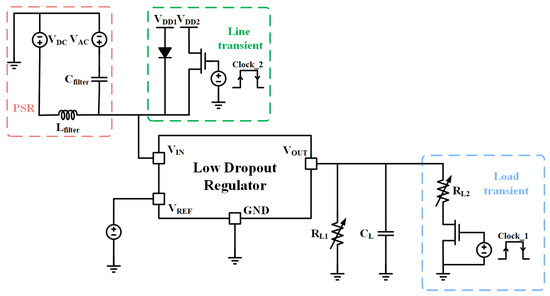

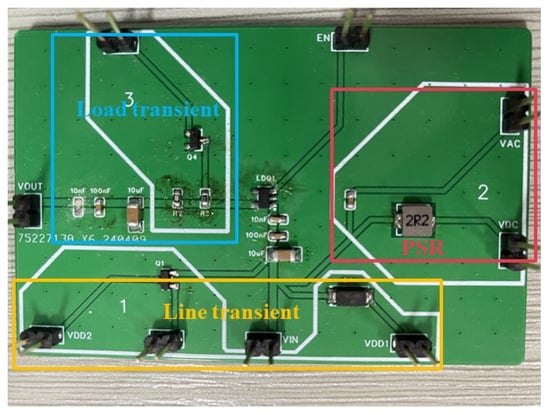

The ultra-low quiescent current OCL-LDO with the sub-threshold slew-rate enhancement circuit proposed in this paper is fabricated in a TSMC 0.18 m process. The chip micrograph is shown in Figure 14, with an active area of 0.049 mm2 (228 m × 215 m). The dropout of this OCL-LDO is 200 mV, i.e., when the output is 1 V, the minimum input voltage is 1.2 V, at which point the OCL-LDO is capable of driving a load current range of 1 A–100 mA. The minimum quiescent current is only 640 nA, and because of the adaptive biasing scheme, the quiescent current range of this OCL-LDO is 0.64–61.2 A. The test circuit schematic of this OCL-LDO is given in Figure 15, and Figure 16 is the PCB test board corresponding to the test circuit schematic.

Figure 14.

Photomicrograph of proposed OCL-LDO.

Figure 15.

Schematic diagram of OCL-LDO measurements.

Figure 16.

PCB board for the measurement of OCL-LDOs.

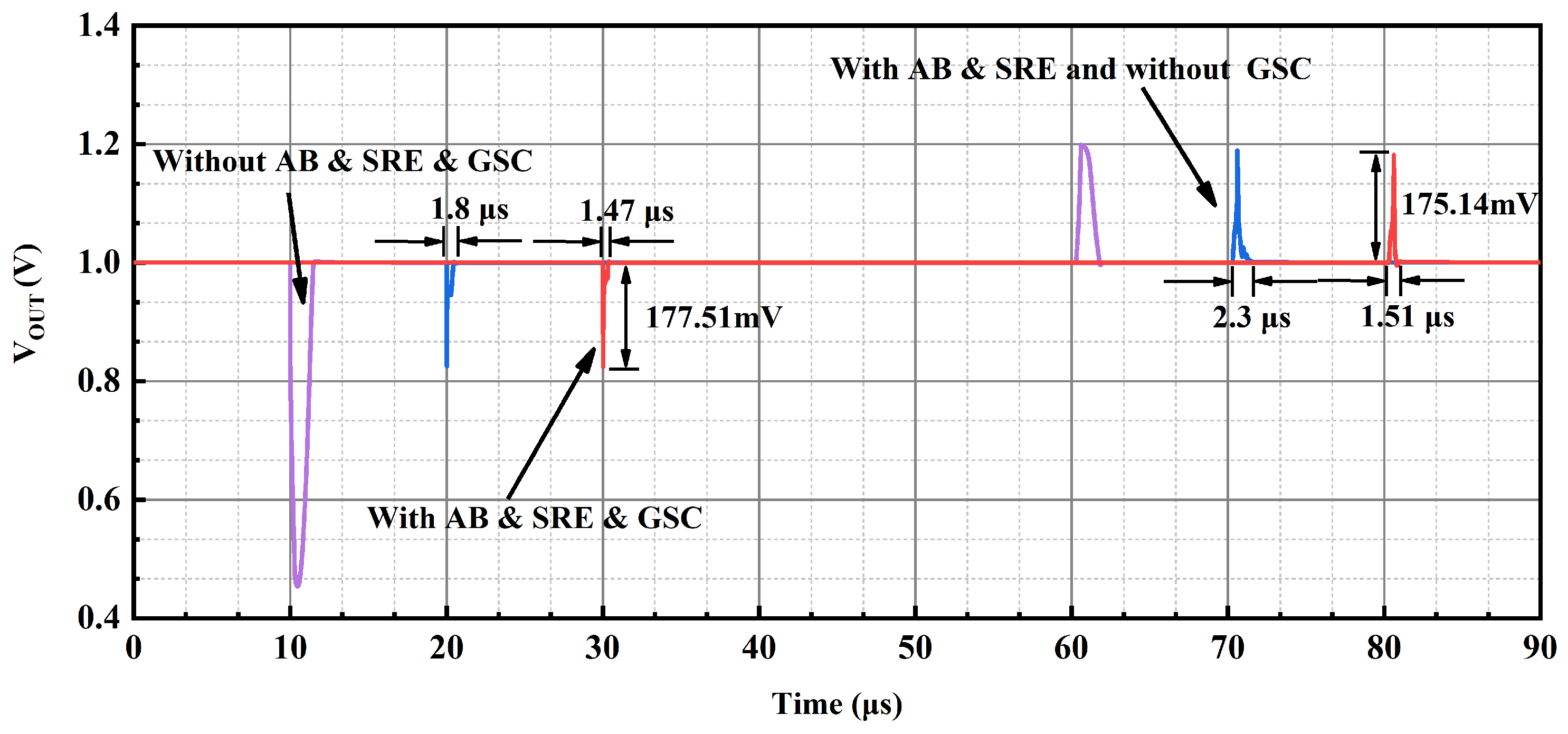

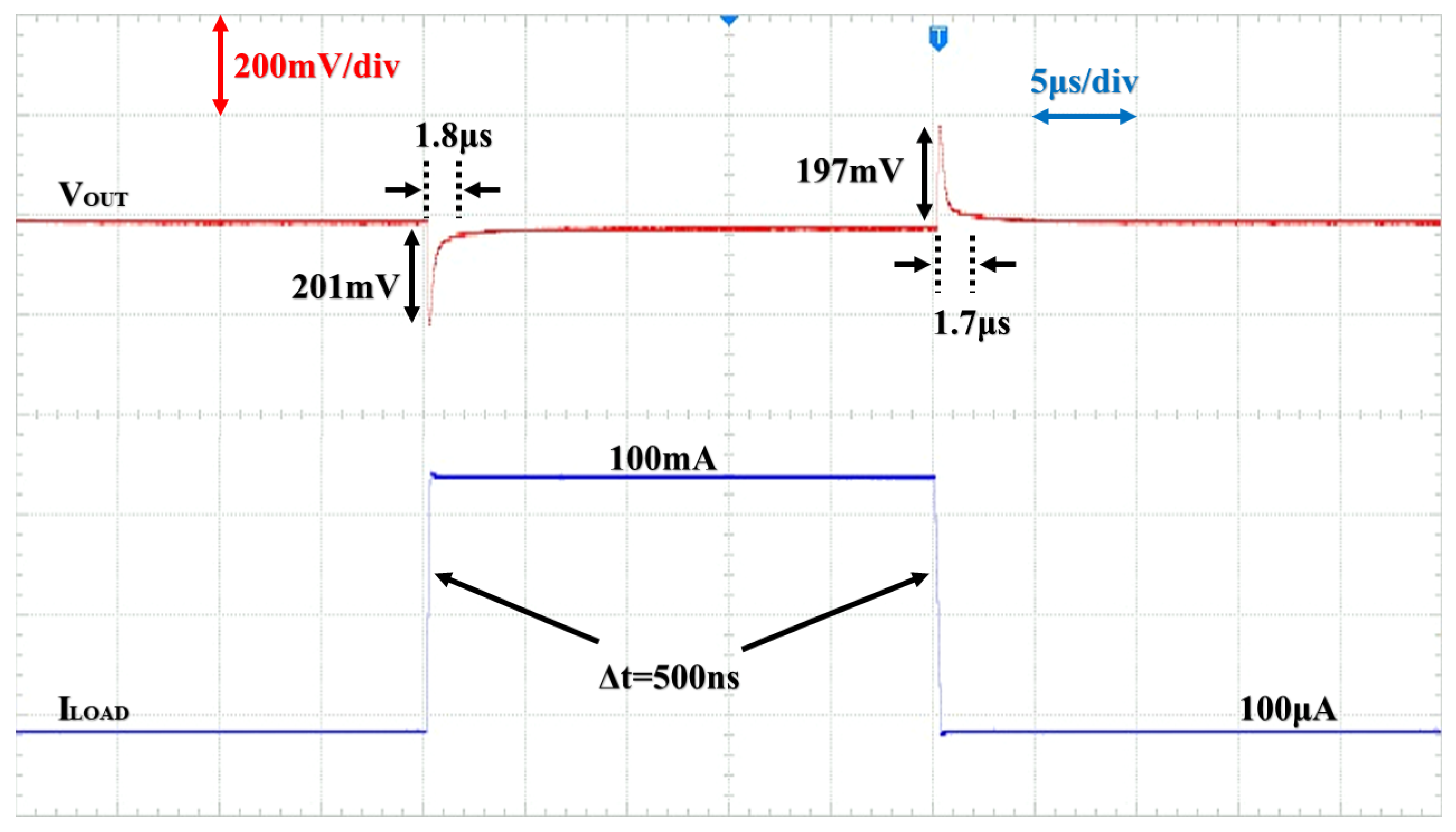

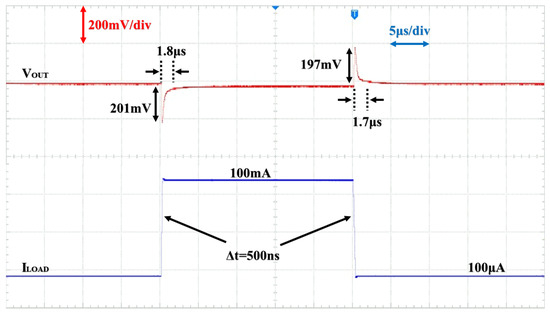

Figure 17 presents the load transient response of the OCL-LDO when the input voltage is 1.2 V and the output voltage is 1 V, where the load current switches between 100 A and 100 mA load current within 500 ns. As seen in the figure, the overshoot voltage is 197 mV, corresponding to a recovery time of 1.7 s. And when the load is changed from 100 A to 100 mA, the undershoot voltage is 201 mV, with a recovery time of 1.8 s. Compared with the simulation results in Figure 17, the overshoot and undershoot voltages of the measurement results are slightly increased, which is due to the parasitic capacitance at the output PAD.

Figure 17.

Load transient response as = 1.2 V and = 1 V.

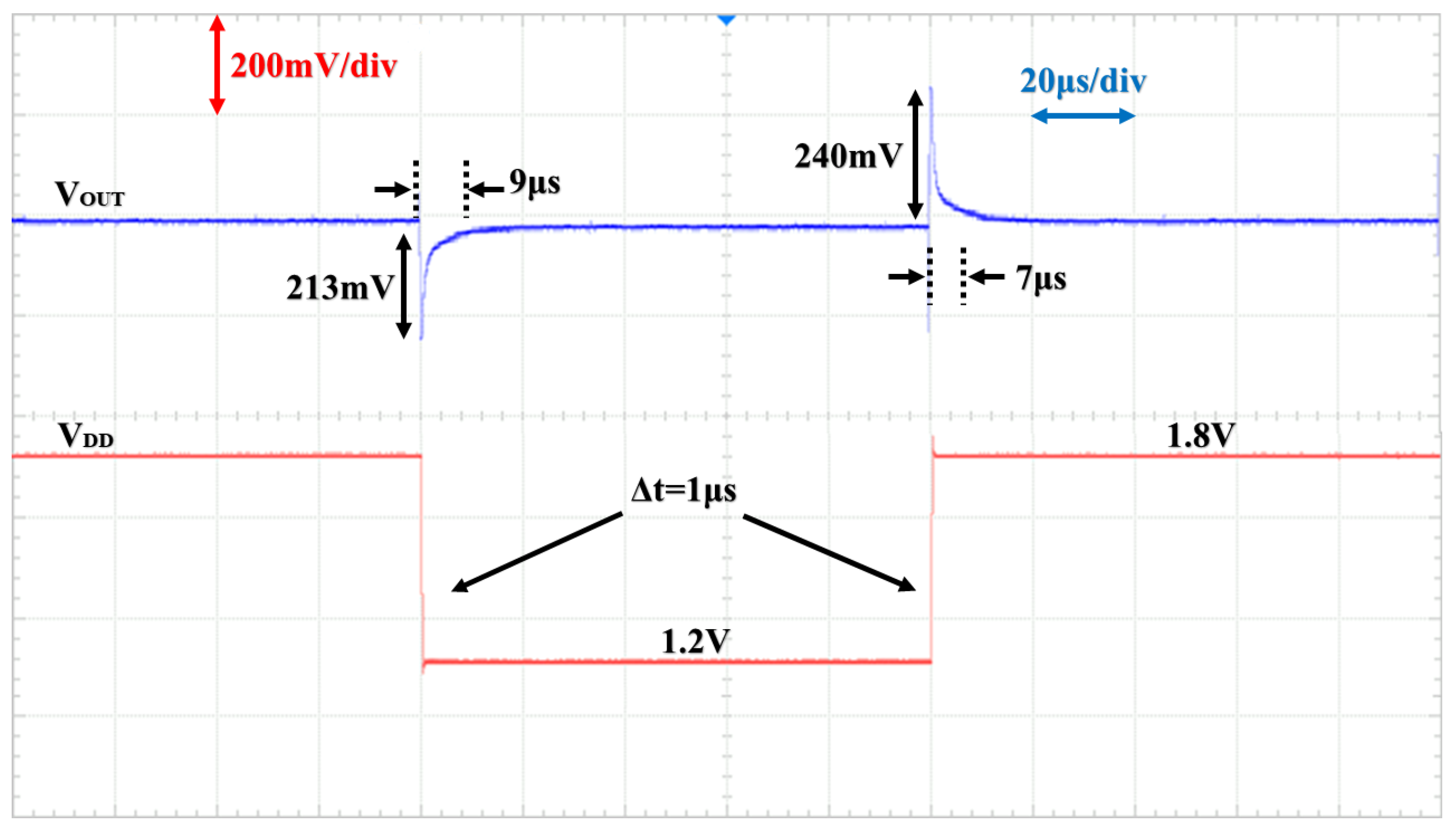

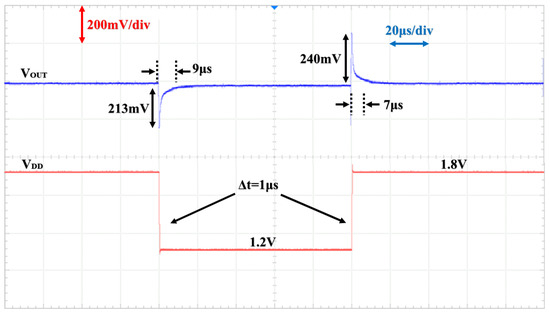

With a load current of 10 A, changing the input voltage from 1.2 V to 1.8 V in 1 s brings about an overshoot voltage of 240 mV and takes 7 s to recover to the designed output voltage. And when the input voltage is reduced, the undershoot voltage is 213 mV, for a recovery time of 9 s as shown in Figure 18.

Figure 18.

Line transient response as = 10 A.

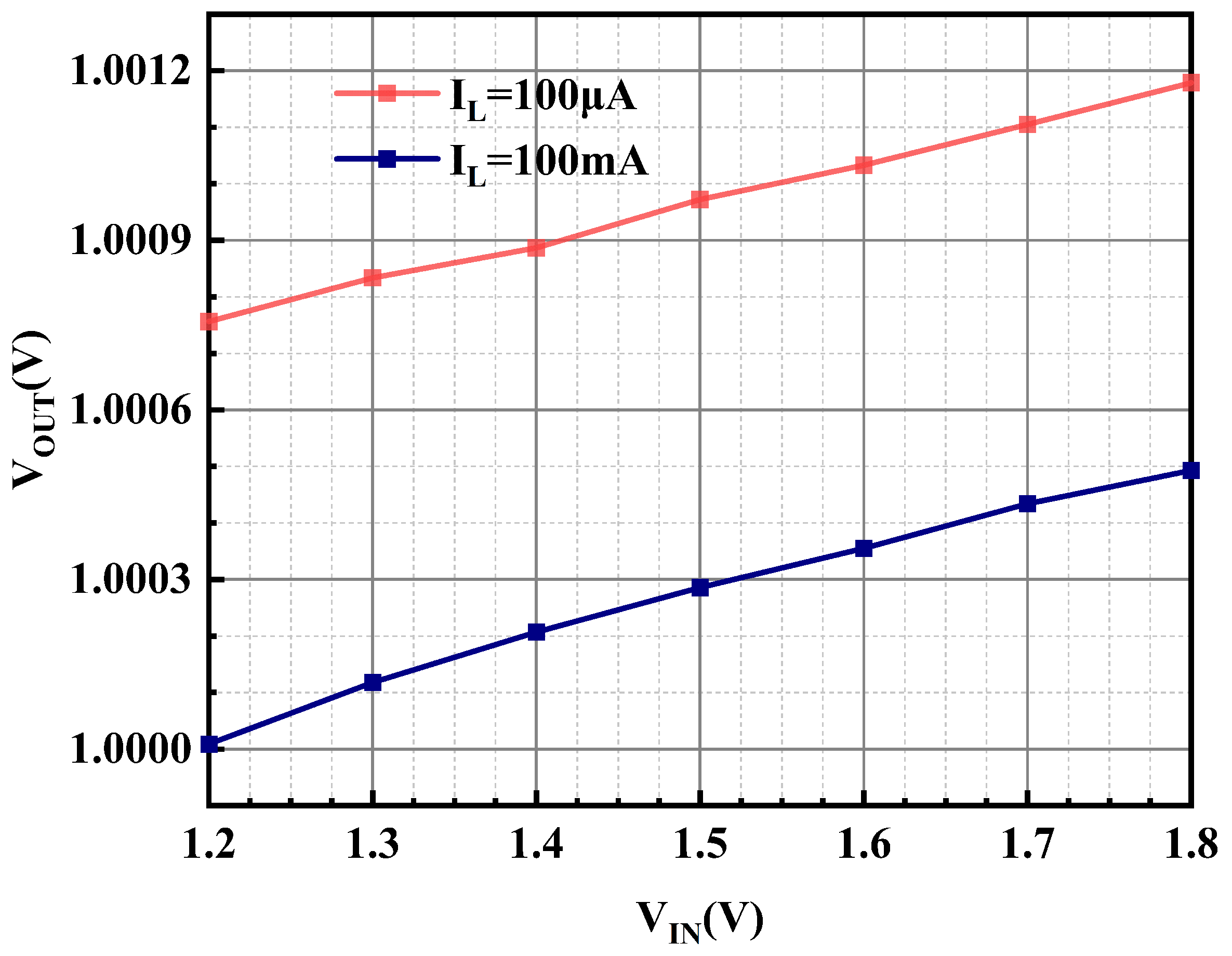

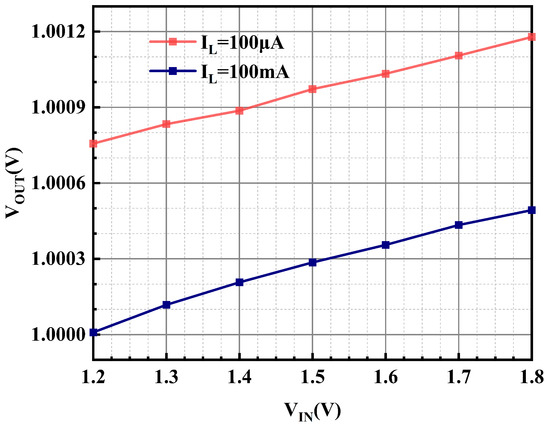

The low dropout regulator is a circuit structure that is capable of delivering a stable voltage value that has no significant deviation with the input voltage variation. In order to feature the effect of input voltage variation on the output voltage, the line regulation is proposed; Figure 19 shows the measurement results of the OCL-LDO proposed in this paper for the variation in the output voltage with the input voltage under different load currents, and its line regulation is 0.7 mV/V and 0.87 mV/V for load currents of 100 A and 100 mA.

Figure 19.

Measured line regulation of the proposed OCL-LDO under different loads.

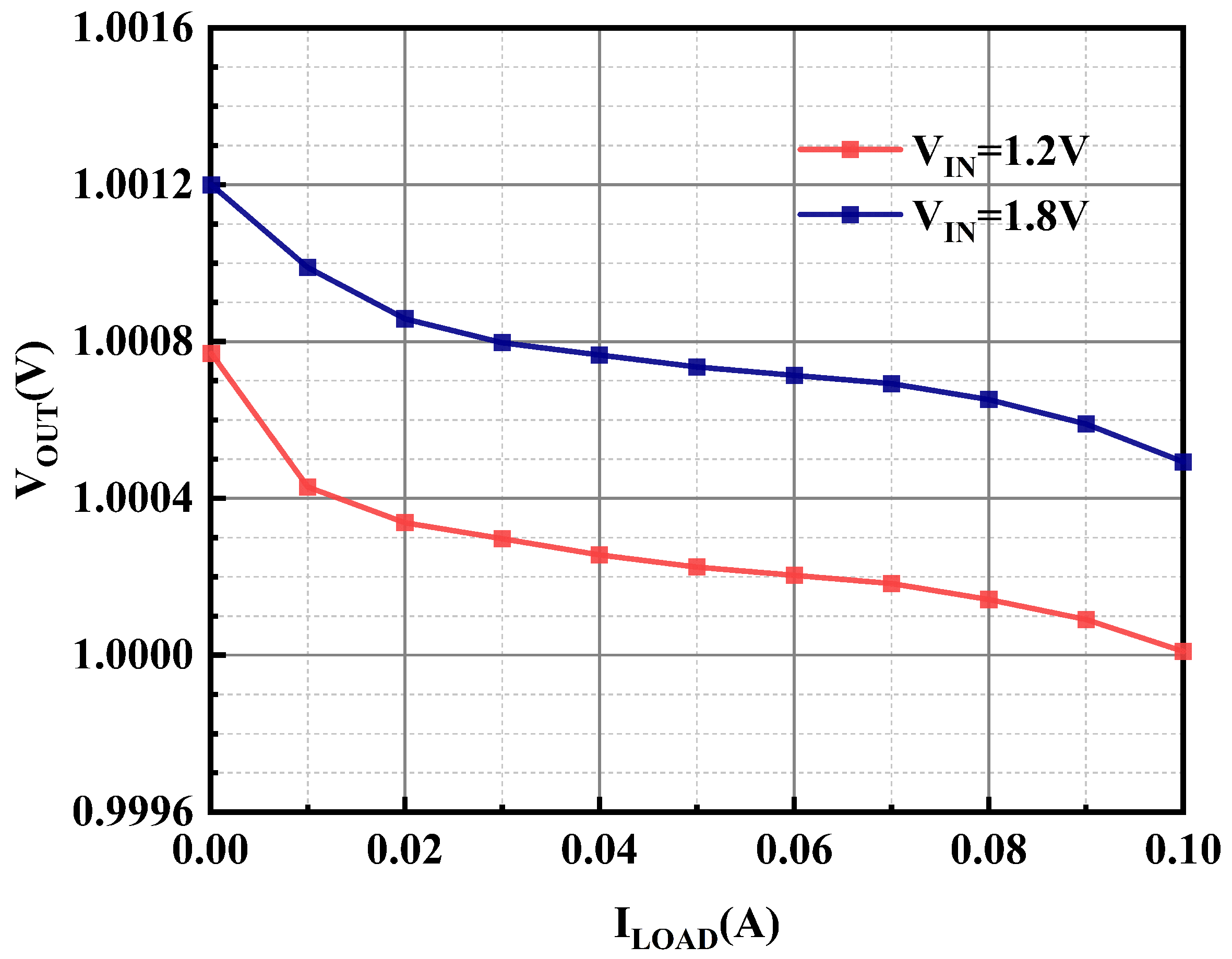

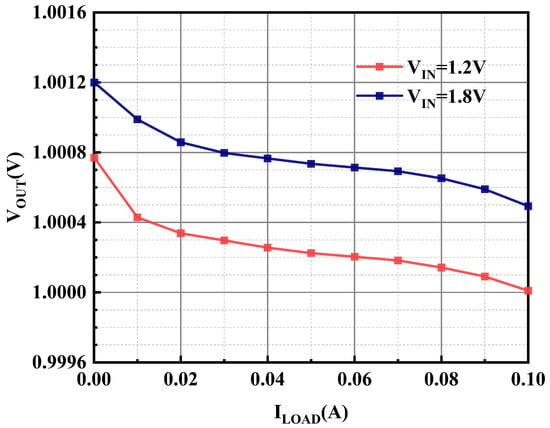

With similarity, the variation in the load current is also not supposed to make the output voltage generate large fluctuations. The experimental results of the load regulation of the OCL-LDO proposed in this paper are shown in Figure 20, which are 7.6 V/mA and 7.3 V/mA when the output voltage is 1 V, and when the input voltage is 1.2 V and 1.8 V, respectively.

Figure 20.

Measured load regulation of proposed OCL-LDO under different supply voltages.

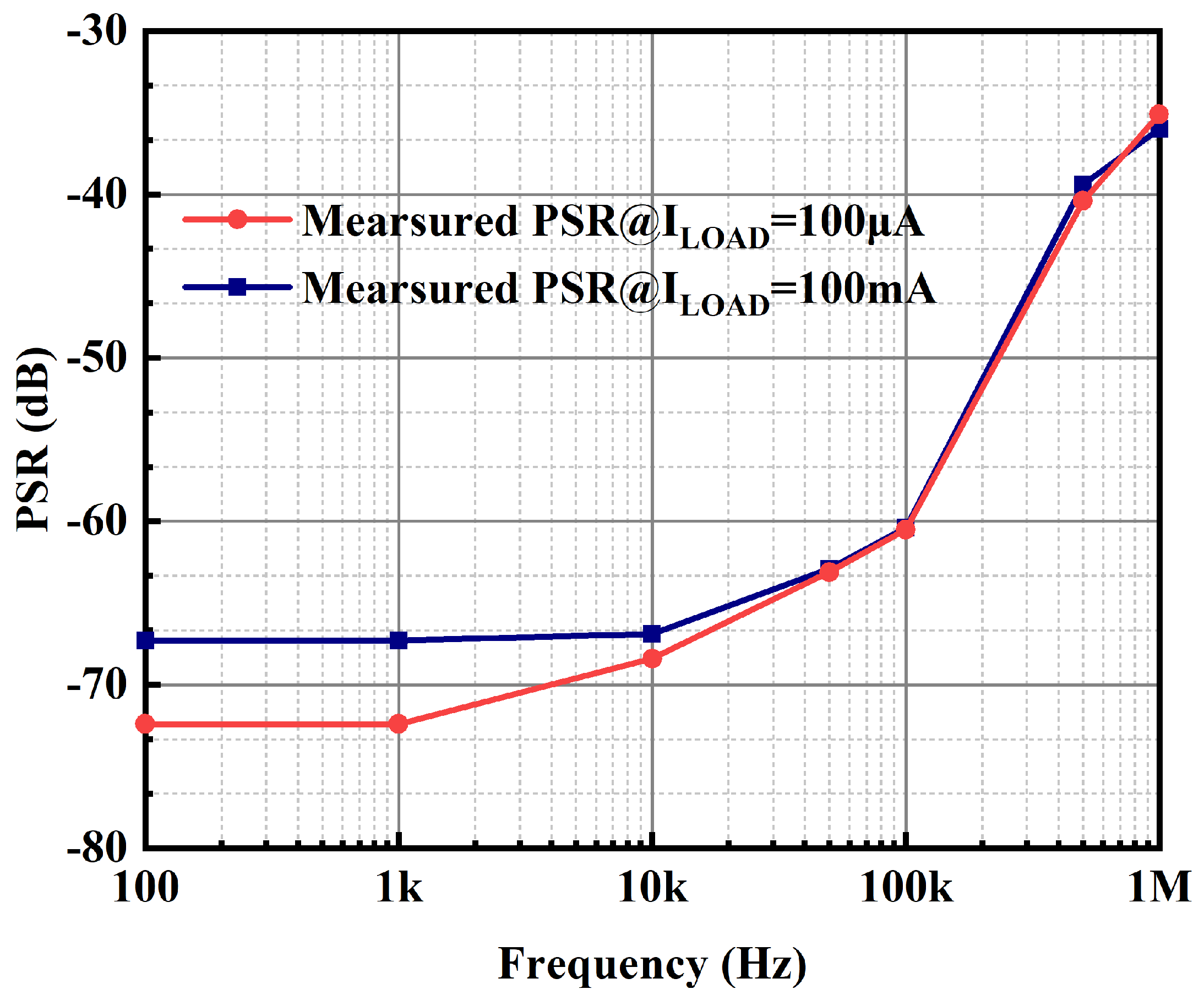

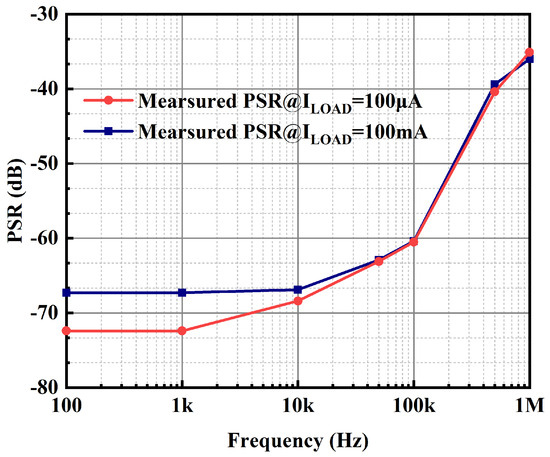

The OCL-LDO is required to have favorable ripple immunity to provide a stable voltage supply, so its PSR performance is also extremely important. The PSR test results of the OCL-LDO proposed in this paper are provided in Figure 21. Since the adaptive biasing scheme is included within the OCL-LDO proposed in this paper, the bias current of the error amplifier increases when the load current is high. The primary pole of the error amplifier increases, which also results in the PSR of the OCL-LDO having a larger zero at heavy loads than the corresponding zero at low loads [31]. The PSR at 1 KHz is −72.4 dB when the load current is 100 A.

Figure 21.

Measured PSR of the proposed OCL-LDO.

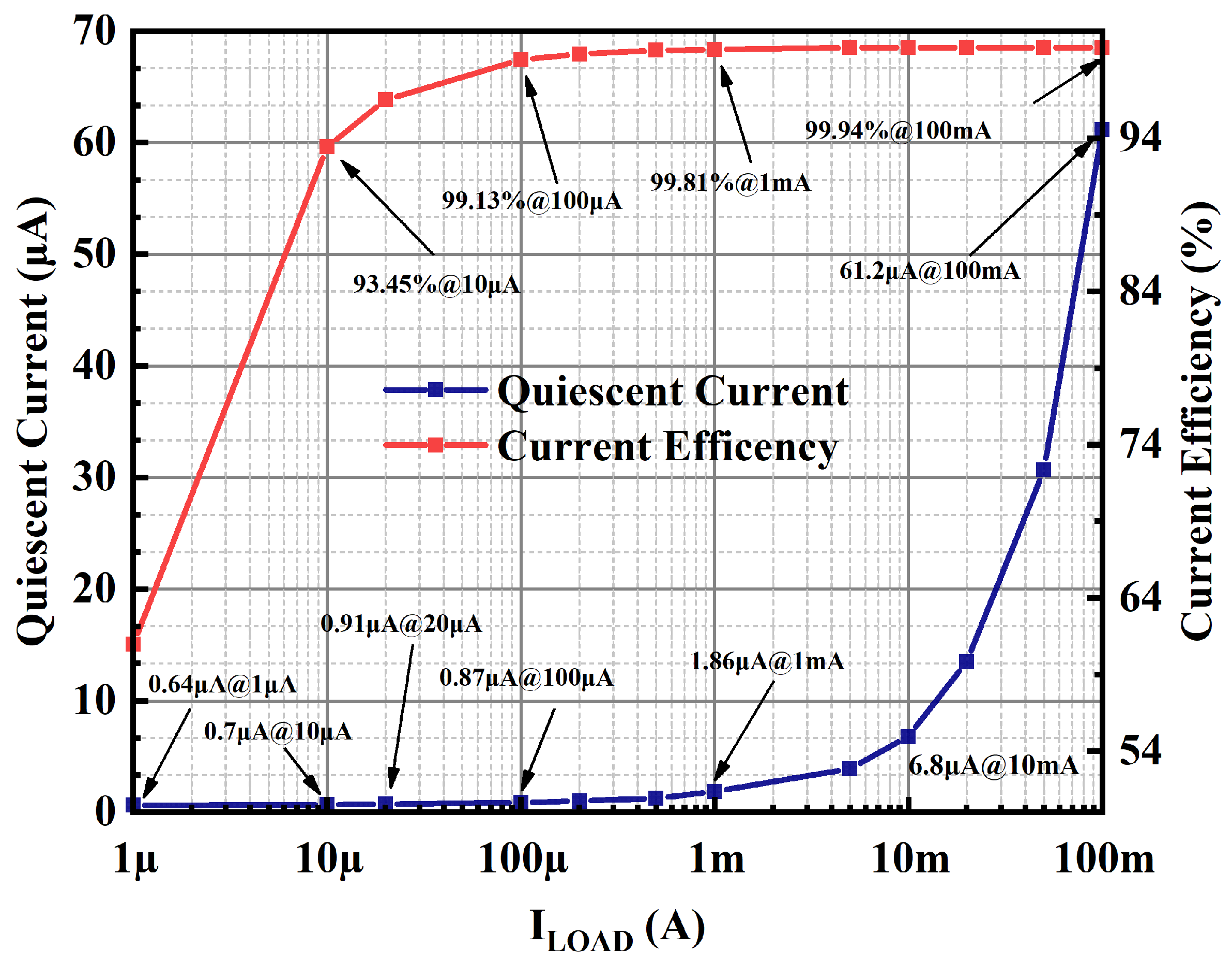

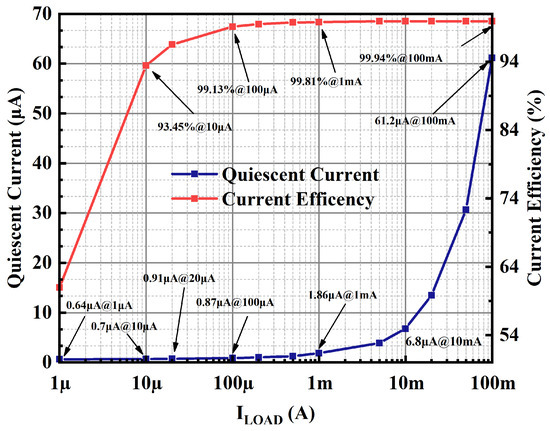

The quiescent current of this OCL-LDO increases with the load currents because of the adaptive biasing scheme within the OCL-LDO proposed in this paper. Measurement of the quiescent current of the OCL-LDO is performed by utilizing the test circuit schematic shown in Figure 15, which requires the supply voltage that is 1.2 V to be provided by the , and the input voltage is 1 V. The load currents could be calculated according to the different load resistances, and the quiescent current of the OCL-LDO is obtained by subtracting the load current from the current flowing out of the power supply. The quiescent current of the OCL-LDO proposed in this paper varies from 0.64–61.2 A as shown in Figure 22. Meanwhile, the current efficiency characterizes the effective conversion rate of the OCL-LDO to the input signals, and the peak current efficiency of the OCL-LDO proposed in this paper is 99.94%.

Figure 22.

Measurement results of quiescent current and current efficiency.

5. Discussion

For comprehensive characterization of the performance of proposed OCL-LDO, a Factor of Merit (FOM) is presented, and its expression is given as [32]:

where is the sum of the overshoot and undershoot voltages, is the quiescent current, and is the maximum load current. The key performance results of the OCL-LDO proposed in this paper and its comparison with prior works are provided in Table 2. As seen in the table, the OCL-LDO proposed in this paper is suitable for NB-IoT applications with good measurement results of the transient response, PSR, line regulation, and load regulation based on a low quiescent current.

Table 2.

Performance summary and comparison with prior works.

6. Conclusions

An ultra-low quiescent current OCL-LDO for narrow band IoT applications is proposed in this paper. In this paper, its overall structure and stability analysis are introduced, and the small-signal transfer function with and without considering the slew-rate enhancement circuit is given respectively. Meanwhile, the specific circuit design and key design considerations are shown in this paper, comparing the simulation results of the error amplifier before and after the addition of the gain increase method, and proposing a sub-threshold CMOS slew-rate enhancement circuit. The experimental results show that the proposed OCL-LDO has a minimum quiescent current of 640 nA and a maximum load current of 100 mA when the input voltage is 1.2 V and the output voltage is 1 V. The overshoot and undershoot voltages when the load current is switched between 100 A and 100 mA are 197 mV and 201 mV, respectively, and both of them have a recovery time of less than 2 s. Therefore, the OCL-LDO proposed in this paper features a favorable transient response based on an nA-level quiescent current, which is suitable for low-power NB-IoT applications.

Author Contributions

Conceptualization, Y.Z. and J.C. (Jueping Cai); methodology, Y.Z.; software, Y.Z.; validation, Y.Z. and Y.Y.; formal analysis, Y.Z.; investigation, Y.Y.; resources, Y.Z.; data curation, Y.Z.; writing—original draft preparation, Y.Z.; writing—review and editing, J.C. (Jizhang Chen) and Y.Y.; visualization, Y.Y.; supervision, J.C. (Jueping Cai); project administration, J.C. (Jueping Cai); funding acquisition, J.C. (Jueping Cai). All authors have read and agreed to the published version of the manuscript.

Funding

This work was supported in part by the National Natural Science Foundation of China (62274123), the Shaanxi Province Key Research and Development Program (2021ZDLGY02-01), and the Fundamental Research Funds for the Central Universities Grant (XJSJ23054).

Data Availability Statement

The original contributions presented in the study are included in the article, further inquiries can be directed to the corresponding author.

Conflicts of Interest

The authors declare that they have no known competing financial interests or personal relationships that could have appeared to influence the work reported in this paper.

References

- Wang, D.M.; Li, D.Z.; Wu, J.; Cai, J.H.; Zhong, Q.H.; Huang, X.; Hu, J.G. A 0.35 mm2 94.25 μW Fully Integrated NFC Tag IC Using 0.13 μm CMOS Process. IEEE Trans. Circuits Syst. I Regul. Pap. 2024, 71, 2612–2622. [Google Scholar] [CrossRef]

- Hu, C.; Zheng, D.; Yin, Y.; Lin, J.; Li, Y.; Li, W.; Xu, H. A Wideband Sliding Digital-IF Quadrature Digital Transmitter for Multimode NB-IoT/BLE Applications. IEEE J. Solid-State Circuits 2024, 59, 1509–1520. [Google Scholar] [CrossRef]

- Yu, Y.J.; Wang, Y.C.; Fan, C.H. Control Period Adaptation and Resource Allocation for Joint Uplink and Downlink in NB-IoT Networks. IEEE Internet Things J. 2024, 11, 16746–16757. [Google Scholar] [CrossRef]

- Odelberg, T.J.; Im, J.; Moosavifar, M.; Wentzloff, D.D. A Fully Integrated NB-IoT Wake-Up Receiver Utilizing an Optimized OFDM 12-Point FFT Wake-Up Engine. In Proceedings of the 2024 IEEE International Symposium on Circuits and Systems (ISCAS), New Delhi, India, 18–19 October 2024; pp. 1–5. [Google Scholar]

- Kim, T.; Kim, B.; Roh, J. A 54-nA Quiescent Current Capless LDO With −39-dB PSRR at 1 MHz Using a Load-Tracking Bandwidth Extension Technique. IEEE Trans. Circuits Syst. II Express Briefs 2024, 71, 1556–1560. [Google Scholar] [CrossRef]

- Liu, X.; Kamineni, S.; Breiholz, J.; Calhoun, B.H.; Li, S. A Sub-μW Energy-Performance-Aware IoT SoC With a Triple-Mode Power Management Unit for System Performance Scaling, Fast DVFS, and Energy Minimization. IEEE J. Solid-State Circuits 2024, 59, 2272–2285. [Google Scholar] [CrossRef]

- Adorni, N.; Stanzione, S.; Boni, A. A 10-mA LDO With 16-nA IQ and Operating From 800-mV Supply. IEEE J. Solid-State Circuits 2020, 55, 404–413. [Google Scholar] [CrossRef]

- Jiang, Y.; Wang, D.; Chan, P.K. A Quiescent 407-nA Output-Capacitorless Low-Dropout Regulator With 0–100-mA Load Current Range. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2019, 27, 1093–1104. [Google Scholar] [CrossRef]

- Shi, C.; Duncan, J.; Pu, Y.; Liu, G.; Homayoun, A.; Attar, R. An Ultralow-Power On-Die PMU in a 28-nm CMOS SoC with Direct Li-Ion Battery-Attach Capability. IEEE J. Emerg. Sel. Top. Power Electron. 2018, 6, 465–476. [Google Scholar] [CrossRef]

- Lee, S.; Lim, J.; Han, J. A PSRR-Enhanced Fast-Response Inverter-Based LDO for Mobile Devices. IEEE Trans. Circuits Syst. II Express Briefs 2024, 71, 3226–3230. [Google Scholar] [CrossRef]

- Darwish, M.; Mohsen, M.; Saad, A.; Weldon, J.A. Ultra low-Area Hysteretic Control LDO with Sub-1 μA Quiescent Current. IEEE Trans. Circuits Syst. II Express Briefs 2016, 63, 1004–1008. [Google Scholar] [CrossRef]

- Kim, J.S.; Javed, K.; Min, K.H.; Roh, J. A 13.5-nA Quiescent Current LDO With Adaptive Ultra-Low-Power Mode for Low-Power IoT Applications. IEEE Trans. Circuits Syst. II Express Briefs 2023, 70, 3278–3282. [Google Scholar] [CrossRef]

- Guo, T.; Kang, W.; Roh, J. A 0.9-μA Quiescent Current High PSRR Low Dropout Regulator Using a Capacitive Feed-Forward Ripple Cancellation Technique. IEEE J. Solid-State Circuits 2022, 57, 3139–3149. [Google Scholar] [CrossRef]

- Huang, J.R.; Wen, Y.H.; Yang, T.H.; Lee, J.J.; Liu, G.T.; Chen, K.H.; Lin, Y.H.; Lin, S.R.; Tsai, T.Y. A 10 nA Ultra-Low Quiescent Current and 60 ns Fast Transient Response Low-Dropout Regulator for Internet-of-Things. IEEE Trans. Circuits Syst. I Regul. Pap. 2022, 69, 139–147. [Google Scholar] [CrossRef]

- Huang, Y.; Lu, Y.; Maloberti, F.; Martins, R.P. Nano-Ampere Low-Dropout Regulator Designs for IoT Devices. IEEE Trans. Circuits Syst. I Regul. Pap. 2018, 65, 4017–4026. [Google Scholar] [CrossRef]

- Bahramali, A.; Lopez-Vallejo, M. An RFID-Based Self-Biased 40 nm Low Power LDO Regulator for IoT Applications. Micromachines 2021, 12, 396. [Google Scholar] [CrossRef]

- Ni, S.; Chen, Z.; Hu, C.; Chen, H.; Wang, Q.; Li, X.; Song, S.; Song, Z. An output-capacitorless low-dropout regulator with slew-rate enhancement. Micromachines 2022, 13, 1594. [Google Scholar] [CrossRef]

- Lee, C.K.; Lee, C.H.; Jeon, Y.J.; Oh, Y.J.; Lee, B.; Hong, S.W. A 92 ns Settling-Time Fast-Transient Capacitor-Less LDO with a Stable Class B Bandwidth-Boosting Error Amplifier and an Improved Buffer for Mobile Applications. IEEE Trans. Ind. Electron. 2024, 71, 11696–11700. [Google Scholar] [CrossRef]

- Pereira-Rial, Ó.; López, P.; Carrillo, J.M. 0.6-V-VIN 7.0-nA-IQ 0.75-mA-IL CMOS Capacitor-Less LDO for Low-Voltage Micro-Energy-Harvested Supplies. IEEE Trans. Circuits Syst. I Regul. Pap. 2022, 69, 599–608. [Google Scholar] [CrossRef]

- Silva-Martinez, J.; Liu, X.; Zhou, D. Recent Advances on Linear Low-Dropout Regulators. IEEE Trans. Circuits Syst. II Express Briefs 2021, 68, 568–573. [Google Scholar] [CrossRef]

- Chen, C.; Sun, M.; Wang, L.; Huang, T.; Xu, M. A Fast Transient Response Capacitor-Less LDO with Transient Enhancement Technology. Micromachines 2024, 15, 299. [Google Scholar] [CrossRef]

- Hu, C.; Chen, Z.; Ni, S.; Wang, Q.; Li, X.; Chen, H.; Song, Z. A fully integrated low-dropout regulator with improved load regulation and transient responses. Micromachines 2022, 13, 1668. [Google Scholar] [CrossRef] [PubMed]

- Fan, H.; Feng, L.; Diao, X.; Xie, X.; Wang, C.; Li, G.; Wei, Q.; Qiao, F.; Feng, Q.; Bonizzoni, E. A Fast Transient LDO Regulator Featuring High PSRR Over 100-kHz Frequency Range with Adaptive, Dynamic Biasing, and Current Mode Feed-Forward Amplifier. IEEE Trans. Circuits Syst. II Express Briefs 2024, 71, 1764–1768. [Google Scholar] [CrossRef]

- Ivanov, V. Design Methodology and Circuit Techniques for Any-Load Stable LDOs with Instant Load Regulation and Low Noise. In Analog Circuit Design: High-Speed Clock and Data Recovery, High-Performance Amplifiers, Power Management; Steyaert, M., Roermund, A.H.M.v., Casier, H., Eds.; Springer: Dordrecht, The Netherlands, 2009; pp. 339–358. [Google Scholar] [CrossRef]

- Zhao, J.; Gao, Y.; Zhang, T.T.; Son, H.; Heng, C.H. A 310-nA Quiescent Current 3-fs-FoM Fully Integrated Capacitorless Time-Domain LDO with Event-Driven Charge Pump and Feedforward Transient Enhancement. IEEE J. Solid-State Circuits 2021, 56, 2924–2933. [Google Scholar] [CrossRef]

- Zhang, Y.; Ge, Q.; Zeng, Y. A 0.6 VIN 100 mV Dropout Capacitor-Less LDO with 220 nA IQ for Energy Harvesting System. Micromachines 2023, 14, 998. [Google Scholar] [CrossRef]

- Tang, J.; Lee, J.; Roh, J. Low-Power Fast-Transient Capacitor-Less LDO Regulator with High Slew-Rate Class-AB Amplifier. IEEE Trans. Circuits Syst. II Express Briefs 2019, 66, 462–466. [Google Scholar] [CrossRef]

- Qu, W.; Singh, S.; Lee, Y.; Son, Y.S.; Cho, G.H. Design-Oriented Analysis for Miller Compensation and Its Application to Multistage Amplifier Design. IEEE J. Solid-State Circuits 2017, 52, 517–527. [Google Scholar] [CrossRef]

- Yan, Z.; Mak, P.I.; Law, M.K.; Martins, R.P. A 0.016-mm2 144-μW Three-Stage Amplifier Capable of Driving 1-to-15 nF Capacitive Load with >0.95-MHz GBW. IEEE J. Solid-State Circuits 2013, 48, 527–540. [Google Scholar] [CrossRef]

- Ming, X.; Kuang, J.J.; Gong, X.C.; Lin, Z.; Xiong, J.; Qin, Y.; Wang, Z.; Zhang, B. A Fast-Transient Capacitorless LDO with Dual Paths Active-Frequency Compensation Scheme. IEEE Trans. Power Electron. 2022, 37, 10332–10347. [Google Scholar] [CrossRef]

- Gupta, V.; Rincon-Mora, G.; Raha, P. Analysis and design of monolithic, high PSR, linear regulators for SoC applications. In Proceedings of the IEEE International SOC Conference, Santa Clara, CA, USA, 12–15 September 2004; pp. 311–315. [Google Scholar] [CrossRef]

- Răducan, C.; Grăjdeanu, A.T.; Plesa, C.S.; Neag, M.; Negoiţă, A.; Ţopa, M.D. LDO With Improved Common Gate Class-AB OTA Handles any Load Capacitors and Provides Fast Response to Load Transients. IEEE Trans. Circuits Syst. I Regul. Pap. 2020, 67, 3740–3752. [Google Scholar] [CrossRef]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).