A Wafer-Level Fabricated Heating–Vacuum Micro-Platform with Resonant MEMS Monolithically Integrated

Abstract

1. Introduction

2. Design

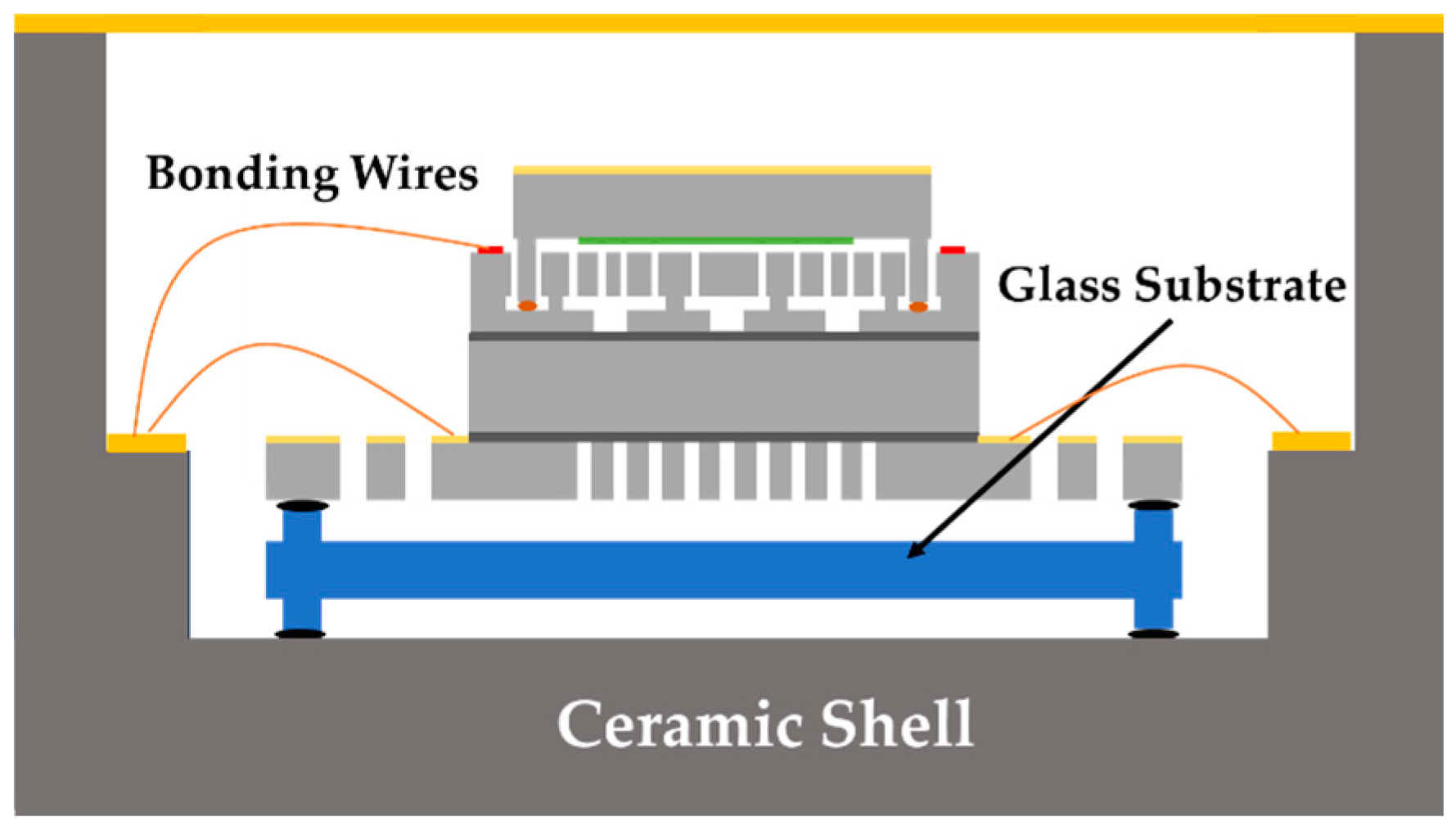

2.1. Platform Structure

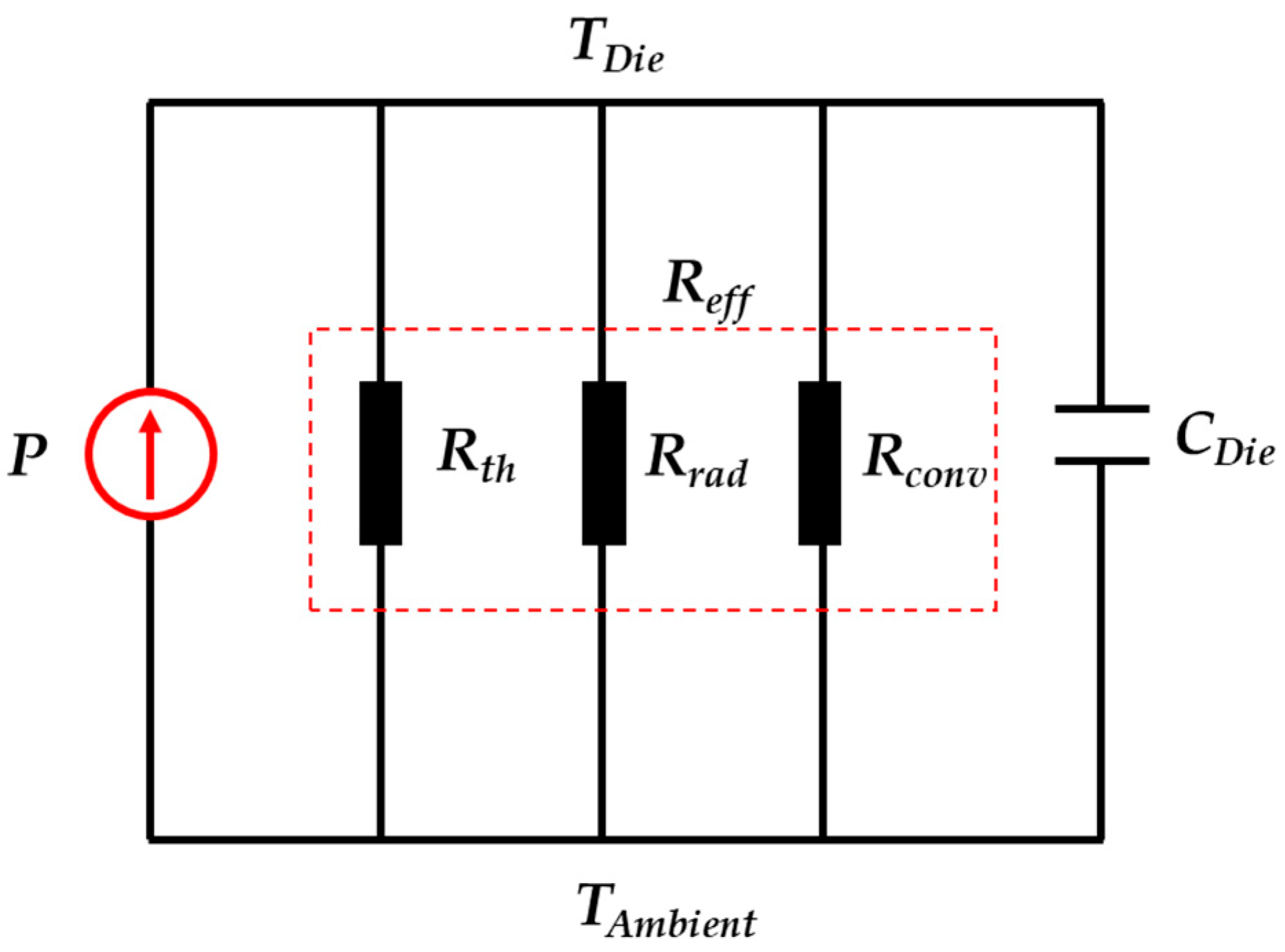

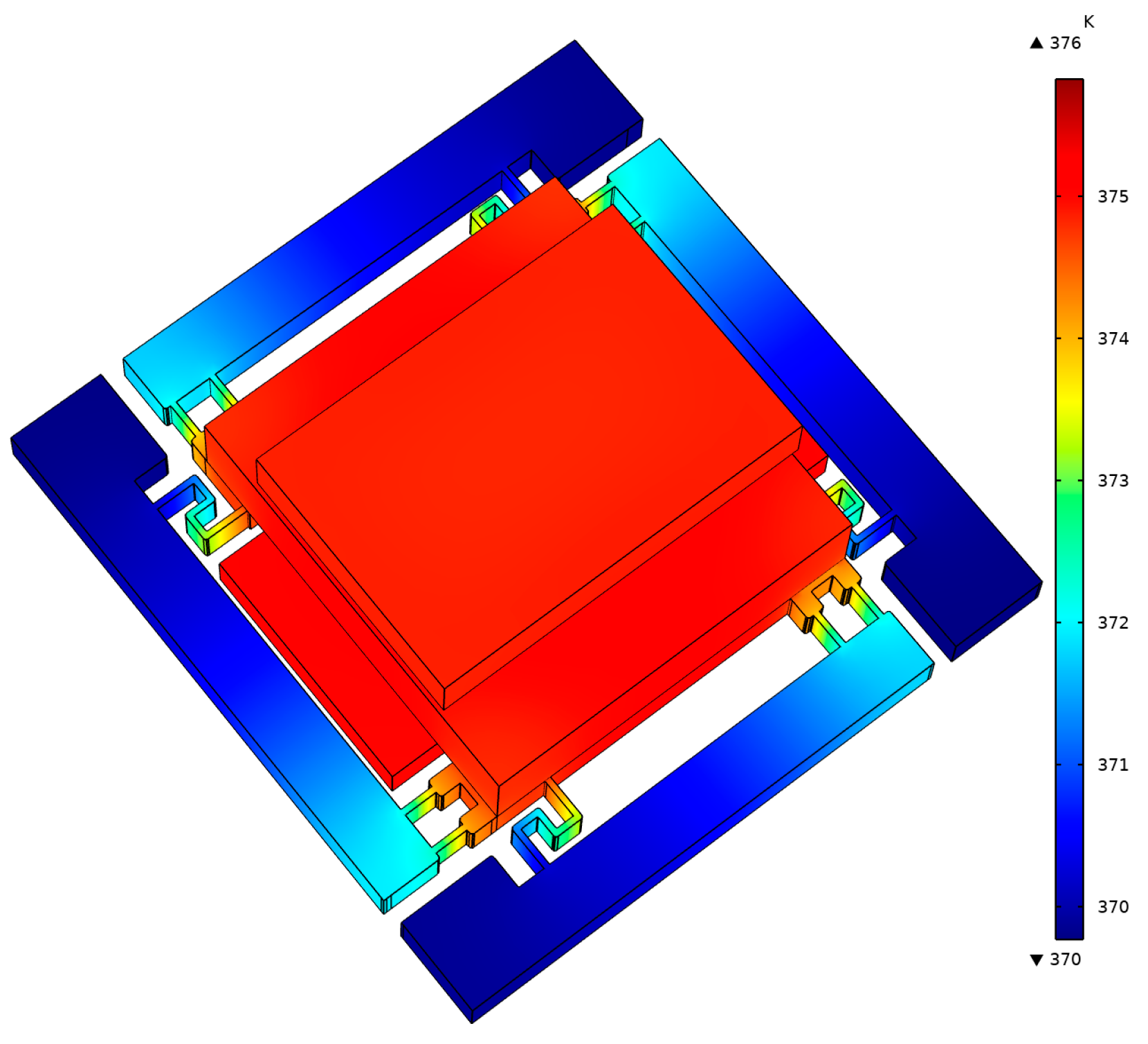

2.2. Theoretical Analysis and Thermal Optimization

3. Fabrication

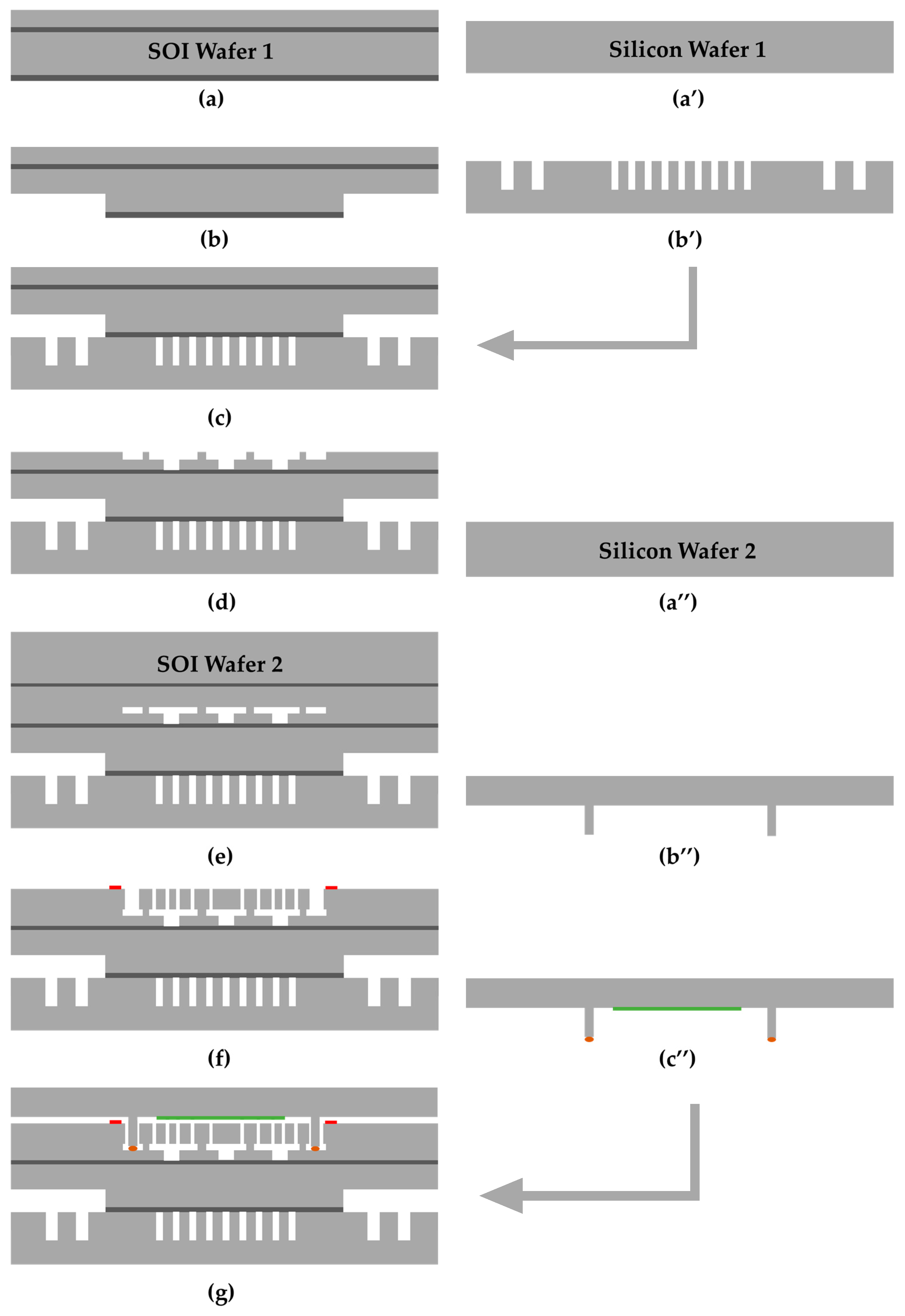

- The process flow begins from SOI wafer 1 (Figure 5a). Deep trenches are etched on the back of the SOI wafer 1 substrate (Figure 5b) using deep reactive ion etching (DRIE), which will later expose the heater pads and die attachment structures through the dicing process. The depth of the trench is approximately 50 μm.

- Meanwhile, isolation and heating structure patterns are fabricated on silicon wafer 1 through photolithography and the DRIE process (Figure 5a’,b’). The etching depth is about 250 μm.

- SOI wafer 1 and silicon wafer 1 are bonded together using fusion bonding (Figure 5c). Fusion bonding annealing is performed at a temperature of 1100 °C for a duration of 4 h.

- The device layer of SOI wafer 1 is processed to form anchors, cavities of the movable structures, and interconnects for the resonator (Figure 5d). The thickness of the SOI device-layer is about 10 μm. First, shallow cavities are etched using DRIE to form anchors, with an etching depth of approximately 5 μm. Subsequently, air isolation is achieved by performing DRIE between the silicon interconnects down to the buried oxide layer.

- SOI wafer 2 is introduced, and subsequently, fusion bonding is performed with SOI wafer 1 (Figure 5e), wherein the device layer of SOI wafer 2 serves as the MEMS movable structure layer. The device layer of SOI wafer 2 is about 50 μm. The substrate of SOI wafer 2 is removed via grinding and KOH wet etching. Subsequently, MEMS movable structures are fabricated on the device layer using photolithography and DRIE processes, and metal pads are deposited via sputtering on the same layer (Figure 5f).

- On silicon wafer 2 (Figure 5a’’), a KOH etching process is used to create the cap cavity structure and the bonding seal ring (Figure 5b’’). The depth of the cavity is approximately 100 μm. Glass frit is then printed onto the seal ring by using the screen-printing process, and a Ti-based getter film is deposited inside the cavity via electron beam evaporation (Figure 5c’’).

- The cap wafer is then bonded with the MEMS movable structure layer using glass frit bonding in a vacuum bonder, thereby achieving wafer-level vacuum packaging (Figure 5g). The bonding temperature is maintained at 450 °C for 1 h to fully activate the getter, and the vacuum pressure in the bonding chamber is set to less than 0.075 mTorr.

- The back of silicon wafer 1 is ground using an 8000-grit grinding wheel to release the isolation and heating structure (Figure 5h). The grinding equipment is equipped with an online thickness detection system, which ensures the grinding thickness accuracy is maintained within ±3 μm. The final remaining thickness of the silicon wafer 1 is approximately 180 μm.

4. Results and Discussion

4.1. Wafer-Level Vacuum Packaging Characterization

4.1.1. Package Pressure

4.1.2. Q-Factor of the Resonator

4.2. Micro-Oven Characterization

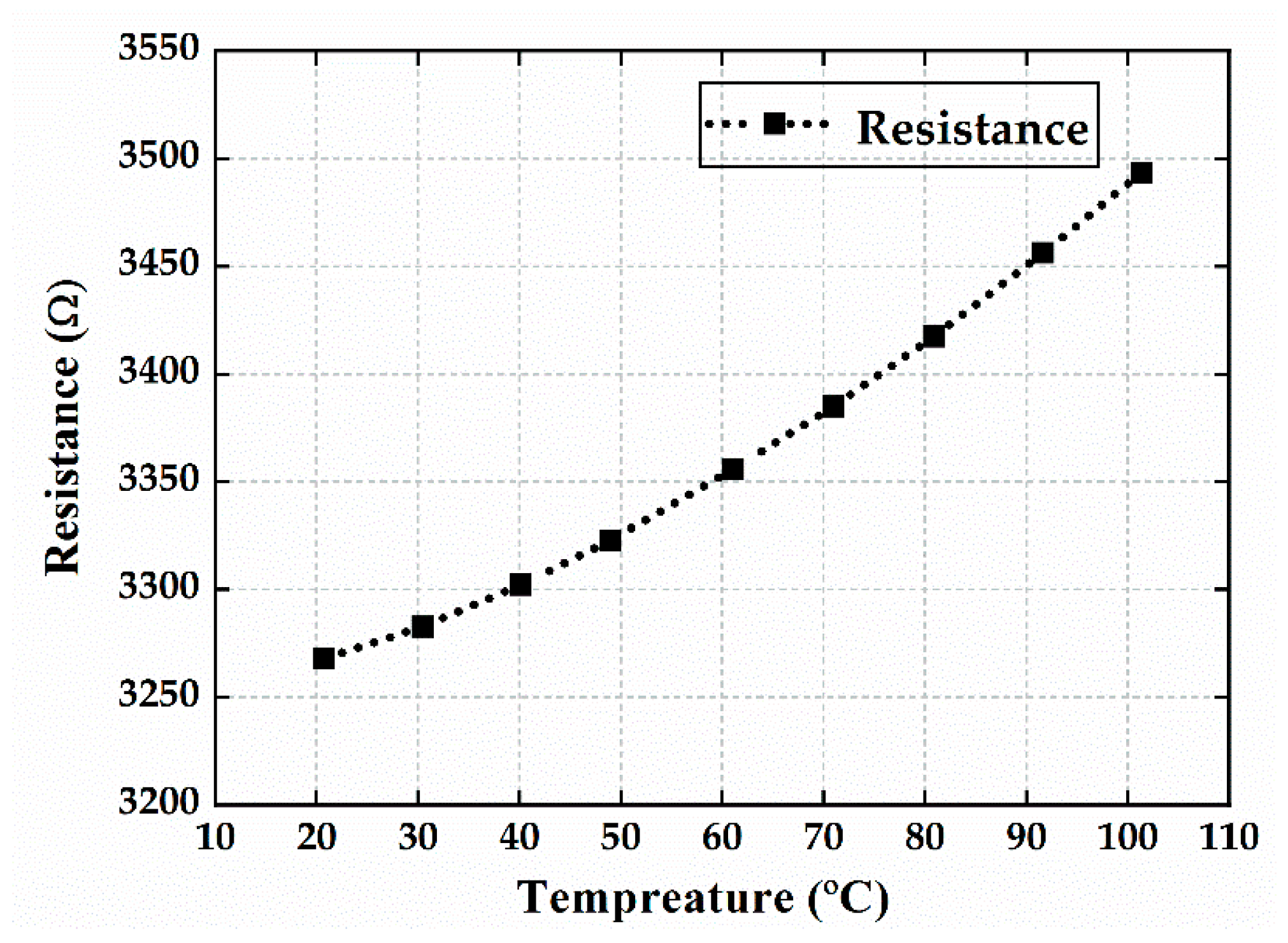

4.2.1. Thermistor Calibration

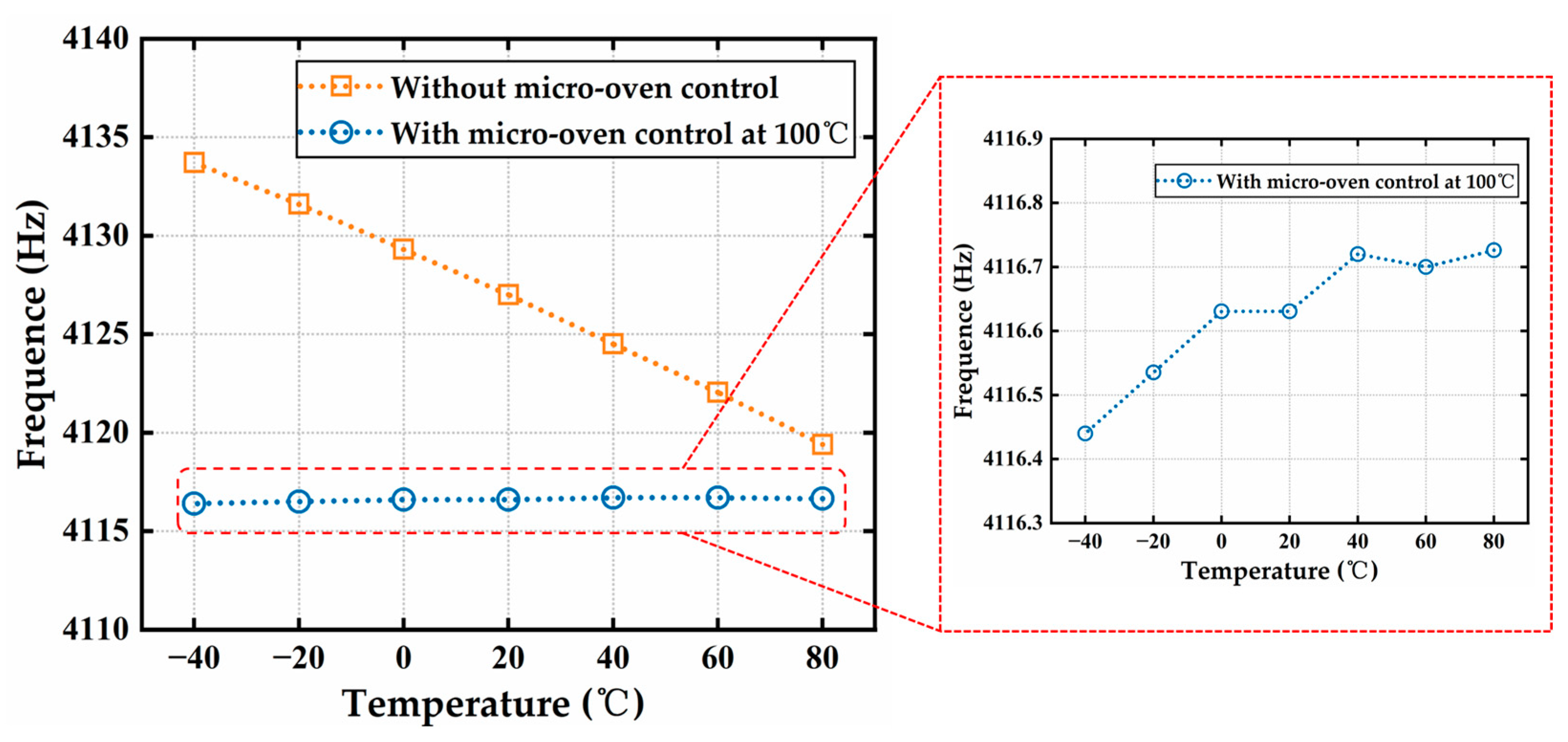

4.2.2. Temperature Coefficient of Resonant Frequency

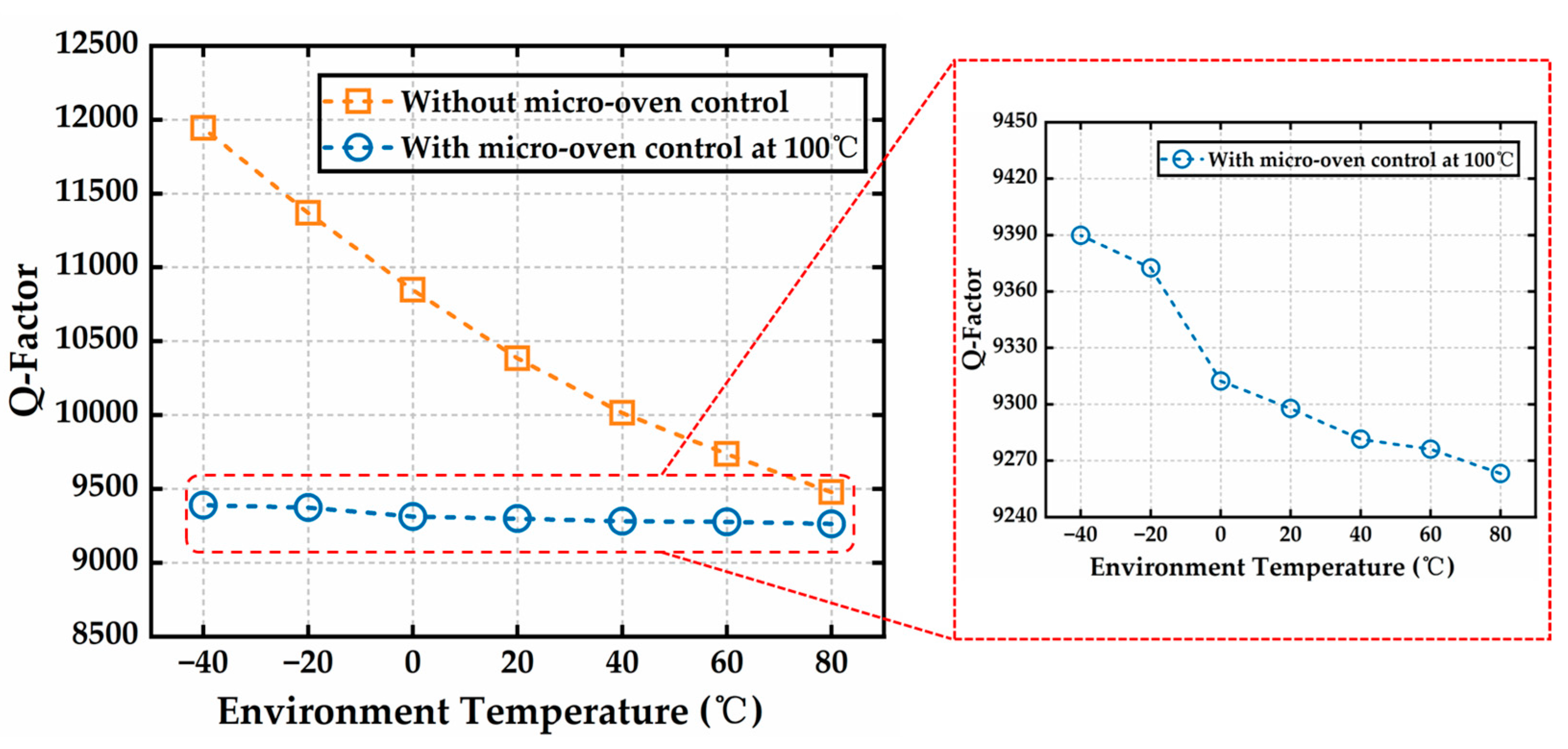

4.2.3. Temperature Coefficient of the Q-Factor

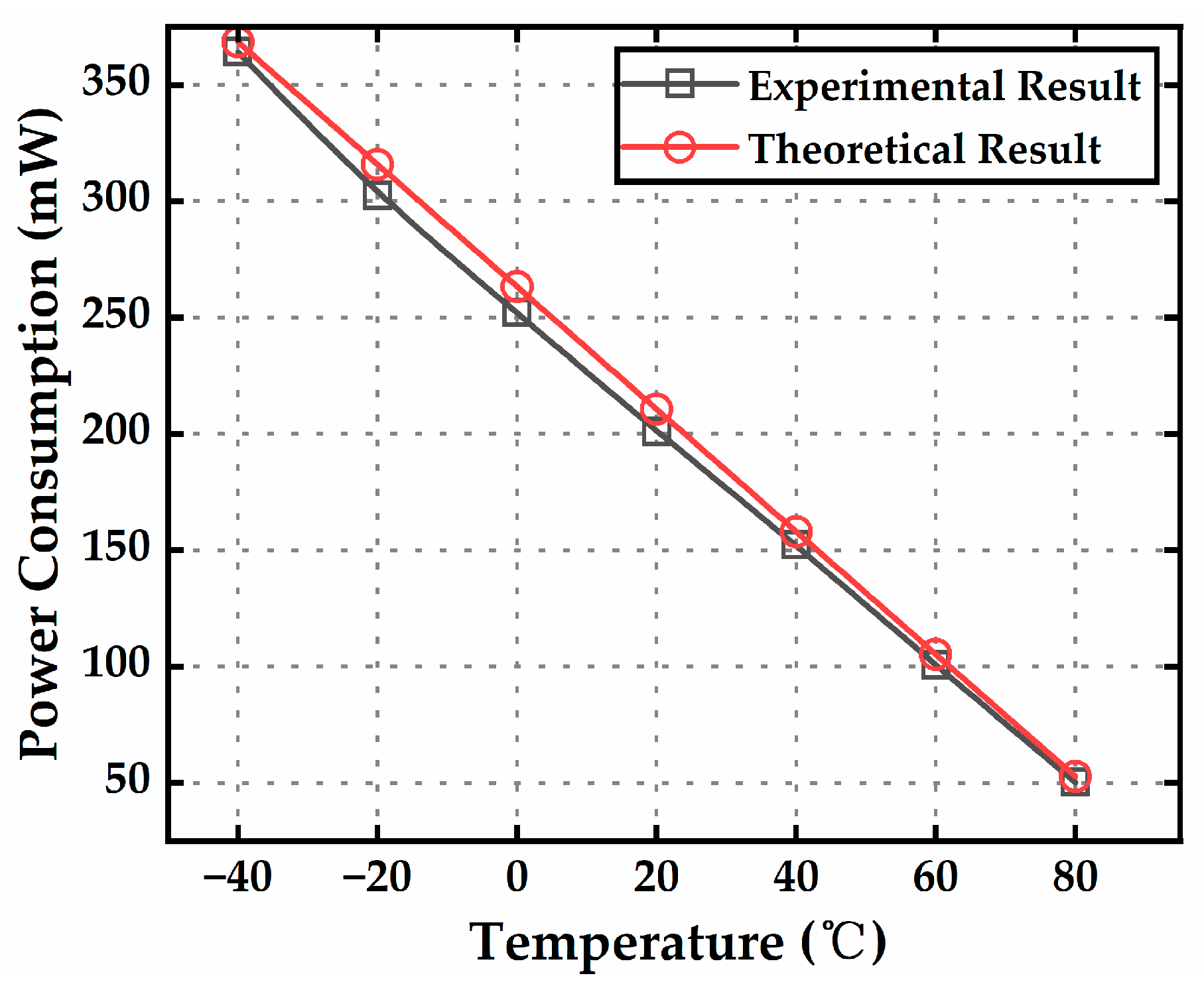

4.2.4. Power Consumption

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Zhai, Z.; Xiong, X.; Ma, L.; Wang, Z.; Wang, K.; Wang, B.; Zhang, M.; Zou, X. A scale factor calibration method for MEMS resonant accelerometers based on virtual accelerations. Micromachines 2023, 14, 1408. [Google Scholar] [CrossRef] [PubMed]

- Qin, S.; Gai, H.; Chen, Y. Status and deveopment of high-performance MEMS gyroscope. In Proceedings of the 2024 IEEE 6th Advanced Information Management, Communicates, Electronic and Automation Control Conference (IMCEC), Chongqing, China, 24–26 May 2024. [Google Scholar]

- Lee, S.H.; Lee, S.W.; Najafi, K. A generic environment-resistant packaging technology for MEMS. In Proceedings of the TRANSDUCERS 2007—2007 International Solid-State Sensors, Actuators and Microsystems Conference, Lyon, France, 10–14 June 2007. [Google Scholar]

- Kim, S.J.; Dean, R.; Flowers, G.; Chen, C. Active Vibration Control and Isolation for Micromachined Devices. J. Mech. Des. 2009, 131, 091002. [Google Scholar] [CrossRef]

- Schiwietz, D.; Weig, E.M.; Degenfeld-Schonburg, P. Temperature dependence of quality factors at high frequencies in MEMS gyroscopes. In Proceedings of the 2023 IEEE 36th International Conference on Micro Electro Mechanical Systems (MEMS), Munich, Germany, 15–19 January 2023. [Google Scholar]

- Yoon, S.W.; Lee, S.; Perkins, N.C.; Najafi, K. Shock-protection improvement using integrated novel shock-protection technologies. J. Microelectromech. Syst. 2011, 20, 1016–1031. [Google Scholar] [CrossRef]

- Yoon, S.W.; Lee, S.; Najafi, K. Vibration-induced errors in MEMS tuning fork gyroscopes. Sens. Actuat. A Phys. 2012, 180, 32–44. [Google Scholar] [CrossRef]

- You, W.; Pei, B.; Sun, K.; Zhang, L.; Yang, H.; Li, X. Oven controlled N++[100] length-extensional mode silicon resonator with frequency stability of 1 ppm over industrial temperature range. J. Micromech. Microeng. 2017, 27, 095002. [Google Scholar] [CrossRef]

- Pei, B.; Sun, K.; Yang, H.; Ye, C.; Zhong, P.; Yu, T.; Li, X. Oven-controlled MEMS oscillator with integrated micro-evaporation trimming. Sensors 2020, 20, 2373. [Google Scholar] [CrossRef]

- Askari, S.; Asadian, M.H.; Kakavand, K.; Shkel, A.M. Vacuum sealed and getter activated MEMS quad mass gyroscope demonstrating better than 1.2 million quality factor. In Proceedings of the 2016 IEEE International Symposium on Inertial Sensors and Systems, Laguna Beach, CA, USA, 22–25 February 2016. [Google Scholar]

- Liang, H.; He, X.; Xiong, B. Two-mask wafer-level vacuum packaging with bulk-Si 3D interconnects for MEMS devices and its package performances. IEEE Sens. J. 2022, 22, 14522–14530. [Google Scholar] [CrossRef]

- Wenk, B.; Collet, J.; Gaff, V. Technology platform for high performance MEMS inertial & vibration sensors. In Proceedings of the 2024 IEEE International Symposium on Inertial Sensors and Systems (INERTIAL), Hiroshima, Japan, 25–28 March 2024. [Google Scholar]

- Lin, D.; Macdonald, R.; Popp, J.; Alberda, M.; Andarawis, E.; Aimi, M. Low-cost navigation-grade MEMS fabrication platform to enable PNT innovations. In Proceedings of the 2023 IEEE/ION Position, Location and Navigation Symposium (PLANS), Monterey, CA, USA, 24–27 April 2023. [Google Scholar]

- Khan, M.J.; Suzuki, Y.; Gong, T.; Tsukamoto, T.; Tanaka, S. MEMS resonator vacuum-sealed by silicon migration and hydrogen outdiffusion. In Proceedings of the 2023 IEEE 36th International Conference on Micro Electro Mechanical Systems (MEMS), Munich, Germany, 15–19 January 2023. [Google Scholar]

- Wang, H.; Quan, H.; Zhou, J.; Zhang, L.; Xie, J.; Chang, H. A wafer-level vacuum packaged MEMS disk resonator gyroscope with 0.42°/h bias instability within ±300°/s full scale. IEEE Trans. Ind. Electron. 2022, 69, 5304–5313. [Google Scholar] [CrossRef]

- Torunbalci, M.M.; Gavcar, H.D.; Yesil, F.; Alper, S.E.; Akin, T. An all-silicon process platform for wafer-level vacuum packaged MEMS devices. IEEE Sens. J. 2021, 21, 13958–13964. [Google Scholar] [CrossRef]

- Gong, T.; Khan, M.J.; Suzuki, Y.; Tsukamoto, T.; Tanaka, S. Vacuum-sealed MEMS resonators based on silicon migration sealing and hydrogen diffusion. J. Microelectromech. Syst. 2024, 33, 369–375. [Google Scholar] [CrossRef]

- Wang, Y.; Cao, R.; Li, C.; Dean, R.N. Concepts, roadmaps and challenges of ovenized MEMS gyroscopes: A review. IEEE Sens. J. 2020, 21, 92–119. [Google Scholar] [CrossRef]

- Li, M.H.; Chen, C.Y.; Li, C.S.; Chin, C.H.; Li, S.S. A monolithic CMOS-MEMS oscillator based on an ultra-low-power ovenized micromechanical resonator. J. Microelectromech. Syst. 2015, 24, 360–372. [Google Scholar] [CrossRef]

- Mahmoud, A.; Mukherjee, T.; Piazza, G. Investigating long-term stability of wide bandwidth surface acoustic waves gyroscopes using a monolithically integrated micro-oven. In Proceedings of the 2020 IEEE 33rd International Conference on Micro Electro Mechanical Systems (MEMS), Vancouver, BC, Canada, 18–22 January 2020. [Google Scholar]

- Ahn, C.H.; Hong, V.A.; Park, W.; Yang, Y.; Chen, Y.; Ng, E.J.; Huynh, J.; Challoner, A.D.; Goodson, K.E.; Kenny, T.W. On-chip ovenization of encapsulated disk resonator gyroscope (DRG). In Proceedings of the 2015 Transducers—2015 18th International Conference on Solid-State Sensors, Actuators and Microsystems (TRANSDUCERS), Anchorage, AK, USA, 21–25 June 2015. [Google Scholar]

- Lee, S.H.; Cho, J.; Lee, S.W.; Zaman, M.F.; Ayazi, F.; Najafi, K. A low-power oven-controlled vacuum package technology for high-performance MEMS. In Proceedings of the 2009 IEEE 22nd International Conference on Micro Electro Mechanical Systems, Sorrento, Italy, 25–29 January 2009. [Google Scholar]

- Lemmerhirt, D.; Srivannavit, O.; Chen, S.; Litow, T.; Mitchell, J.; Cooksey, P.C.; Sturdevant, R.; Bingham, J.; Padilla, O.; Trevino, M.N. Improved scale-factor and bias stability of ovenized inertial sensors in an environmentally-stabilized inertial measurement unit (eIMU). In Proceedings of the 2019 IEEE International Symposium on Inertial Sensors and Systems (INERTIAL), Naples, FL, USA, 1–5 April 2019. [Google Scholar]

- Yang, D.; Woo, J.K.; Lee, S.; Mitchell, J.; Challoner, A.D.; Najafi, K. A micro oven-control system for inertial sensors. J. Microelectromech. Syst. 2017, 26, 507–518. [Google Scholar] [CrossRef]

- Jha, C.M.; Hopcroft, M.A.; Chandorkar, S.A.; Salvia, J.C.; Agarwal, M.; Candler, R.N.; Melamud, R.; Bongsang, K.; Kenny, T.W. Thermal isolation of encapsulated MEMS resonators. J. Microelectromech. Syst. 2008, 17, 175–184. [Google Scholar] [CrossRef]

- Bergman, T.L.; Lavine, A.S.; Incropera, F.P.; Dewitt, D.P. Chapter 1 Introduction. In Fundamentals of Heat and Mass Transfer, 7th ed.; Wiley: Hoboken, NJ, USA, 2011; p. 8. [Google Scholar]

- Bonucci, A.; Guadagnuolo, S.; Caterino, A.; Conte, A.; Moraja, M. A new model for vacuum quality and lifetime prediction in hermetic vacuum bonded MEMS. In Proceedings of the SPIE 6884, Reliability, Packaging, Testing, and Characterization of MEMS/MOEMS VII, San Jose, CA, USA, 14 February 2008. [Google Scholar]

- Hopcroft, M.A.; Agarwal, M.; Park, K.K.; Kim, B.; Jha, C.M.; Candler, R.N.; Yama, G.; Murmann, B.; Kenny, T.W. Temperature compensation of a MEMS resonator using quality factor as a thermometer. In Proceedings of the 19th IEEE International Conference on Micro Electro Mechanical Systems, Istanbul, Turkey, 22–26 January 2006. [Google Scholar]

- Samarao, A.K.; Ayazi, F. Temperaure compensation of silicon micromechanical resonators via degenerate doping. In Proceedings of the 2009 IEEE International Electron Devices Meeting, Baltimore, MD, USA, 7–9 December 2009. [Google Scholar]

- Wasisto, H.S.; Merzsch, S.; Waag, A.; Uhde, E.; Salthammer, T.; Peiner, E. Airborne engineered nanoparticle mass sensor based on a silicon resonant cantilever. Sens. Actuat. B Chem. 2013, 180, 77–89. [Google Scholar] [CrossRef]

- Ng, E.J.; Hong, V.A.; Yang, Y.; Ahn, C.H.; Everhart, C.L.M.; Kenny, T.W. Temperature dependence of the elastic constants of doped silicon. J. Microelectromech. Syst. 2015, 24, 730–741. [Google Scholar] [CrossRef]

| Parameters | Values | Units |

|---|---|---|

| Thickness of cap wafer | 525 | μm |

| Depth of the cavity in the cap wafer | 100 | μm |

| Area of the cap | 6.64 × 106 | μm2 |

| Thickness of the resonator | 50 | μm |

| Thickness of the anchor layer | 10 | μm |

| Thickness of the SOI substrate | 380 | μm |

| Area of the SOI substrate | 1.05 × 107 | μm2 |

| Thickness of the heater | 180 | μm |

| Length of the heater | 1.12 × 104 | μm |

| Width of the heater | 150 | μm |

| Length of the isolation beam | 1300 | μm |

| Width of the isolation beam | 50 | μm |

| Area of the die attach area | 1.26 × 105 | μm2 |

| Resistivity of the heater | 0.005~0.025 | Ω·cm |

| Gas | H2 | CO | N2 | CH4 | H2O | O2 | CnHm | Ar | CO2 | Noble Gas | Total |

|---|---|---|---|---|---|---|---|---|---|---|---|

| Pressure (mTorr) | - | - | - | 2.2 × 10−1 | - | - | 9.0 × 10−3 | 5.9 | - | 1.4 × 10−2 | 6.14 |

| Concentration (%) | - | - | - | 3.58 | - | - | 0.15 | 96.04 | - | 0.23 | 100 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

He, K.; Feng, R.; Zheng, Y.; Guo, L.; Liao, Q.; Song, D.; Xiang, Y.; Li, X. A Wafer-Level Fabricated Heating–Vacuum Micro-Platform with Resonant MEMS Monolithically Integrated. Micromachines 2025, 16, 214. https://doi.org/10.3390/mi16020214

He K, Feng R, Zheng Y, Guo L, Liao Q, Song D, Xiang Y, Li X. A Wafer-Level Fabricated Heating–Vacuum Micro-Platform with Resonant MEMS Monolithically Integrated. Micromachines. 2025; 16(2):214. https://doi.org/10.3390/mi16020214

Chicago/Turabian StyleHe, Kaixuan, Rui Feng, Yu Zheng, Lijian Guo, Qichao Liao, Dongfang Song, Yuan Xiang, and Xinxin Li. 2025. "A Wafer-Level Fabricated Heating–Vacuum Micro-Platform with Resonant MEMS Monolithically Integrated" Micromachines 16, no. 2: 214. https://doi.org/10.3390/mi16020214

APA StyleHe, K., Feng, R., Zheng, Y., Guo, L., Liao, Q., Song, D., Xiang, Y., & Li, X. (2025). A Wafer-Level Fabricated Heating–Vacuum Micro-Platform with Resonant MEMS Monolithically Integrated. Micromachines, 16(2), 214. https://doi.org/10.3390/mi16020214