A 3.2–3.6 GHz GaN Doherty Power Amplifier Module Based on a Compact Low-Loss Combiner

Abstract

1. Introduction

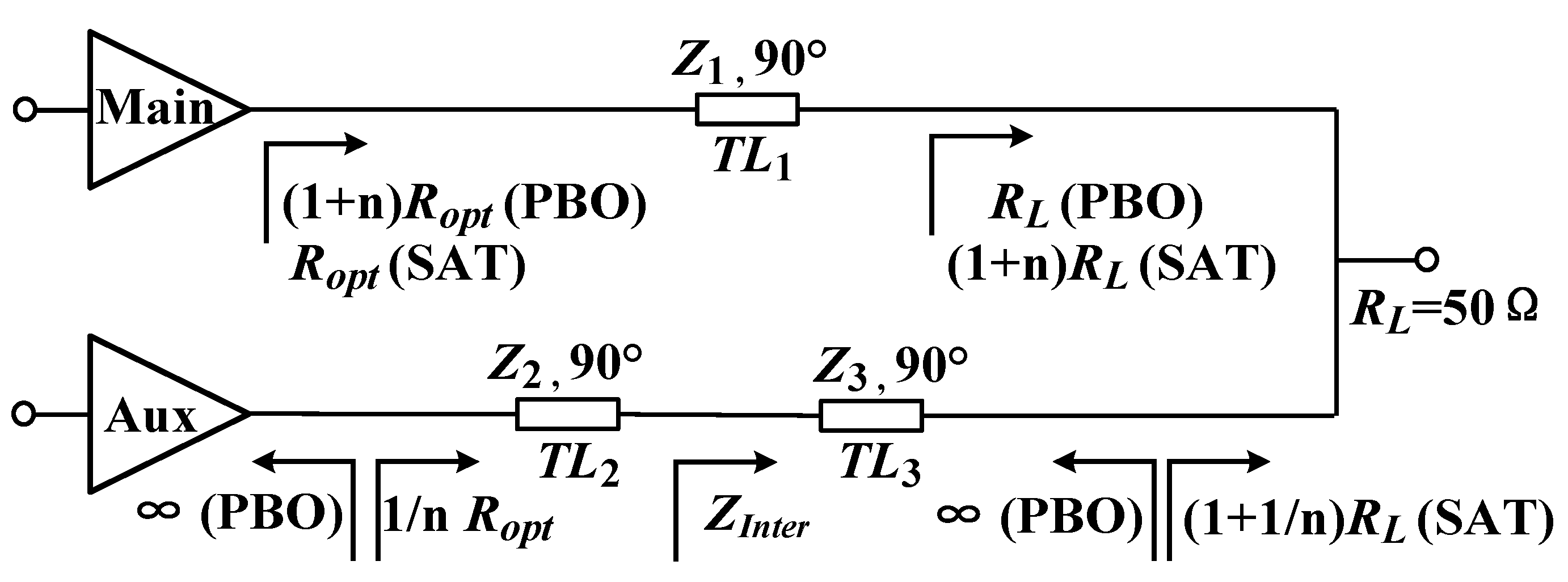

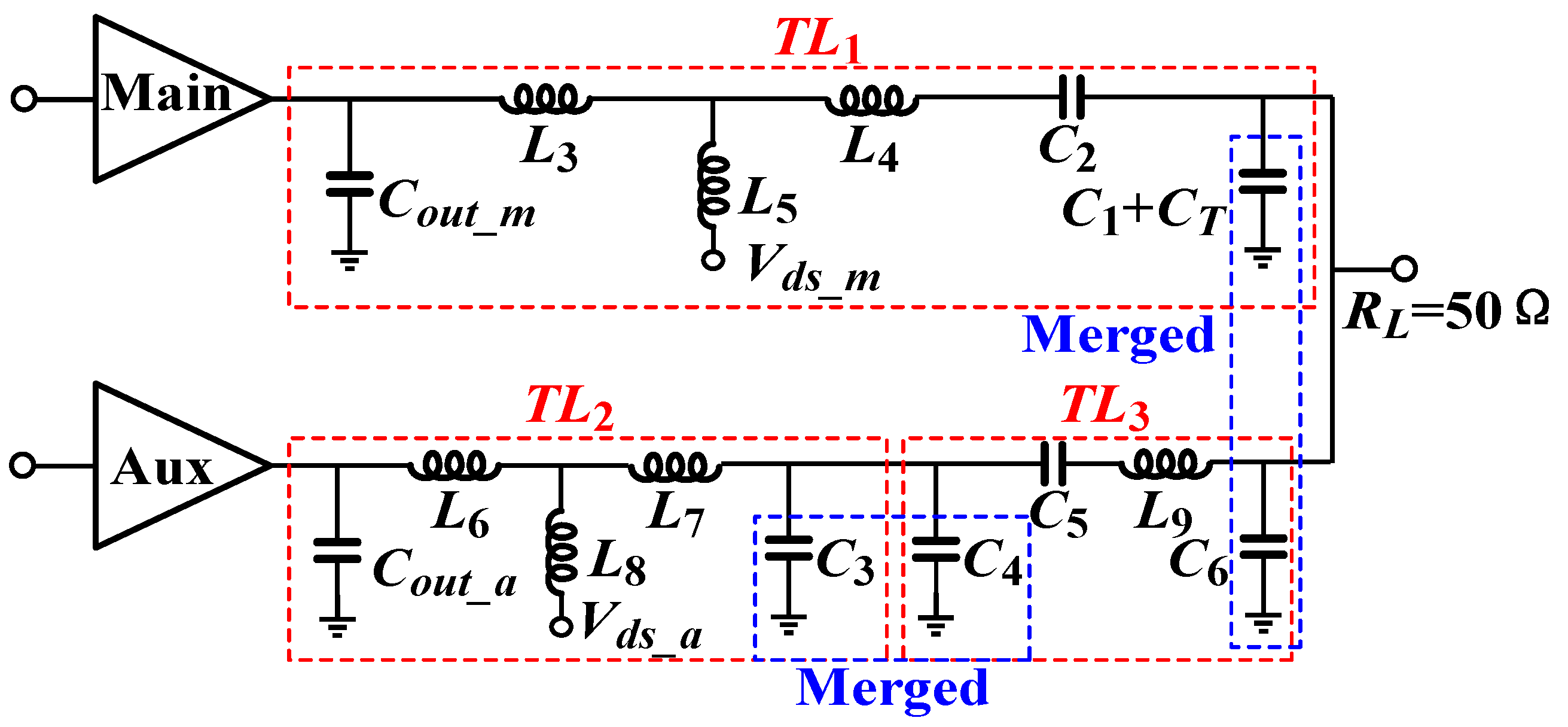

2. Circuit Analysis and Design

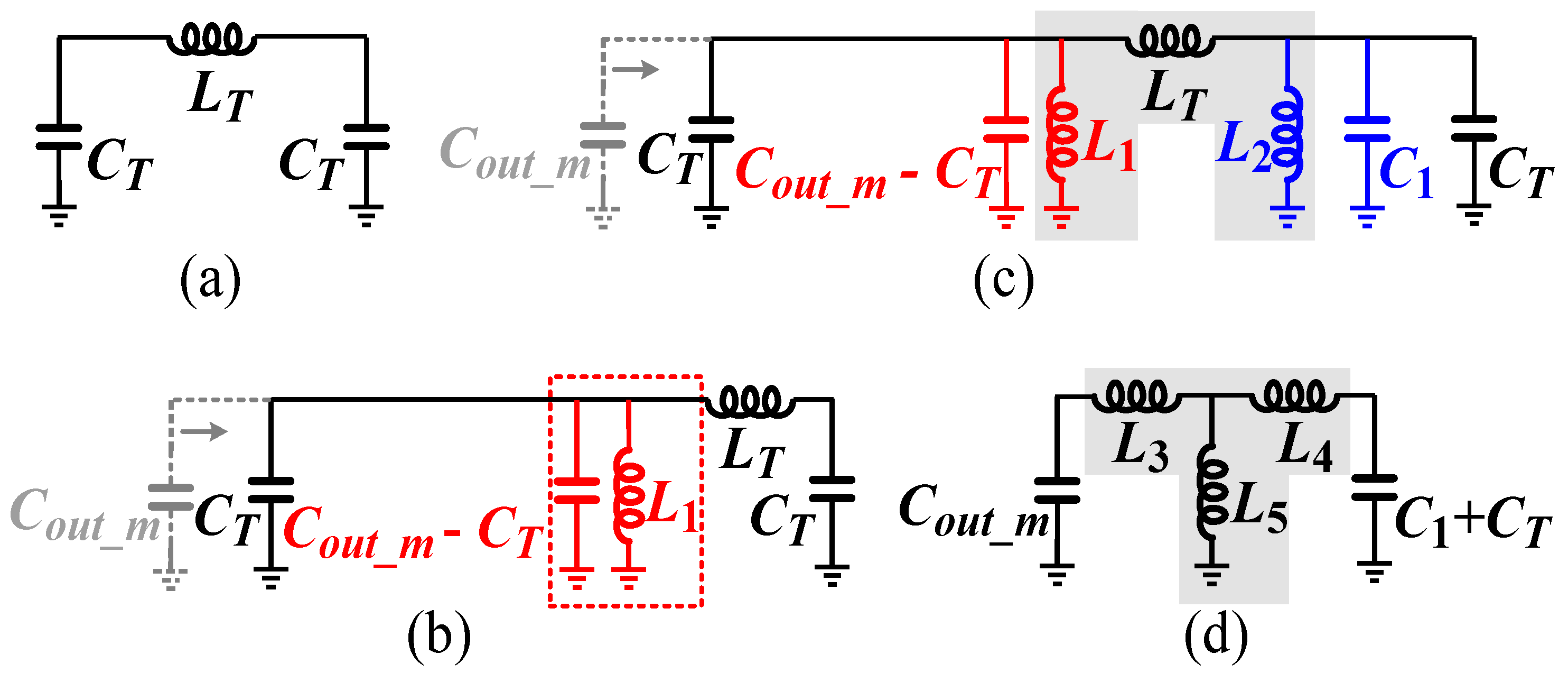

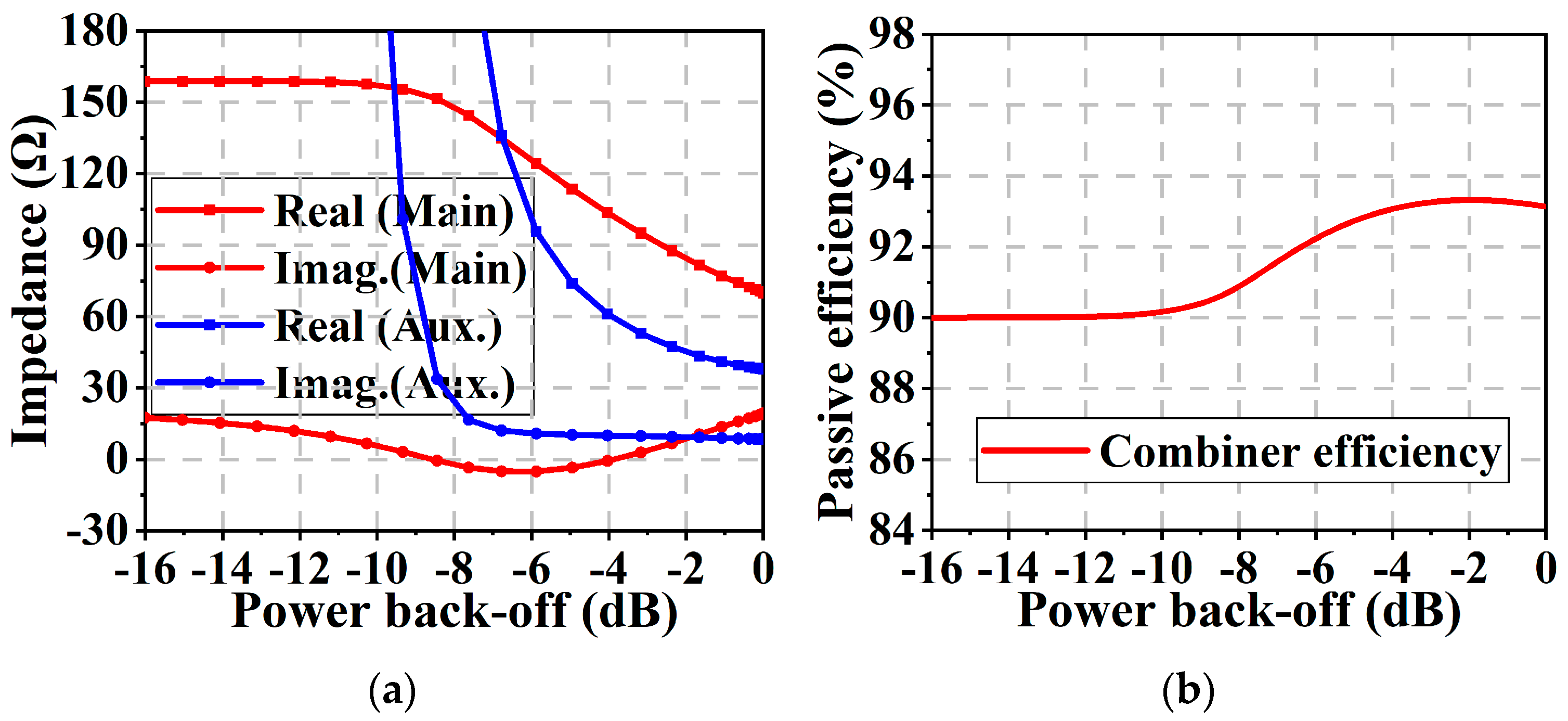

2.1. Analysis and Design of the Output Combiner

2.2. Design Procedure of the Combiner

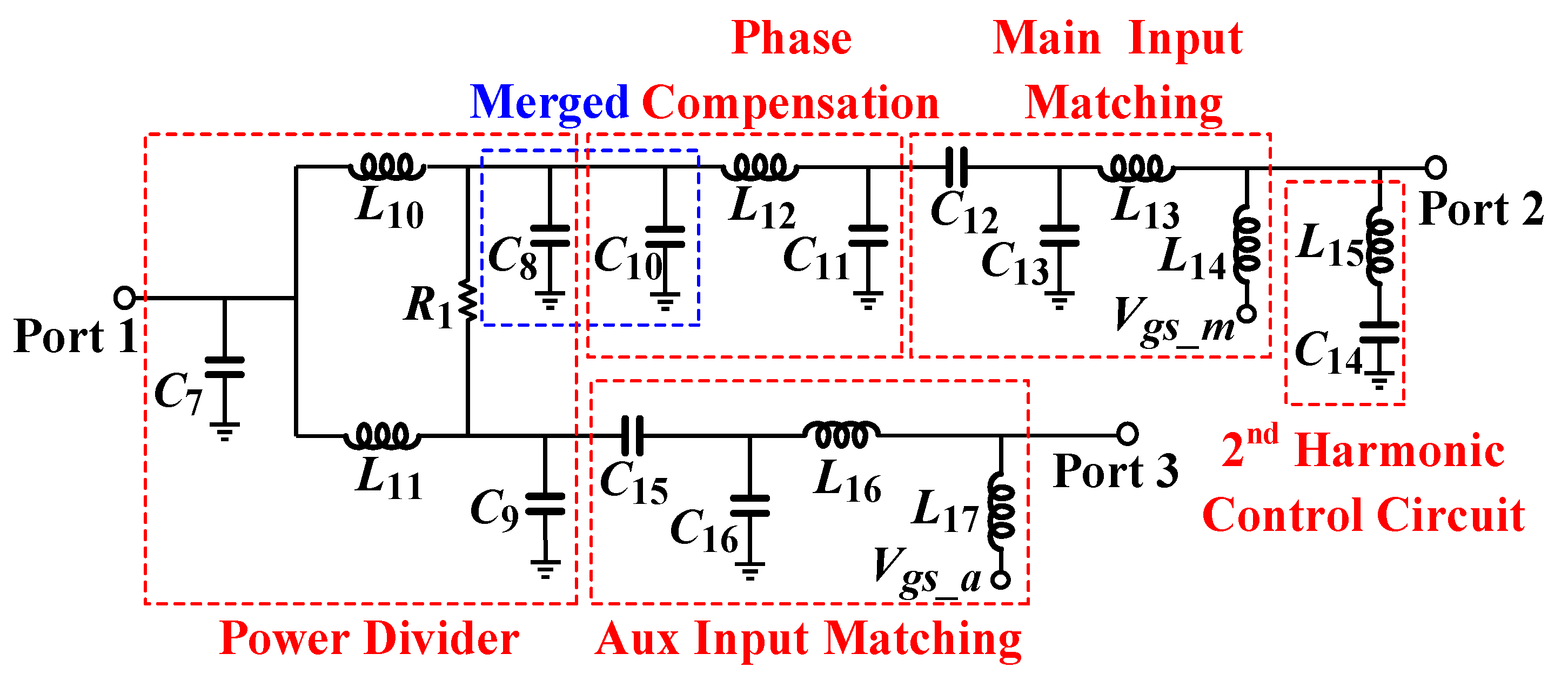

2.3. Design of Input Matching and Power Divider

3. Implementation and Measurement Results

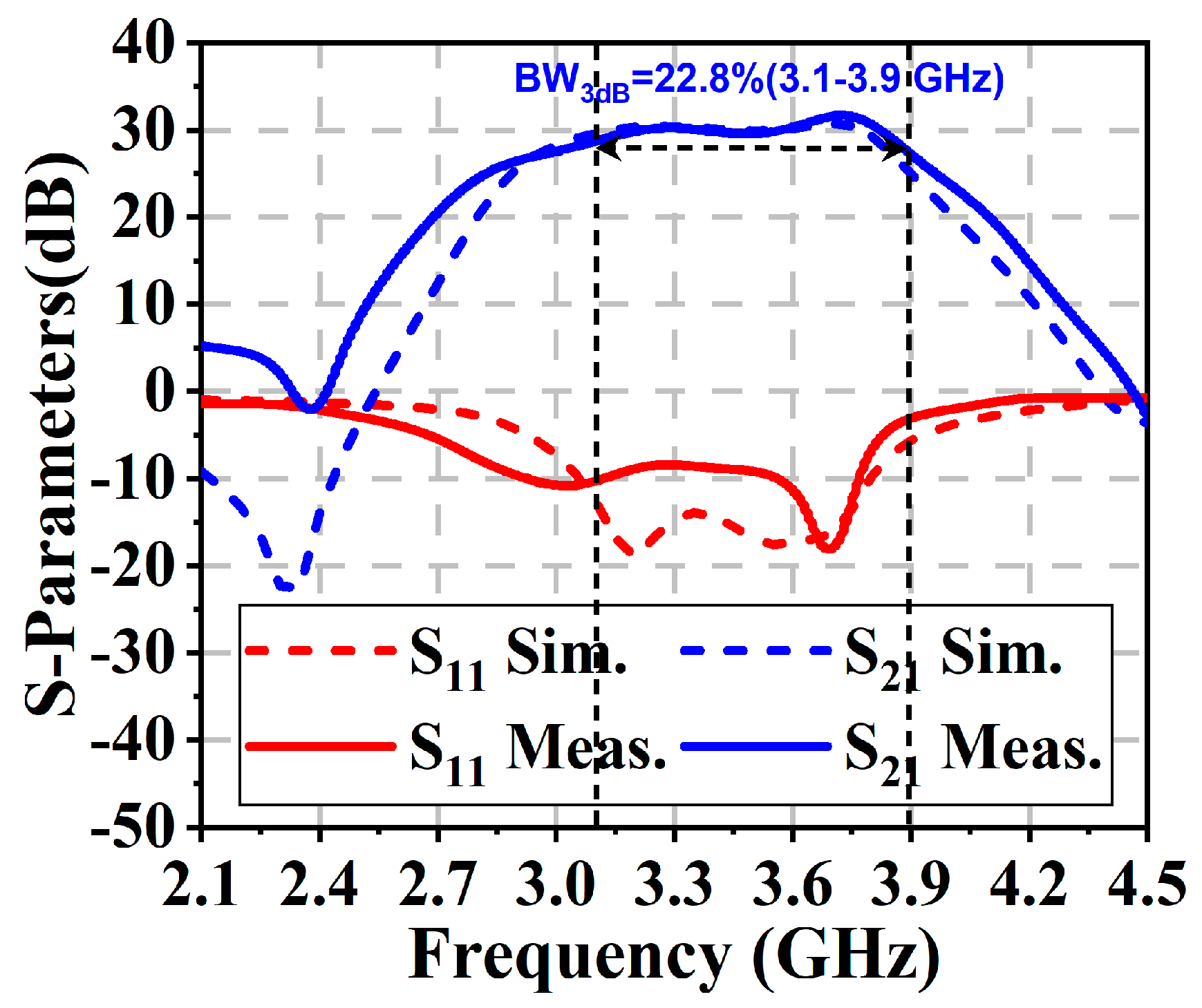

3.1. Small-Signal Measurement

3.2. Large-Signal Measurement

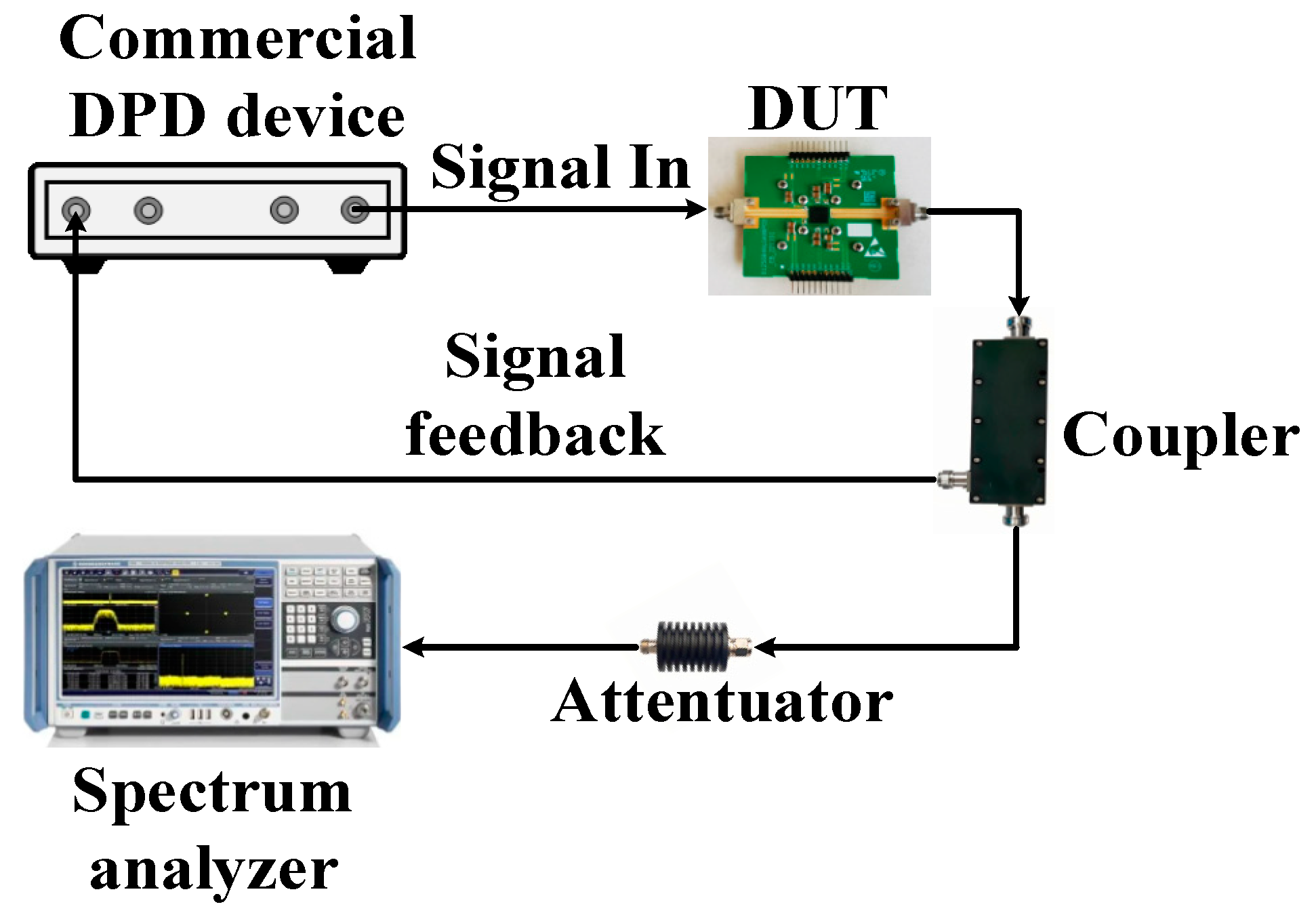

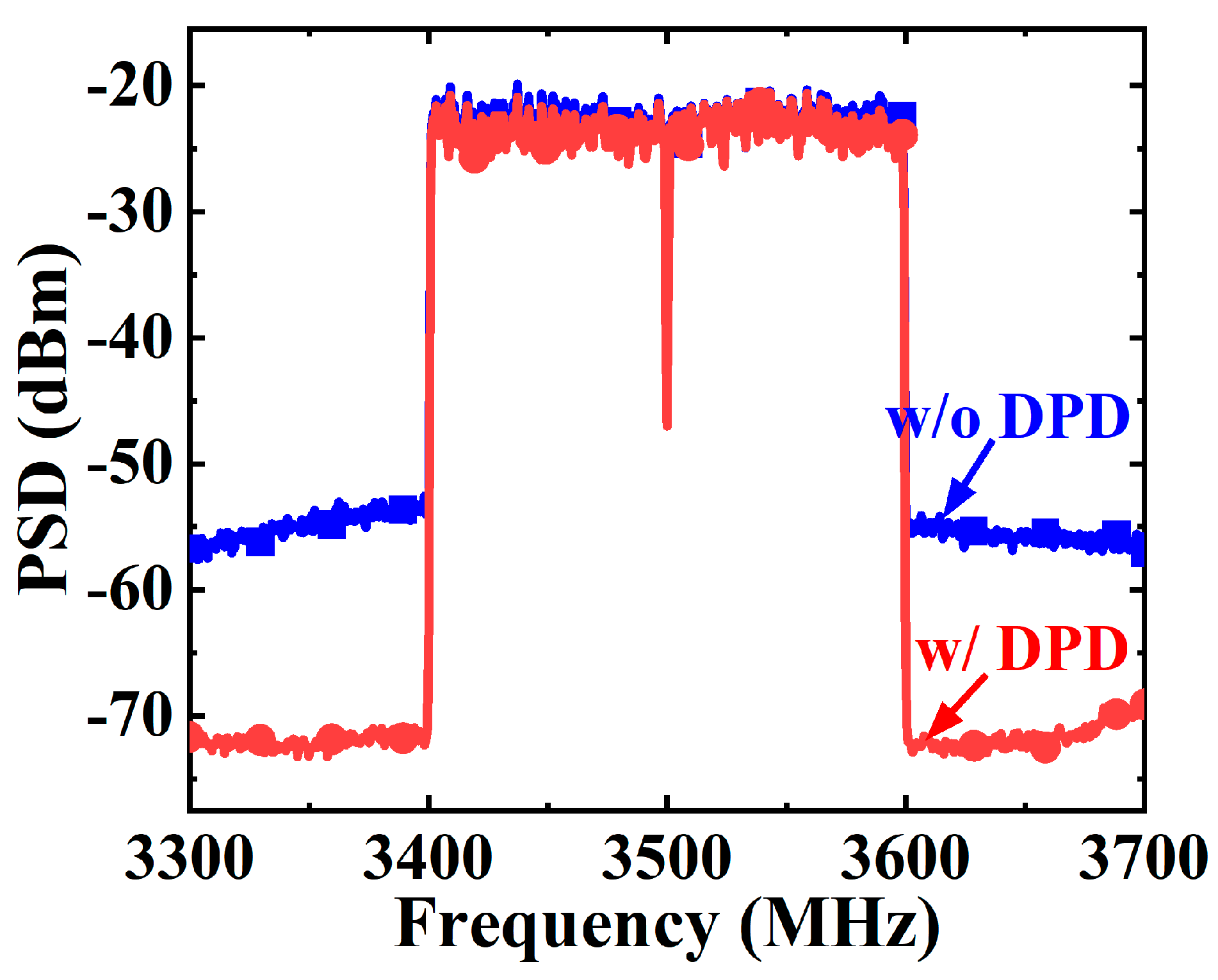

3.3. Modulated-Signal Measurement

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Doherty, W.H. A New High Efficiency Power Amplifier for Modulated Waves. Proc. IRE 1936, 24, 1163–1182. [Google Scholar] [CrossRef]

- Musolff, C.; Kamper, M.; Abou-Chahine, Z.; Fischer, G. A Linear and Efficient Doherty PA at 3.5 GHz. IEEE Microw. Mag. 2013, 14, 95–101. [Google Scholar] [CrossRef]

- Chen, W.; Lv, G.; Liu, X.; Wang, D.; Ghannouchi, F.M. Doherty PAs for 5G massive MIMO: Energy-efficient integrated DPA MMICs for sub-6-GHz and mm-wave 5G massive MIMO systems. IEEE Microw. Mag. 2020, 21, 78–93. [Google Scholar] [CrossRef]

- Sakata, S.; Kato, K.; Teranishi, E.; Sugitani, T.; Ma, R.; Chuang, K.; Wu, Y.-C.; Fukunaga, K.; Komatsuzaki, Y.; Horiguchi, K.; et al. A Fully-Integrated GaN Doherty Power Amplifier Module with a Compact Frequency-Dependent Compensation Circuit for 5G massive MIMO Base Stations. In Proceedings of the IEEE MTT-S International Microwave Symposium (IMS), Los Angeles, CA, USA, 4–6 August 2020; pp. 711–714. [Google Scholar]

- Liu, R.-J.; Zhu, X.-W.; Xia, J.; Chen, P.; Yu, C.; Zhang, L.; Chen, Z.Y. A 30-W GaN Quasi-MMIC Doherty Power Amplifier Based on All-Distributed Inductors Load Network. In Proceedings of the 51st European Microwave Conference (EuMC), London, UK, 4–6 April 2022; pp. 946–949. [Google Scholar]

- Sakata, S.; Taguchi, M.; Kato, K.; Teranishi, E.; Honda, S.; Komatsuzaki, Y.; Tsuru, M.; Yamanaka, K. A 3.4–4.1 GHz Broadband GaN Doherty Power Amplifier Module for 5G massive-MIMO Base-Stations. In Proceedings of the Asia-Pacific Microwave Conference (APMC), Yokohama, Japan, 29 November–2 December 2022; pp. 500–502. [Google Scholar]

- Giofrè, R.; Piazzon, L.; Colantonio, P.; Giannini, F. A Closed-Form Design Technique for Ultra-Wideband Doherty Power Amplifiers. IEEE Trans. Microw. Theory Tech. 2014, 62, 3414–3424. [Google Scholar] [CrossRef]

- Barakat, A.; Thian, M.; Fusco, V.; Bulja, S.; Guan, L. Toward a More Generalized Doherty Power Amplifier Design for Broadband Operation. IEEE Trans. Microw. Theory Tech. 2017, 65, 846–859. [Google Scholar] [CrossRef]

- Kuylenstierna, D.; Gunnarsson, S.E.; Zirath, H. Lumped-element quadrature power splitters using mixed right/left-handed transmission lines. IEEE Trans. Microw. Theory Tech. 2005, 53, 2616–2621. [Google Scholar] [CrossRef]

- Gustafsson, D.; Cahuana, J.C.; Kuylenstierna, D.; Angelov, I.; Rorsman, N.; Fager, C. A Wideband and Compact GaN MMIC Doherty Amplifier for Microwave Link Applications. IEEE Trans. Microw. Theory Tech. 2013, 61, 922–930. [Google Scholar] [CrossRef]

- Jee, S.; Lee, J.; Son, J.; Kim, S.; Kim, C.H.; Moon, J.; Kim, B. Asymmetric Broadband Doherty Power Amplifier Using GaN MMIC for Femto-Cell Base-Station. IEEE Trans. Microw. Theory Tech. 2015, 63, 2802–2810. [Google Scholar]

- Lv, G.; Chen, W.; Liu, X.; Feng, Z. A Dual-Band GaN MMIC Power Amplifier With Hybrid Operating Modes for 5G Application. IEEE Microw. Wireless Compon. Lett. 2019, 29, 228–230. [Google Scholar] [CrossRef]

- Seidel, A.; Wagner, J.; Ellinger, F. 3.6 GHz Asymmetric Doherty PA MMIC in 250 nm GaN for 5G Applications. In Proceedings of the German Microwave Conference (GeMiC), Cottbus, Germany, 9–11 March 2020; pp. 1–4. [Google Scholar]

- Lv, G.; Chen, W.; Chen, X.; Wan, S.; Ghannouchi, F.M.; Feng, Z. A Fully Integrated 3.5-/4.9-GHz Dual-Band GaN MMIC Doherty Power Amplifier Based on Multi-Resonant Circuits. IEEE Trans. Microw. Theory Tech. 2022, 70, 416–431. [Google Scholar] [CrossRef]

- Oh, H.; Choi, W.; Shin, J.; Chen, Y.; Kang, H.; Woo, Y.Y.; Yang, Y. A 6-/12-dB Back-off Multi-Mode GaN MMIC Doherty Power Amplifier for 5G Applications. In Proceedings of the IEEE MTT-S International Microwave Symposium (IMS), San Diego, CA, USA, 11–16 June 2023; pp. 458–461. [Google Scholar]

| Ref. | Freq.(GHz) | Gain (dB) | Psat (dBm) | DE@OPBO (%) | Stage | Area (mm2) | Type |

|---|---|---|---|---|---|---|---|

| This work | 3.2–3.6 | 29.6–30.4 | 40.4–41.1 | 45.5–48.6 @8dB OPBO | 2 | 8 × 8 | SMD Module |

| [3] | 3.4–3.8 | 26.9–28.6 | 37.7–38.5 | 42.9–47.8 * @8dB OPBO | 2 | 10 × 6 | SMD + IPD Module |

| [4] | 3.4–3.8 | 10.5–12 ** | 44.4–45.1 | 45–49 @8dB OPBO | 1 | 5.6 × 4.3 | IPD Module |

| [5] | 3.4–4.1 | 31.7 | 47.9 | 42–44.6 * @8dB OPBO | 2 | 76 | Module |

| [12] | 3.3–3.8 | 12 | 41.8–42.6 | 42–51 @6dB OPBO | 1 | 2.4 × 2.4 | MMIC |

| [13] | 3.4–3.7 | 11.7 | 38.8 | 40–46 * @8.5dB OPBO | 1 | 10 | MMIC |

| [14] | 3.35–3.6 | 12.1–12.3 | 43.8–44.7 | 41–46 @6dB OPBO | 1 | 2.8 × 3.5 | MMIC |

| [15] | 3.3–3.6 | 11 ** | 42.6–43 | 34.7–39 @6dB OPBO | 1 | 3.3 × 3.2 | MMIC |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Wang, X.; Wang, D.; Li, W.; Lv, X.; Cui, K.; Liu, H.; Kang, K. A 3.2–3.6 GHz GaN Doherty Power Amplifier Module Based on a Compact Low-Loss Combiner. Micromachines 2025, 16, 220. https://doi.org/10.3390/mi16020220

Wang X, Wang D, Li W, Lv X, Cui K, Liu H, Kang K. A 3.2–3.6 GHz GaN Doherty Power Amplifier Module Based on a Compact Low-Loss Combiner. Micromachines. 2025; 16(2):220. https://doi.org/10.3390/mi16020220

Chicago/Turabian StyleWang, Xiyu, Dehan Wang, Wenming Li, Xiaolin Lv, Kai Cui, Haijun Liu, and Kai Kang. 2025. "A 3.2–3.6 GHz GaN Doherty Power Amplifier Module Based on a Compact Low-Loss Combiner" Micromachines 16, no. 2: 220. https://doi.org/10.3390/mi16020220

APA StyleWang, X., Wang, D., Li, W., Lv, X., Cui, K., Liu, H., & Kang, K. (2025). A 3.2–3.6 GHz GaN Doherty Power Amplifier Module Based on a Compact Low-Loss Combiner. Micromachines, 16(2), 220. https://doi.org/10.3390/mi16020220