A Stepped Gate Oxide Structure for Suppressing Gate-Induced Drain Leakage in Fully Depleted Germanium-on-Insulator Multi-Subchannel Tunneling Field-Effect Transistors

Abstract

:1. Introduction

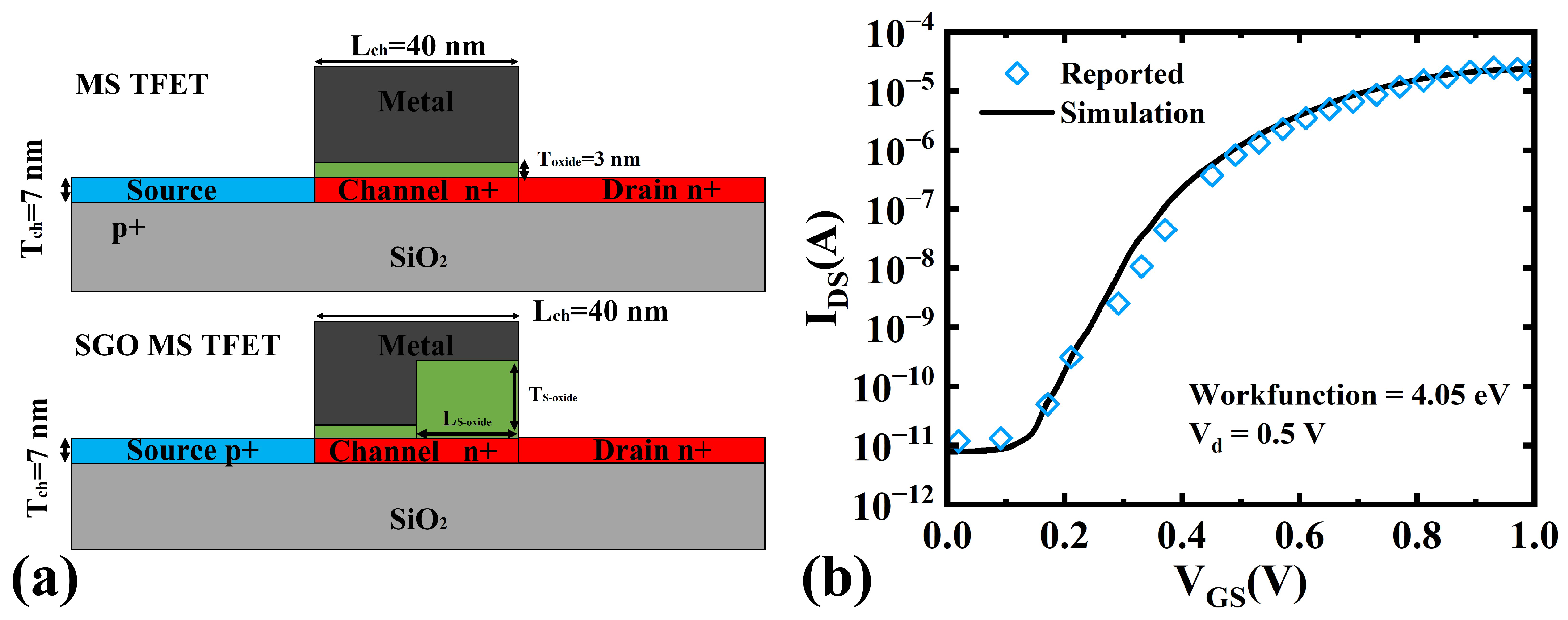

2. Device Structure and Simulation Method

2.1. Device Structure

2.2. Simulation Methodology

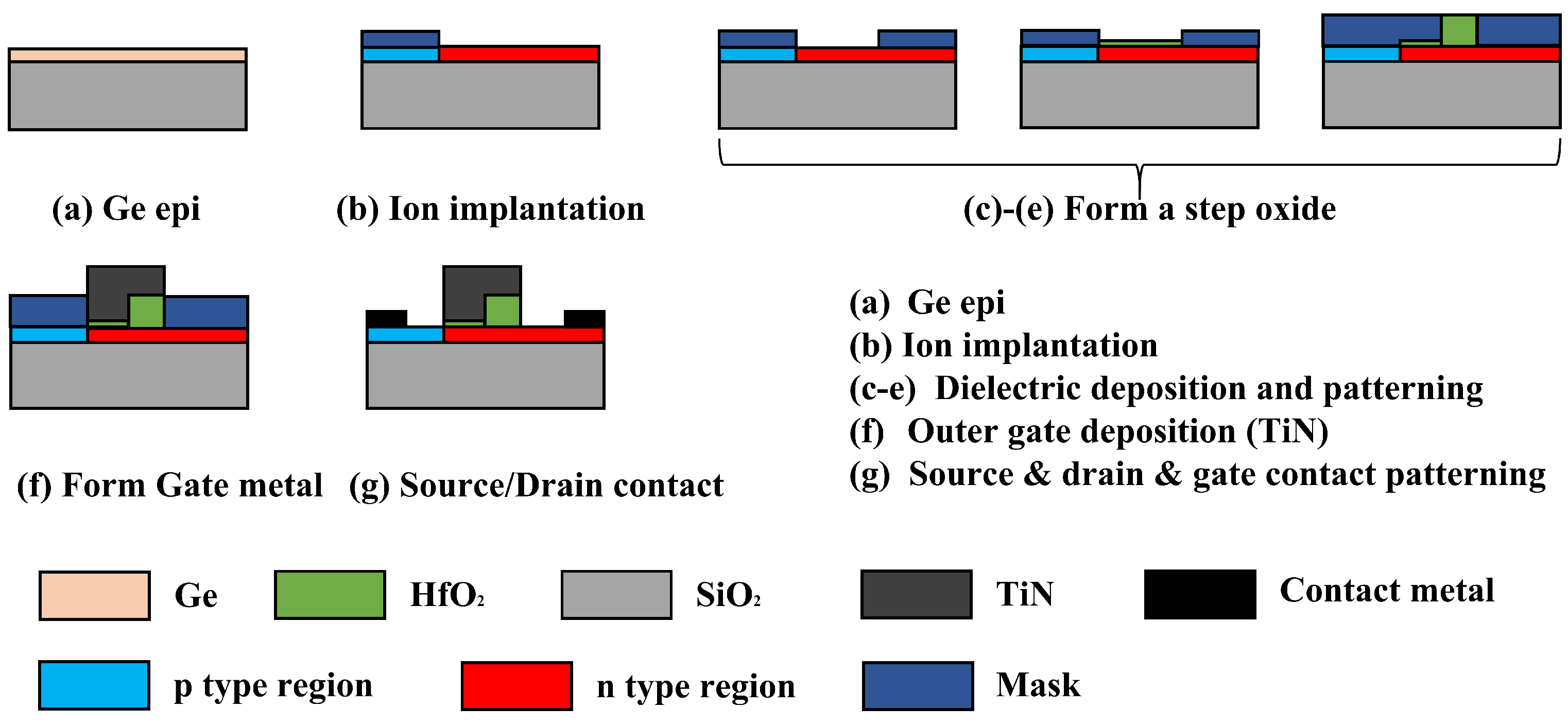

2.3. Suggested Process Flow

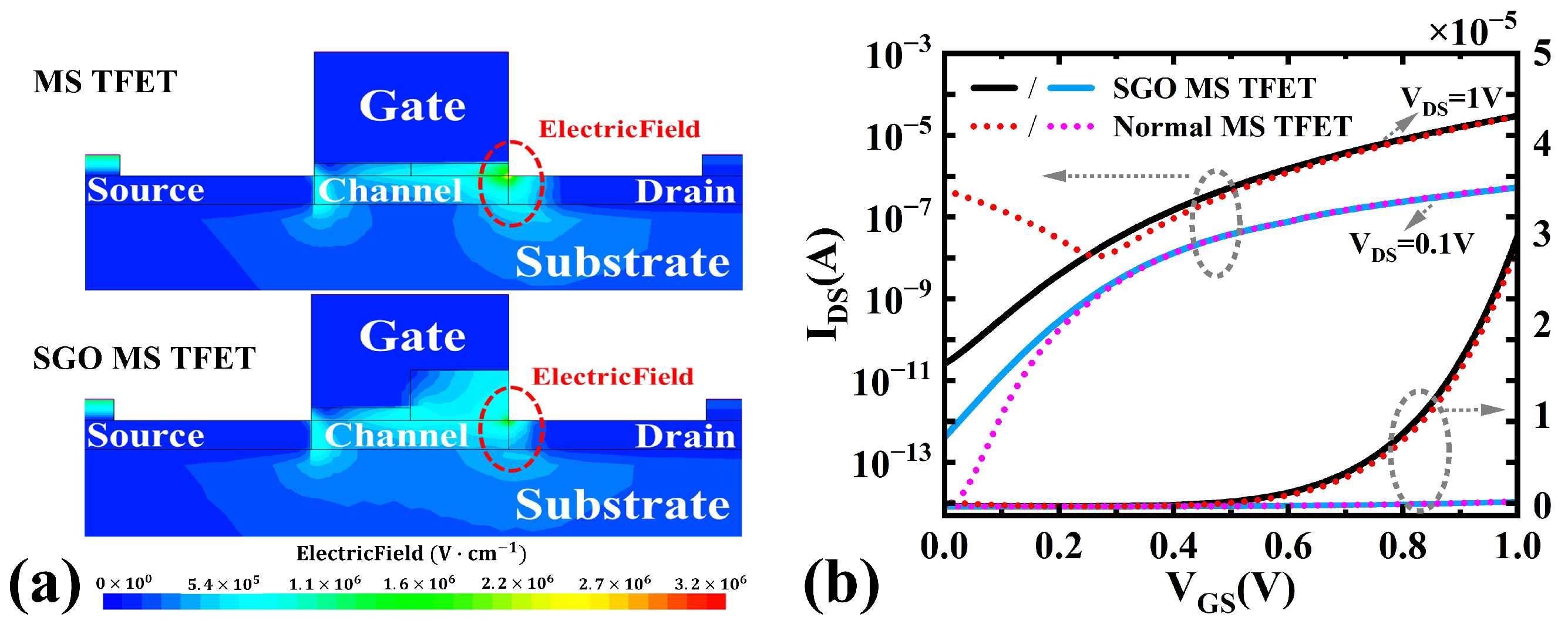

3. Results and Discussion

3.1. Off-State Current Reduction

3.2. Analysis of SGO Structural Parameters

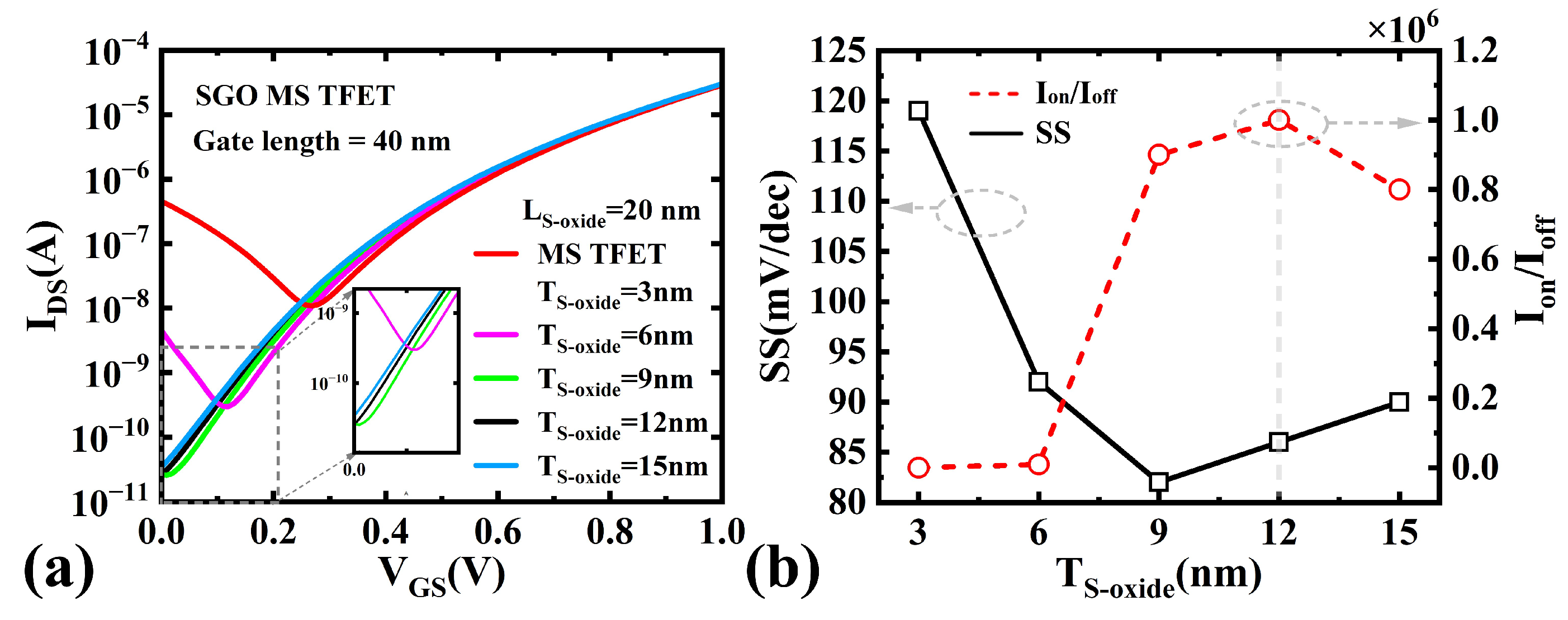

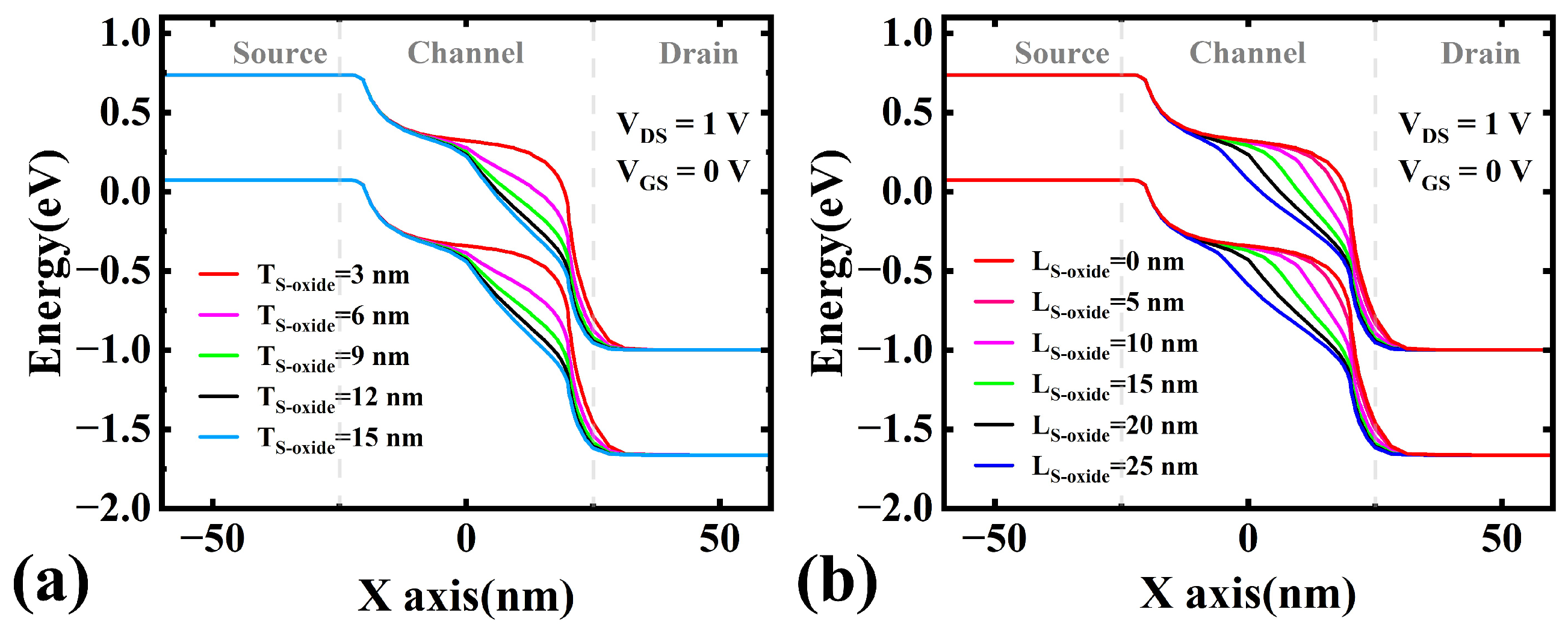

3.2.1. Effect of Suppression Oxide Thickness

3.2.2. Effect of Suppression Oxide Length

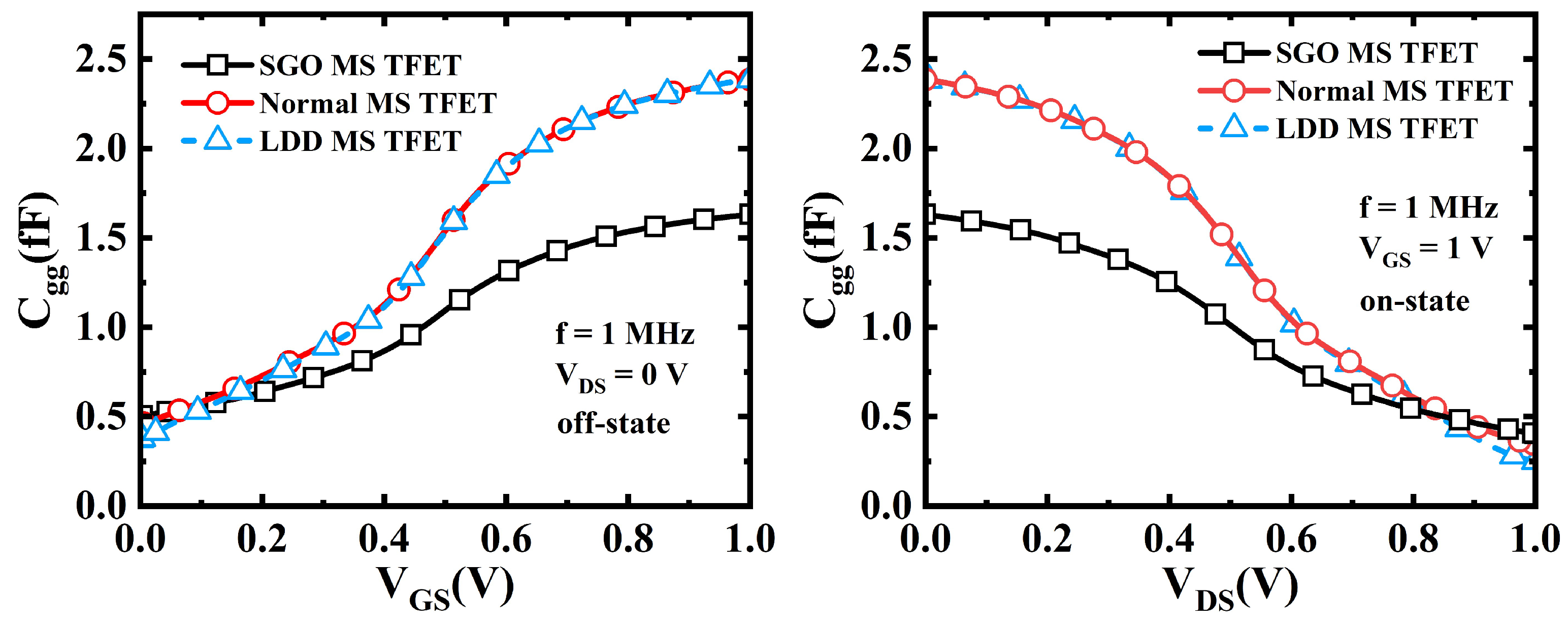

3.3. Capacitance and Mobility Analysis

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

Abbreviations

| FD-SOI | Fully depleted Silicon-on-Insulator |

| FD-GeOI | Fully depleted Germanium-on-Insulator |

| GIDL | Gate-induced drain leakage |

| SGO | Stepped gate oxide |

| MS TFET | Multi-subchannel Tunneling field effect transistor |

| LDD | Lightly doped drain |

| FP | Field plate |

| On-state current | |

| Off-state current | |

| / | The on-state to off-state current ratio |

| SS | Subthreshold swing |

| BTBT | Band-to-band tunneling |

| BGN | Bandgap narrowing |

| SRH | Shockley–Read–Hall |

| RTA | Rapid thermal annealing |

| ALD | Atomic layer deposition |

| SADP | Self-aligned double patterning |

| SPA | Spike annealing |

| BARC | Bottom anti-reflective coating |

| P | Phosphorus |

| As | Arsenic |

| Cgg | Total gate capacitance |

References

- Shih, P.-C.; Hou, W.-C.; Li, J.-Y. A U-Gate InGaAs/GaAsSb Heterojunction TFET of Tunneling Normal to the Gate With Separate Control Over ON- and OFF-State Current. IEEE Electron Device Lett. 2017, 38, 1751–1754. [Google Scholar] [CrossRef]

- Kato, K.; Tanamoto, T.; Mori, T.; Morita, Y.; Matsukawa, T.; Takenaka, M.; Takagi, S. Impact of Switching Voltage on Complementary Steep-Slope Tunnel Field Effect Transistor Circuits. IEEE Trans. Electron Devices 2020, 67, 3876–3882. [Google Scholar] [CrossRef]

- Musalgaonkar, G.; Sahay, S.; Saxena, R.S.; Kumar, M.J. Nanotube Tunneling FET With a Core Source for Ultrasteep Subthreshold Swing: A Simulation Study. IEEE Trans. Electron Devices 2019, 66, 4425–4432. [Google Scholar]

- Kim, G.; Lee, J.; Kim, J.H.; Kim, S. High On-Current Ge-Channel Heterojunction Tunnel Field-Effect Transistor Using Direct Band-to-Band Tunneling. Micromachines 2019, 10, 77. [Google Scholar] [CrossRef]

- Liu, X.-Y.; Hu, H.-Y.; Wang, B.; Wang, M.; Han, G.-Q.; Cui, S.-M.; Zhang, H.-M. Study of novel junctionless Ge n-Tunneling Field-Effect Transistors with lightly doped drain (LDD) region. Superlattices Microstruct. 2017, 102, 7–16. [Google Scholar] [CrossRef]

- Wang, B.; Hu, S.; Feng, Y.; Li, P.; Hu, H.Y.; Shu, B. Simulation study of device physics and design of GeOI TFET with PNN structure and buried layer for high performance. Chin. Phys. B 2020, 29, 107401. [Google Scholar] [CrossRef]

- Chen, W.; Cheng, J.; Huang, H.; Zhang, B.; Chen, X.B. The Oppositely Doped Islands IGBT Achieving Ultralow Turn Off Loss. IEEE Trans. Electron Devices 2019, 66, 3690–3693. [Google Scholar] [CrossRef]

- Choi, K.M.; Lee, W.S.; Lee, K.H.; Park, Y.K.; Choi, W.Y. Influence of Preferred Gate Metal Grain Orientation on Tunneling FETs. IEEE Trans. Electron Devices 2015, 62, 1353–1356. [Google Scholar] [CrossRef]

- Kim, S.W.; Kim, J.H.; Liu, T.J.K.; Choi, W.Y.; Park, B.G. Demonstration of L-Shaped Tunnel Field-Effect Transistors. IEEE Trans. Electron Devices 2016, 63, 1774–1778. [Google Scholar] [CrossRef]

- Revelant, A.; Villalon, A.; Wu, Y.; Zaslavsky, A.; Le Royer, C.; Iwai, H.; Cristoloveanu, S. Electron-Hole Bilayer TFET: Experiments and Comments. IEEE Trans. Electron Devices 2014, 61, 2674–2681. [Google Scholar] [CrossRef]

- Chang, H.; Liu, Q.; Yang, H.; Zhou, L.; Ji, Z.; Tang, B.; Zhang, Q.; Yin, H.; Du, A.; Li, J.; et al. Effectiveness of Repairing Hot Carrier Degradation in Si p-FinFETs Using Gate Induced Drain Leakage. IEEE Electron Device Lett. 2023, 44, 372–375. [Google Scholar]

- Wan, J.; Le Royer, C.; Zaslavsky, A.; Cristoloveanu, S. Gate-induced drain leakage in FD-SOI devices: What the TFET teaches us about the MOSFET. Microelectron. Eng. 2011, 88, 1301–1304. [Google Scholar]

- Mitra, S.K.; Goswami, R.; Bhowmick, B. A hetero-dielectric stack gate SOI-TFET with back gate and its application as a digital inverter. Superlattices Microstruct. 2016, 92, 37–51. [Google Scholar]

- Wang, B.; Zhang, H.-M.; Hu, H.-Y.; Shi, X.-W. Enhancement of off-state characteristics in junctionless field effect transistor using a field plate. Chin. Phys. B 2018, 27, 067402. [Google Scholar]

- Wang, X.; Tang, Z.; Cao, L.; Li, J.; Liu, Y. Gate Field Plate Structure for Subthreshold Swing Improvement of Si Line-Tunneling FETs. IEEE Access 2019, 7, 100675–100683. [Google Scholar]

- Li, C.; Zhao, X.; Zhuang, Y.; Yan, Z.; Guo, J.; Han, R. Optimization of L-shaped tunneling field-effect transistor for ambipolar current suppression and Analog/RF performance enhancement. Superlattices Microstruct. 2018, 115, 154–167. [Google Scholar]

- Zhu, G.; Zhang, M.; Lu, L.; Wong, M.; Kwok, H.-S. Hot Carrier Degradation Reduction in Metal Oxide Thin-Film Transistors by Implementing a Lightly Doped Drain-Like Structure. IEEE Electron Device Lett. 2024, 45, 1602–1605. [Google Scholar] [CrossRef]

- Teng, Q.; Wu, Y.; Xu, K.; Gao, D. Hot Carrier Degradation-Induced Variability in Different Lightly Doped Drain Processes: From Transistors to SRAM Cells. IEEE Trans. Electron Devices 2024, 71, 6527–6533. [Google Scholar]

- Tiwari, V.A.; Teh, Y.W.; Jaeger, D.; Divakaruni, R.; Nair, D.R. Effect of Germanium Preamorphization Implant on Performance and Gate-Induced Drain Leakage in SiGe Channel pFET. IEEE Electron Device Lett. 2015, 36, 531–533. [Google Scholar]

- Dabhi, C.K.; Roy, A.S.; Chauhan, Y.S. Compact Modeling of Temperature-Dependent Gate-Induced Drain Leakage Including Low-Field Effects. IEEE Trans. Electron Devices 2019, 66, 2892–2897. [Google Scholar] [CrossRef]

- Synopsys. Advanced Calibration for Device Simulation User Guide. Available online: https://picture.iczhiku.com/resource/eetop/sYKTQPSOlSOZAvNb.pdf (accessed on 15 June 2024).

- Li, W.; Liu, H.-X.; Wang, S.-L.; Chen, S.-P.; Yang, Z.-N. Design of High Performance Si/SiGe Heterojunction Tunneling FETs with a T-Shaped Gate. Nanoscale Res. Lett. 2017, 12, 198. [Google Scholar] [CrossRef]

- Beneventi, G.B.; Gnani, E.; Gnudi, A.; Reggiani, S.; Baccarani, G. Optimization of a Pocketed Dual-Metal-Gate TFET by Means of TCAD Simulations Accounting for Quantization-Induced Bandgap Widening. IEEE Trans. Electron Devices 2015, 62, 44–51. [Google Scholar]

- Liu, W.; Bi, S.; Song, J. Novel Ge-Based Plasma TFET with High Rectification Efficiency for 2.45 GHz Microwave Wireless Weak Energy Transmission. Micromachines 2024, 15, 117. [Google Scholar] [CrossRef]

- Chen, Z.-X.; Liu, W.-J.; Liu, J.-N.; Wang, Q.-H.; Zhang, X.-G.; Xu, J.; Li, Q.-H.; Bai, W.; Tang, X.-D. DC and analog/RF performance of C-shaped pocket TFET (CSP-TFET) with fully overlapping gate. Chin. Phys. B 2022, 31, 058501. [Google Scholar] [CrossRef]

- Manikanta, K.; Nanda, U.; Pandey, C.K. Physics based model development of a double gate reverse T-shaped channel TFET including 1D and 2D band-to-band tunneling components. Microelectron. J. 2024, 144, 106100. [Google Scholar] [CrossRef]

- Damrongplasit, N.; Kim, S.-H.; Liu, T.-J.K. Study of Random Dopant Fluctuation Induced Variability in the Raised-Ge-Source TFET. IEEE Electron Device Lett. 2013, 34, 184–186. [Google Scholar] [CrossRef]

- Biswas, A.; Dan, S.S.; Le Royer, C.; Grabinski, W.; Ionescu, A.M. TCAD simulation of SOI TFETs and calibration of non-local band-to-band tunneling model. Microelectron. Eng. 2012, 98, 334–337. [Google Scholar] [CrossRef]

- Hellings, G.; Eneman, G.; Krom, R.; De Jaeger, B.; Mitard, J.; De Keersgieter, A.; Hoffmann, T.; Meuris, M.; De Meyer, K. Electrical TCAD Simulations of a Germanium pMOSFET Technology. IEEE Trans. Electron Devices 2010, 57, 04FD05. [Google Scholar] [CrossRef]

- Yang, Z.-N. Tunnel Field-Effect Transistor With an L-Shaped Gate. IEEE Electron Device Lett. 2016, 37, 839–842. [Google Scholar] [CrossRef]

- Singh, A.K.; Tripathy, M.R.; Baral, K.; Singh, P.K.; Jit, S. Investigation of DC, RF and linearity performances of a back-gated (BG) heterojunction (HJ) TFET-on-selbox-substrate (STFET): Introduction to a BG-HJ-STEFT based CMOS inverter. Microelectron. J. 2020, 104775. [Google Scholar] [CrossRef]

- Kao, K.-H.; Verhulst, A.S.; Vandenberghe, W.G.; Sorée, B.; Groeseneken, G.; De Meyer, K. Direct and Indirect Band-to-Band Tunneling in Germanium-Based TFETs. IEEE Trans. Electron Devices 2012, 59, 292–301. [Google Scholar]

- Ding, X.; Zhang, H.; Wang, X.; Zhou, X.; Lee, C.; Zhao, Y. 8F2 Ternary Content Addressable Memory Array Utilizing Interface Passivated Ge Memory-Diodes With 2 × 105 Self-Rectifying Ratio. IEEE Electron Device Lett. 2024, 45, 833–836. [Google Scholar]

- Jhan, Y.-R.; Wu, Y.-C.; Wang, Y.-L.; Lee, Y.-J.; Hung, M.-F.; Lin, H.-Y.; Chen, Y.-H.; Yeh, M.-S. Low-Temperature Microwave Annealing for Tunnel Field-Effect Transistor. IEEE Electron Device Lett. 2015, 36, 105–107. [Google Scholar]

- Liao, J.; Zeng, B.; Sun, Q.; Chen, Q.; Liao, M.; Qiu, C.; Zhang, Z.; Zhou, Y. Grain Size Engineering of Ferroelectric Zr-doped HfO2 for the Highly Scaled Devices Applications. IEEE Electron Device Lett. 2019, 40, 1868–1871. [Google Scholar]

- Raley, A.; Lee, J.; Smith, J.T.; Sun, X.; Farrell, R.A.; Shearer, J.; Xu, Y.; Ko, A.; Metz, A.W.; Biolsi, P.; et al. Self-aligned blocking integration demonstration for critical sub-30-nm pitch Mx level patterning with EUV self-aligned double patterning. J. Micro/Nanolithogr. MEMS MOEMS 2019, 18, 011002. [Google Scholar]

- Lee, G.; Yang, J.; Yeom, M.J.; Yoon, S.; Yoo, G. Effects of a Spike-Annealed HfO2 Gate Dielectric Layer on the On-Resistance and Interface Quality of AlGaN/GaN High-Electron-Mobility Transistors. Electronics 2024, 13, 2783. [Google Scholar] [CrossRef]

- Lee, R.; Lee, J.; Lee, K.; Kim, S.; Ahn, H.; Kim, S.; Kim, H.-M.; Kim, C.; Lee, J.-H.; Kim, S.; et al. Vertically-Stacked Si0.2Ge0.8 Nanosheet Tunnel FET With 70 mV/Dec Average Subthreshold Swing. IEEE Electron Device Lett. 2021, 42, 962–965. [Google Scholar]

- Pan, J.; Canaperi, D.; Jammy, R.; Steen, M.; Pellerin, J.; Lin, M.R. CVD rhenium and PVD tantalum gate MOSFETs fabricated with a replacement technique. IEEE Electron Device Lett. 2004, 25, 775–777. [Google Scholar]

- Zhao, Y.; Wu, C.; Huang, Q.; Chen, C.; Zhu, J.; Guo, L.; Jia, R.; Lv, Z.; Yang, Y.; Li, M.; et al. A Novel Tunnel FET Design Through Adaptive Bandgap Engineering With Constant Sub-Threshold Slope Over 5 Decades of Current and High ION/IOFF Ratio. IEEE Electron Device Lett. 2017, 38, 540–543. [Google Scholar]

- Nakashima, A.; Kimura, M. Mechanism Analysis of Off-Leakage Current in an LDD Poly-Si TFT Using Activation Energy. IEEE Electron Device Lett. 2011, 32, 764–766. [Google Scholar]

- Han, T.; Liu, H.; Chen, S.; Wang, S.; Li, W. Design and Investigation of the High Performance Doping-Less TFET with Ge/Si0.6Ge0.4/Si Heterojunction. Micromachines 2019, 10, 424. [Google Scholar] [CrossRef]

- Wang, D.; Liu, H.; Zhang, H.; Cai, M.; Lin, J. Modeling and Simulation Investigation of Ferroelectric-Based Electrostatic Doping for Tunnelling Field-Effect Transistor. Micromachines 2023, 14, 672. [Google Scholar] [CrossRef]

- Wang, Y.; Li, C.; Li, O.; Cheng, S.; Liu, W.; You, H. Simulation Study of Dual Metal-Gate Inverted T-Shaped TFET for Label-Free Biosensing. IEEE Sens. J. 2022, 22, 18266–18272. [Google Scholar]

- Xie, H.-W.; Liu, H.-X. Design and investigation of a dual source and U-shaped gate TFET with n buffer and SiGe pocket. AIP Adv. 2020, 10, 055125. [Google Scholar]

- Rasheed, G.; Sridevi, S. Design of 7T SRAM Using InGaAs-Dual Pocket-Dual Gate-Tunnel FET for IoT Applications. IEEE Access 2023, 11, 76034–76045. [Google Scholar]

| Parameter | Normal MS TFET | SGO MS TFET |

|---|---|---|

| Gate length () | 40 nm | 40 nm |

| Suppression oxide thickness () | - | 3–15 nm |

| Suppression oxide length () | - | 0–25 nm |

| Gate work function | 4.5 eV | 4.5 eV |

| Source doping | 1 × /cm3 | 1 × /cm3 |

| Drain/channel doping | 1 × /cm3 | 1 × /cm3 |

| Device layer thickness () | 7 nm | 7 nm |

| Control oxide thickness () | 3 nm | 3 nm |

| Parameter | Normal MS TFET | SGO TFET | Improvement |

|---|---|---|---|

| (A) | 4.6 × | 2.6 × | Reduced by 4.25 orders of magnitude |

| (A) | 2.9 × | 3.0 × | No significant loss |

| / Ratio | 0.6 × | 1 × | Increased by 4.22 orders of magnitude |

| SS (mV/dec) | 119 | 86 | Reduced by 28% |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Chen, R.; Wang, L.; Han, R.; Liao, K.; Shi, X.; Zhang, P.; Hu, H. A Stepped Gate Oxide Structure for Suppressing Gate-Induced Drain Leakage in Fully Depleted Germanium-on-Insulator Multi-Subchannel Tunneling Field-Effect Transistors. Micromachines 2025, 16, 375. https://doi.org/10.3390/mi16040375

Chen R, Wang L, Han R, Liao K, Shi X, Zhang P, Hu H. A Stepped Gate Oxide Structure for Suppressing Gate-Induced Drain Leakage in Fully Depleted Germanium-on-Insulator Multi-Subchannel Tunneling Field-Effect Transistors. Micromachines. 2025; 16(4):375. https://doi.org/10.3390/mi16040375

Chicago/Turabian StyleChen, Rui, Liming Wang, Ruizhe Han, Keqin Liao, Xinlong Shi, Peijian Zhang, and Huiyong Hu. 2025. "A Stepped Gate Oxide Structure for Suppressing Gate-Induced Drain Leakage in Fully Depleted Germanium-on-Insulator Multi-Subchannel Tunneling Field-Effect Transistors" Micromachines 16, no. 4: 375. https://doi.org/10.3390/mi16040375

APA StyleChen, R., Wang, L., Han, R., Liao, K., Shi, X., Zhang, P., & Hu, H. (2025). A Stepped Gate Oxide Structure for Suppressing Gate-Induced Drain Leakage in Fully Depleted Germanium-on-Insulator Multi-Subchannel Tunneling Field-Effect Transistors. Micromachines, 16(4), 375. https://doi.org/10.3390/mi16040375