3D Integrated Circuit Cooling with Microfluidics

Abstract

:1. Introduction

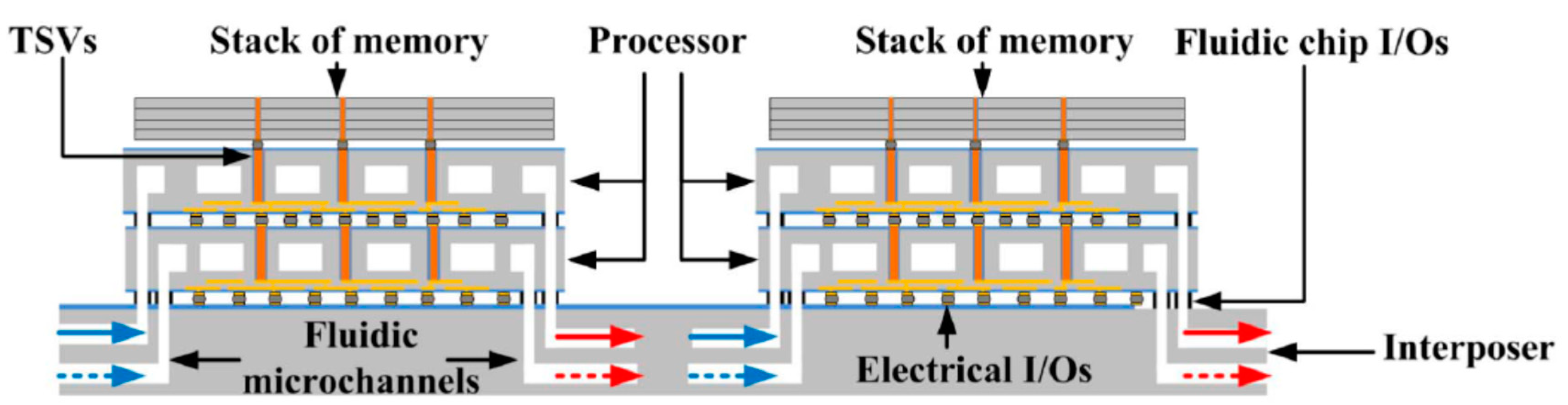

2. Microfluidic Cooling Structure and Manufacture

3. Co-Design of Microfluidic Cooling in 3D Integrated Circuits (ICs)

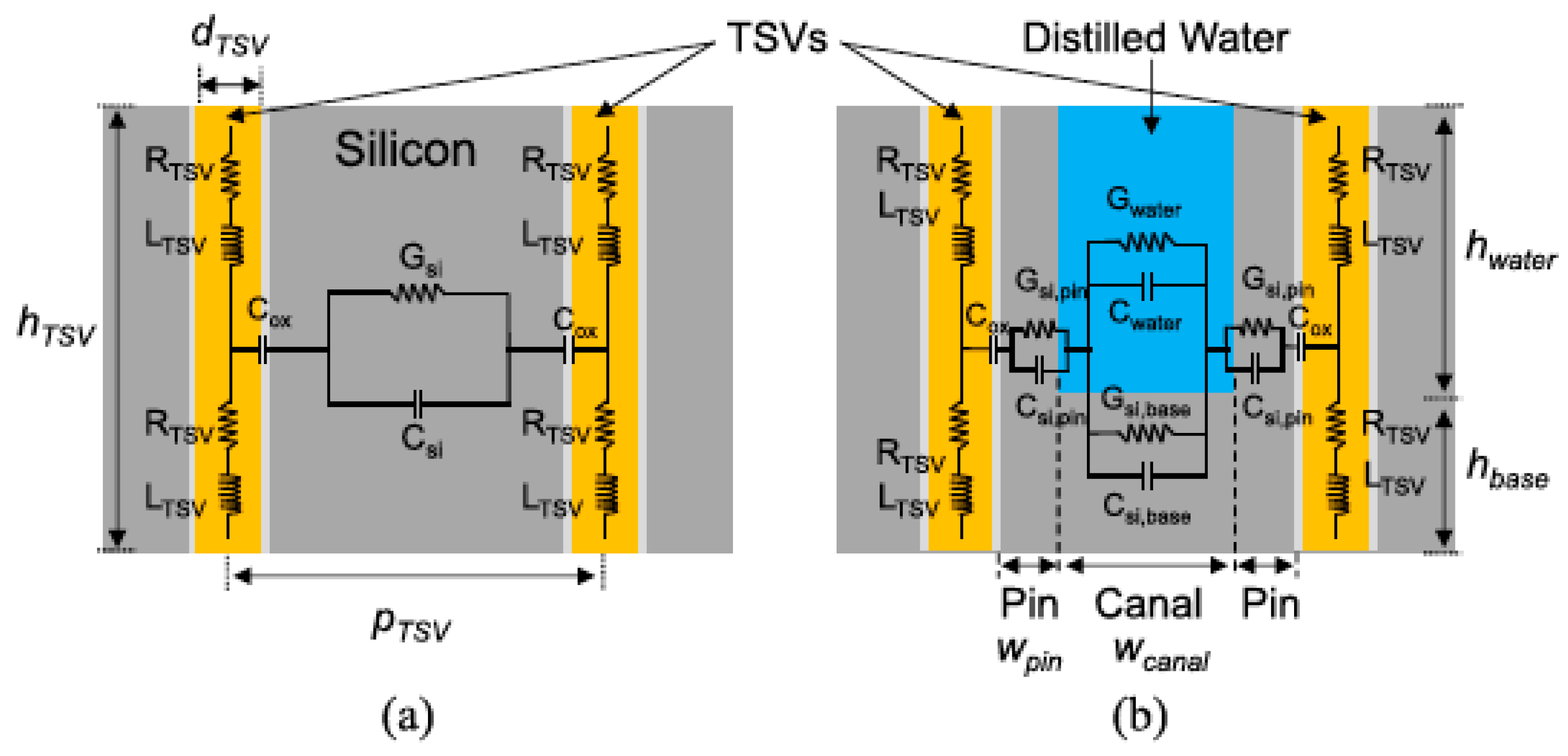

4. Influence of Microfluidic Cooling on Through Silicon Vias

5. Microfluidic Cooling Application in Specific Application

6. Thermal Models, Characteristics, and Transmissions in Microfluidic Cooling

7. Non-Uniform Heating and Hotspots

8. Conclusions

- Determining how non-uniform heating can be achieved is important for applying microfluidic cooling to 3D ICs, but no exact methods and models are yet available for evaluating hotspots.

- Digital microfluidics is an effective approach used in the cooling processes, but how drive voltage needs to be reduced when the cooling structures are embedded into 3D stacked ICs.

- More systematic achievements are required in manufacturing, testing, and designing methods when using microfluidic cooling in 3D ICs.

Author Contributions

Acknowledgments

Conflicts of Interest

References

- Beyne, E. The rise of the 3rd dimension for system integration. In Proceedings of the International Interconnect Technology Conference, Burlingame, CA, USA, 5–7 June 2006. [Google Scholar]

- Cheramy, S.; Charbonnier, J.; Henry, D.; Astier, A.; Chausse, P.; Neyret, M.; Brunet-Manquat, C.; Verrun, S.; Sillon, N.; Bonnot, L.; et al. 3D integration process flow for set-top box application: Description of technology and electrical results. In Proceedings of the 2009 EMPC 2009 European Microelectronics and Packaging Conference, Rimini, Italy, 15–18 June 2009. [Google Scholar]

- 2015 International Technology Roadmap for Semiconductors (ITRS). Available online: https://www.semiconductors.org/main/2015_international_technology_roadmap_for_semiconductors_itrs/ (accessed on 7 June 2018).

- Bar-Cohen, A. Thermal management of on-chip hot spots and 3D chip stacks. In Proceedings of the IEEE International Conference on Microwaves, Communications, Antennas and Electronics Systems, Tel Aviv, Israel, 9–11 November 2009. [Google Scholar]

- Paik, P.Y.; Pamula, V.K.; Chakrabarty, K. A digital-microfluidic approach to chip cooling. IEEE Des. Test Comput. 2008, 25, 372–381. [Google Scholar] [CrossRef]

- Demello, A.J. Control and detection of Chemical reactions in microfluidic systems. Nature 2006, 442, 394–402. [Google Scholar] [CrossRef] [PubMed]

- Available online: http://money.cnn.com/magazines/business2/business2_archive/2004/09/01/toc.html (accessed on 7 June 2018).

- Whitesides, G.M. The origins and the future of microfluidics. Nature 2006, 442, 368–373. [Google Scholar] [CrossRef] [PubMed]

- Keller, J. DARPA moves forward with ICECool thermal-management program for embedded computing. Mil. Aerosp. Electron. 2013, 6, 15–23. [Google Scholar]

- Altman, D.H.; Gupta, A.; Tyhach, M. Development of a diamond microfluidics-based intra-chip cooling technology for GaN. In ASME 2015 International Technical Conference and Exhibition on Packaging and Integration of Electronic and Photonic Microsystems Collocated with the ASME 2015 13th International Conference on Nanochannels, Microchannels, and Minichannels (pp. V003T04A006-V003T04A006); American Society of Mechanical Engineers: New York, NY, USA, 2015. [Google Scholar]

- Bar-Cohen, A.; Maurer, J.J.; Felbinger, J.G. DARPA’s intra/inter chip enhanced cooling (ICECool) program. In Proceedings of the CS MANTECH Conference, New Orleans, LA, USA, 13–16 May 2013. [Google Scholar]

- Yarin, L.P.; Mosyak, A.; Hetsroni, G. Fluid Flow, Heat Transfer and Boiling in Micro-Channels; Springer: Berlin/Heidelberg, Germany, 2009. [Google Scholar]

- Bar-Cohen, A.; Geisler, K.J.L. Cooling the electronic brain. Mech. Eng. 2011, 133, 38–41. [Google Scholar]

- Bar-Cohen, A.; Sheehan, J.R.; Rahim, E. Two-phase thermal transport in microgap channels—Theory, experimental results, and predictive relations. Microgravity Sci. Technol. 2012, 24, 1–15. [Google Scholar] [CrossRef]

- Zhang, Y.; Zheng, L.; Bakir, M.S. 3-D stacked tier-specific microfluidic cooling for heterogeneous 3-D ICs. IEEE Trans. Compon. Packag. Manuf. Technol. 2013, 3, 1811–1819. [Google Scholar] [CrossRef]

- Hassan, S.M.; Yalamanchili, S. Understanding the impact of air and microfluidics cooling on performance of 3D stacked memory systems. In Proceedings of the 2nd International Symposium on Memory Systems, Alexandria, VA, USA, 3–6 October 2016. [Google Scholar]

- Madhour, Y.; Brunschwiler, T.; Kazzi, M.E.; Thome, J.R. Patterned die-to-die thin film bonding for 3D chip stacks with integrated microfluidic cooling. In Proceedings of the International Conference on Electronic Packaging Technology and High Density Packaging, Guilin, China, 13–16 August 2012. [Google Scholar]

- Thadesar, P.A.; Li, Z.; Bakir, M.S. Low-loss silicon interposer for three-dimensional system integration with embedded microfluidic cooling. In Proceedings of the Symposium on VLSI Technology (VLSI-Technology): Digest of Technical Papers, Honolulu, HI, USA, 9–12 June 2014. [Google Scholar]

- Zhang, Y.; Dembla, A.; Joshi, Y.; Bakir, M.S. 3D stacked microfluidic cooling for high-performance 3D ICs. In Proceedings of the 62nd Electronic Components and Technology Conference, San Diego, CA, USA, 29 May–1 June 2012. [Google Scholar]

- Zhang, Y.; Bakir, M.S. Independent interlayer microfluidic cooling for heterogeneous 3D IC applications. Electron. Lett. 2013, 49, 404–406. [Google Scholar] [CrossRef]

- Zheng, L.; Zhang, Y.; Bakir, M.S. Design, fabrication and assembly of a novel electrical and microfluidic I/Os for 3-D chip stack and silicon interposer. In Proceedings of the Electronic Components and Technology Conference, Las Vegas, NV, USA, 28–31 May 2013. [Google Scholar]

- Xie, J.; Swaminathan, M. Electrical-thermal co-simulation of 3D integrated systems with micro-fluidic cooling and joule heating effects. IEEE Trans. Compon. Packag. Manuf. Technol. 2011, 1, 234–246. [Google Scholar] [CrossRef]

- Wan, Z.; Xiao, H.; Joshi, Y.; Yalamanchili, S. Co-design of multicore architectures and microfluidic cooling for 3D stacked ICs. In Proceedings of the International Workshop on Thermal Investigations of ICS and Systems, Berlin, Germany, 25–27 September 2013. [Google Scholar]

- Shi, B.; Srivastava, A.; Bar-Cohen, A. Co-design of micro-fluidic heat sink and thermal through-silicon-vias for cooling of three-dimensional integrated circuit. IET Circu its Dev. Syst. 2013, 7, 223–231. [Google Scholar] [CrossRef]

- Caleb, S. Architectural-Physical Co-Design of 3D CPUs with Microfluidic Cooling; University of Maryland: College Park, MD, USA, 2016. [Google Scholar]

- Zhang, Y.; Dembla, A.; Bakir, M.S. Silicon micropin-fin heat sink with integrated TSVs for 3-D ICs: Tradeoff analysis and experimental testing. IEEE Trans. Compon. Packag. Manuf. Technol. 2013, 3, 1842–1850. [Google Scholar] [CrossRef]

- Wan, Z.; Wen, Y.; Joshi, Y.; Mukhopadhyay, S. Enhancement in CMOS chip performance through microfluidic cooling. In Proceedings of the International Workshop on Thermal Investigations of ICS and Systems, London, UK, 24–26 September 2014. [Google Scholar]

- Chlieh, O.L.; Khan, W.T.; Papapolymerou, J. L-band tunable microstrip bandpass filter on multilayer organic substrate with integrated microfluidic channel. In Proceedings of the Microwave Symposium, Tampa, FL, USA, 1–6 June 2014. [Google Scholar]

- Cui, Y.; Sun, J.; He, Y.; Wang, Z.; Wang, P. A simple, tunable, and highly sensitive radio-frequency sensor. Appl. Phys. Lett. 2013, 103. [Google Scholar] [CrossRef] [PubMed]

- Curran, B.; Ndip, I.; Guttovski, S.; Reichl, H. The impacts of dimensions and return current path geometry on coupling in single ended Through Silicon Vias. In Proceedings of the Electronic Components and Technology Conference, San Diego, CA, USA, 26–29 May 2009. [Google Scholar]

- Oh, H.; Zhang, X.; May, G.S.; Bakir, M.S. High-frequency analysis of embedded microfluidic cooling within 3-D ICs using a TSV testbed. In Proceedings of the 66th Electronic Components and Technology Conference, Las Vegas, NV, USA, 31 May–3 June 2016; pp. 68–73. [Google Scholar]

- Oh, H.; Zhang, Y.; May, G.S.; Bakir, M.S. TSVs embedded in a microfluidic heat sink: High-frequency characterization and thermal modeling. In Proceedings of the 20th Workshop on Signal and Power Integrity (SPI), Turin, Italy, 8–11 May 2016; pp. 1–4. [Google Scholar]

- Oh, H.; Gu, J.M.; Hong, S.J.; May, G.S.; Bakir, M.S. High-aspect ratio through-silicon vias for the integration of microfluidic cooling with 3D microsystems. Microelectron. Eng. 2015, 142, 30–35. [Google Scholar] [CrossRef]

- Oh, H.; May, G.S.; Bakir, M.S. Analysis of signal propagation through TSVs within distilled water for liquid-cooled microsystems. IEEE Trans. Electron Dev. 2016, 63, 1176–1181. [Google Scholar] [CrossRef]

- Qian, H.; Liang, H.; Chang, C.H.; Zhang, W. Thermal simulator of 3D-IC with modeling of anisotropic TSV conductance and microchannel entrance effects. In Proceedings of the 18th Asia and South Pacific Design Automation Conference (ASP-DAC), Yokohama, Japan, 22–25 January 2013. [Google Scholar]

- Serafy, C.; Shi, B.; Srivastava, A.; Yeung, D. High performance 3D stacked DRAM processor architectures with micro-fluidic cooling. In Proceedings of the IEEE International 3D Systems Integration Conference, San Francisco, CA, USA, 2–4 October 2013. [Google Scholar]

- Yang, Z.; Srivastava, A. Physical design of 3D FPGAs embedded with micro-channel-based fluidic cooling. In Proceedings of the Acm/sigda International Symposium on Field-Programmable Gate Arrays, Monterey, CA, USA, 21–23 February 2016. [Google Scholar]

- Sarvey, T.E.; Zhang, Y.; Cheung, C.; Gulata, R.; Rahman, A.; Dasu, A. Monolithic integration of a micropin-fin heat sink in a 28-nm FPGA. IEEE Trans. Compon. Packag. Manuf. Technol. 2017, 7, 1617–1624. [Google Scholar] [CrossRef]

- Serafy, C.; Bar-Cohen, A.; Srivastava, A.; et al. Unlocking the true potential of 3-D CPUs with microfluidic cooling. IEEE Trans. Larg. Scale Integr. Syst. 2016, 24, 1515–1523. [Google Scholar] [CrossRef]

- Serafy, C.; Yang, Z.; Hu, Y.; Srivastava, A.; Joshi, Y. Thermo-electric co-design of 3D CPUs and embedded micro-fluidic pin-fin heatsinks. IEEE Des. Test 2016, 33, 40–48. [Google Scholar] [CrossRef]

- Zhang, Y.; Oh, H.; Bakir, M.S. Within-tier cooling and thermal isolation technologies for heterogeneous 3D ICs. In Proceedings of the 3D Systems Integration Conference, San Francisco, CA, USA, 2–4 October 2013. [Google Scholar]

- Zheng, L.; Zhang, Y.; Zhang, X.; Bakir, M.S. Silicon interposer with embedded microfluidic cooling for high-performance computing systems. In Proceedings of the Electronic Components and Technology Conference (ECTC), San Diego, CA, USA, 26–29 May 2015. [Google Scholar]

- Li, Z.; Yang, Z.; Bakir, M.S. A Silicon interposer platform utilizing microfluidic cooling for high-performance computing systems. IEEE Trans. Compon. Packag. Manuf. Technol. 2017, 5, 1379–1386. [Google Scholar]

- Schultz, M.D.; Parida, P.R.; Gaynes, M.; Ozsun, O.; McVicker, G.; Drechsler, U.; Chainer, T. Microfluidic two-phase cooling of a high power microprocessor part A: Design and fabrication. In Proceedings of the IEEE Intersociety Conference on Thermal and Thermomechanical Phenomena in Electronic Systems, Orlando, FL, USA, 30 May–2 June 2017. [Google Scholar]

- Schultz, M.D.; Parida, P.R.; Gaynes, M.; Ozsun, O.; McVicker, G.; Drechsler, U.; Chainer, T. Microfluidic two-phase cooling of a high power microprocessor part B: Test and characterization. In Proceedings of the IEEE Intersociety Conference on Thermal and Thermomechanical Phenomena in Electronic Systems, Orlando, FL, USA, 30 May–2 June 2017. [Google Scholar]

- Sabry, M.M.; Sridhar, A.; Atienza, D.; Ruch, P. Integrated microfluidic power generation and cooling for bright silicon MPSoCs. In Proceedings of the Design, Automation and Test in Europe Conference and Exhibition, Dresden, Germany, 24–28 March 2014. [Google Scholar]

- Wen, Y.; Wan, Z.; He, X.; Yalamanchili, S.; Joshi, Y. Active fluidic cooling on energy constrained system-on-chip systems. IEEE Trans. Compon. Packag. Manuf. Technol. 2017, 7, 1813–1822. [Google Scholar]

- Chlieh, O.L.; Morcillo, C.A.D.; Pavlidis, S.; Khan, W.; Papapolymerou, J. Integrated microfluidic cooling for GaNdevices on multilayer organic LCP substrate. In Proceedings of the Microwave Symposium Digest, Seattle, WA, USA, 2–7 June 2013. [Google Scholar]

- Chlieh, O.L.; Papapolymerou, J. Hybrid integrated microfluidic channels on multilayer organic substrate and on copper for tuning and cooling an RF reconfigurable S-/C-band GaN-based power amplifier. IEEE Trans. Microw. Theory Tech. 2017, 65, 156–164. [Google Scholar] [CrossRef]

- Ditri, J.; Pearson, R.R.; Cadotte, R.; Hahn, J.W.; Fetterolf, D.; McNulty, M.; Luppa, D. GaN unleashed: The benefits of microfluidic cooling. IEEE Trans. Semicond. Manuf. 2016, 29, 376–383. [Google Scholar] [CrossRef]

- Chlieh, O.L.; Khan, W.T.; Papapolymerou, J. Thermal modelling of microfluidic channels for cooling high power resistors on multilayer organic liquid crystal polymer substrate. J. Electron. Packag. 2015, 137. [Google Scholar] [CrossRef]

- Wan, Z.; Xiao, H.; Joshi, Y.; Yalamanchili, S. S3-P9: Thermal and electrical performance of microfluidically cooled 3D ICs with non-uniform power dissipation. In Proceedings of the Lester Eastman Conference on High PERFORMANCE Devices, Ithaca, NY, USA, 5–7 August 2014. [Google Scholar]

- Agarwal, G.; Kazior, T.; Kenny, T.; Weinstein, D. Modeling and analysis for thermal management in GaN HEMTs using microfluidic cooling. J. Electron. Packag. 2017, 139. [Google Scholar] [CrossRef]

- Wang, G.L.; Yang, D.W.; Wang, Y.; Niu, D.; Zhao, X.L.; Ding, G.F. Heat transfer and friction characteristics of the microfluidic heat sink with variously-shaped ribs for chip cooling. Sensors 2015, 15, 9547–9562. [Google Scholar] [CrossRef] [PubMed]

- Zhang, X.; Han, X.; Sarvey, T.T.; Green, C.E.; Kottke, P.A. Three-dimensional integrated circuit with embedded microfluidic cooling: Technology, thermal performance, and electrical implications. J. Electron. Packag. 2016, 138. [Google Scholar] [CrossRef]

- Waddell, A.M.; Punch, J.; Stafford, J.; Jeffers, N. The characterization of a low-profile channel–confined jet for targeted hot-spot cooling in microfluidic applications. Int. J. Heat Mass Transf. 2016, 101, 620–628. [Google Scholar] [CrossRef]

- Pi, Y.; Wang, W.; Chen, J.; Jin, Y. Microfluidic cooling for distributed hot-spots. In Proceedings of the Electronic Components and Technology Conference, Las Vegas, NV, USA, 31 May–3 June 2016. [Google Scholar]

- Sharma, C.S.; Tiwari, M.K.; Poulikakos, D. A simplified approach to hotspot alleviation in microprocessors. Appl. Ther. Eng. 2016, 93, 1314–1323. [Google Scholar] [CrossRef]

- Pamula, V.K.; Chakrabarty, K. Cooling of integrated circuits using droplet-based microfluidics. In Proceedings of the 13th ACM Great Lakes Symposium on Vlsi, Washington, DC, USA, 28–29 April 2003. [Google Scholar]

- Paik, P.Y.; Pamula, V.K.; Chakrabarty, K. Adaptive cooling of integrated circuits using digital microfluidics. IEEE Trans. Larg. Scale Integr. Syst. 2008, 16, 432–443. [Google Scholar] [CrossRef]

- Bindiganavale, G.S. Study of Hotspot Cooling for Integrated Circuits Using Electrowetting on Dielectric Digital Microfluidic System; The University of Texas: Arlington, TX, USA, 2015. [Google Scholar]

- Bindiganavale, G.; You, S.M.; Moon, H. Study of hotspot cooling using electrowetting on dielectric digital microfluidic system. In Proceedings of the International Conference on MICRO Electro Mechanical Systems, San Francisco, CA, USA, 26–30 January 2014. [Google Scholar]

- Jagath, B. Yaddessalage, Study of the Capabilities of Electrowetting on Dielectric Digital Microfluidics towards the High efficient thin film Evaporative Cooling Platform; The University of Texas: Arlington, TX, USA, 2013. [Google Scholar]

- Park, S.Y.; Nam, Y. Single-Sided Digital Microfluidic (SDMF) Devices for Effective Coolant Delivery and Enhanced Two-Phase Cooling. Micromachines 2017, 8, 3. [Google Scholar] [CrossRef]

- Qian, H.; Chang, C.-H.; Yu, H. An efficient channel clustering and flow rate allocation algorithm for: Non-uniform microfluidic cooling of 3D integrated circuits. Integr. VLSI J. 2013, 46, 57–68. [Google Scholar] [CrossRef]

- Sharma, C.S.; Tiwari, M.K.; Zimmermann, S.; Brunschwiler, T.; Schlottig, G.; Michel, B.; Poulikakos, D. Energy efficient hotspot-targeted embedded liquid cooling of electronics. Appl. Energy 2015, 138, 414–422. [Google Scholar] [CrossRef]

- Lorenzini, D.; Green, C.; Sarvey, T.E.; Zhang, X.; Hu, Y.; Fedorov, A.G.; Bakir, M.S.; Joshi, Y. Embedded single phase microfluidic thermal management for non-uniform heating and hotspots using microgaps with variable pin fin clustering. Int. J. Heat Mass Transf. 2016, 103, 1359–1370. [Google Scholar] [CrossRef]

- Sarvey, T.E.; Hu, Y.; Green, C.E.; Kottke, P.A.; Woodrum, D.C.; Joshi, Y.K.; Fedorov, A.G.; Sitaraman, S.K.; Bakir, M.S. Integrated circuit cooling using heterogeneous micropin-fin arrays for nonuniform power maps. IEEE Trans. Compon. Packag. Manuf. Technol. 2017, 7, 1465–1475. [Google Scholar] [CrossRef]

- Zheng, L.; Zhang, Y.; Huang, G.; Bakir, M.S. Novel electrical and fluidic microbumps for silicon interposer and 3-D ICs. IEEE Trans. Compon. Packag. Manuf. Technol. 2014, 4, 777–785. [Google Scholar] [CrossRef]

- Azarkish, H.; Barrau, J.; Coudrain, P.; Savelli, G.; Collin, L.; Frechette, L.G. Self-adaptive microvalve array for energy efficient fluidic cooling in microelectronic systems. In Proceedings of the 16th Intersociety Conference on Thermal and Thermomechanical Phenomena in Electronic Systems, Orlando, FL, USA, 30 May–2 June 2017; pp. 522–529. [Google Scholar]

- Laguna, G.; Azarkish, H.; Vilarrubi, M.; Ibariez, M.; Roseli, J.; Betancourt, Y. Microfluidic cell cooling system for electronics. In Proceedings of the International Workshop on Thermal Investigations of ICS and Systems, Orlando, FL, USA, 30 May–2 June 2017. [Google Scholar]

- Sahu, V.; Fedorov, A.G.; Joshi, Y.K. Transient characterization of hybrid microfluidic-thermoelectric cooling scheme for dynamic thermal management of microprocessor. J. Electron. Packag. 2014, 136. [Google Scholar] [CrossRef]

- Wirdatmadja, S.A.; Moltchanov, D.; Balasubramaniam, S.; Koucheryavy, Y. Microfluidic system protocols for integrated on-chip communications and cooling. IEEE Access 2017, 5, 2417–2429. [Google Scholar] [CrossRef]

| Categories | The Methods Used in the Literatures | References |

|---|---|---|

| The analysis of non-uniform heating and hotspots | A novel, low profile jet impingement was given within an individual channel suitable for targeting hotspots in a densely packed circuit, at the low Reynolds numbers prevalent in micro-fluidic applications (Re < 500). | A.M. Waddell et al. (2016) [56] |

| A micro-fluidic cooling chip with different-sized hotspots was fabricated to investigate the influence of hotspot characteristics on the cooling ability of the embedded micro-channel. | Y.D. Pi et al. (2016) [57] | |

| A one-dimensional, semi-empirical approach was presented for quick design of a microchannel heat sink for targeted, energy-efficient liquid cooling of hotspots in microprocessors. | C.S. Sharma (2016) [58] | |

| Using digital microfluidics to solve non-uniform heating | A digital microfluidic cooling platform enabled adaptive cooling in IC design. | P.Y. Paik et al. (2008) [5] |

| A cooling method based on high-speed electrowetting manipulation of discrete sub-microliter droplets was achieved under voltage control with volume flow rates in excess of 10 mL/min. | V.K. Pamula et al. (2003) [59] | |

| An alternative cooling technique based on a recently invented “digital microfluidic” platform was reached. | P.Y. Paik et al. (2008) [60] | |

| An innovative approach to regulate hotspot temperature was demonstrated by creating a hydrophilic spot (H-spot) on the heater that retains a small droplet while the main coolant droplet passes over the hotspot. | G.S. Bindiganavale (2015) [61] | |

| A novel digital microfluidic liquid cooling system using electrowetting on dielectric developed for demonstrating and studying hotspot cooling towards electronics thermal management was shown. | G.S. Bindiganavale et al. (2014) [62] | |

| The high accuracy and consistency in volume of coolant nanodrops dispensed from the reservoir, the fast motion of coolant nanodrops to the hotspot to avoid dry-out, and the simultaneous achievement of both small volume and high frequency of nanodrop that arrives to the hotspot were analyzed. | J.B. Yaddessalage (2013) [63] | |

| A single-sided digital microfluidic device that enables not only effective liquid handling on a single-sided surface but also two-phase heat transfer to enhance thermal rejection performance was created. | S.Y. Park et al. (2017) [64] | |

| Changing channel clustering for non-uniform heating | An efficient clustering algorithm was used to guide the division of microchannels into clusters and the allocation of cooling resources to each cluster in order to achieve an effective microfluidic cooling with a minimal total flow rate. | H.H. Qian et al. (2011) [65] |

| A novel liquid-cooling concept was studied, for targeted, energy-efficient cooling of hotspots through passively optimized microchannel structures etched into the backside of a chip. | C.S. Sharma (2014) [66] | |

| The model was presented for independent interlayer microfluidic cooling for heterogeneous 3D IC applications. | Y. Zhang (2013) [20] | |

| Using novel structures for non-uniform heating | A single microfluidic loop was demonstrated for the combined and efficient cooling of hotspot and moderate power areas. | D. Lorenzini et al. (2016) [67] |

| Non-uniform micropin-fin heat sinks for the cooling of ICs with non-uniform maps were studied. | T.E. Sarvey et al. (2017) [68] | |

| Fine pitch electrical microbumps and annular shaped fluidic microbumps were achieved to enable high bandwidth die-to-die signaling, embedded microfluidic cooling and power delivery for silicon interposer and 3D integrated electronics systems | L. Zheng et al. (2014) [69] | |

| Temperature-regulated microvalves were designed for energy-efficient fluidic cooling of microelectronic systems. | H. Azarkish et al. (2017) [70] | |

| A liquid cooling device was achieved based on a matrix of microfluidic cells with individually flow rate controlling microvalves for temperature uniformities. | G. Laguna et al. (2017) [71] | |

| The test and protocols for non-uniform heating solving methods | Novel thermal testbeds with embedded micropin-fin heat sinks for 3D ICs were created. | X.C. Zhang et al. (2016) [72] |

| Microfluidic system protocols for integrated on-chip communication and cooling were demonstrated. | S.A. Wirdatmadja et al. (2017) [73] |

© 2018 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Wang, S.; Yin, Y.; Hu, C.; Rezai, P. 3D Integrated Circuit Cooling with Microfluidics. Micromachines 2018, 9, 287. https://doi.org/10.3390/mi9060287

Wang S, Yin Y, Hu C, Rezai P. 3D Integrated Circuit Cooling with Microfluidics. Micromachines. 2018; 9(6):287. https://doi.org/10.3390/mi9060287

Chicago/Turabian StyleWang, Shaoxi, Yue Yin, Chenxia Hu, and Pouya Rezai. 2018. "3D Integrated Circuit Cooling with Microfluidics" Micromachines 9, no. 6: 287. https://doi.org/10.3390/mi9060287

APA StyleWang, S., Yin, Y., Hu, C., & Rezai, P. (2018). 3D Integrated Circuit Cooling with Microfluidics. Micromachines, 9(6), 287. https://doi.org/10.3390/mi9060287