Current Understanding of Bias-Temperature Instabilities in GaN MIS Transistors for Power Switching Applications

Abstract

:1. Introduction

2. Devices, Models, and Methods

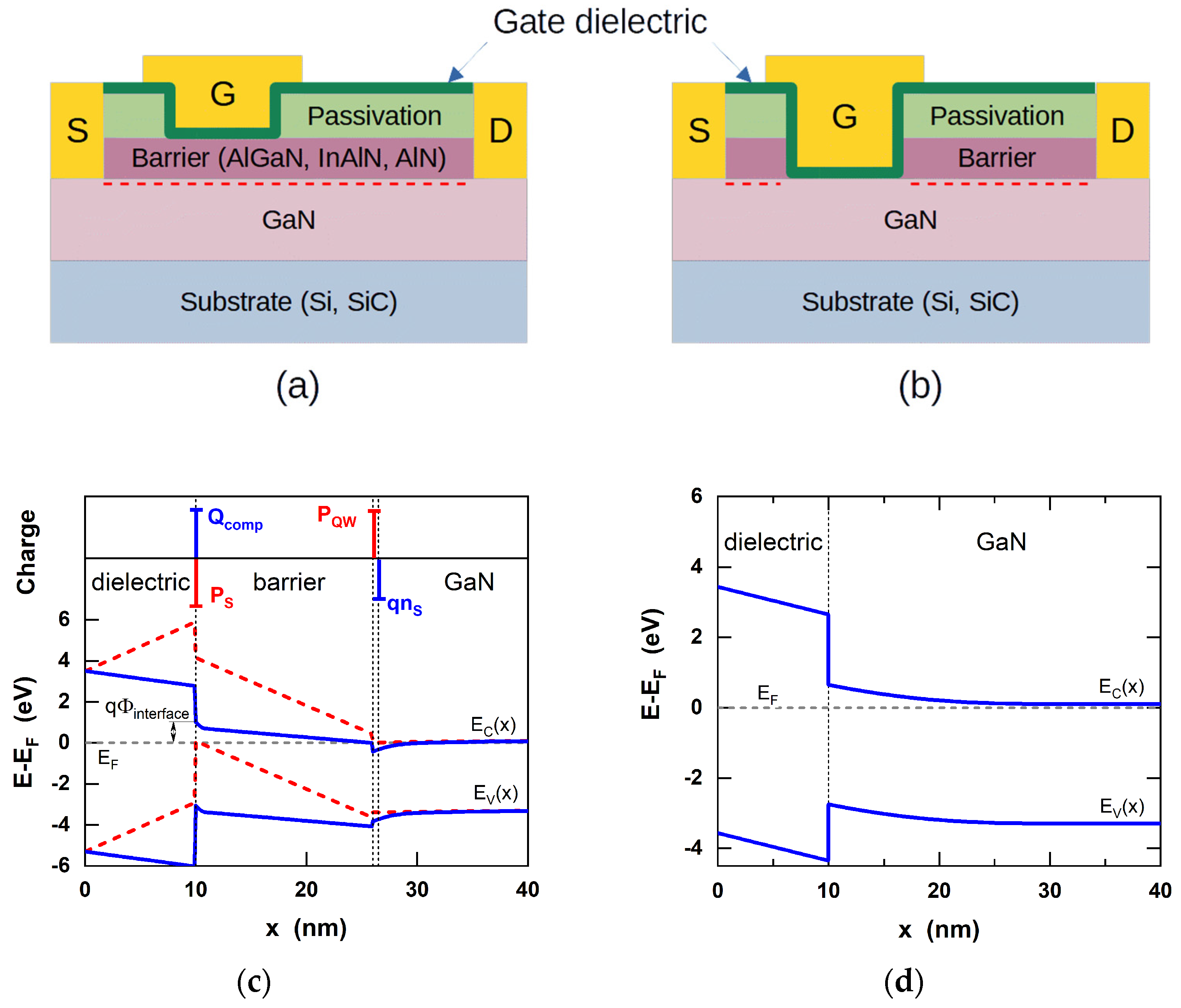

2.1. GaN MISHEMTs and MISFETs

2.1.1. E-Mode GaN MIS Transistors

2.1.2. Gate Materials and Technologies

2.2. Modeling of Defect States in the Gate Stack

2.2.1. Interface Traps

2.2.2. Disorder-Induced Gap States in the Gate Dielectric

2.2.3. Dielectric Bulk Traps and ‘Border’ Traps

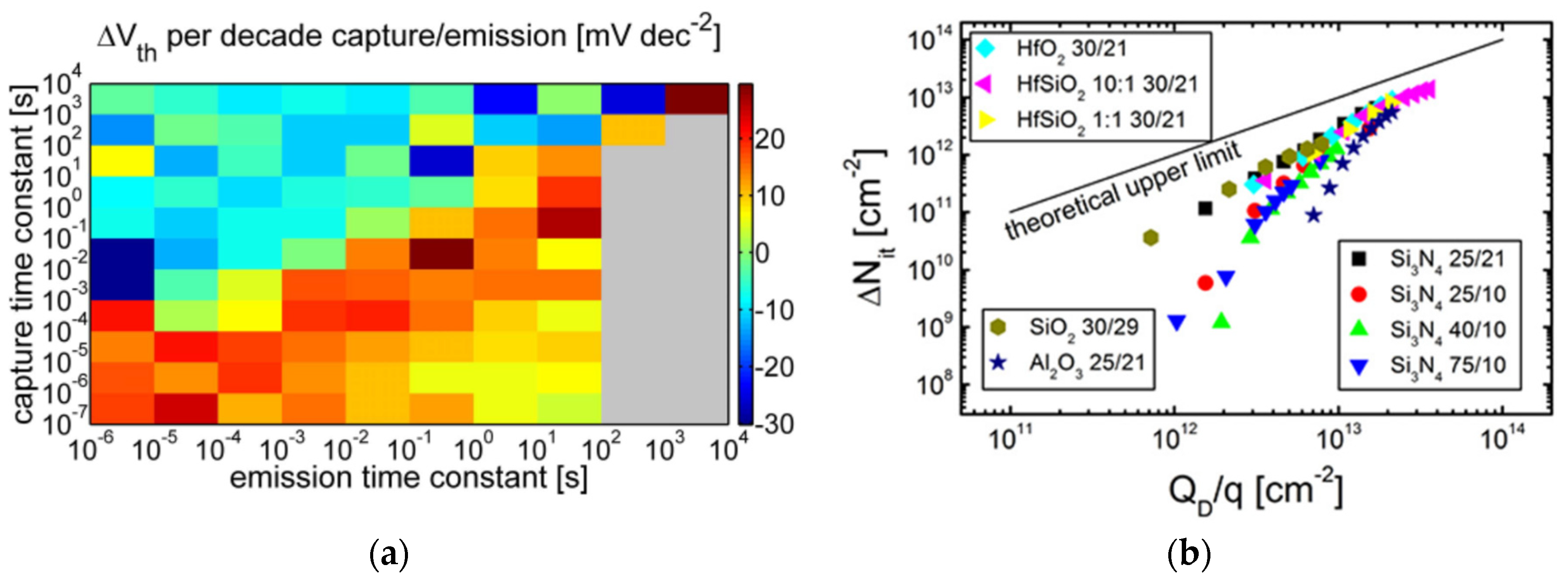

2.2.4. Effects of Trapping Dynamics

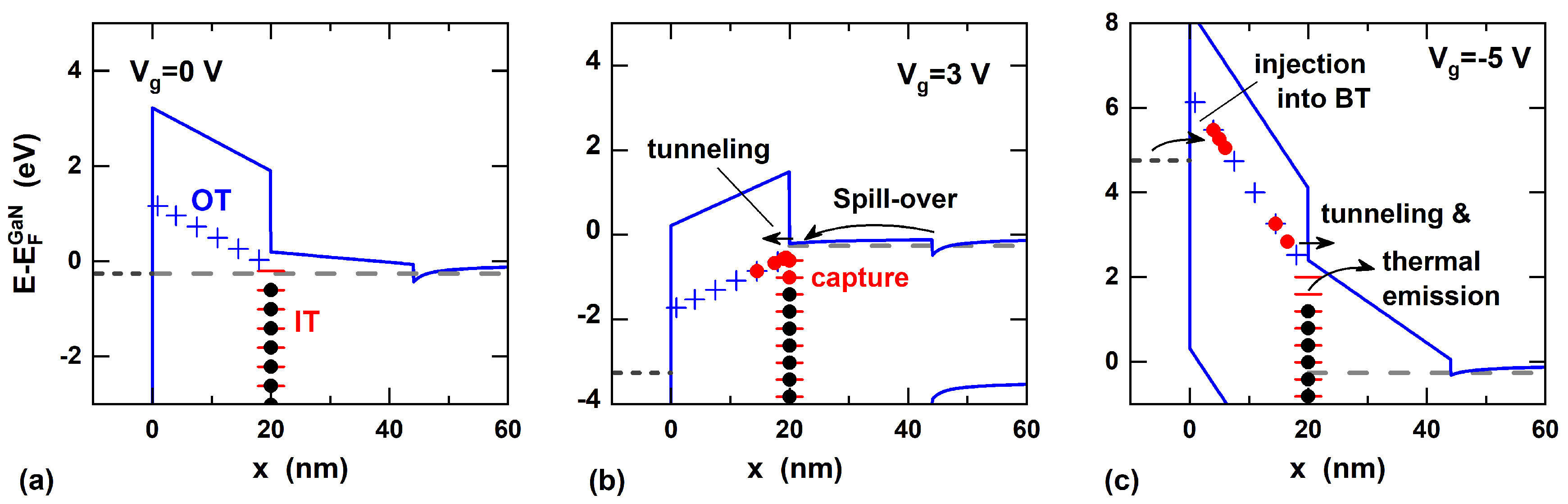

2.2.5. Pictorial View of VTH Instabilities in GaN MISHEMTs

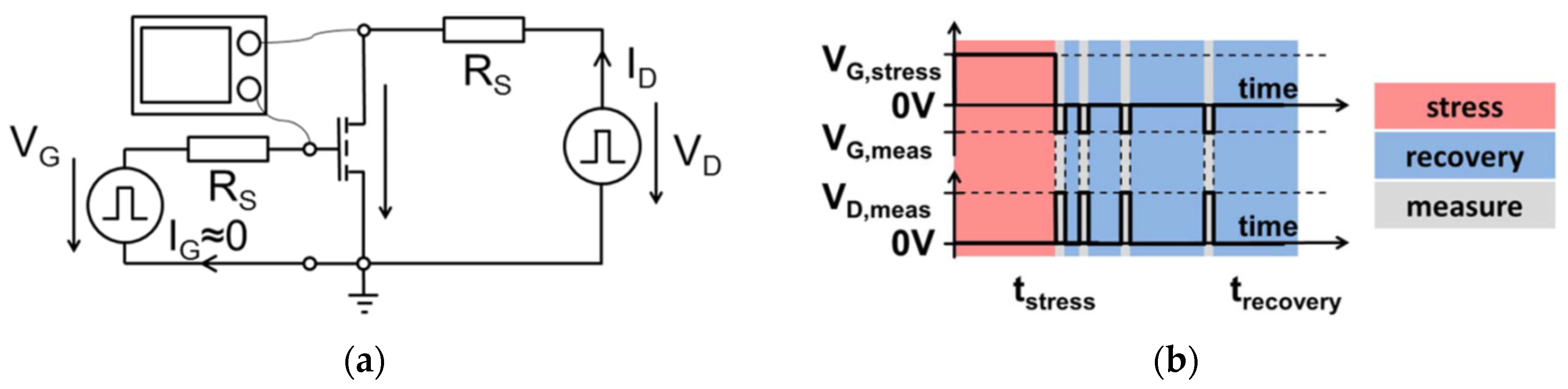

2.3. BTI Measurement Techniques

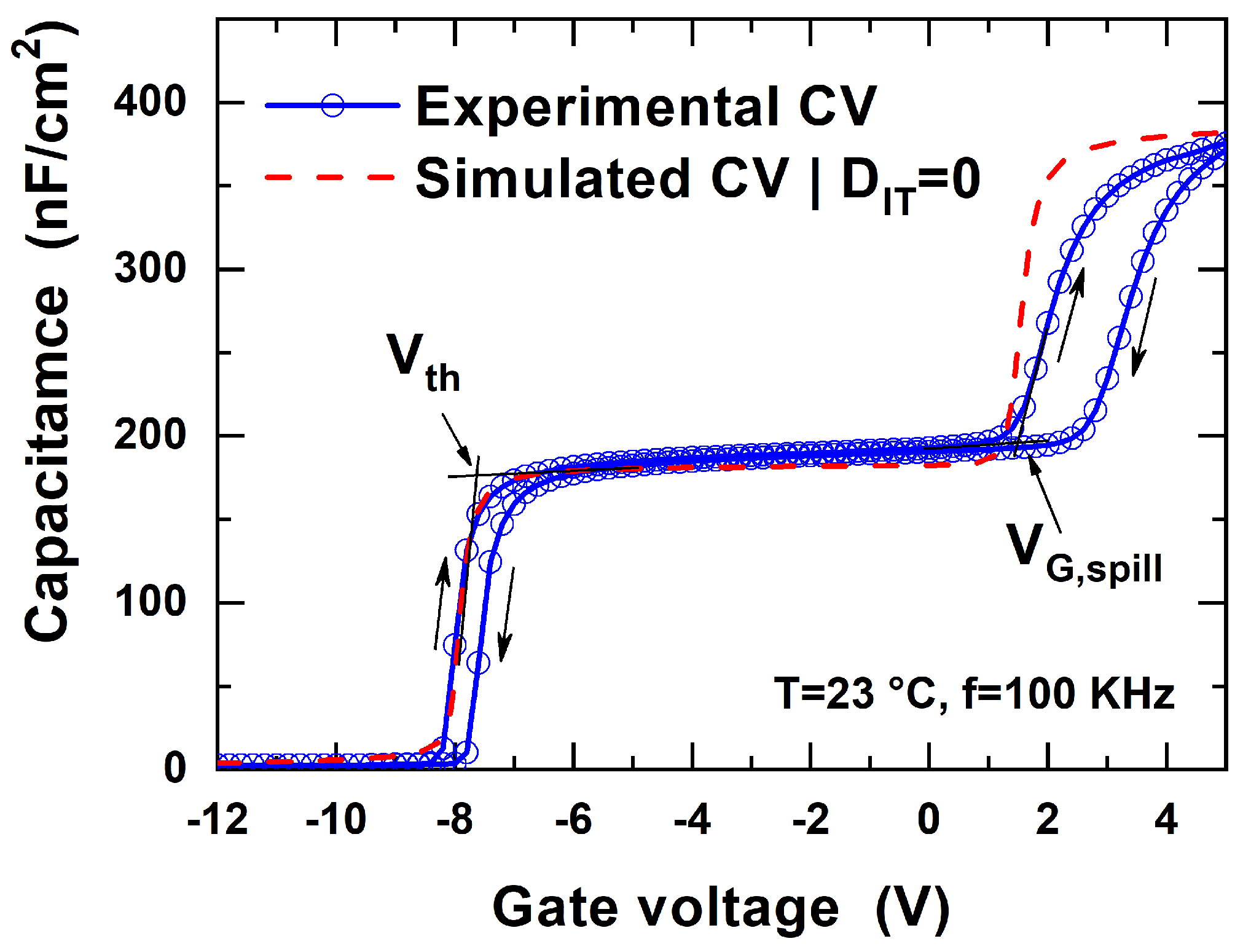

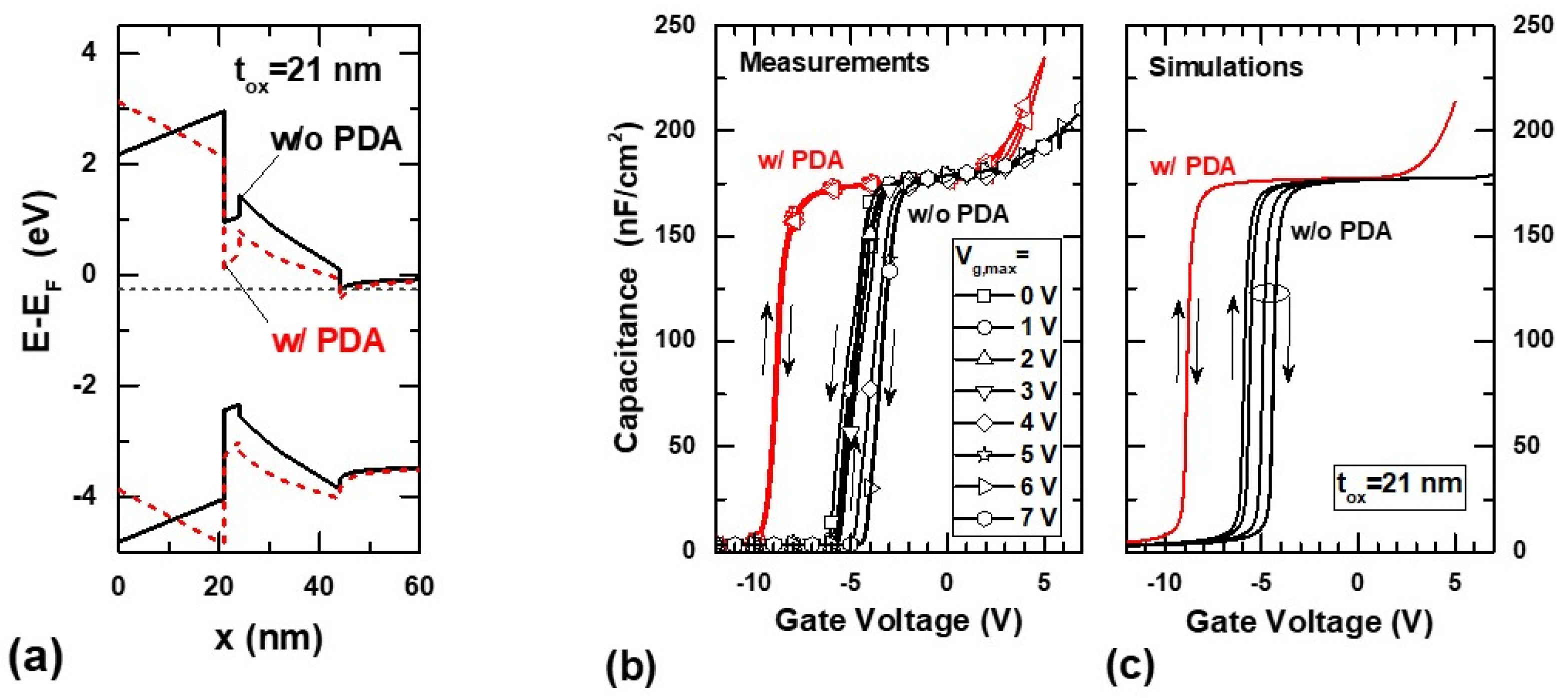

2.3.1. Capacitance Techniques

2.3.2. Stress-Measure IV and Pulsed ID Techniques

3. BTI in GaN MISHEMTs

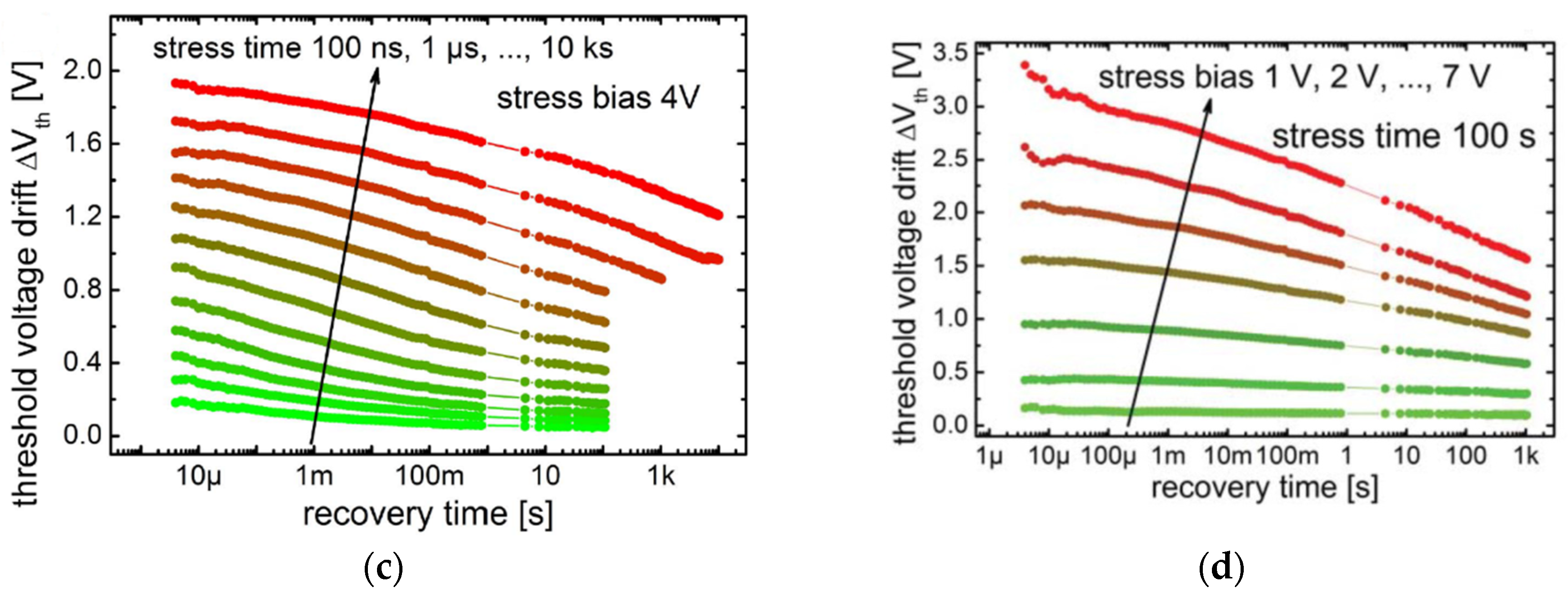

3.1. PBTI in D-Mode GaN MISHEMTs

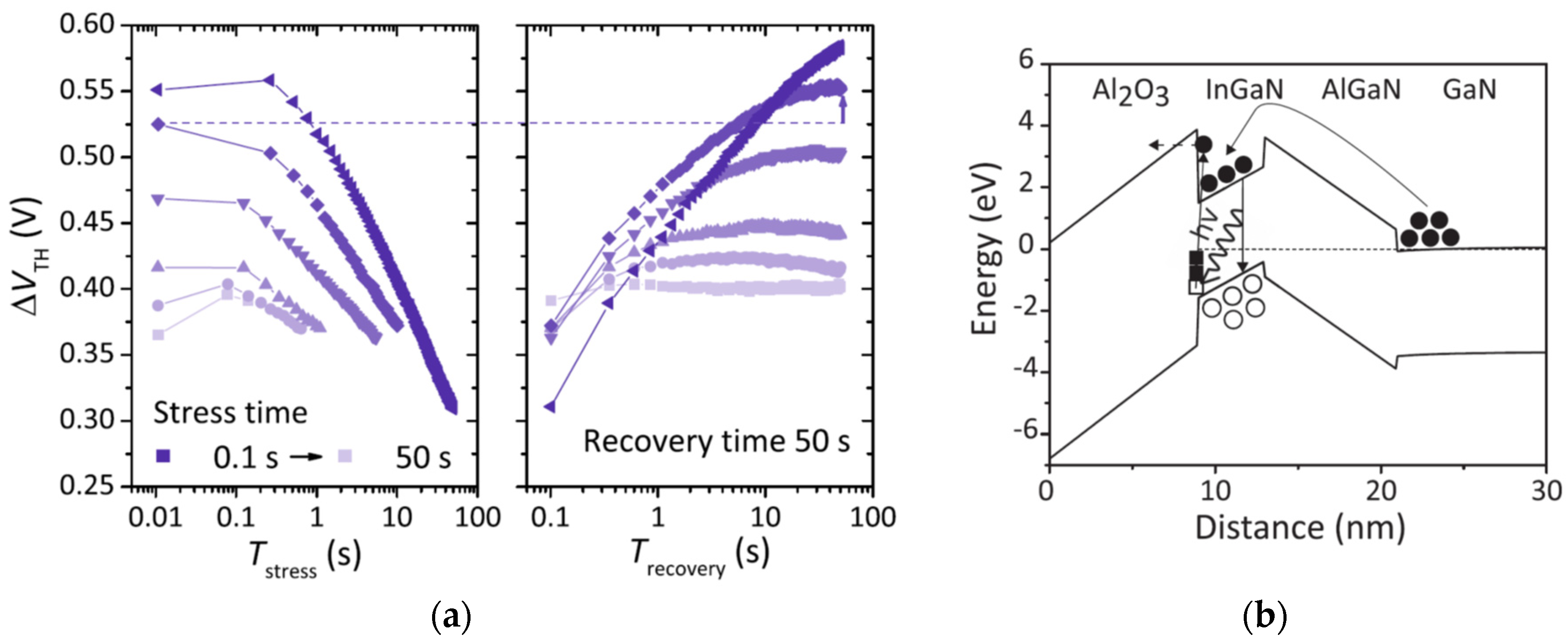

3.2. PBTI in E-Mode MISHEMTs

3.3. NBTI in GaN MISHEMTs

4. BTI in GaN MISFETs

4.1. PBTI in GaN MISFETs

4.2. NBTI in GaN MISFETs

5. Conclusions and Prospects

Funding

Conflicts of Interest

References

- Dmitriev, V.A.; Irvine, K.G.; Carter, C.H., Jr.; Kuznetsov, N.I.; Kalinina, E.V. Electric breakdown in GaN p–n junctions. Appl. Phys. Lett. 1996, 68, 229–231. [Google Scholar] [CrossRef]

- Gelmont, B.; Kim, K.; Shur, M. Monte Carlo simulation of electron transport in gallium nitride. J. Appl. Phys. 1993, 74, 1818–1821. [Google Scholar] [CrossRef]

- Sichel, E.K.; Pankove, J.I. Thermal conductivity of GaN, 25-360 K. J. Phys. Chem. Solids 1977, 38, 330. [Google Scholar] [CrossRef]

- Mishra, U.K.; Parikh, P.; Wu, Y.-F. AlGaN/GaN HEMTs-an overview of device operation and applications. Proc. IEEE 2002, 6, 1022–1031. [Google Scholar] [CrossRef] [Green Version]

- Dora, Y. High breakdown voltage achieved on AlGaN/GaN HEMTs with integrated slant field plates. IEEE Electron Dev. Lett. 2006, 27, 713–715. [Google Scholar] [CrossRef]

- Uemoto, Y.; Hikita, M.; Ueno, H.; Matsuo, H.; Ishida, H.; Yanagihara, M.; Ueda, T.; Tanaka, T.; Ueda, D. Gate injection transistor (GIT): A normally-off AlGaN/GaN power transistor using conductivity modulation. IEEE Trans. Electron Dev. 2007, 54, 3393–3399. [Google Scholar] [CrossRef]

- Kuzuhara, M.; Tokuda, H. Low-loss and high-voltage III-nitride transistors for power switching applications. IEEE Trans. Electron Dev. 2015, 62, 405–413. [Google Scholar] [CrossRef] [Green Version]

- Rosina, M. GaN and SiC power device: Market overview. In Proceedings of the Semicon Europa, Munich, Germany, 13–16 November 2018. [Google Scholar]

- Hashizume, T.; Nishiguchi, K.; Kaneki, S.; Kuzmik, J.; Yatabe, Z. State of the art on gate insulation and surface passivation for GaN-based power HEMTs. Mat. Sci. Semicond. Process. 2018, 78, 85–95. [Google Scholar] [CrossRef]

- Downey, B.P.; Meyer, D.J.; Roussos, J.A.; Katzer, D.S.; Ancona, M.G.; Pan, M.; Gao, X. Effect of gate insulator thickness on RF power gain degradation of vertically scaled GaN MIS-HEMTs at 40 GHz. IEEE Trans. Dev. Mat. Reliab. 2015, 15, 474–477. [Google Scholar] [CrossRef]

- Saito, W.; Takada, Y.; Kuraguchi, M.; Tsuda, K.; Omura, I. Recessed-gate structure approach toward normally off high-voltage AlGaN/GaN HEMT for power electronics applications. IEEE Trans. Electron Dev. 2006, 53, 356–362. [Google Scholar] [CrossRef]

- Capriotti, M.; Fleury, C.; Bethge, O.; Rigato, M.; Lancaster, S.; Pogany, D.; Triedel, E.-B.; Hilt, O.; Brunner, F.; Würfl, J. E-mode AlGaN/GaN True-MOS, with high-k ZrO2 gate insulator. In Proceedings of the 2015 45th European Solid-State Device Research Conference (ESSDERC), Graz, Austria, 14–18 September 2015; pp. 60–63. [Google Scholar]

- Gregušová, D.; Blaho, M.; Haščík, Š.; Šichman, P.; Laurenčíková, A.; Seifertová, A.; Dérer, J.; Brunner, F.; Würfl, J.H.; Kuzmík, J. Polarization-engineered n+GaN/InGaN/AlGaN/GaN normally-off MOS HEMTs. Phys. Stat. Solidi A 2017, 214, 1700407. [Google Scholar] [CrossRef]

- Zhang, Y.; Sun, M.; Joglekar, S.J.; Fujishima, T.; Palacios, T. Threshold voltage control by gate oxide thickness in fluorinated GaN metal-oxide-semiconductor high-electron-mobility transistors. Appl. Phys. Lett. 2013, 103, 033524. [Google Scholar] [CrossRef]

- Hori, Y.; Yatabe, Z.; Hashizume, T. Characterization of interface states in Al2O3/AlGaN/GaN structures for improved performance of high-electron-mobility transistors. J. Appl. Phys. 2013, 114, 244503. [Google Scholar] [CrossRef] [Green Version]

- Ťapajna, M.; Jurkovič, M.; Válik, L.; Haščík, Š.; Gregušová, D.; Brunner, F.; Cho, E.-M.; Kuzmík, J. Bulk and interface trapping in the gate dielectric of GaN based metal-oxide semiconductor high-electron-mobility transistors. Appl. Phys. Lett. 2013, 102, 243509. [Google Scholar] [CrossRef]

- Shih, H.-A.; Kudo, M.; Suzuki, T. Gate-control efficiency and interface state density evaluated from capacitance-frequency-temperature mapping for GaN-based metal-insulator-semiconductor devices. J. Appl. Phys. 2014, 116, 184507. [Google Scholar] [CrossRef]

- Matys, M.; Stoklas, R.; Kuzmik, J.; Adamowicz, B.; Yatabe, Z.; Hashizume, T. Characterization of capture cross sections of interface states in dielectric/III-nitride heterojunction structures. J. Appl. Phys. 2016, 119, 205304. [Google Scholar] [CrossRef] [Green Version]

- Guo, A.; del Alamo, J.A. Negative-bias temperature instability of GaN MOSFETs. In Proceedings of the 2016 IEEE International Reliability Physics Symposium (IRPS), Pasadena, CA, USA, 17–21 April 2016. [Google Scholar]

- Lagger, P.; Ostermaier, C.; Pobegen, G.; Pogany, D. Towards understanding the origin of threshold voltage instability of AlGaN/GaN MIS-HEMTs. In Proceedings of the 2012 International Electron Devices Meeting, San Francisco, CA, USA, 10–13 December 2012. [Google Scholar]

- Meneghesso, G.; Meneghini, M.; De Santi, C.; Ruzzarin, M.; Zanoni, E. Positive and negative threshold voltage instabilities in GaN-based transistors. Microelectron. Reliab. 2018, 80, 257–265. [Google Scholar] [CrossRef]

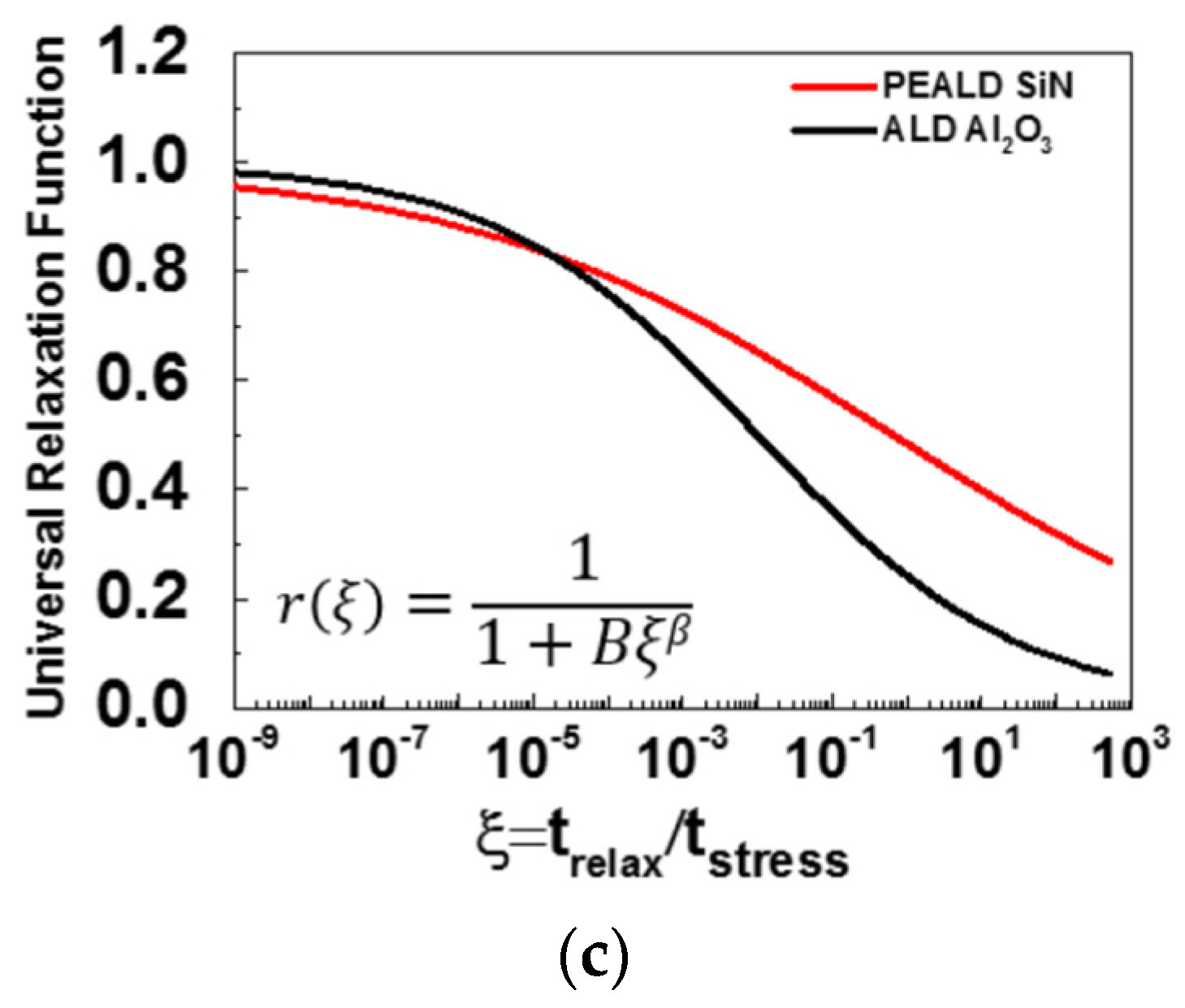

- Lagger, P.; Reiner, M.; Pogany, D.; Ostermaier, C. Comprehensive study of the complex dynamics of forward bias-induced threshold voltage drifts in GaN based MIS-HEMTs by stress/recovery experiments. IEEE Trans. Electron Dev. 2014, 61, 1022–1030. [Google Scholar] [CrossRef]

- Ostermaier, C.; Lagger, P.; Reiner, M.; Pogany, D. Review of bias-temperature instabilities at the III-N/dielectric interface. Microelectron. Reliab. 2018, 82, 62–83. [Google Scholar] [CrossRef]

- Zhang, K.; Wu, M.; Lei, X.; Chen, W.; Zheng, X.; Ma, X.; Hao, Y. Observation of threshold voltage instabilities in AlGaN/GaN MIS HEMTs. Semicond. Sci. Technol. 2014, 29, 075019. [Google Scholar] [CrossRef]

- Pohorelec, O.; Ťapajna, M.; Gregušová, D.; Gucmann, F.; Hasenöhrl, S.; Haščík, Š.; Stoklas, R.; Seifertová, A.; Pécz, B.; Tóth, L.; et al. Investigation of interfaces and threshold voltage instabilities in normally-off MOS-gated InGaN/AlGaN/GaN HEMTs. Appl. Surf. Sci. 2020, 528, 146824. [Google Scholar] [CrossRef]

- Roccaforte, F.; Greco, G.; Fiorenza, P.; Iucolano, F. An overview of normally-off GaN-based high electron mobility transistors. Materials 2019, 12, 1599. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Wu, T.-L.; Franco, J.; Marcon, D.; De Jaeger, B.; Bakeroot, B.; Stoffels, S.; Van Hove, M.; Groeseneken, G.; Decoutere, S. Toward understanding positive bias temperature instability in fully recessed-gate GaN MISFETs. IEEE Trans. Electron Dev. 2016, 63, 1853–1860. [Google Scholar] [CrossRef]

- Guo, A.; del Alamo, J.A. Unified mechanism for positive- and negative-bias temperature instability in GaN MOSFETs. IEEE Trans. Electron Dev. 2017, 64, 2142–2147. [Google Scholar] [CrossRef]

- del Alamo, J.A.; Lee, E.S. Stability and Reliability of Lateral GaN Power Field-Effect Transistors. IEEE Trans. Electron Dev. 2019, 66, 4578–4590. [Google Scholar] [CrossRef]

- Ambacher, O.; Smart, J.; Shealy, J.R.; Weimann, N.G.; Chu, K.; Murphy, M.; Schaff, W.J.; Eastman, L.F.; Dimitrov, R.; Wittmer, L.; et al. Two-dimensional electron gases induced by spontaneous and piezoelectric polarization charges in N- and Ga-face AlGaN/GaN heterostructures. J. Appl. Phys. 1999, 85, 3222–3233. [Google Scholar] [CrossRef] [Green Version]

- Ibbetson, J.P.; Fini, P.T.; Ness, K.D.; DenBaars, S.P.; Speck, J.S.; Mishra, U.K. Polarization effects, surface states, and the source of electrons in AlGaN/GaN heterostructure field effect transistors. Appl. Phys. Lett. 2000, 77, 250–252. [Google Scholar] [CrossRef]

- Higashiwaki, M.; Chowdhury, S.; Miao, M.-S.; Swenson, B.L.; Van de Walle, C.G.; Mishra, U.K. Distribution of donor states on etched surface of AlGaN/GaN heterostructures. J. Appl. Phys. 2010, 108, 063719. [Google Scholar] [CrossRef] [Green Version]

- Reiner, M.; Lagger, P.; Prechtl, G.; Steinschifter, P.; Pietschnig, R.; Pogany, D.; Ostermaier, C. Modification of “native” surface donor states in AlGaN/GaN MISHEMTs by fluorination: Perspective for defect engineering. In Proceedings of the IEEE International Electron Device Meeting (IEDM), Washington, DC, USA, 7–9 December 2015. [Google Scholar]

- Bakeroot, B.; You, S.; Wu, T.-L.; Hu, J.; Van Hove, M.; De Jaeger, B.; Geens, K.; Stoffels, S.; Decoutere, S. On the origin of the two-dimensional electron gas at AlGaN/GaN heterojunctions and its influence on recessed-gate metal-insulator-semiconductor high electron mobility transistors. J. Appl. Phys. 2014, 116, 134506. [Google Scholar] [CrossRef]

- Matys, M.; Stoklas, R.; Blaho, M.; Adamowicz, B. Origin of positive fixed charge at insulator/AlGaN interfaces and its control by AlGaN composition. Appl. Phys. Lett. 2017, 110, 243505. [Google Scholar] [CrossRef] [Green Version]

- Ťapajna, M.; Stoklas, R.; Gregušová, D.; Gucmann, F.; Hušeková, K.; Haščík, Š.; Fröhlich, K.; Tóth, L.; Pécz, B.; Brunner, F.; et al. Investigation of ‘surface donors’ in Al2O3/AlGaN/GaN metal-oxide-semiconductor heterostructures: Correlation of electrical, structural, and chemical properties. Appl. Surf. Sci. 2017, 426, 656–661. [Google Scholar] [CrossRef]

- Ber, E.; Osman, B.; Ritter, D. Measurement of the variable surface charge concentration in Gallium Nitride and implications on device modeling and physics. IEEE Trans. Electron Dev. 2019, 66, 2100–2105. [Google Scholar] [CrossRef] [Green Version]

- Esposto, M.; Krishnamoorthy, S.; Nathan, D.N.; Bajaj, S.; Hung, T.-H.; Rajan, S. Electrical properties of atomic layer deposited aluminum oxide on gallium nitride. Appl. Phys. Lett. 2011, 99, 133503. [Google Scholar] [CrossRef] [Green Version]

- Ganguly, S.; Verma, J.; Li, G.; Zimmermann, T.; Xing, H.; Jena, D. Presence and origin of interface charges at atomic-layer deposited Al2O3/III-nitride heterojunctions. Appl. Phys. Lett. 2011, 99, 193504. [Google Scholar] [CrossRef] [Green Version]

- Briere, M.A. Progress in silicon-based 600 V power GaN. Power Semicond. 2013, 4, 30. [Google Scholar]

- Ťapajna, M.; Drobný, J.; Gucmann, F.; Hušeková, K.; Gregušová, D.; Hashizume, T.; Kuzmík, J. Impact of oxide/barrier charge on threshold voltage instabilities in AlGaN/GaN metal-oxide-semiconductor heterostructures. Mater. Sci. Semicond. Process. 2019, 91, 356–361. [Google Scholar] [CrossRef]

- Ťapajna, M.; Kuzmík, J. Control of threshold voltage in GaN based metal–oxide–semiconductor high-electron mobility transistors towards the normally-off operation. Jpn. J. Appl. Phys. 2013, 52, 08JN08. [Google Scholar] [CrossRef]

- Harada, N.; Hori, Y.; Azumaishi, N.; Ohi, K.; Hashizume, T. Formation of recessed-oxide gate for normally-off AlGaN/GaN high Electron mobility transistors using selective electrochemical oxidation. Appl. Phys. Exp. 2011, 4, 021002. [Google Scholar]

- Gregušová, D.; Jurkovič, M.; Haščík, Š.; Blaho, M.; Seifertová, A.; Fedor, J.; Ťapajna, M.; Fröhlich, K.; Vogrinčič, P.; Liday, J.; et al.; et al. Adjustment of threshold voltage in AlN/AlGaN/GaN high-electron mobility transistors by plasma oxidation and Al2O3 atomic layer deposition overgrowth. Appl. Phys. Lett. 2014, 104, 013506. [Google Scholar] [CrossRef]

- Hung, T.; Park, P.S.; Krishnamoorthy, S.; Nath, D.N.; Rajan, S. Interface charge engineering for enhancement-mode GaN MISHEMTs. IEEE Electron Dev. Lett. 2014, 35, 312–314. [Google Scholar] [CrossRef]

- Blaho, M.; Gregušová, D.; Haščík, Š.; Jurkovič, M.; Ťapajna, M.; Fröhlich, K.; Dérer, J.; Carlin, J.-F.; Grandjean, N.; Kuzmík, J. Self-aligned normally-off metal-oxide-semiconductor n++GaN/InAlN/GaN high-electron mobility transistors. Phys. Status Solidi A 2015, 112, 1086–1090. [Google Scholar] [CrossRef]

- Maeda, N.; Hiroki, M.; Sasaki, S.; Harada, Y. High-temperature characteristics in recessed-gate AlGaN/GaN enhancement-mode heterostructure field effect transistors with enhanced-barrier structures. Jpn. J. Appl. Phys. 2013, 52, 08JN18. [Google Scholar] [CrossRef]

- Lee, Y.; Kao, T.; Merola, J.J.; Shen, S. A remote-oxygen-plasma surface treatment technique for III-nitride heterojunction field-effect transistors. IEEE Trans. Electron Dev. 2014, 61, 493–497. [Google Scholar] [CrossRef]

- Li, Z.; Chow, T.P. Channel scaling of hybrid GaN MOS-HEMTs. Solid State Electron. 2011, 56, 111–115. [Google Scholar] [CrossRef]

- Ikeda, N.; Tamura, R.; Kokawa, T.; Kambayashi, H.; Sato, Y.; Nomura, T.; Kato, S. Over 1.7 kV normally-off GaN hybrid MOS-HFETs with a lower on-resistance on a Si substrate. In Proceedings of the 23rd International Symposium on Power Semiconductor Devices and IC’s (ISPSD2011), San Diego, CA, USA, 23–26 May 2011; pp. 284–287. [Google Scholar]

- Freedsman, J.J.; Watanabe, A.; Egawa, T. Enhancement-mode Al2O3/InAlN/GaN MOS-HEMT on Si with high drain current density 0.84 A/mm and threshold voltage of +1.9 V. In Proceedings of the 72nd Device Research Conference, Santa Barbara, CA, USA, 22–25 June 2014; pp. 49–50. [Google Scholar]

- Yang, S.; Liu, S.; Liu, C.; Lu, Y.; Chen, K.J. Mechanisms of thermally induced threshold voltage instability in GaN-based heterojunction transistors. Appl. Phys. Lett. 2014, 105, 223508. [Google Scholar] [CrossRef]

- Deen, D.; Storm, D.; Meyer, D.; Katzer, D.S.; Bass, R.; Binari, S.; Gougousi, T. AlN/GaN HEMTs with high-κ ALD HfO2 or Ta2O5 gate insulation. Phys. Status Solidi C 2011, 8, 2420–2423. [Google Scholar] [CrossRef]

- Ťapajna, M.; Kuzmík, J.; Čičo, K.; Pogany, D.; Pozzovivo, G.; Strasser, G.; Abermann, S.; Bertagnolli, E.; Carlin, J.-F.; Grandjean, N.; et al. Interface states and trapping effects in Al2O3- and ZrO2/InAlN/AlN/GaN metal–oxide–semiconductor heterostructures. Jpn. J. Appl. Phys. 2009, 48, 090201. [Google Scholar] [CrossRef]

- Čičo, K.; Hušeková, K.; Ťapajna, M.; Gregušová, D.; Stoklas, R.; Kuzmík, J.; Carlin, J.-F.; Grandjean, N.; Pogany, D.; Fröhlich, K. Electrical properties of InAlN/GaN high electron mobility transistor with Al2O3, ZrO2, and GdScO3 gate dielectrics. J. Vac. Sci Technol. B 2011, 29, 01A808. [Google Scholar] [CrossRef]

- Kikkawa, T.; Makiyama, K.; Ohki, T.; Kanamura, M.; Imanishi, K.; Hara, N.; Joshin, K. High performance and high reliability AlGaN/GaN HEMTs. Phys. Stat. Solidi A 2009, 206, 1135–1144. [Google Scholar] [CrossRef]

- Yang, S.; Huang, S.; Schnee, M.; Zhao, Q.-T.; Schubert, J.; Chen, K.J. Fabrication and Characterization of Enhancement-Mode High-κ LaLuO3-AlGaN/GaN MIS-HEMTs. IEEE Trans. Electron Dev. 2013, 60, 3040–3046. [Google Scholar] [CrossRef]

- Hsu, C.; Shih, W.; Lin, Y.; Hsu, H.; Hsu, H.; Huang, Y.; Lin, T.; Wu, C.; Wu, W.; Ma, J.; et al. Improved linearity and reliability in GaN metal–oxide–semiconductor high-electron-mobility transistors using nanolaminate La2O3/SiO2 gate dielectric. Jpn. J. Appl. Phys. 2016, 55, 04EG04. [Google Scholar] [CrossRef]

- Zhou, H.; Makiyama, K.; Ohki, T.; Kanamura, M.; Imanishi, K.; Hara, N.; Joshin, K. High-performance InAlN/GaN MOSHEMTs enabled by atomic layer epitaxy MgCaO as gate dielectric. IEEE Electron Dev. Lett. 2016, 37, 556–559. [Google Scholar] [CrossRef]

- Huang, M.L.; Chang, Y.C.; Chang, Y.H.; Lin, T.D.; Kwo, J.; Hong, M. Energy-band parameters of atomic layer deposited Al2O3 and HfO2 on InxGa1−xAs. Appl. Phys. Lett. 2009, 94, 052106. [Google Scholar] [CrossRef]

- Yatabe, Z.; Hori, Y.; Kim, S.; Hashizume, T. Effects of Cl2-based inductively coupled plasma etching of AlGaN on interface properties of Al2O3/AlGaN/GaN heterostructures. Appl. Phys. Express 2013, 6, 016502. [Google Scholar] [CrossRef]

- Ozaki, S.; Makiyama, K.; Ohki, T.; Okamoto, N.; Kaneki, S.; Nishiguchi, K.; Hara, N.; Hashizume, T. Effects of air annealing on DC characteristics of InAlN/GaN MOS high-electron-mobility transistors using atomic-layer-deposited Al2O3. Appl. Phys. Express 2017, 10, 061001. [Google Scholar] [CrossRef]

- Ťapajna, M.; Válik, L.; Gucmann, F.; Gregušová, D.; Fröhlich, K.; Haščík, Š.; Dobročka, E.; Tóth, L.; Pécz, B.; Kuzmík, J. Low-temperature atomic layer deposition-grown Al2O3 gate dielectric for GaN/AlGaN/GaN MOS HEMTs: Impact of deposition conditions on interface state density. J. Vac. Sci. Technol. B 2017, 35, 01A107. [Google Scholar] [CrossRef] [Green Version]

- Im, K.-S.; Ha, J.-B.; Kim, K.-W.; Lee, J.-S.; Kim, D.-S.; Hahm, S.-H.; Lee, J.-H. Normally off GaN MOSFET based on AlGaN/GaN heterostructure with extremely high 2DEG density grown on silicon substrate. IEEE Electron Device Lett. 2010, 31, 192–194. [Google Scholar]

- Kim, K.-W.; Jung, S.-D.; Kim, D.-S.; Kang, H.-S.; Im, K.-S.; Oh, J.-J.; Ha, J.-B.; Shin, J.-K.; Lee, J.H. Effects of TMAH treatment on device performance of normally off Al2O3/GaN MOSFET. IEEE Electron Device Lett. 2011, 32, 1376–1378. [Google Scholar] [CrossRef]

- Wang, Y.; Wang, M.; Xie, B.; Wen, C.P.; Wang, J.; Hao, Y.; Wu, W.; Chen, K.J.; Shen, B. High-performance normally-off Al2O3/GaN MOSFET using a wet etching-based gate recess technique. IEEE Electron Device Lett. 2013, 34, 1370–1372. [Google Scholar] [CrossRef]

- Wang, M.; Wang, Y.; Zhang, C.; Xie, B.; Wen, C.P.; Wang, J.; Hao, Y.; Wu, W.; Chen, K.J.; Shen, B. 900 V/1.6 mΩ cm2 normally off Al2O3/GaN MOSFET on silicon substrate. IEEE Trans. Electron Dev. 2014, 61, 2035–2040. [Google Scholar] [CrossRef]

- Asahara, R.; Nozaki, M.; Yamada, T.; Ito, J.; Nakazawa, S.; Ishida, M.; Ueda, T.; Yoshigoe, A.; Hosoi, T.; Shimura, T.; et al. Effect of nitrogen incorporation into Al-based gate insulators in AlON/AlGaN/GaN metal–oxide–semiconductor structures. Appl. Phys. Express 2016, 9, 101002. [Google Scholar] [CrossRef] [Green Version]

- Kikuta, D.; Itoh, K.; Narita, T.; Mori, T. Al2O3/SiO2 nanolaminate for a gate oxide in a GaN-based MOS device. J. Vac. Sci. Technol. A 2017, 35, 01B122. [Google Scholar]

- Lee, J.-G.; Kim, H.-S.; Seo, K.-S.; Cho, C.-H.; Cha, H.-Y. High quality PECVD SiO2 process for recessed MOS-gate of AlGaN/GaN-on-Si metal–oxide–semiconductor heterostructure field-effect transistors. Solid State Electron. 2016, 122, 32–36. [Google Scholar] [CrossRef]

- Khan, M.A.; Hu, X.; Sumin, G.; Lunev, A.; Yang, J.; Gaska, R.; Shur, M.S. Effects of air annealing on DC characteristics of InAlN/GaN MOS high-electron-mobility transistors using atomic-layer-deposited Al2O3. IEEE Electron Device Lett. 2000, 21, 63–65. [Google Scholar] [CrossRef]

- Kambayashi, H.; Satoh, Y.; Kokawa, T.; Ikeda, N.; Nomura, T.; Kato, S. High field-effect mobility normally-off AlGaN/GaN hybrid MOS-HFET on Si substrate by selective area growth technique. Solid State Electron. 2011, 56, 163–167. [Google Scholar] [CrossRef]

- Hua, M.; Zhang, Z.; Wei, J.; Lei, J.; Tang, G.; Fu, K.; Cai, Y.; Zhang, B.; Chen, K.J. Integration of LPCVD SiNx Gate Dielectric with Recessed-gate E-mode GaN MIS-FETs: Toward High Performance, High Stability and Long TDDB Lifetime. In Proceedings of the International Electron Device Meeting 2016 (IEDM 2016), San Francisco, CA, USA, 3–7 December 2016; pp. 260–263. [Google Scholar]

- Hua, M.; Wei, J.; Bao, Q.; Zhang, Z.; Zheng, Z.; Chen, K.J. Dependence of VTH stability on gate-bias under reverse-bias stress in E-mode GaN MIS-FET. IEEE Electron Dev. Lett. 2018, 39, 413–416. [Google Scholar] [CrossRef]

- Meneghesso, G.; Meneghini, M.; Bisi, D.; Rossetto, I.; Wu, T.-L.; Van Hove, M.; Marcon, D.; Stoffels, S.; Decoutere, S.; Zanoni, E. Trapping and reliability issues in GaN-based MIS HEMTs with partially recessed gate. Microelectron. Reliab. 2016, 58, 151–157. [Google Scholar] [CrossRef]

- Hashizume, T.; Ootomo, S.; Inagaki, T.; Hasegawa, H. Surface passivation of GaN and GaN/AlGaN heterostructures by dielectric films and its application to insulated-gate heterostructure transistors. J. Vac. Sci. Technol. B 2003, 21, 1828–1838. [Google Scholar] [CrossRef] [Green Version]

- Van Hove, M.; Kang, X.; Stoffels, S.; Wellekens, D.; Ronchi, N.; Venegas, R.; Geens, K.; Decoutere, S. Fabrication and performance of Au-free AlGaN/GaN-on-silicon power devices with Al2O3 and Si3N4/Al2O3 gate dielectrics. IEEE Trans. Electron Dev. 2013, 60, 3071–3078. [Google Scholar] [CrossRef]

- Yang, S.; Tang, Z.; Wong, K.-Y.; Lin, Y.-S.; Lu, Y.; Huang, S.; Chen, K.J. Mapping of interface traps in high-performance Al2O3/AlGaN/GaN MIS-heterostructures using frequency- and temperature-dependent C-V techniques. In Proceedings of the 2013 IEEE International Electron Devices Meeting (IEDM), Washington, DC, USA, 9–11 December 2013. [Google Scholar]

- Zhu, J.; Ma, X.-H.; Xie, Y.; Hou, B.; Chen, W.-W.; Zhang, J.-C.; Hao, Y. Improved interface and transport properties of AlGaN/GaN MIS-HEMTs with PEALD-grown AlN gate dielectric. IEEE Trans. Electron Dev. 2015, 62, 512–518. [Google Scholar]

- Hashizume, T.; Kaneki, S.; Oyobiki, T.; Ando, Y.; Sasaki, S.; Nishiguchi, K. Effects of postmetallization annealing on interface properties of Al2O3/GaN structures. Appl. Phys. Exp. 2018, 11, 124102. [Google Scholar] [CrossRef]

- Fritsch, J.; Sankey, O.F.; Schmidt, K.E.; Page, J.B. Ab initio calculation of the stoichiometry and structure of the (0001) surfaces of GaN and AlN. Phys. Rev. B 1998, 57, 15360. [Google Scholar] [CrossRef]

- Eller, B.S.; Yang, J.; Nemanich, R.J. Electronic surface and dielectric interface states on GaN and AlGaN. J. Vacuum Sci. Technol. A 2013, 31, 050807. [Google Scholar] [CrossRef]

- Ťapajna, M.; Kuzmík, J. A comprehensive analytical model for threshold voltage calculation in GaN based metal-oxide-semiconductor high-electron-mobility transistors. Appl. Phys. Lett. 2012, 100, 113509. [Google Scholar] [CrossRef]

- Hasegawa, H.; Ohno, H. Unified disorder induced gap state model for insulator–semiconductor and metal–semiconductor interfaces. J. Vac. Sci. Technol. B 1986, 4, 1130–1138. [Google Scholar] [CrossRef]

- Yatabe, Z.; Asubar, J.T.; Hashizume, T. Insulated gate and surface passivation structures for GaN-based power transistors. J. Phys. D Appl. Phys. 2016, 49, 393001. [Google Scholar] [CrossRef]

- Jackson, C.M.; Arehart, A.R.; Cinkilic, E.; McSkimming, B.; Speck, J.S.; Ringel, S.A. Interface trap characterization of atomic layer deposition Al2O3/GaN metal-insulator-semiconductor capacitors using optically and thermally based deep level spectroscopies. J. Appl. Phys. 2013, 113, 204505. [Google Scholar] [CrossRef]

- Capriotti, M.; Lagger, P.; Fleury, C.; Oposich, M.; Bethge, O.; Ostermaier, C.; Strasser, G.; Pogany, D. Modeling small-signal response of GaN-based metal-insulator- semiconductor high electron mobility transistor gate stack in spill-over regime: Effect of barrier resistance and interface states. J. Appl. Phys. 2015, 117, 024506. [Google Scholar] [CrossRef] [Green Version]

- Miczek, M.; Mizue, C.; Hashizume, T.; Adamowicz, B. Effects of interface states and temperature on the C-V behavior of metal/insulator/AlGaN/GaN heterostructure capacitors. J. Appl. Phys. 2008, 103, 104510. [Google Scholar] [CrossRef] [Green Version]

- Matys, M.; Kaneki, S.; Nishiguchi, K.; Adamowicz, B.; Hashizume, T. Disorder induced gap states as a cause of threshold voltage instabilities in Al2O3/AlGaN/GaN metal-oxide-semiconductor high-electron-mobility transistors. J. Appl. Phys. 2017, 122, 224504. [Google Scholar] [CrossRef]

- Hasegawa, H.; Inagaki, T.; Ootomo, S.; Hashizume, T. Mechanisms of current collapse and gate leakage currents in AlGaN/GaN heterostructure field effect transistors. J. Vac. Sci. Technol. B 2003, 21, 1844–1855. [Google Scholar] [CrossRef] [Green Version]

- Heiman, F.P.; Warfield, G. The effects of oxide traps on the MOS capacitance. IEEE Trans. Electron Dev. 1965, 12, 167–178. [Google Scholar] [CrossRef] [Green Version]

- Shluger, A. Defects in oxides in electronic devices. In Handbook of Materials Modeling; Andreoni, W., Yip, S., Eds.; Springer Nature: Cham, Switzerland, 2019. [Google Scholar]

- Choi, M.; Lyons, J.L.; Janotti, A.; Van de Walle, C.G. Impact of carbon and nitrogen impurities in high-κ dielectrics on metal-oxide semiconductor devices. Appl. Phys. Lett. 2013, 102, 142902. [Google Scholar] [CrossRef] [Green Version]

- Choi, M.; Janotti, A.; Van de Walle, C.G. Native point defects and dangling bonds in α-Al2O3. J. Appl. Phys. 2013, 113, 044501. [Google Scholar] [CrossRef]

- Sun, X.; Saadat, O.I.; Chang-Liao, K.S.; Palacios, T.; Cui, S.; Ma, T.P. Study of gate oxide traps in HfO2/AlGaN/GaN metal-oxide-semiconductor high-electron-mobility transistors by use of ac transconductance method. Appl. Phys. Lett. 2013, 102, 103504. [Google Scholar] [CrossRef] [Green Version]

- Warren, W.; Rong, F.C.; Poindexter, E.; Gerardi, G.; Kanicki, J. Structural identification of the silicon and nitrogen dangling-bond centers in amorphous silicon nitride. J. Appl. Phys. 1991, 70, 346–354. [Google Scholar] [CrossRef]

- Zhu, J.; Hou, B.; Chen, L.; Zhu, Q.; Ling, Y.; Xiaowei, Z.; Zhang, P.; Ma, X.; Hao, Y. Threshold voltage shift and interface/border trapping mechanism in Al2O3/AlGaN/GaN MOS-HEMTs. In Proceedings of the 2018 IEEE International Reliability Physics Symposium (IRPS), Burlingame, CA, USA, 11–15 March 2018. [Google Scholar]

- Henry, C.H.; Lang, D.V. Nonradiative capture and recombination by multiphonon emission in GaAs and GaP. Phys. Rev. B 1977, 15, 989–1016. [Google Scholar] [CrossRef]

- Lax, M. Cascade capture of electrons in solids. Phys. Rev. 1960, 119, 1502–1523. [Google Scholar] [CrossRef]

- Kirton, M.J.; Uren, M.J. Noise in solid-state microstructures: A new perspective on individual defects, interface states and low-frequency (I/f) noise. Adv. Phys. 1989, 38, 367–468. [Google Scholar] [CrossRef]

- Grasser, T. Stochastic charge trapping in oxides: From random telegraph noise to bias temperature instabilities. Microelectron. Reliab. 2012, 52, 39–70. [Google Scholar] [CrossRef]

- Taoka, N.; Kubo, T.; Yamada, T.; Egawa, T.; Shimizu, M. Experimental evidence of the existence of multiple charged states at Al2O3/GaN interfaces. Semicond. Sci. Technol. 2019, 34, 025009. [Google Scholar] [CrossRef]

- Wu, T.-L.; Marcon, D.; Ronchi, N.; Bakeroot, B.; You, S.; Stoffels, S.; Van Hove, M.; Bisi, D.; Meneghini, M.; Groeseneken, G.; et al. Analysis of slow de-trapping phenomena after a positive gate bias on AlGaN/GaN MIS-HEMTs with in-situ Si3N4/Al2O3 bilayer gate dielectrics. Solid State Electron. 2015, 103, 127–130. [Google Scholar] [CrossRef]

- Meneghini, M.; Rossetto, I.; Bisi, D.; Ruzzarin, M.; Van Hove, M.; Stoffels, S.; Wu, T.-L.; Marcon, D.; Decoutere, S.; Meneghesso, G.; et al. Negative bias-induced threshold voltage instability in GaN-on-Si power HEMTs. IEEE Electron Dev. Lett. 2016, 37, 474–477. [Google Scholar] [CrossRef]

- Dalcanale, S.; Meneghini, M.; Tajalli, A.; Rossetto, I.; Ruzzarin, M.; Zanoni, E.; Meneghesso, G. GaN-based MIS-HEMTs: Impact of cascode-mode high temperature source current stress on NBTI shift. In Proceedings of the 2017 IEEE International Reliability Physics Symposium (IRPS), Monterey, CA, USA, 2–6 April 2017. [Google Scholar]

- Chini, A.; Iucolano, F. Evolution of on-resistance (RON) and threshold voltage (VTH) in GaN HEMTs during switch-mode operation. Mat. Sci. Semicond. Proc. 2018, 78, 127–131. [Google Scholar] [CrossRef]

- Ťapajna, M.; Válik, L.; Gregušová, D.; Fröhlich, K.; Gucmann, F.; Hashizume, T.; Kuzmík, J. Threshold voltage instabilities in AlGaN/GaN MOS-HEMTs with ALD-grown Al2O3 gate dielectrics: Relation to distribution of oxide/semiconductor interface state density. In 2016 11th International Conference on Advanced Semiconductor Devices & Microsystems (ASDAM), Proceedings of the IEEE, Smolenice, Slovakia, 13–16 November 2016; IEEE: Smolenice, Slovakia, 2016; pp. 1–4. [Google Scholar]

- Fagerlind, M.; Allerstam, F.; Sveinbjörnsson, E.Ö.; Rorsman, N.; Kakanakova-Georgieva, A.; Lundskog, A.; Forsberg, U.; Janzén, E. Investigation of the interface between silicon nitride passivations and AlGaN/AlN/GaN heterostructures by C(V) characterization of metal-insulator-semiconductor heterostructure capacitors. J. Appl. Phys. 2010, 108, 014508. [Google Scholar] [CrossRef] [Green Version]

- Huang, S.; Yang, S.; Roberts, J.; Chen, K.J. Threshold voltage instability in Al2O3/GaN/AlGaN/GaN metal–insulator–semiconductor high-electron mobility transistors. Jpn. J. Appl. Phys. 2011, 50, 110202. [Google Scholar] [CrossRef]

- Ťapajna, M.; Čičo, K.; Kuzmík, J.; Pogany, D.; Pozzovivo, G.; Strasser, G.; Carlin, J.-F.; Grandjean, N.; Fröhlich, K. Thermally induced voltage shift in capacitance–voltage characteristics and its relation to oxide/semiconductor interface states in Ni/Al2O3/InAlN/GaN heterostructures. Semicond. Sci. Technol. 2009, 24, 035008. [Google Scholar] [CrossRef]

- Winzer, A.; Schuster, M.; Hentschel, R.; Ocker, J.; Merkel, U.; Jahn, A.; Wachowiak, A.; Mikolajick, T. Analysis of threshold voltage instability in AlGaN/GaN MISHEMTs by forward gate voltage stress pulses. Phys. Status Solidi A 2016, 213, 1246–1251. [Google Scholar] [CrossRef]

- Reisinger, H.; Grasser, T.; Gustin, W.; Schluandnder, C. The statistical analysis of individual defects constituting NBTI and its implications for modeling DC- and AC stress. In Proceedings of the 2010 IEEE International Reliability Physics Symposium (IRPS), Anaheim, CA, USA, 2–6 May 2010. [Google Scholar]

- Ostermaier, C.; Lagger, P.; Prechtl, G.; Grill, A.; Grasser, T.; Pogany, D. Dynamics of carrier transport via AlGaN barrier in AlGaN/GaN MIS-HEMTs. Appl. Phys. Lett. 2017, 110, 173502. [Google Scholar] [CrossRef]

- Lagger, P.; Steinschifter, P.; Reiner, M.; Stadtmüller, M.; Denifl, G.; Naumann, A.; Mueller, J.; Wilde, L.; Pogany, D.; Ostermaier, C. Role of the dielectric for the charging dynamics of the dielectric/barrier interface in AlGaN/GaN based metal-insulator-semiconductor structures under forward gate bias stress. Appl. Phys. Lett. 2014, 105, 033512. [Google Scholar] [CrossRef]

- Wu, C.; Han, P.-C.; Luc, Q.H.; Hsu, C.Y.; Hsieh, T.-E.; Wang, H.-C.; Lin, Y.-K.; Chang, P.-C.; Lin, Y.-C.; Chang, E.Y. Normally-OFF GaN MIS-HEMT with F− doped gate insulator using standard ion implantation. IEEE J. Electron Dev. Soc. 2018, 6, 893–899. [Google Scholar] [CrossRef]

- Kikkawa, T.; Hosoda, T.; Imanishi, K.; Shono, K.; Itabashi, K.; Ogino, T.; Miyazaki, Y.; Mochizuki, A.; Kiuchi, K.; Kanamura, M.; et al. 600 V JEDEC-qualified highly reliable GaN HEMTs on Si substrates. In Proceedings of the 2014 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 15–17 December 2014. [Google Scholar]

- Kaczer, B.; Grasser, T.; Roussel, P.J.; Martin-Martinez, J.; O’Connor, R.; O’Sullivan, B.J.; Groeseneken, G. Ubiquitous relaxation in BTI stressing-New evaluation and insights. In Proceedings of the 2008 IEEE International Reliability Physics Symposium, Phoenix, AZ, USA, 24 April–1 May 2008; pp. 20–27. [Google Scholar]

- Bisi, D.; Chan, S.H.; Liu, X.; Yeluri, R.; Keller, S.; Meneghini, M.; Meneghesso, G.; Zanoni, E.; Mishra, U.K. On trapping mechanisms at oxide-traps in Al2O3/GaN metal-oxide-semiconductor capacitors. Appl. Phys. Lett. 2016, 108, 112104. [Google Scholar] [CrossRef]

- Acurio, E.; Crupi, F.; Magnone, P.; Trojman, L.; Meneghesso, G.; Iucolano, F. On recoverable behavior of PBTI in AlGaN/GaN MOS-HEMT. Solid State Electron. 2017, 132, 49–56. [Google Scholar] [CrossRef]

- Iucolano, F.; Parisi, A.; Reina, S.; Meneghesso, G.; Chini, A. Study of threshold voltage instability in E-mode GaN MOS-HEMTs. Phys. Stat. Solidi C 2016, 13, 321–324. [Google Scholar] [CrossRef]

- Chini, A.; Iucolano, F. Experimental and numerical analysis of VTH and RON drifts in E-mode GaN HEMTs during switch-mode operation. Mat. Sci. Semicond. Proc. 2019, 98, 77–80. [Google Scholar] [CrossRef]

- Sang, F.; Wang, M.; Zhang, C.; Tao, M.; Xie, B.; Wen, C.P.; Wang, J.; Hao, Y.; Wu, W.; Shen, B. Investigation of the threshold voltage drift in enhancement mode GaN MOSFET under negative gate bias stress. Jpn. J. Appl. Phys. 2015, 54, 044101. [Google Scholar] [CrossRef]

- Lelis, A.J.; Habersat, D.; Green, R.; Ogunniyi, A.; Gurfinkel, M.; Suehle, J.; Goldsman, N. Time dependence of bias-stress-induced SiC Mosfet threshold-voltage instability measurements. IEEE Trans. Electron Dev. 2008, 55, 1835–1840. [Google Scholar] [CrossRef]

- Hua, M.; Qian, Q.; Wei, J.; Zhang, Z.; Tang, G.; Chen, K.J. Bias temperature instability of normally-off GaN MIS-FET with low-pressure chemical vapor deposition SiNx gate dielectric. Phys. Stat. Solidi A 2018, 215, 1700641. [Google Scholar] [CrossRef]

- He, J.; Hua, M.; Zhang, Z.; Chen, K.J. Performance and VTH stability in E-mode GaN fully recessed MIS-FETs and partially recessed MIS-HEMTs with LPCVD-SiNx/PECVD-SiNx gate dielectric stack. IEEE Trans. Electron Dev. 2018, 65, 3185–3191. [Google Scholar] [CrossRef]

- Killat, N.; Ťapajna, M.; Faqir, M.; Palacios, T.; Kuball, M. Evidence for impact ionisation in AlGaN/GaN HEMTs with InGaN back-barrier. Electron. Lett. 2011, 47, 405–406. [Google Scholar] [CrossRef] [Green Version]

- Degraeve, R.; Kaczer, R.B.; Groeseneken, G. Degradation and breakdown in thin oxide layers: Mechanisms, models and reliability prediction. Microelectron. Reliab. 1999, 39, 1445–1460. [Google Scholar] [CrossRef]

- Hua, M.; Wei, J.; Bao, Q.; He, J.; Zhang, Z.; Zheng, Z.; Lei, J.; Chen, K.J. Reverse-bias stability and reliability of hole-barrier-free E-mode LPCVD-SiNx/GaN MIS-FETs. In Proceedings of the 2017 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2–6 December 2017. [Google Scholar]

- Hua, M.; Cai, X.; Yang, S.; Zhang, Z.; Zheng, Z.; Wang, N.; Chen, J.K. Enhanced gate reliability in GaN MIS-FETs by converting the GaN channel into crystalline gallium oxynitride. ACS Appl. Electron. Mat. 2019, 1, 642–648. [Google Scholar] [CrossRef]

- Hua, M.; Yang, S.; Zheng, Z.; Wei, J.; Zhang, Z.; Chen, J.K. Effects of Substrate termination on reverse-bias stress reliability of normally-off lateral GaN-on-Si MIS-FETs. In Proceedings of the 31st International Symposium on Power Semiconductor Devices & ICs, Shanghai, China, 19–23 May 2019. [Google Scholar]

- Moens, P.; Liu, C.; Banerjee, A.; Vanmeerbeek, P.; Coppens, P.; Ziad, H.; Constant, A.; Li, Z.; De Vleeschouwer, H.; Roig-Guitart, J.; et al.; et al. An industrial process for 650V rated GaN-on-Si power devices using in-situ SiN as a gate dielectric. In Proceedings of the 2014 IEEE 26th International Symposium on Power Semiconductor Devices & IC’s (ISPSD), Waikoloa, HI, USA, 15–19 June 2014; pp. 374–377. [Google Scholar]

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2020 by the author. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Ťapajna, M. Current Understanding of Bias-Temperature Instabilities in GaN MIS Transistors for Power Switching Applications. Crystals 2020, 10, 1153. https://doi.org/10.3390/cryst10121153

Ťapajna M. Current Understanding of Bias-Temperature Instabilities in GaN MIS Transistors for Power Switching Applications. Crystals. 2020; 10(12):1153. https://doi.org/10.3390/cryst10121153

Chicago/Turabian StyleŤapajna, Milan. 2020. "Current Understanding of Bias-Temperature Instabilities in GaN MIS Transistors for Power Switching Applications" Crystals 10, no. 12: 1153. https://doi.org/10.3390/cryst10121153

APA StyleŤapajna, M. (2020). Current Understanding of Bias-Temperature Instabilities in GaN MIS Transistors for Power Switching Applications. Crystals, 10(12), 1153. https://doi.org/10.3390/cryst10121153