Effect of Thickness of InP Nucleation Layer on the Two-Step Growth of InP on Si(001)

Abstract

:1. Introduction

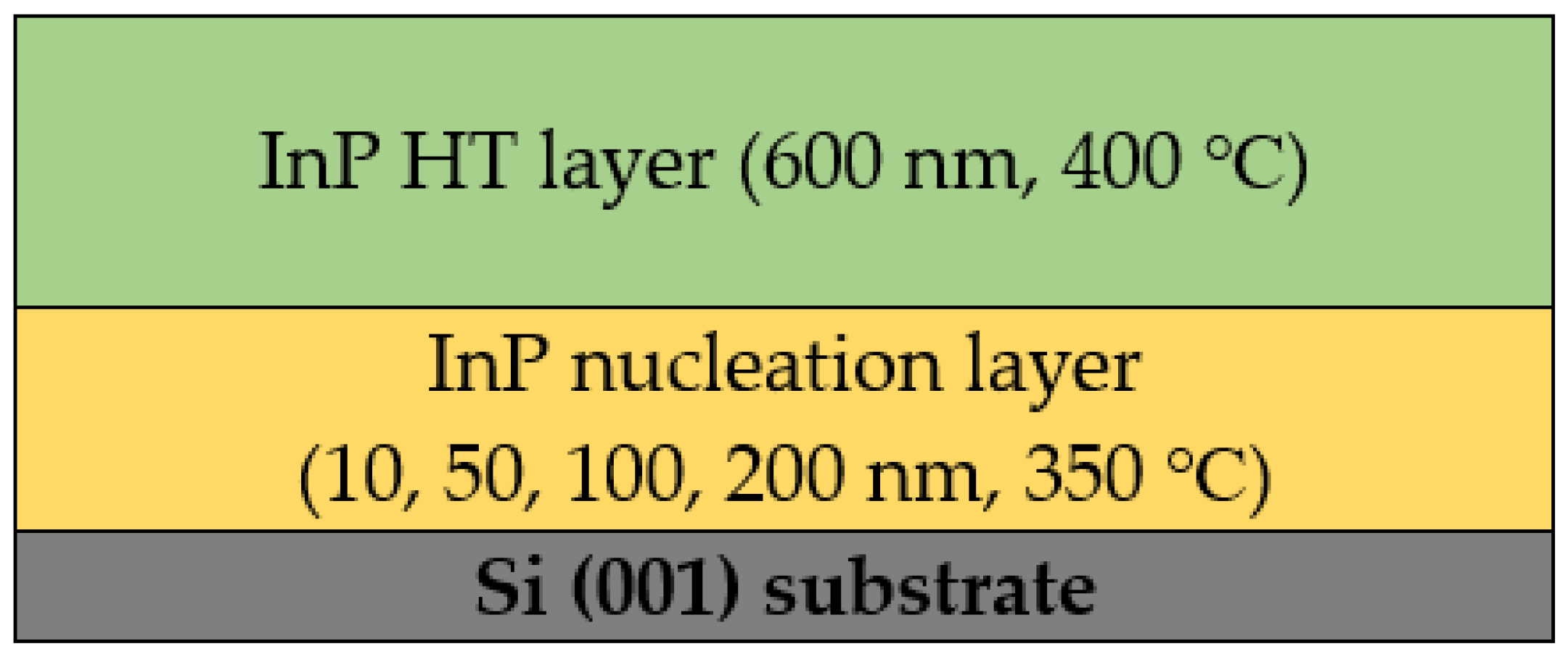

2. Experimental Section

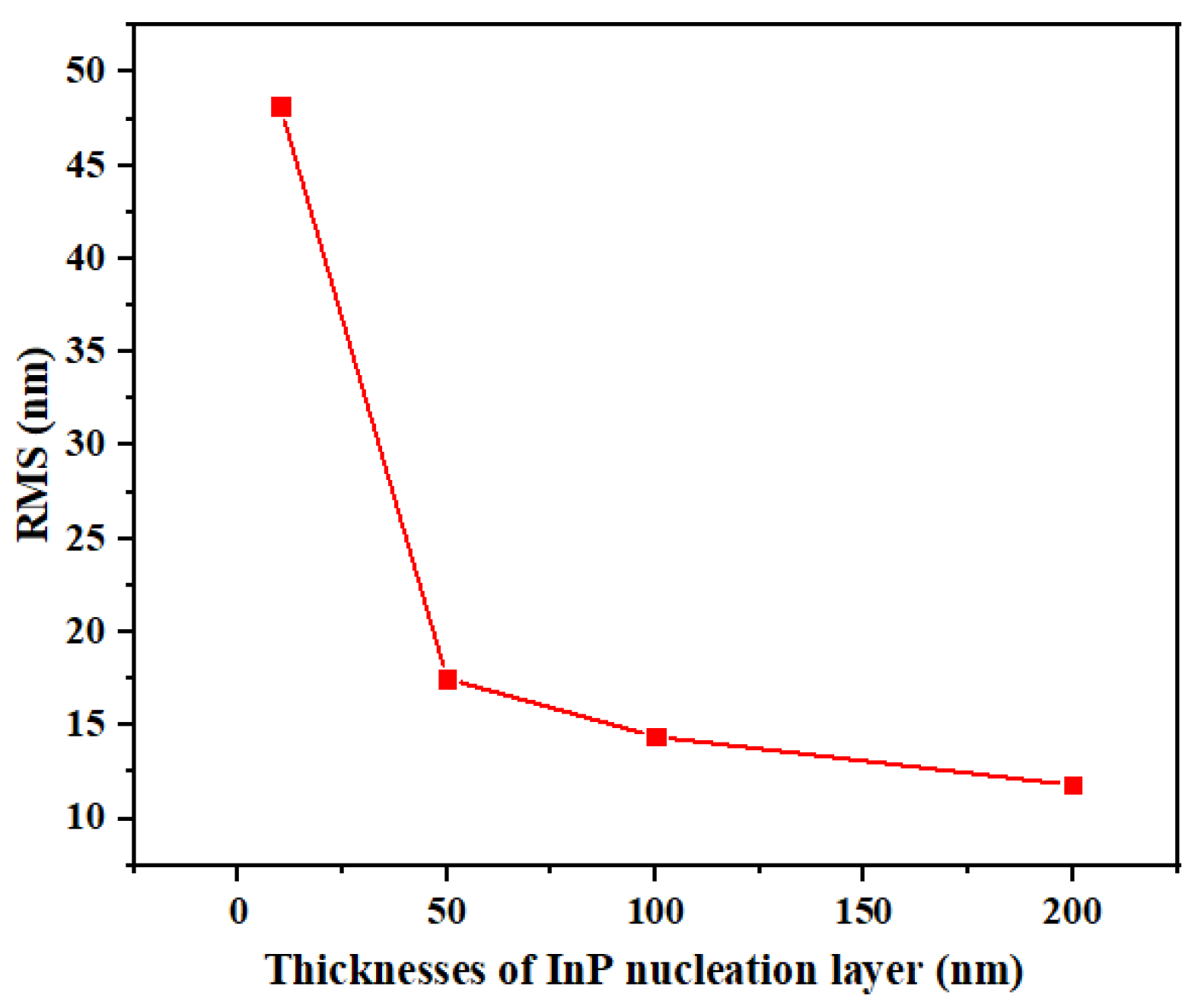

3. Results and Discussion

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Hiraki, T.; Aihara, T.; Hasebe, K.; Fujiia, T.; Takedaa, K.; Nishia, H.; Kakitsukaa, T.; Fukudaa, H.; Tsuchizawaa, T.; Matsuoa, S. Heterogeneous Integration of III-V Semiconductors on Si Photonics Platform. ECS Trans. 2018, 86, 11–16. [Google Scholar] [CrossRef]

- Hancock, T.M.; Demmin, J.C. Heterogeneous and 3D Integration at DARPA. In Proceedings of the 2019 International 3D Systems Integration Conference (3DIC), Sendai, Japan, 8–10 October 2019; pp. 1–4. [Google Scholar]

- Dallesasse, J.M.; Carlson, J.A.; Ganjoo, M.; Espenhahn, L. Heterogeneous Integration for Silicon Photonic Systems: Challenges and Approaches. In Proceedings of the 2021 5th IEEE Electron Devices Technology & Manufacturing Conference (EDTM), Chengdu, China, 8–11 April 2021; pp. 1–3. [Google Scholar]

- Green, D.S.; Dohrman, C.L.; Demmin, J.; Zheng, Y.; Chang, T.H. A Revolution on the Horizon from DARPA: Heterogeneous Integration for Revolutionary Microwave/Millimeter-Wave Circuits at DARPA: Progress and Future Directions. IEEE Microw. Mag. 2017, 18, 44–59. [Google Scholar] [CrossRef]

- Park, J.S.; Tang, M.; Chen, S.; Liu, H. Heteroepitaxial Growth of III-V Semiconductors on Silicon. Crystals 2020, 10, 1163. [Google Scholar] [CrossRef]

- Kazior, T.E. Beyond CMOS: Heterogeneous integration of III-V devices, RF MEMS and other dissimilar materials/devices with Si CMOS to create intelligent microsystems. Philos. Trans. R. Soc. A-Math. Phys. Eng. Sci. 2014, 372, 20130105. [Google Scholar] [CrossRef] [Green Version]

- Weimann, N.G.; Johansen, T.K.; Stoppel, D.; Matalla, M.; Brahem, M.; Nosaeva, K.; Boppel, S.; Volkmer, N.; Ostermay, I.; Krozer, V.; et al. Transferred-Substrate InP/GaAsSb heterojunction bipolar transistor technology with fmax~0.53 THz. IEEE Trans. Electron Devices 2018, 65, 3704–3710. [Google Scholar] [CrossRef] [Green Version]

- Weimann, N. InP HBT technology for THz applications. In Proceedings of the 2020 IEEE International Symposium on Radio-Frequency Integration Technology (RFIT), Hiroshima, Japan, 2–4 September 2020; pp. 190–192. [Google Scholar]

- Hossain, M.; Shivan, T.; Hrobak, M.; Al-Sawaf, T.; Stoppel, D.; Yacoub, H.; Weimann, N.; Heinrich, W.; Krozer, V. A W-Band Transceiver Chip for Future 5G Communications in InP-DHBT Technology. In Proceedings of the 2020 15th European Microwave Integrated Circuits Conference (EuMIC), Utrecht, The Netherlands, 10–15 January 2021; pp. 193–196. [Google Scholar]

- Liu, W.K.; Lubyshev, D.; Fastenau, J.M.; Wu, Y.; Bulsara, M.T.; Fitzgerald, E.A.; Urteaga, M.; Ha, W.; Bergman, J.; Brar, B.; et al. Monolithic integration of InP-based transistors on Si substrates using MBE. J. Cryst. Growth 2009, 311, 1979–1983. [Google Scholar] [CrossRef]

- Kraemer, T.; Ostermay, I.; Jensen, T.; Johansen, T.K.; Schmueckle, F.; Thies, A.; Krozer, V.; Heinrich, W.; Krueger, O.; Traenkle, G.; et al. lnP-DHBT-on-BiCMOS Technology with fT/fmax of 400/3S0 GHz for heterogeneous integrated millimeter wave sources. IEEE Trans. Electron. Devices 2013, 60, 2209–2222. [Google Scholar] [CrossRef]

- Gutierrez-Aitken, A.; Chang-Chien, P.; Scott, D.; Hennig, K.; Kaneshiro, E.; Nam, P.; Cohen, N.; Ching, D.; Thai, K.; Oyama, B.; et al. Advanced Heterogeneous Integration of InP HBT and CMOS Si Technologies. In Proceedings of the 2010 IEEE Compound Semiconductor Integrated Circuit Symposium, Monterey, CA, USA, 3–6 October 2010. [Google Scholar]

- Li, Q.; Lau, K.M. Epitaxial growth of highly mismatched III-V materials on (001) silicon for electronics and optoelectronics. Prog. Cryst. Growth Charact. Mater. 2017, 63, 105–120. [Google Scholar] [CrossRef] [Green Version]

- Li, J.; Miao, G.; Zhang, Z.; Zeng, Y. Experiments and analysis of the two-step growth of InGaAs on GaAs substrate. Crystengcomm 2015, 17, 5808–5813. [Google Scholar] [CrossRef]

- Okumura, S.; Suzuki, R.; Tsunoda, K.; Nishino, H.; Sugiyama, M. Suppression of Three-Dimensional Pit Formation of InAs on GaSb (001) by Two-Step MBE. In Proceedings of the 2019 Compound Semiconductor Week (CSW), Nara, Japan, 19–23 May 2019. [Google Scholar]

- Nakamura, S.; Harada, Y.; Seno, M. Novel metalorganic chemical vapor deposition system for GaN growth. Appl. Phys. Lett. 1991, 58, 2021. [Google Scholar] [CrossRef]

- Nakamura, S. GaN growth using GaN buffer layer. Jpn. J. Appl. Phys. 1991, 30, L1705. [Google Scholar] [CrossRef]

- Waltereit, P.; Poblenz, C.; Rajan, S.; Wu, F.; Mishra, U.K.; Speck, J.S. Structural properties of GaN buffer layers on 4H-SiC (0001) grown by plasma-assisted molecular beam epitaxy for high electron mobility transistors. Jpn. J. Appl. Phys. 2004, 43, L1520. [Google Scholar] [CrossRef]

- Kim, Y.H.; Lee, J.Y.; Noh, Y.G.; Kim, M.D.; Kwon, Y.J.; Oh, J.E.; Gronsky, R. Effect of two-step growth on the heteroepitaxial growth of InSb thin film on Si (001) substrate: A transmission electron microscopy study. Appl. Phys. Lett. 2006, 89, 031919. [Google Scholar] [CrossRef]

- Cho, Y.-D.; Lee, I.-G.; Kim, S.-W.; Jun, D.-H.; Choi, I.-H.; Kwon, H.-M.; Shin, C.-S.; Park, K.-H.; Park, W.-K.; Kim, D.-H.; et al. Two-Step Growth of Epitaxial InP Layers by Metal Organic Chemical Vapor Deposition. J. Nanosci. Nanotechnol. 2016, 16, 5168–5172. [Google Scholar] [CrossRef] [PubMed]

- Shin, K.W.; Kim, H.; Kim, J.; Yang, C.; Lee, S.; Yoon, E. The effects of low temperature buffer layer on the growth of pure Ge on Si(001). Thin Solid Films 2010, 518, 6496–6499. [Google Scholar] [CrossRef]

- Barrett, C.S.C.; Martin, T.P.; Bao, X.Y.; Kennon, E.L.; Gutierrez, L.; Martin, P.; Sanchez, E.; Jones, K.S. Effect of bulk growth temperature on antiphase domain boundary annihilation rate in MOCVD-grown GaAs on Si(001). J. Cryst. Growth 2016, 450, 39–44. [Google Scholar] [CrossRef]

- Li, J.; Guo, Z.; Zhao, L.; Jia, Z.; Zhang, M.; Zhao, L. Effect of thicknesses of InP epilayers on InP/GaAs heterostructure. Surf. Interface Anal. 2018, 50, 27–31. [Google Scholar] [CrossRef]

- Kim, T.W.; Jung, M.; Park, T.H.; Cho, J.W.; Park, H.L. Structural and optical properties of InP/GaAs strained heterostructures grown by metal-organic chemical vapor deposition. Thin Solid Films. 1995, 257, 36–39. [Google Scholar] [CrossRef]

- Lee, S.; Cho, Y.J.; Park, J.; Shin, K.W.; Hwang, E.; Lee, S.; Lee, M.; Cho, S.; Su Shin, D.; Park, J.; et al. Effects of growth temperature on surface morphology of InP grown on patterned Si(001) substrates. J. Cryst. Growth 2015, 416, 113–117. [Google Scholar] [CrossRef]

- Kwoen, J.; Jang, B.; Lee, J.; Kageyama, T.; Watanabe, K.; Arakawa, Y. All MBE grown InAs/GaAs quantum dot lasers on on-axis Si (001). Opt. Express 2018, 26, 11568. [Google Scholar] [CrossRef]

- Liu, A.Y.; Peters, J.; Huang, X.; Jung, D.; Norman, J.; Lee, M.L.; Gossard, A.C.; Bowers, J.E. Electrically pumped continuous-wave 1.3 μm quantum-dot lasers epitaxially grown on on-axis (001) GaP/Si. Opt. Lett. 2017, 42, 338–341. [Google Scholar] [CrossRef] [PubMed]

- Jung, D.; Callahan, P.G.; Shin, B.; Mukherjee, K.; Gossard, A.C.; Bowers, J.E. Low threading dislocation density GaAs growth on on-axis GaP/Si (001). J. Appl. Phys. 2017, 122, 225703. [Google Scholar] [CrossRef] [Green Version]

- Yang, S.; Lv, H.; Ai, L.; Tian, F.; Yan, S.; Zhang, Y. Influence of Growth Temperature of the Nucleation Layer on the Growth of InP on Si (001). Coatings 2019, 9, 823. [Google Scholar] [CrossRef] [Green Version]

- Liu, X.; Song, H.; Miao, G.Q.; Jiang, H.; Cao, L.; Li, D.; Sun, X.; Chen, Y. Influence of thermal annealing duration of buffer layer on the crystalline quality of In 0.82 Ga 0.18 As grown on InP substrate by LP-MOCVD. Appl. Surf. Sci. 2011, 257, 1996. [Google Scholar] [CrossRef]

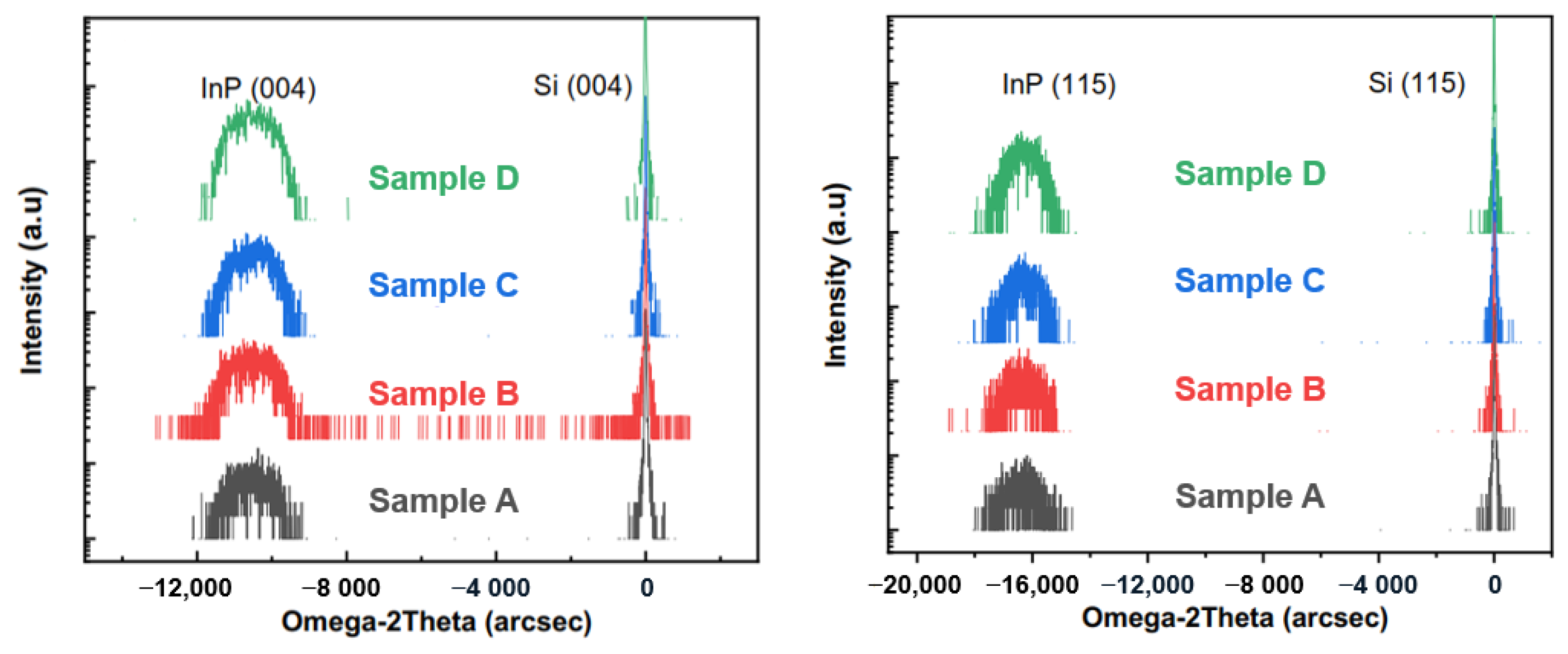

| Sample | Intensity of 004 (a.u) | FWHM of 004 (arcsec) | Intensity of 115 (a.u) | FWHM of 115 (arcsec) |

|---|---|---|---|---|

| A | 75 | 1400.76 | 68 | 21,619.11 |

| B | 138 | 1353.6 | 86 | 1806.8 |

| C | 155 | 1178.28 | 125 | 1639.5 |

| D | 394 | 901.44 | 221 | 1464.3 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Yan, S.; Lv, H.; Zhang, Y.; Yang, S. Effect of Thickness of InP Nucleation Layer on the Two-Step Growth of InP on Si(001). Crystals 2022, 12, 462. https://doi.org/10.3390/cryst12040462

Yan S, Lv H, Zhang Y, Yang S. Effect of Thickness of InP Nucleation Layer on the Two-Step Growth of InP on Si(001). Crystals. 2022; 12(4):462. https://doi.org/10.3390/cryst12040462

Chicago/Turabian StyleYan, Silu, Hongliang Lv, Yuming Zhang, and Shizheng Yang. 2022. "Effect of Thickness of InP Nucleation Layer on the Two-Step Growth of InP on Si(001)" Crystals 12, no. 4: 462. https://doi.org/10.3390/cryst12040462

APA StyleYan, S., Lv, H., Zhang, Y., & Yang, S. (2022). Effect of Thickness of InP Nucleation Layer on the Two-Step Growth of InP on Si(001). Crystals, 12(4), 462. https://doi.org/10.3390/cryst12040462