Subthreshold Characteristics of a Metal-Oxide–Semiconductor Field-Effect Transistor with External PVDF Gate Capacitance

Abstract

:1. Introduction

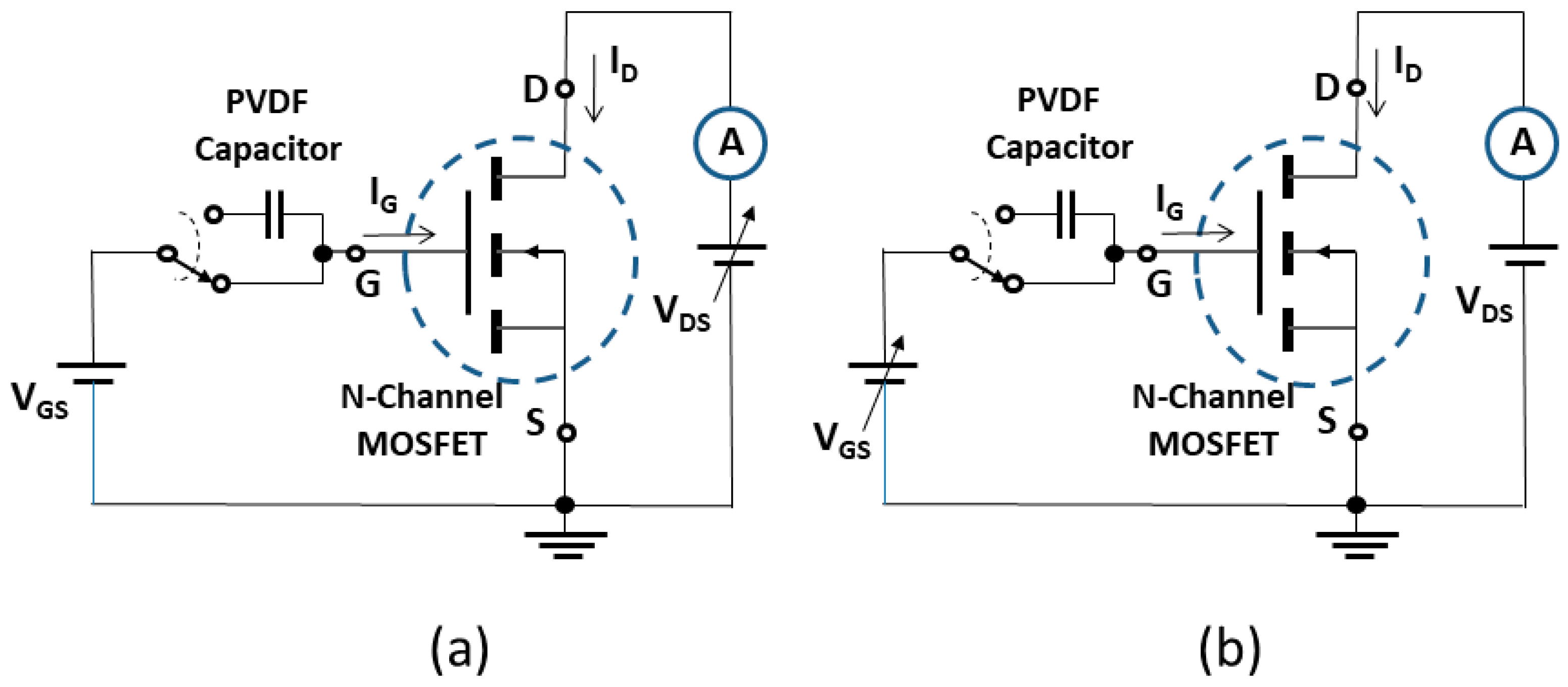

2. Materials and Methods

3. Results and Discussion

4. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Zhirnov, V.V.; Cavin, R.K. Negative capacitance to the rescue? Nat. Nanotechnol. 2008, 3, 77–78. [Google Scholar] [CrossRef]

- Theis, T.N.; Solomon, P.M. It’s time to reinvent transistor. Science 2010, 327, 1600–1601. [Google Scholar] [CrossRef]

- Han, G.; Zhou, J.; Liu, Y.; Li, J.; Peng, Y.; Hao, Y. Experimental investigation of fundamentals of negative capacitance FETs. In Proceedings of the 2018 IEEE SOI-3D-Subthreshold Microelectronics Technology Unified Conference (S3S), Burlingame, CA, USA, 15–18 October 2018; pp. 1–2. [Google Scholar]

- Krivokapic, Z.; Rana, U.; Galatage, R.; Razavieh, A.; Aziz, A.; Liu, J.; Shi, J.; Kim, H.J.; Sporer, R.; Serrao, C.; et al. 14 nm ferroelectric FinFET technology with steep subthreshold slope for ultra-low power applications. In Proceedings of the IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2–6 December 2017; pp. 15.1.1–15.1.4. [Google Scholar]

- Khan, A.I.; Chatterjee, K.; Wang, B.; Drapcho, S.; You, L.; Serrao, C.; Bakaul, S.R.; Ramesh, R.; Salahuddin, S. Negative capacitance in a ferroelectric capacitor. Nat. Mater. 2015, 14, 182–186. [Google Scholar] [CrossRef] [PubMed]

- Jo, J.; Choi, W.Y.; Park, J.-D.; Shim, J.W.; Yu, H.-Y.; Shin, C. Negative capacitance in organic/ferroelectric capacitor to implement steep switching MOS devices. Nano Lett. 2015, 15, 4553–4556. [Google Scholar] [CrossRef] [PubMed]

- Ku, H.; Shin, A. Transient response of negative capacitance in P(VDF0.75-TrFE0.25) organic ferroelectric capacitor. IEEE J. Electron Devices Soc. 2017, 5, 232–236. [Google Scholar] [CrossRef]

- Then, H.W.; Dasgupta, S.; Radosavljevic, M.; Chow, L.; Chu-Kung, B.; Dewey, G.; Gardner, S.; Gao, X.; Kavalieros, J.; Mukherjee, N.; et al. Experimental observation and physics of “negative” capacitance and steeper than 40mV/decade subthreshold swing in Al0.83In0.17N/AlN/GaN MOS-HEMT on SiC substrate”. In Proceedings of the IEEE International Electron Devices Meeting, Washington, DC, USA, 9–11 December 2013; pp. 28.3.1–28.3.4. [Google Scholar]

- Khan, A.I.; Chatterjee, K.; Duarte, J.P.; Lu, Z.; Sachid, A.; Khandelwal, S.; Ramesh, R.; Hu, C.; Salahuddin, S. Negative capacitance in short-channel FinFETs externally connected to an epitaxial ferroelectric capacitor. IEEE Elect. Dev. Lett. 2016, 37, 111–114. [Google Scholar] [CrossRef]

- Salvatore, G.A.; Bouvet, D.; Ionescu, A.M. Demonstration of subthreshold swing smaller than 60mV/decade in Fe-FET with P(VDF-TrFE)/SiO2gate stack. In Proceedings of the International Electron Devices Meeting, San Francisco, CA, USA, 15–17 December 2008; pp. 1–4. [Google Scholar]

- Choi, W.Y.; Park, B.-G.; Lee, J.D.; Liu, T.-J.K. Tunneling field-effect transistors (TFETs) with subthreshold swing (SS) less than 60 mV/dec. IEEE Electron Device Lett. 2007, 28, 743–745. [Google Scholar] [CrossRef]

- Khatami, Y.; Banerjee, K. Steep subthreshold slope n- and p-type tunnel-FET devices for low-power and energy-efficient digital circuits. IEEE Trans. Elect. Dev. 2009, 56, 2752–2761. [Google Scholar] [CrossRef]

- Liu, H.; Datta, S.; Narayanan, V. Steep switching tunnel FET: A promise to extend the energy efficient roadmap for post-CMOS digital and analog/RF applications. In Proceedings of the International Symposium on Low Power Electronics and Design (ISLPED), Beijing, China, 4–6 September 2013; pp. 145–150. [Google Scholar]

- Li, K.S.; Chen, P.G.; Lai, T.Y.; Lin, C.H.; Cheng, C.C.; Chen, C.C.; Wei, Y.J.; Hou, Y.F.; Liao, M.H.; Lee, M.H.; et al. Sub-60mV-swing negative-capacitance FinFET without hysteresis. In Proceedings of the IEEE International Electron Devices Meeting (IEDM), Washington, DC, USA, 7–9 December 2015; pp. 22.6.1–22.6.4. [Google Scholar]

- Yadav, A.K.; Nguyen, K.X.; Hong, Z.; García-Fernández, P.; Aguado-Puente, P.; Nelson, C.T.; Das, S.; Prasad, B.; Kwon, D.; Cheema, S.; et al. Spatially resolved steady-state negative capacitance. Nature 2019, 565, 468–471. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Das, S.; Tang, Y.L.; Hong, Z.; Gonçalves, M.A.P.; McCarter, M.R.; Klewe, C.; Nguyen, K.X.; Gómez-Ortiz, F.; Shafer, P.; Arenholz, E.; et al. Observation of room-temperature polar skyrmions. Nature 2019, 568, 368–372. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Lu, X.; Chen, Z.; Cao, Y.; Tang, Y.; Xu, R.; Saremi, S.; Zhang, Z.; You, L.; Dong, Y.; Das, S.; et al. Mechanical-force-induced non-local collective ferroelastic swiching in epitaxial lead-titanate thin films. Nat. Commun. 2019, 10, 3951. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Das, S.; Ghosh, A.; McCarter, M.R.; Hsu, S.-L.; Tang, Y.-L.; Damodaran, A.R.; Ramesh, R.; Martin, L.W. Perspective: Emergent topologies in oxidesuperlattices. APL Mater. 2018, 6, 100901. [Google Scholar] [CrossRef] [Green Version]

- Stoica, V.A.; Laanait, N.; Dai, C.; Hong, Z.; Yuan, Y.; Zhang, Z.; Lei, S.; McCarter, M.R.; Yadav, A.; Damodaran, A.R.; et al. Optical creation of a supercrystal with three-dimensional nanoscale periodicity. Nat. Mater. 2019, 18, 377–383. [Google Scholar] [CrossRef] [PubMed]

- Martens, H.C.F.; Pasveer, W.F.; Brom, H.B.; Huiberts, J.N.; Blom, P.W.M. Crossover from space-charge-limited to recombination-limited transport in polymer light-emitting diodes. Phys. Rev. B 2001, 63, 125328. [Google Scholar] [CrossRef] [Green Version]

- Martens, H.C.F.; Huiberts, J.N.; Blom, P.W.M. Simultaneous measurement of electron and hole mobilities in polymer light-emitting diodes. Appl. Phys. Lett. 2000, 77, 1852–1854. [Google Scholar] [CrossRef] [Green Version]

- Kwok, H.L. Maximizing the value of gate capacitance in field-effect devices using an organic interface layer. Solid-State Electron. 2015, 114, 163–166. [Google Scholar] [CrossRef]

- Jo, J.; Shin, C. Negative capacitance field effect transistor with hysteresis-free sub-60-mV/decade switching. IEEE Elect. Dev. Lett. 2016, 37, 245–248. [Google Scholar] [CrossRef]

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Lin, J.-J.; Tao, J.-H.; Wu, Y.-L. Subthreshold Characteristics of a Metal-Oxide–Semiconductor Field-Effect Transistor with External PVDF Gate Capacitance. Crystals 2019, 9, 673. https://doi.org/10.3390/cryst9120673

Lin J-J, Tao J-H, Wu Y-L. Subthreshold Characteristics of a Metal-Oxide–Semiconductor Field-Effect Transistor with External PVDF Gate Capacitance. Crystals. 2019; 9(12):673. https://doi.org/10.3390/cryst9120673

Chicago/Turabian StyleLin, Jing-Jenn, Ji-Hua Tao, and You-Lin Wu. 2019. "Subthreshold Characteristics of a Metal-Oxide–Semiconductor Field-Effect Transistor with External PVDF Gate Capacitance" Crystals 9, no. 12: 673. https://doi.org/10.3390/cryst9120673

APA StyleLin, J.-J., Tao, J.-H., & Wu, Y.-L. (2019). Subthreshold Characteristics of a Metal-Oxide–Semiconductor Field-Effect Transistor with External PVDF Gate Capacitance. Crystals, 9(12), 673. https://doi.org/10.3390/cryst9120673