Resistive Switching Characteristics of ZnO-Based RRAM on Silicon Substrate

Abstract

:1. Introduction

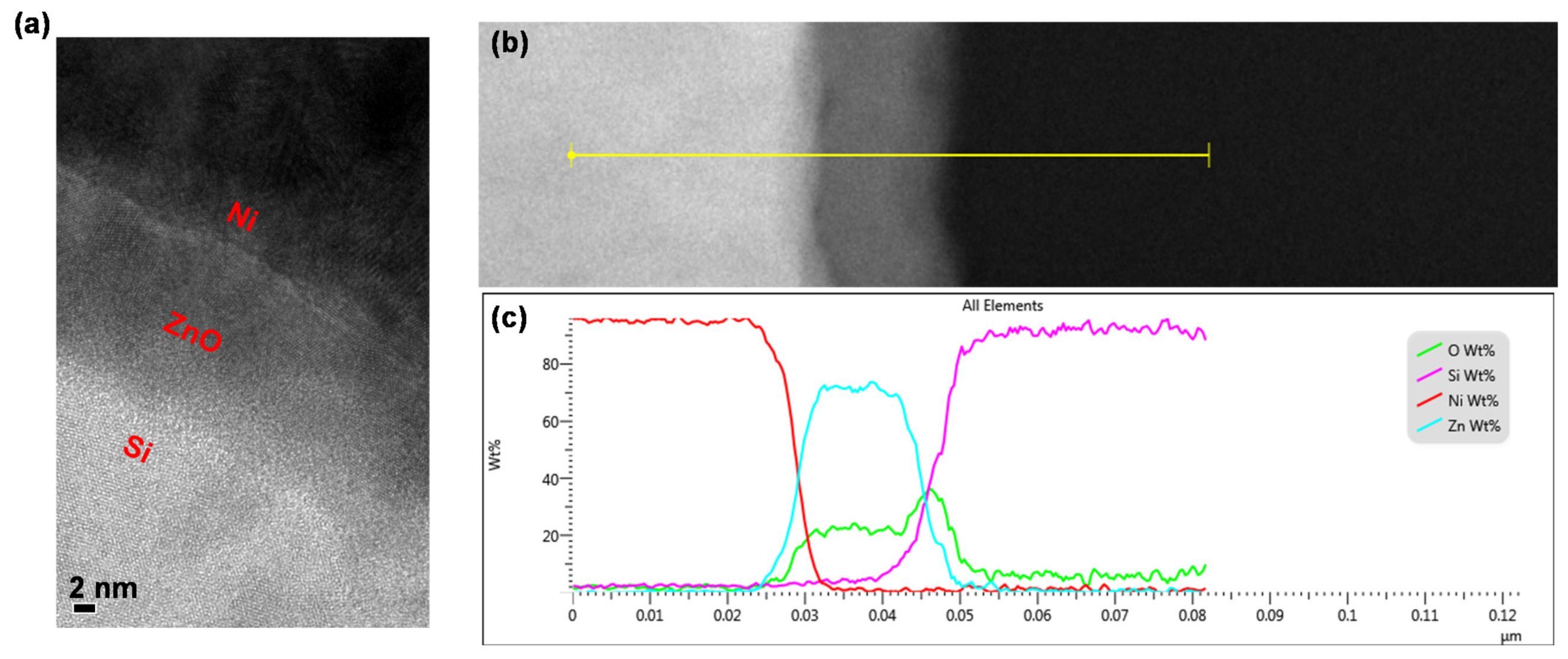

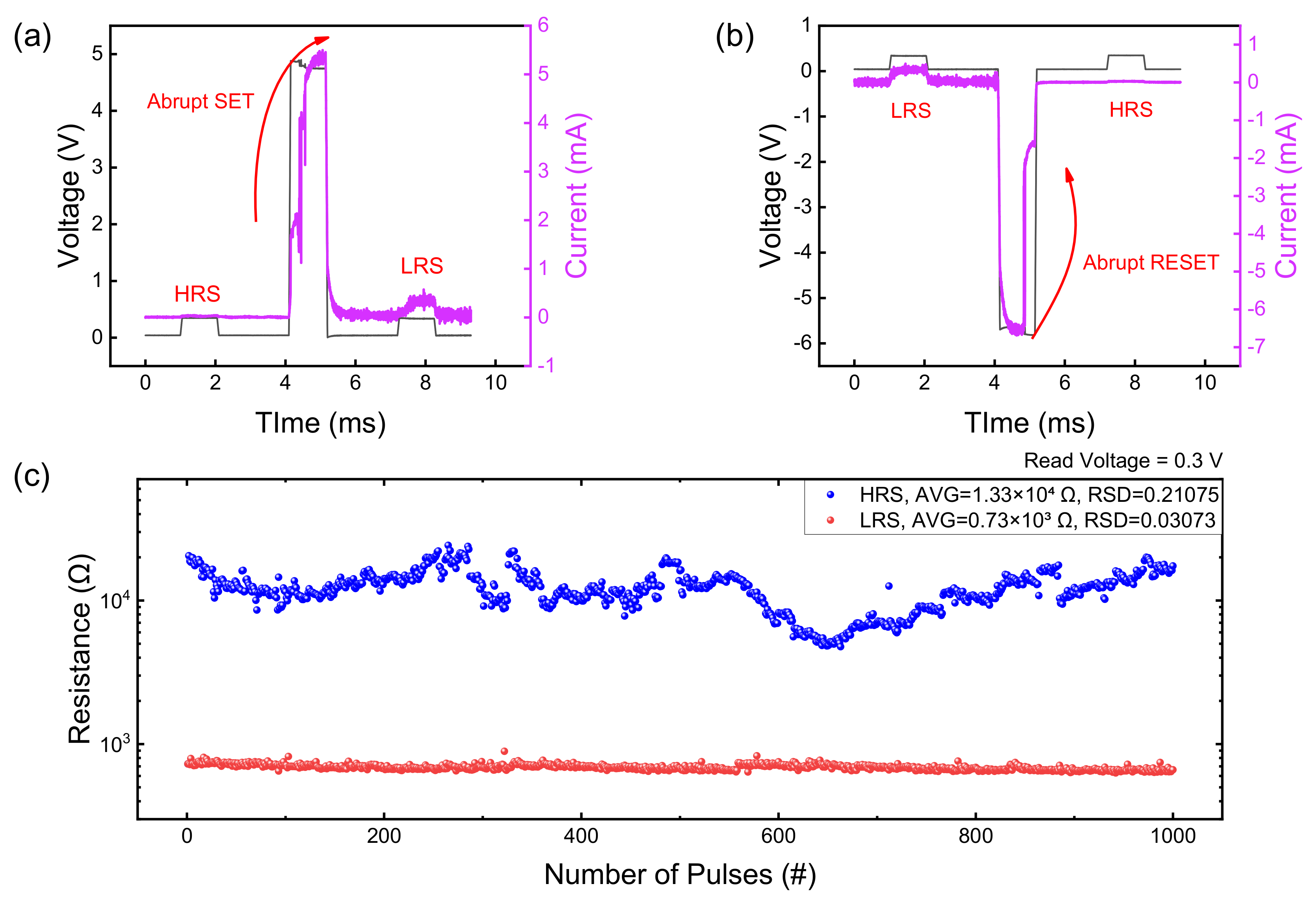

2. Materials and Methods

3. Results and Discussion

4. Conclusions

Supplementary Materials

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Lee, G.; Hwang, S.; Yu, J.; Kim, H. Architecture and Process Integration Overview of 3D NAND Flash Technologies. Appl. Sci. 2021, 11, 6703. [Google Scholar] [CrossRef]

- Lanza, M.; Wong, H.-S.P.; Pop, E.; Ielmini, D.; Strukov, D.; Regan, B.C.; Larcher, L.; Villena, M.A.; Yang, J.J.; Goux, L.; et al. Recommended Methods to Study Resistive Switching Devices. Adv. Electron. Mater. 2018, 5, 1800143. [Google Scholar] [CrossRef] [Green Version]

- Linn, E.C.; Rosezin, R.D.; Kügeler, C.; Waser, R. Complementary resistive switches for passive nanocrossbar memories. Nat. Mater. 2010, 9, 403–406. [Google Scholar] [CrossRef]

- Mikhaylov, A.; Belov, A.; Korolev, D.; Antonov, I.; Kotomina, V.; Kotina, A.; Gryaznov, E.; Sharapov, A.; Koryazhkina, M.; Kryukov, R.; et al. Multilayer Metal-Oxide Memristive Device with Stabilized Resistive Switching. Adv. Mater. Technol. 2019, 5. [Google Scholar] [CrossRef]

- Ryu, H.; Kim, S. Self-Rectifying Resistive Switching and Short-Term Memory Characteristics in Pt/HfO2/TaOx/TiN Artificial Synaptic Device. Nanomaterials 2020, 10, 2159. [Google Scholar] [CrossRef]

- Kim, S.; Jung, S.; Kim, M.-H.; Chen, Y.-C.; Chang, Y.-F.; Ryoo, K.-C.; Cho, S.; Lee, J.-H.; Park, B.-G. Scaling Effect on Silicon Nitride Memristor with Highly Doped Si Substrate. Small 2018, 14, e1704062. [Google Scholar] [CrossRef] [PubMed]

- Ryu, H.; Kim, S. Pseudo-Interface Switching of a Two-Terminal TaOx/HfO2 Synaptic Device for Neuromorphic Applications. Nanomaterials 2020, 10, 1550. [Google Scholar] [CrossRef]

- Ryu, H.; Choi, J.; Kim, S. Voltage Amplitude-Controlled Synaptic Plasticity from Complementary Resistive Switching in Alloying HfOx with AlOx-Based RRAM. Metals 2020, 10, 1410. [Google Scholar] [CrossRef]

- Ohno, T.; Hasegawa, T.; Tsuruoka, T.; Terabe, K.; Gimzewski, J.; Aono, M. Short-term plasticity and long-term potentiation mimicked in single inorganic synapses. Nat. Mater. 2011, 10, 591–595. [Google Scholar] [CrossRef]

- Su, Y.; Chang, K.-C.; Chang, T.-C.; Tsai, T.-M.; Zhang, R.; Lou, J.C.; Chen, J.-H.; Young, T.-F.; Chen, K.-H.; Tseng, B.-H.; et al. Characteristics of hafnium oxide resistance random access memory with different setting compliance current. Appl. Phys. Lett. 2013, 103, 163502. [Google Scholar] [CrossRef] [Green Version]

- Ryu, H.; Kim, S. Gradually Tunable Conductance in TiO2/Al2O3 Bilayer Resistors for Synaptic Device. Metals 2021, 11, 440. [Google Scholar] [CrossRef]

- Ismail, M.; Abbas, H.; Choi, C.; Kim, S. Controllable analog resistive switching and synaptic characteristics in ZrO2/ZTO bilayer memristive device for neuromorphic systems. Appl. Surf. Sci. 2020, 529, 147107. [Google Scholar] [CrossRef]

- Chen, H.-K.; Chang, K.-C.; Chang, T.-C.; Tsai, T.-M.; Liao, K.-H.; Syu, Y.-E.; Sze, S.M. Effect of different constant compliance current for hopping conduction distance properties of the Sn:SiOx thin film RRAM devices. Appl. Phys. A 2016, 122, 228. [Google Scholar] [CrossRef]

- Yu, S.; Wong, H.S.P. Compact Modeling of Conducting-Bridge Random-Access Memory (CBRAM). IEEE Trans. Electron Devices 2011, 58, 1352–1360. [Google Scholar]

- Zhao, M.; Gao, B.; Xi, Y.; Xu, F.; Wu, H.; Qian, H. Endurance and Retention Degradation of Intermediate Levels in Filamentary Analog RRAM. IEEE J. Electron. Devices Soc. 2019, 7, 1239–1247. [Google Scholar] [CrossRef]

- Chen, Y.-C.; Lin, C.-C.; Hu, S.-T.; Lin, C.-Y.; Fowler, B.; Lee, J. A Novel Resistive Switching Identification Method through Relaxation Characteristics for Sneak-path-constrained Selectorless RRAM application. Sci. Rep. 2019, 9, 12420. [Google Scholar] [CrossRef] [Green Version]

- Lammie, C.; Azghadi, M.R.; Ielmini, D. Empirical metal-oxide RRAM device endurance and retention model for deep learning simulations. Semicond. Sci. Technol. 2021, 36, 065003. [Google Scholar] [CrossRef]

- Kim, S.; Chang, Y.F.; Park, B.G. Understanding rectifying and nonlinear bipolar resistive switching characteristics in Ni/SiNx/p-Si memory devices. RSC Adv. 2017, 7, 17882. [Google Scholar] [CrossRef] [Green Version]

- Kim, S.; Jung, S.; Kim, M.-H.; Cho, S.; Park, B.-G. Resistive switching characteristics of Si3N4-based resistive-switching random-access memory cell with tunnel barrier for high density integration and low-power applications. Appl. Phys. Lett. 2015, 106, 212106. [Google Scholar] [CrossRef]

- Simanjuntak, F.M.; Ohno, T.; Samukawa, S. Influence of rf sputter power on ZnO film characteristics for transparent memristor devices. AIP Adv. 2019, 9, 105216. [Google Scholar] [CrossRef] [Green Version]

- Simanjuntak, F.M.; Ohno, T.; Samukawa, S. Film-Nanostructure-Controlled Inerasable-to-Erasable Switching Transition in ZnO-Based Transparent Memristor Devices: Sputtering-Pressure Dependency. ACS Appl. Electron. Mater. 2019, 11, 2184–2189. [Google Scholar] [CrossRef]

- Simanjuntak, F.M.; Panda, D.; Wei, K.H.; Tseng, T.Y. Status and Prospects of ZnO-Based Resistive Switching Memory Devices. Nanoscale Res. Lett. 2016, 11, 368. [Google Scholar] [CrossRef] [Green Version]

- Shimura, K.; Yoshida, H. Heterogeneous photocatalytic hydrogen production from water and biomass derivatives. Energy Environ. Sci. 2011, 4, 2467–2481. [Google Scholar] [CrossRef]

- Chizhov, A.S.; Rumyantseva, M.N.; Vasilieva, R.B.; Filatova, D.F.; Drozdov, K.A.; Krylov, I.V.; Marchevsky, A.V.; Karakulina, O.M.; Abakumov, A.M.; Gaskov, A. Visible light activation of room temperature NO2 gas sensors based on ZnO, SnO2 and In2O3 sensitized with CdSe quantum dots. Thin Solid Film. 2016, 11, 253–262. [Google Scholar] [CrossRef]

- Fujimura, N.; Ohta, A.; Makihara, K.; Miyazaki, S. Evaluation of valence band top and electron affinity of SiO2 and Si-based semiconductors using X-ray photoelectron spectroscopy. Jpn. J. Appl. Phys. 2016, 55, 08PC06. [Google Scholar] [CrossRef]

- Gao, S.; Liu, G.; Chen, Q.; Xue, W.; Yang, H.; Shang, J.; Chen, B.; Zeng, F.; Song, C.; Pan, F.; et al. Improving Unipolar Resistive Switching Uniformity with Cone-Shaped Conducting Filaments and Its Logic-In-Memory Application. ACS Appl. Mater. Interfaces 2018, 10, 6453–6462. [Google Scholar] [CrossRef] [PubMed]

| Matrial | Work Function (eV) | Electron Affinity (eV) | Band Gap (eV) |

|---|---|---|---|

| Ni | 5.15 | - | - |

| ZnO | - | 4.6 | 3.3 |

| SiO₂ | - | 0.9 | 9.0 |

| Si | - | 4.03 | 1.12 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Kim, D.; Shin, J.; Kim, S. Resistive Switching Characteristics of ZnO-Based RRAM on Silicon Substrate. Metals 2021, 11, 1572. https://doi.org/10.3390/met11101572

Kim D, Shin J, Kim S. Resistive Switching Characteristics of ZnO-Based RRAM on Silicon Substrate. Metals. 2021; 11(10):1572. https://doi.org/10.3390/met11101572

Chicago/Turabian StyleKim, Dahye, Jiwoong Shin, and Sungjun Kim. 2021. "Resistive Switching Characteristics of ZnO-Based RRAM on Silicon Substrate" Metals 11, no. 10: 1572. https://doi.org/10.3390/met11101572