Low-Noise Chopper-Stabilized Multi-Path Operational Amplifier with Nested Miller Compensation for High-Precision Sensors

Abstract

:1. Introduction

2. Circuit Implementation of the Proposed Operational Amplifier

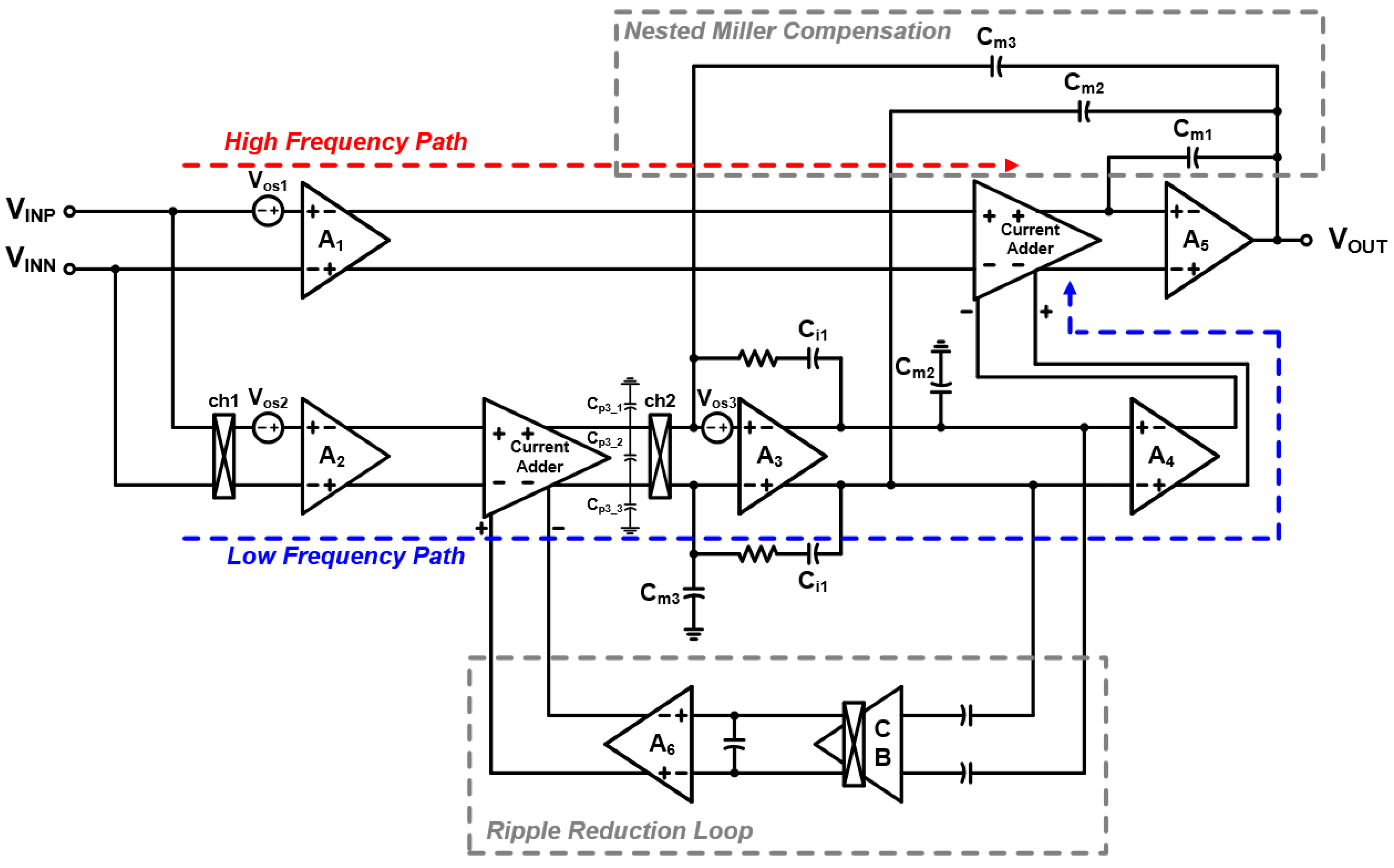

2.1. Architecture of the Proposed Multi-Path Operational Amplifier

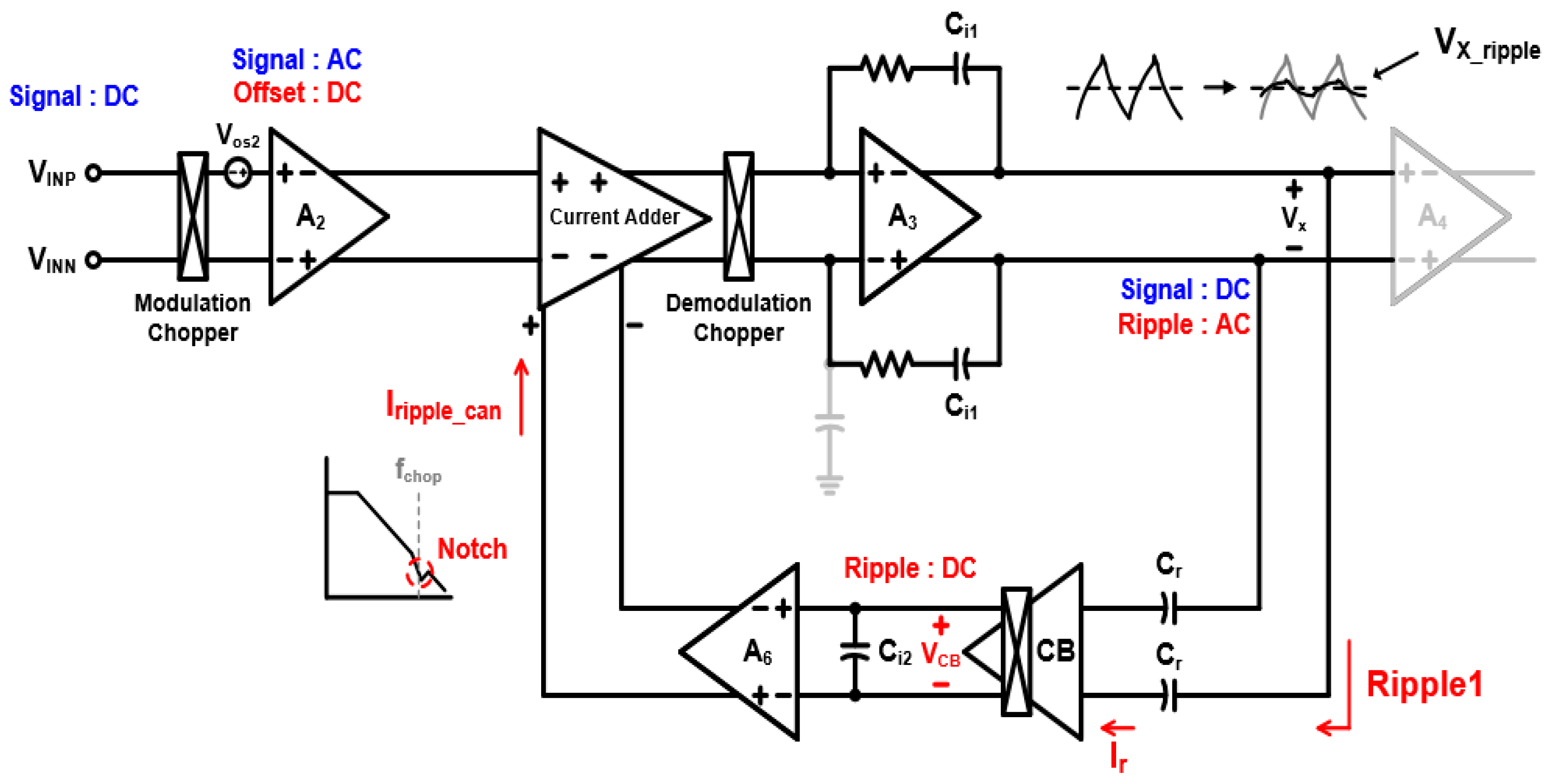

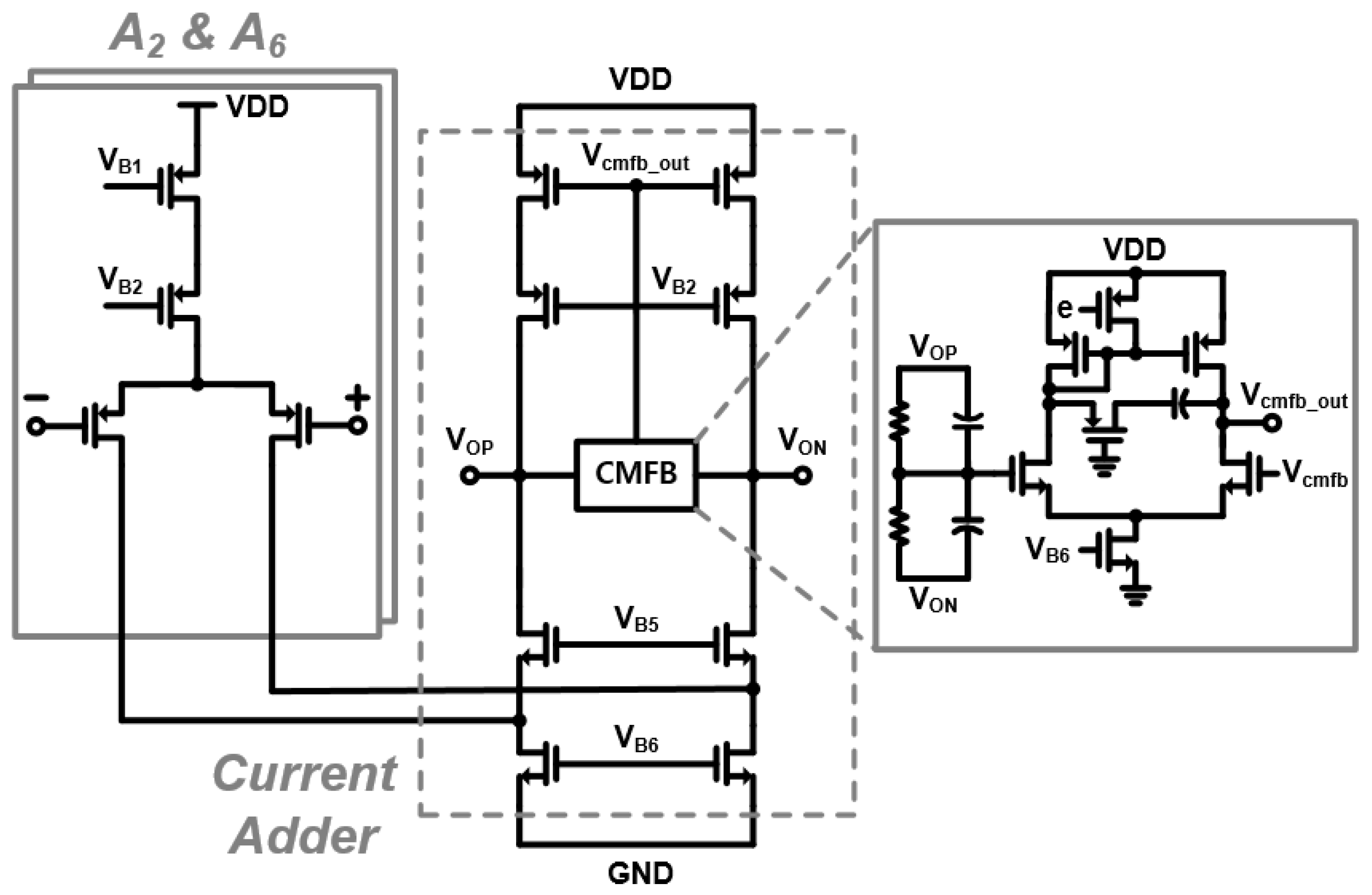

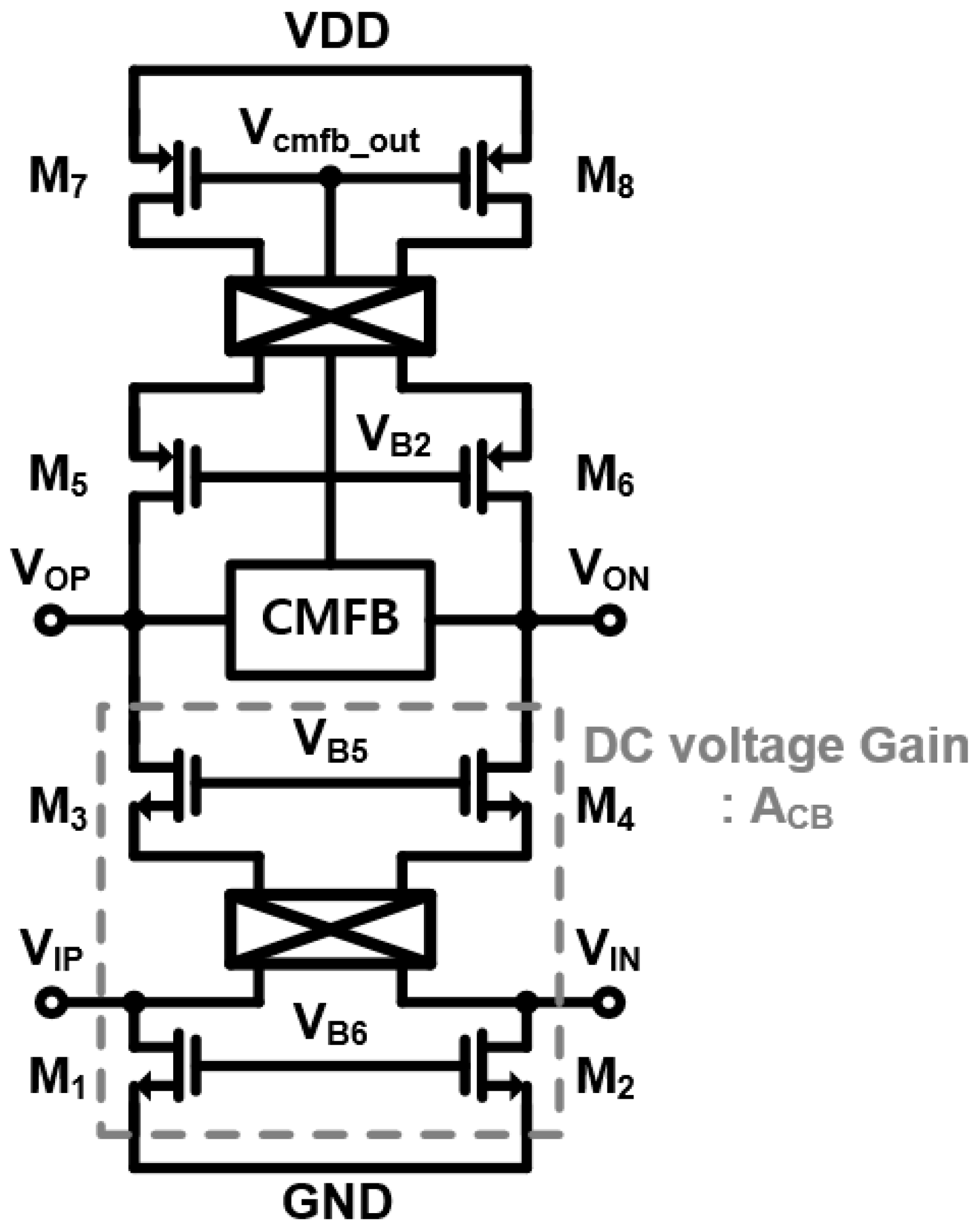

2.2. Low-Frequency Path Design

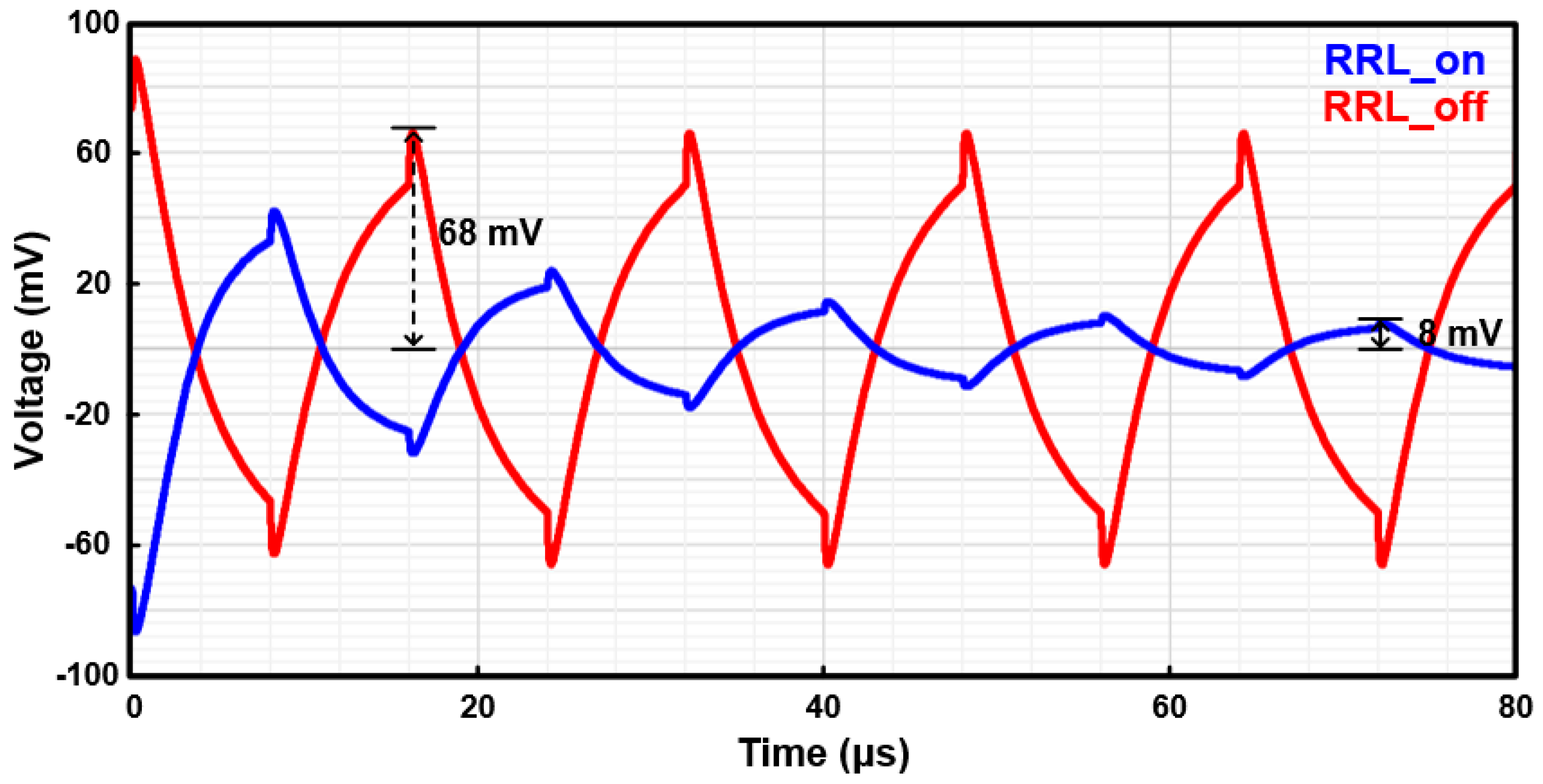

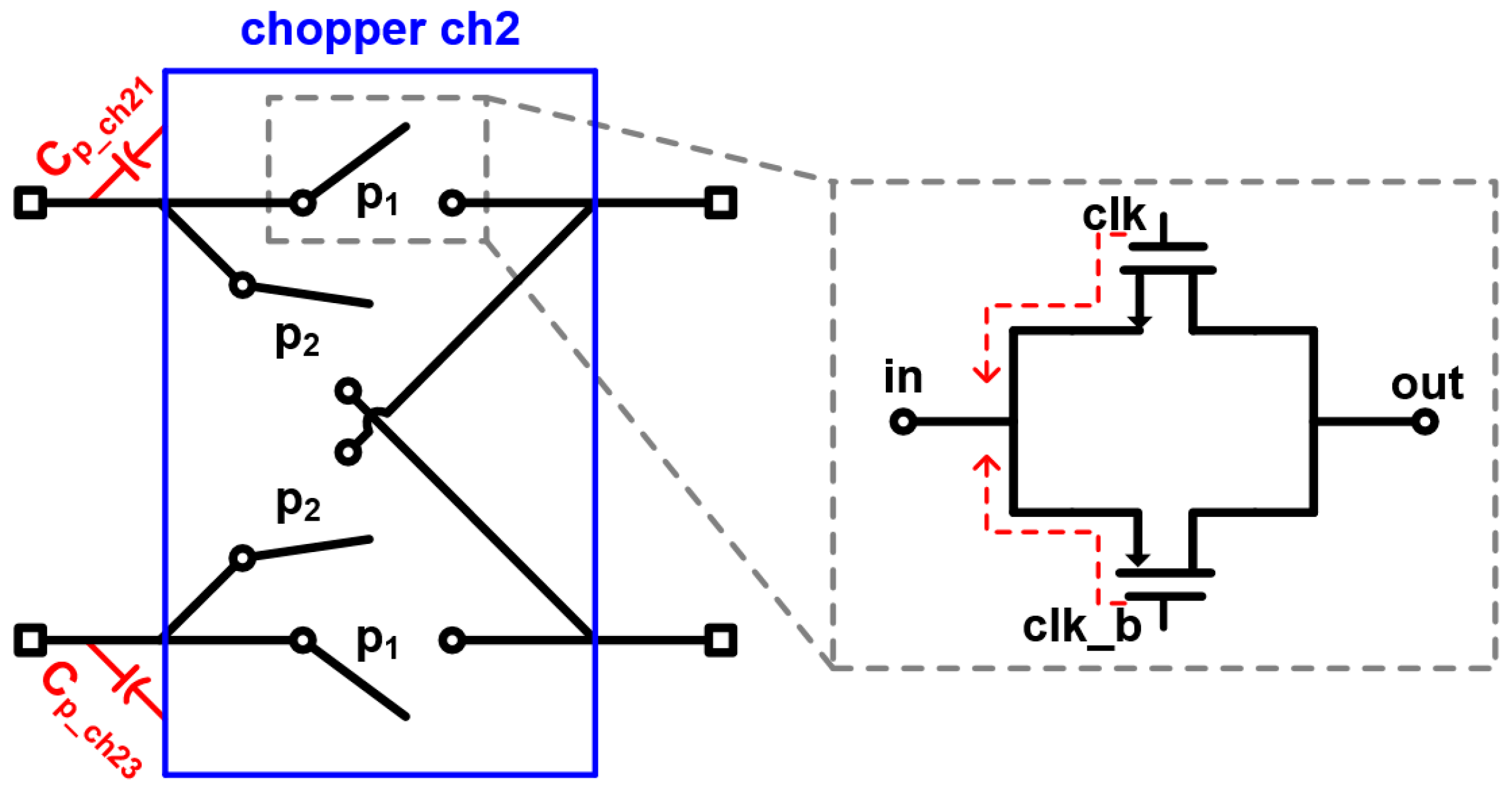

2.3. Ripple Reduction Loop Design

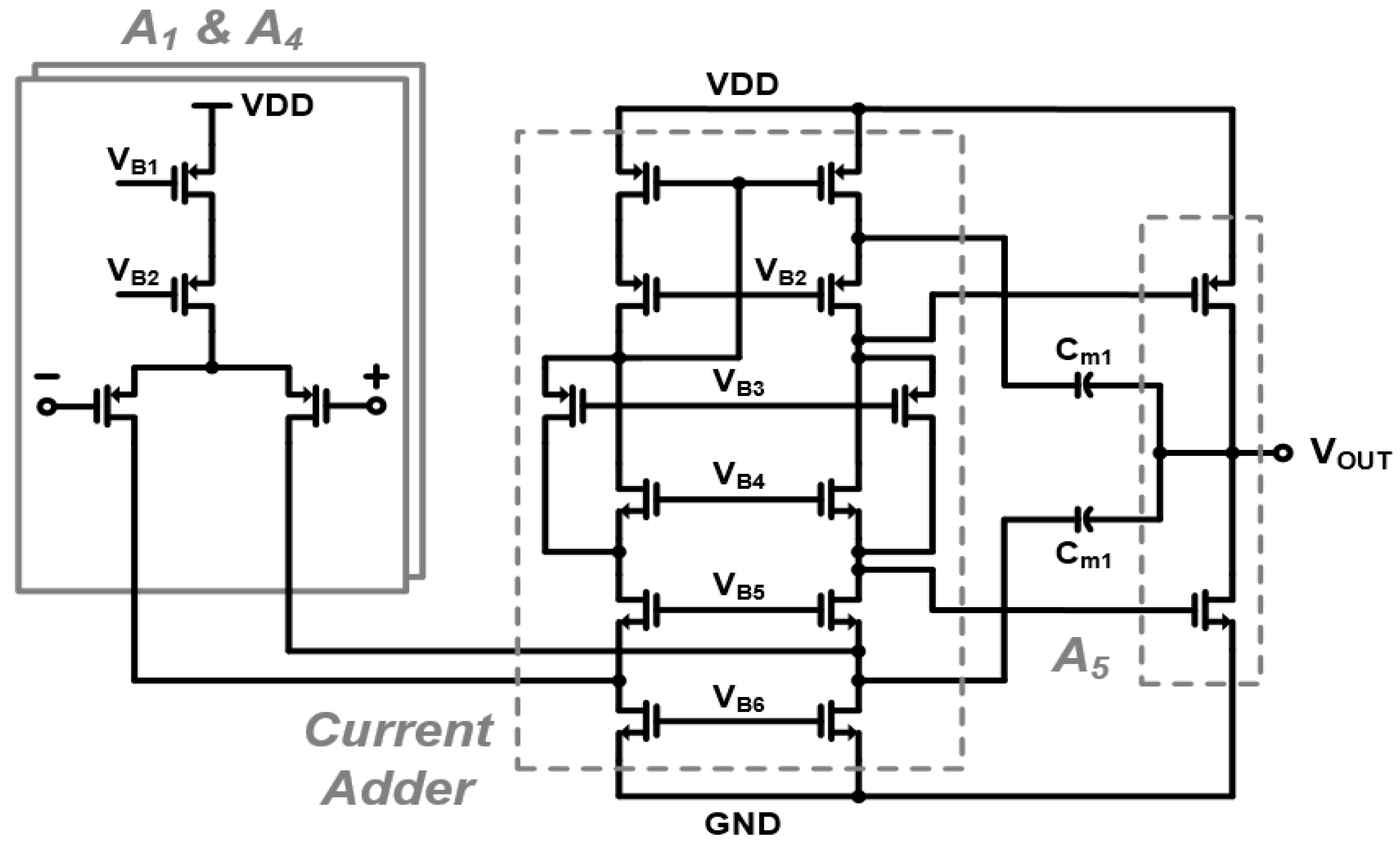

2.4. High-Frequency Path Design

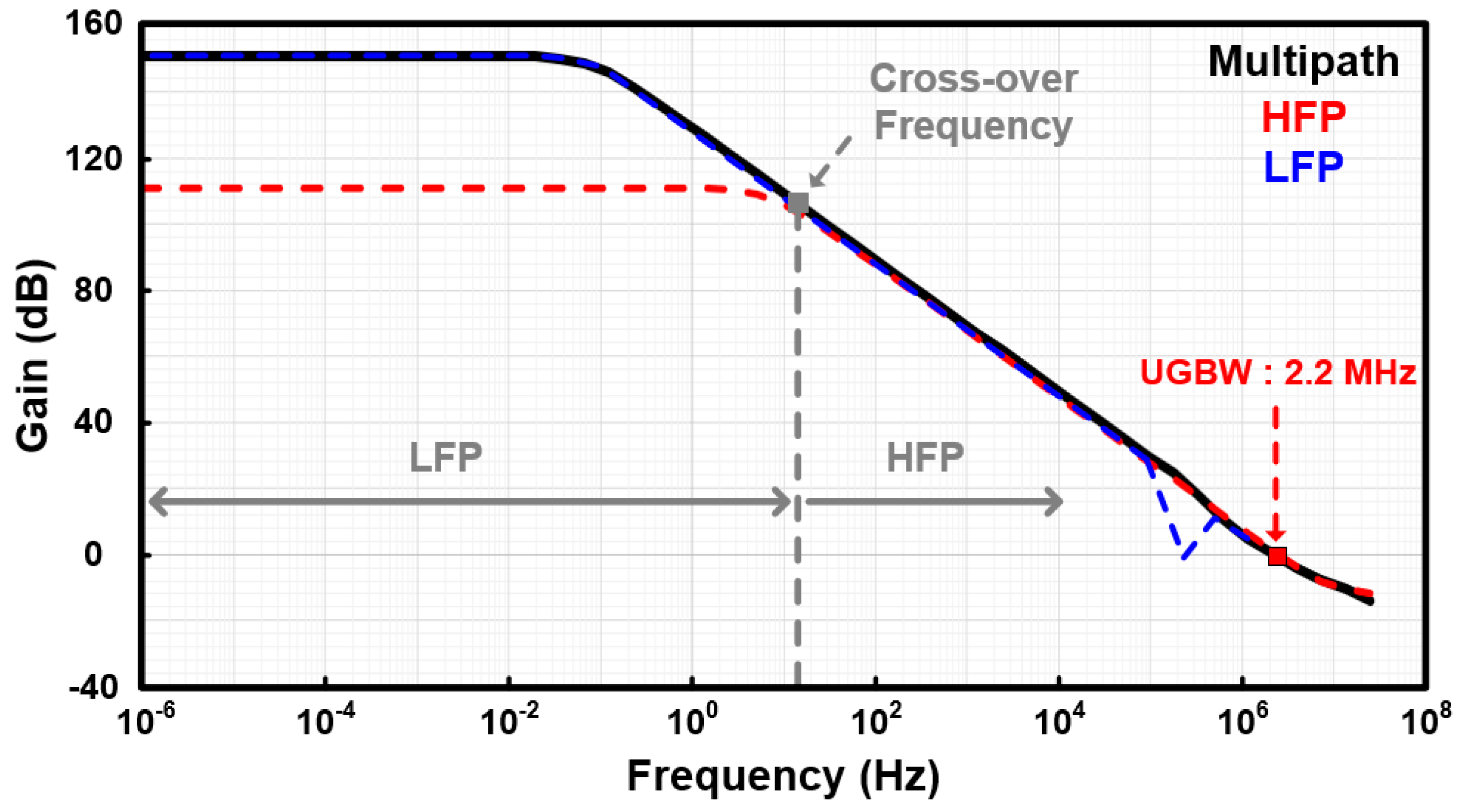

2.5. Frequency Response

2.6. Residual Input Offset

3. Measurement Results

3.1. Chip Die and Measurement Environment

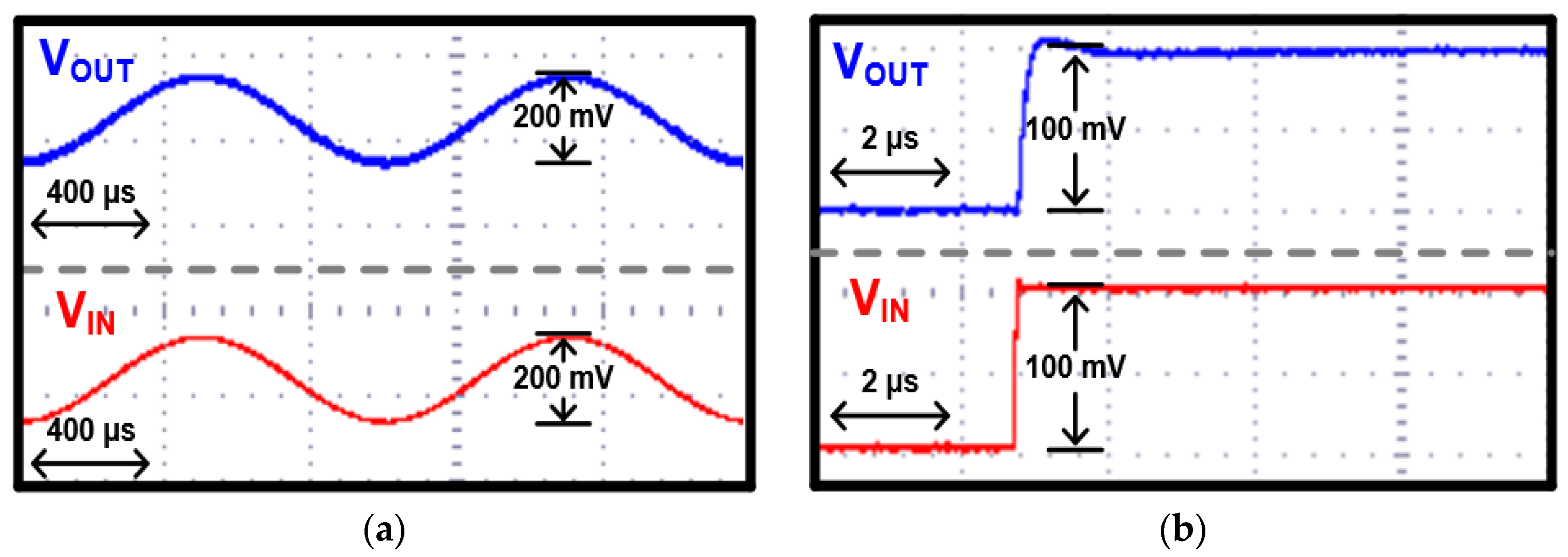

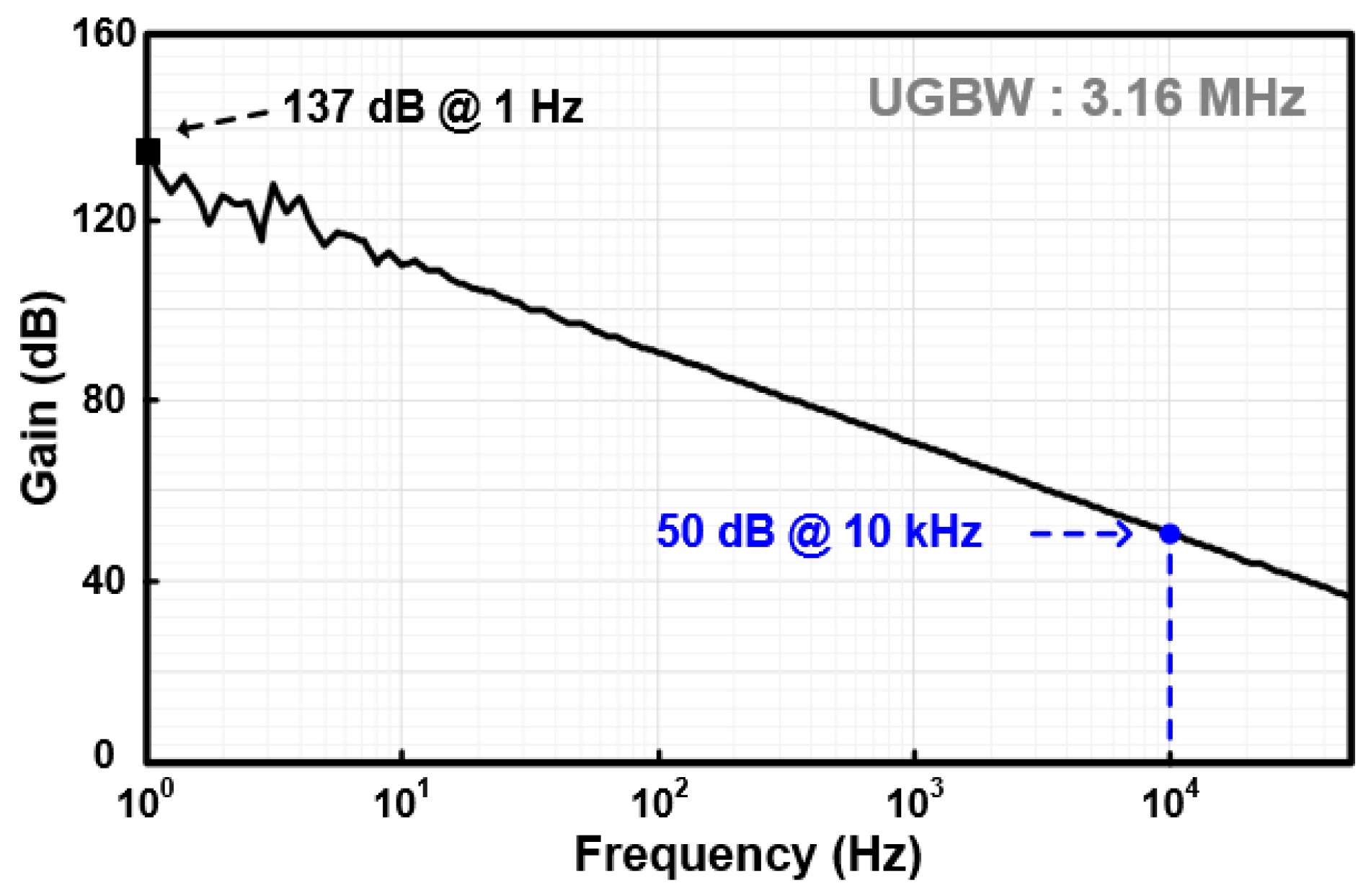

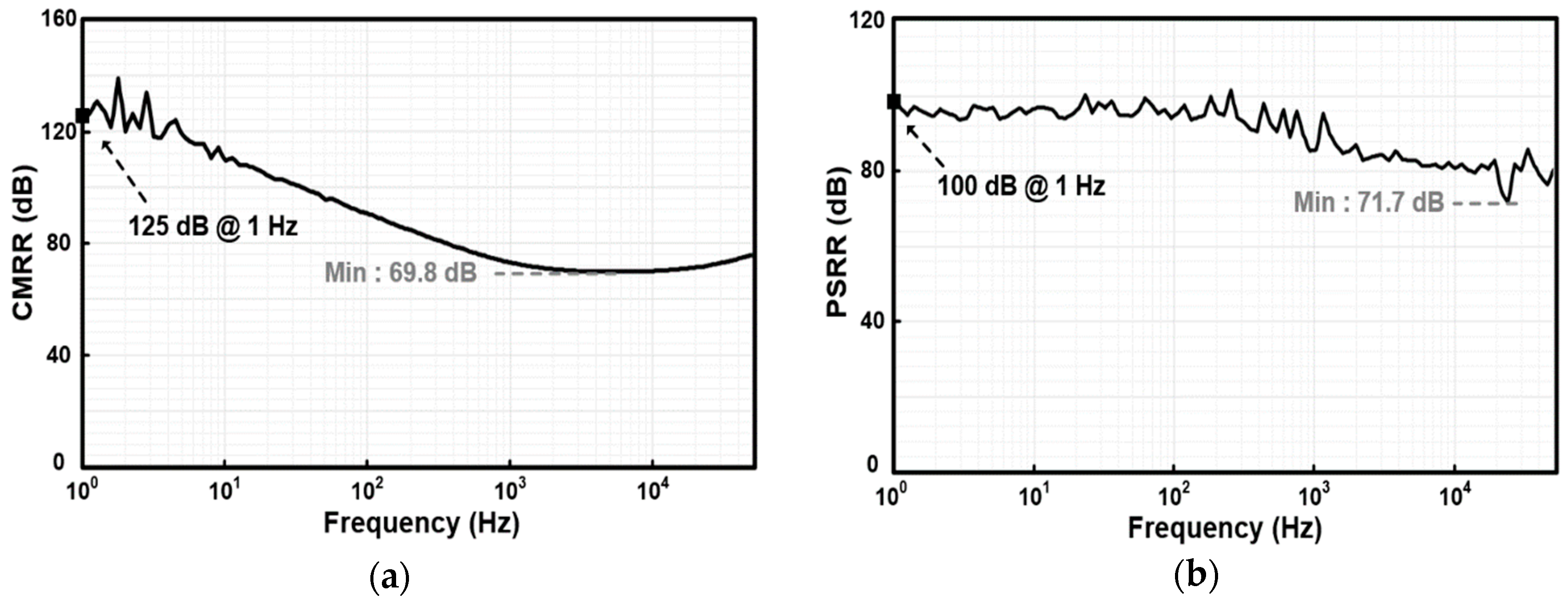

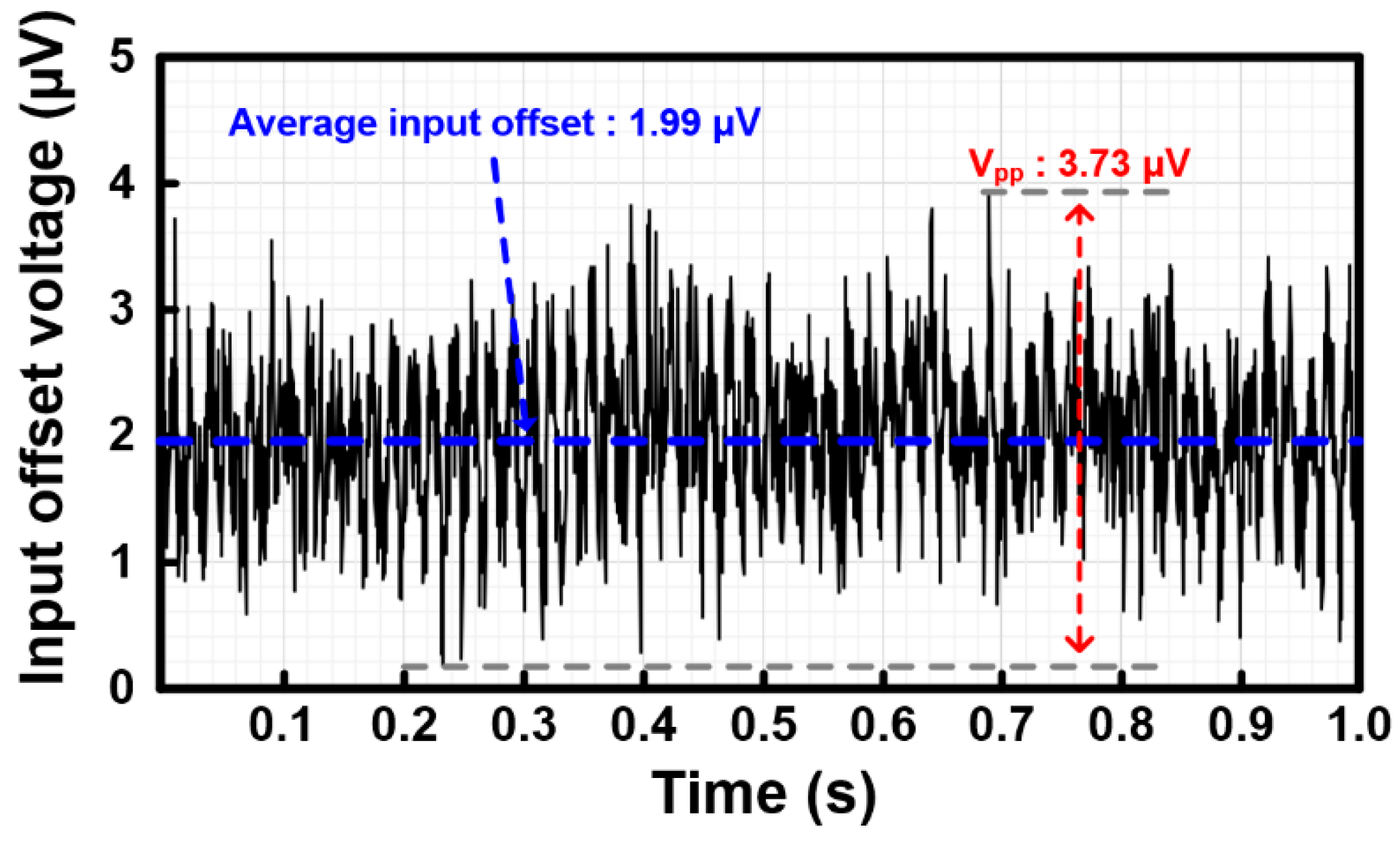

3.2. Measurement Results

4. Discussion

5. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Sun, H.; Fang, D.; Jia, K.; Maarouf, F.; Qu, H.; Xie, H. A low-power low-noise dual-chopper amplifier for capacitive CMOS-MEMS accelerometers. IEEE Sens. J. 2010, 11, 925–933. [Google Scholar] [CrossRef]

- Tan, Z.; Shalmany, S.H.; Meijer, G.C.; Pertijs, M.A. An energy-efficient 15-bit capacitive-sensor interface based on period modulation. IEEE J. Solid State Circuits 2012, 47, 1703–1711. [Google Scholar] [CrossRef]

- Yu, H.Y.; Qin, M.; Huang, J.Q.; Huang, Q.A. A MEMS capacitive pressure sensor compatible with CMOS process. In Proceedings of the SENSORS 2012 IEEE, Taipei, Taiwan, 28–31 October 2012; IEEE: Piscataway, NJ, USA, 2012; pp. 1–4. [Google Scholar]

- Ladani, L.; Nelson, S. A novel piezo-actuator-sensor micromachine for mechanical characterization of micro-specimens. Micromachines 2010, 1, 129–152. [Google Scholar] [CrossRef]

- Belloni, M.; Bonizzoni, E.; Fornasari, A.; Maloberti, F. A micropower chopper—CDS operational amplifier. IEEE J. Solid State Circuits 2010, 45, 2521–2529. [Google Scholar] [CrossRef]

- Kim, H.; Song, H.; Park, Y.; Ko, H. Low noise resistive analog front-end with automatic offset calibration loop. In Proceedings of the 2015 International SoC Design Conference (ISOCC), Gyungju, Korea, 2–5 November 2015. [Google Scholar]

- Wu, R.; Huijsing, J.H.; Makinwa, K.A. A 21b ± 40 mV range read-out IC for bridge transducers. In Proceedings of the 2011 IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 20–24 February 2011. [Google Scholar]

- Enz, C.C.; Temes, G.C. Circuit techniques for reducing the effects of op-amp imperfections: Autozeroing, correlated double sampling, and chopper stabilization. Proc. IEEE 1996, 84, 1584–1614. [Google Scholar] [CrossRef] [Green Version]

- Ko, Y.; Kim, H.; Park, Y.; Mun, Y.; Cho, D.I.D.; Ko, H. Low-Noise Chopper-Stabilized Resistive Readout Integrated Circuit with Ripple Rejection Loop. Sens. Mater. 2017, 29, 927–933. [Google Scholar]

- Wu, R.; Makinwa, K.A.; Huijsing, J.H. A chopper current-feedback instrumentation amplifier with a 1 mHz 1/f noise corner and an AC-coupled ripple reduction loop. IEEE J. Solid State Circuits 2009, 44, 3232–3243. [Google Scholar] [CrossRef] [Green Version]

- Eschauzier, R.G.; Kerklaan, L.P.; Huijsing, J.H. A 100-MHz 100-dB operational amplifier with multipath nested Miller compensation structure. IEEE J. Solid-State Circuits 1992, 27, 1709–1717. [Google Scholar] [CrossRef] [Green Version]

- Monticelli, D.M. A Quad CMOS Single-Supply Op Amp with Rail-to-Rail Output Swing. IEEE J. Solid-State Circuits 1986, 21, 1026–1034. [Google Scholar] [CrossRef] [Green Version]

- Eschauzier, R.G.; Hogervorst, R.; Huijsing, J.H. A programmable 1.5 V CMOS class-AB operational amplifier with hybrid nested Miller compensation for 120 dB gain and 6 MHz UGF. IEEE J. Solid State Circuits 1994, 29, 1497–1504. [Google Scholar] [CrossRef]

- Witte, F.; Huijsing, J.H.; Makinwa, K.A. Dynamic Offset Compensated CMOS Amplifiers; Springer: Berlin, Germany, 2010; pp. 23–40. [Google Scholar]

- Steyaert, M.S.J.; Sansen, W.M.C. A Micropower Low-Noise Monolitic Instrumentation 284 Amplifier for Medical Purposes. IEEE J. Solid-State Circuits 1987, 22, 1163–1168. [Google Scholar] [CrossRef]

- Fan, Q.; Huijsing, J.H.; Makinwa, K.A. A 21 nV/√Hz Chopper-Stabilized Multi-Path Current-Feedback Instrumentation Amplifier with 2 µV Offset. IEEE J. Solid State Circuits 2011, 47, 464–475. [Google Scholar]

- Burt, R.; Zhang, J. A micropower chopper-stabilized operational amplifier using a SC notch filter with synchronous integration inside the continuous time signal path. In Proceedings of the 2006 IEEE International Solid-State Circuits Conference-Digest of Technical Papers, San Francisco, CA, USA, 6–9 February 2006. [Google Scholar]

- Kusuda, Y. A 5.9 nV/√ Hz chopper operational amplifier with 0.78 μV maximum offset and 28.3 nV/°C offset drift. In Proceedings of the 2011 IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 20–24 February 2011. [Google Scholar]

- Ong, G.T.; Chan, P.K. A power-aware chopper-stabilized instrumentation amplifier for resistive wheatstone bridge sensors. IEEE Trans. Instrum. Meas. 2014, 63, 2253–2263. [Google Scholar] [CrossRef]

- Lue, D.; Zhang, M.; Wang, Z. A Low-Noise Chopper Amplifier Designed for Multi-Channel Neural Signal Acquisition. IEEE J. Solid State Circuits 2019, 54, 2255–2265. [Google Scholar] [CrossRef]

- Butti, F.; Piotto, M.; Bruschi, P. A Chopper Instrumentation Amplifier with Input Resistance Boosting by Means of Synchronous Dynamic Element Matching. IEEE Trans. Circuits Syst. I Regul. Pap. 2017, 64, 753–794. [Google Scholar] [CrossRef]

| This Work | [5] | [10] | [16] | [17] | [18] | [19] | [20] | [21] | |

|---|---|---|---|---|---|---|---|---|---|

| Technology (µm) | 0.18 | 0.18–0.5 | 0.7 | 0.7 | 0.3–0.6 | 0.35 | 0.18 | 0.18 | 0.32 |

| Multi-path | Y | N | N | Y | N | Y | N | N | N |

| Power (µW) | 174 | 25.9 | 1150 | 715 | 27 | 3675 | 74 | 3.24 | 561 |

| DC gain | >137 | 168 | - | 100 | >130 | 150 | 100 | - | 201.2 |

| UGBW * | 3.16M | 260k | 800k | 1.8M | 350k | 4M | 2k | - | 40k |

| CMRR (dB) | >125 | 124 | >120 | 137 | - | - | >120 | 100 | >120 |

| PSRR (dB) | >100 | 120 | >120 | 120 | - | - | - | >70 | 115 |

| Input referred offset (µV) | 1.99 | 2 | 5 | 1 | 3 | 0.78 | 1.78 | - | 2 |

| Input referred noise (nV/√Hz) | 11.8 | 37 | 15 | 10.5 | 55 | 5.9 | 1.8 | 45.9 | 18 |

| Chip Area (mm2) | 1.18 | 1.14 | 4.8 | 1.8 | 0.7 | 1.26 | 0.12 | 0.2 | 0.57 |

| NEF ** | 4.4 | 5.5 | 8.8 | 4.8 | 8.1 | 8.4 | 17 | 2.37 | 10.6 |

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Kim, J.; Kim, H.; Han, K.; You, D.; Heo, H.; Kwon, Y.; Cho, D.-i.“.; Ko, H. Low-Noise Chopper-Stabilized Multi-Path Operational Amplifier with Nested Miller Compensation for High-Precision Sensors. Appl. Sci. 2020, 10, 281. https://doi.org/10.3390/app10010281

Kim J, Kim H, Han K, You D, Heo H, Kwon Y, Cho D-i“, Ko H. Low-Noise Chopper-Stabilized Multi-Path Operational Amplifier with Nested Miller Compensation for High-Precision Sensors. Applied Sciences. 2020; 10(1):281. https://doi.org/10.3390/app10010281

Chicago/Turabian StyleKim, Jaesung, Hyungseup Kim, Kwonsang Han, Donggeun You, Hyunwoo Heo, Yongsu Kwon, Dong-il “Dan” Cho, and Hyoungho Ko. 2020. "Low-Noise Chopper-Stabilized Multi-Path Operational Amplifier with Nested Miller Compensation for High-Precision Sensors" Applied Sciences 10, no. 1: 281. https://doi.org/10.3390/app10010281

APA StyleKim, J., Kim, H., Han, K., You, D., Heo, H., Kwon, Y., Cho, D.-i. “., & Ko, H. (2020). Low-Noise Chopper-Stabilized Multi-Path Operational Amplifier with Nested Miller Compensation for High-Precision Sensors. Applied Sciences, 10(1), 281. https://doi.org/10.3390/app10010281