Improvement of Power Converters Performance by an Efficient Use of Dead Time Compensation Technique

Abstract

1. Introduction

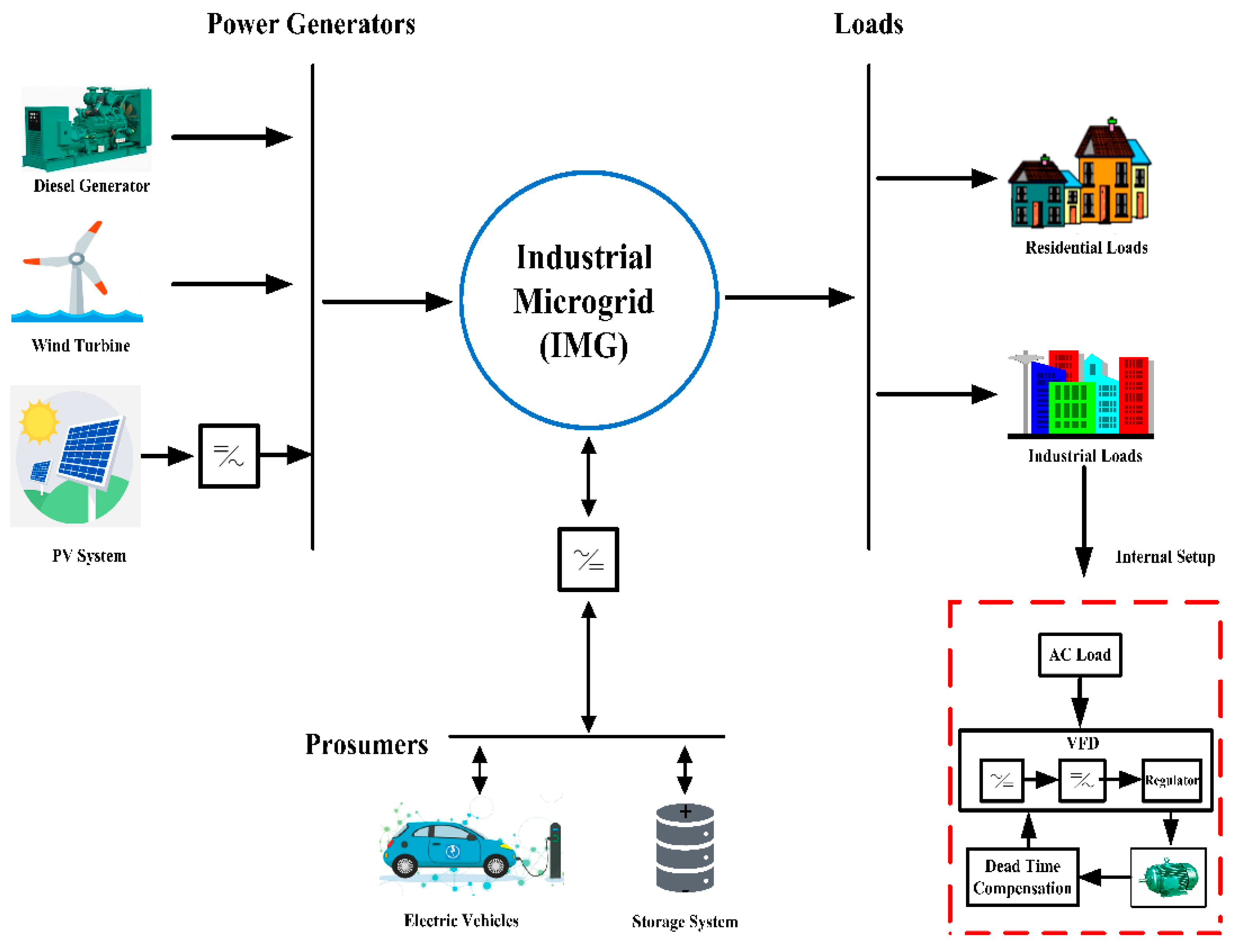

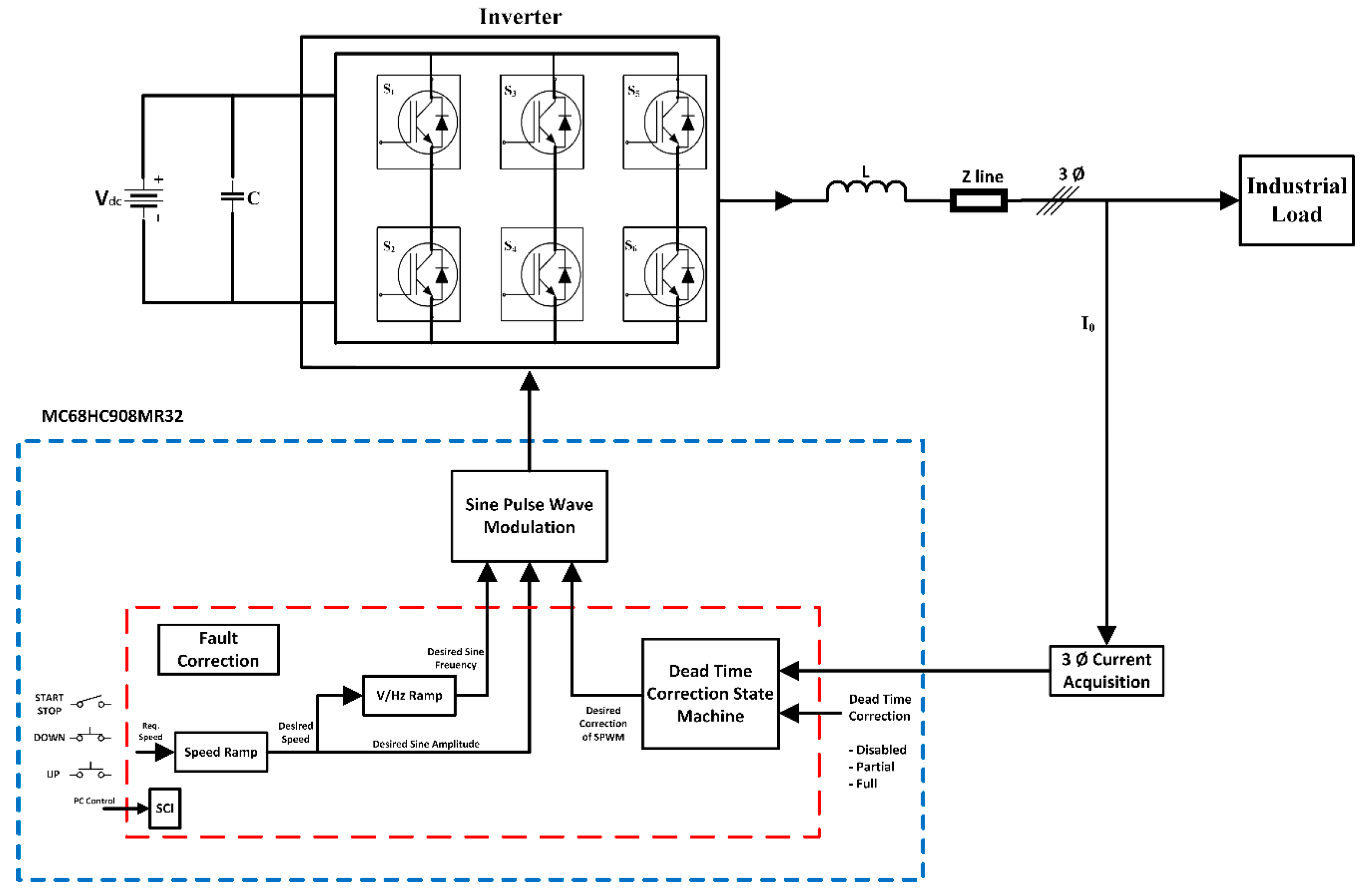

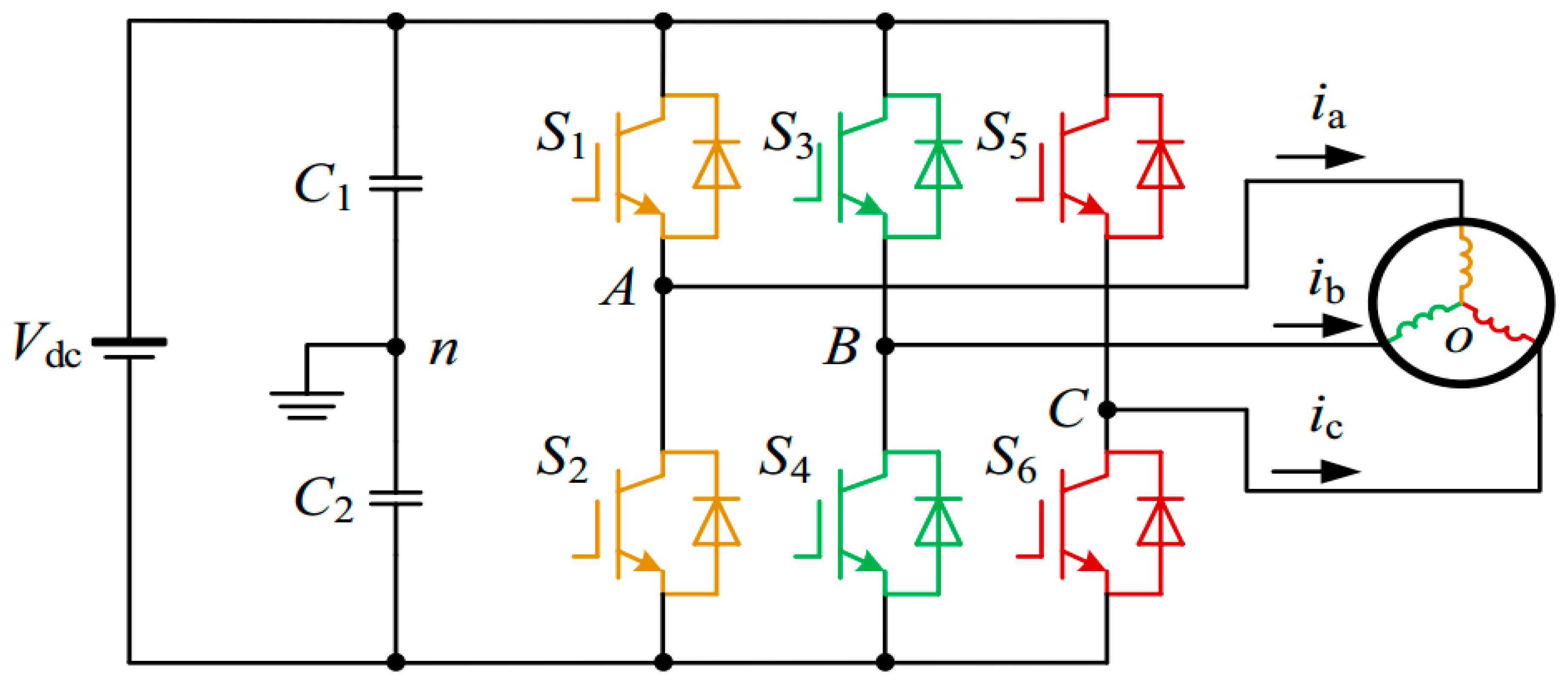

2. System Modeling

3. Proposed Dead Time Compensation Technique

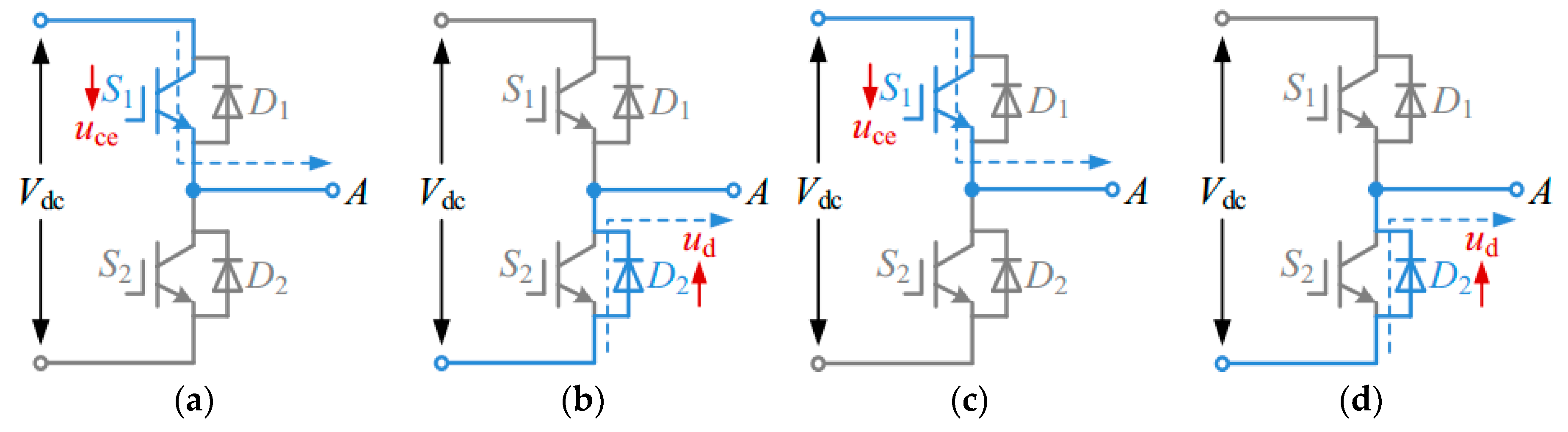

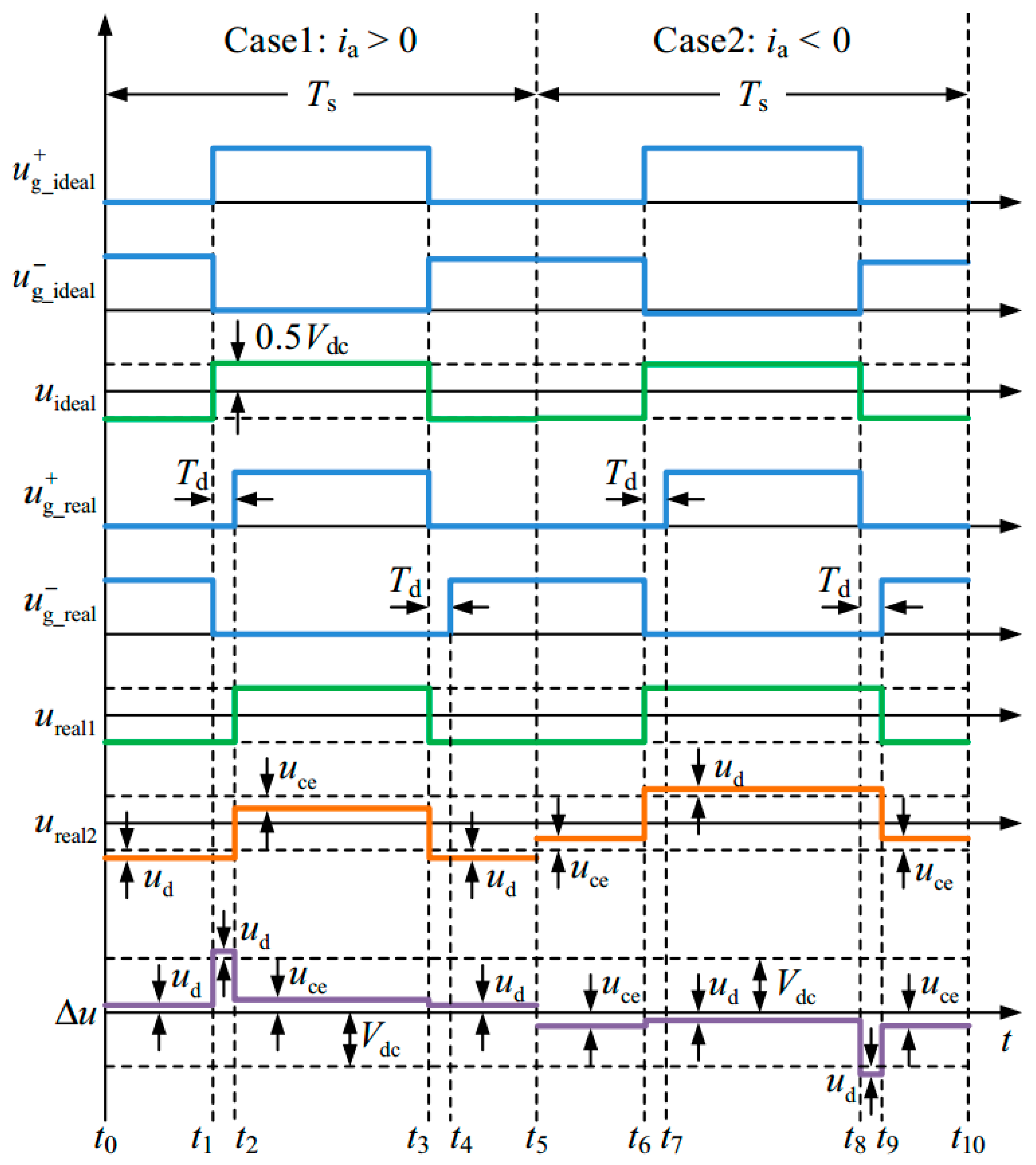

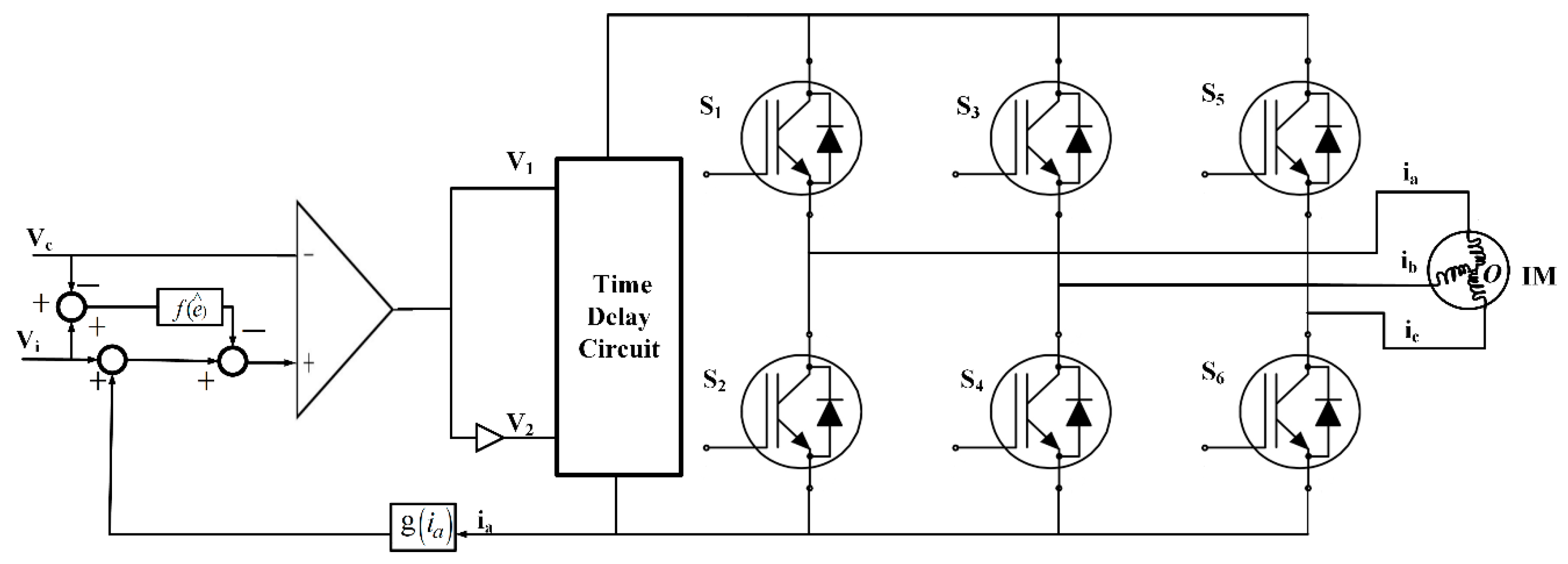

3.1. Dead-Time Compensation for PWM Inverter

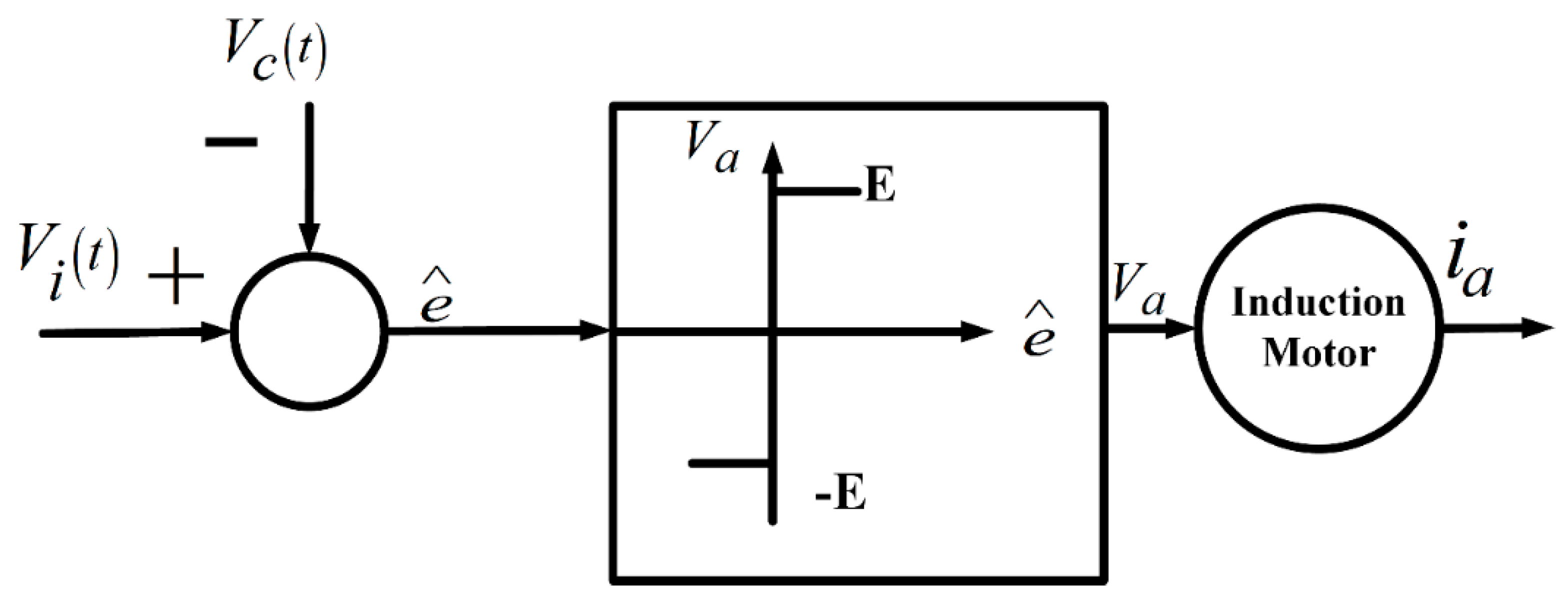

3.2. Modeling of the Proposed Dead Time Compensation

4. Results and Discussion

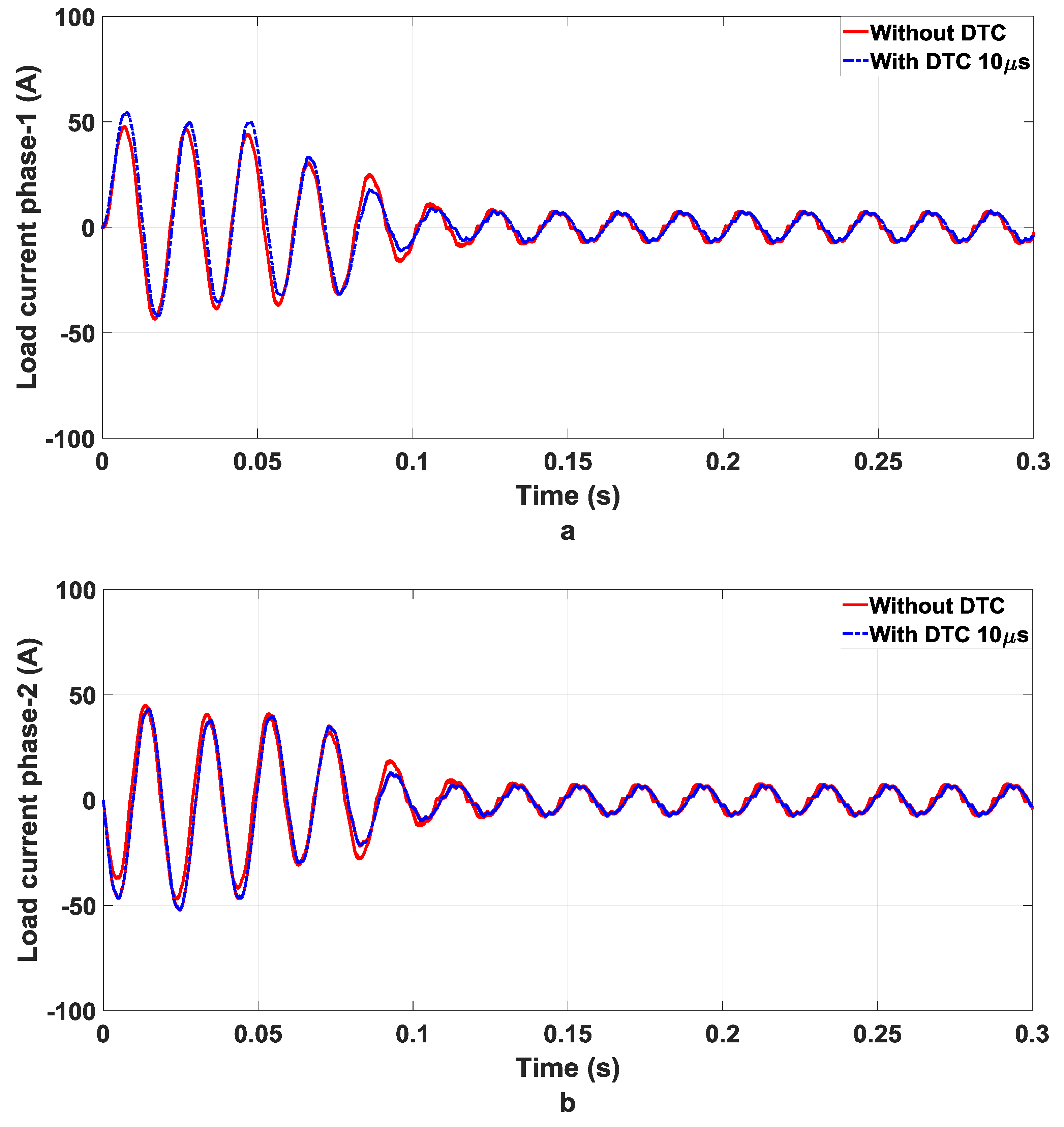

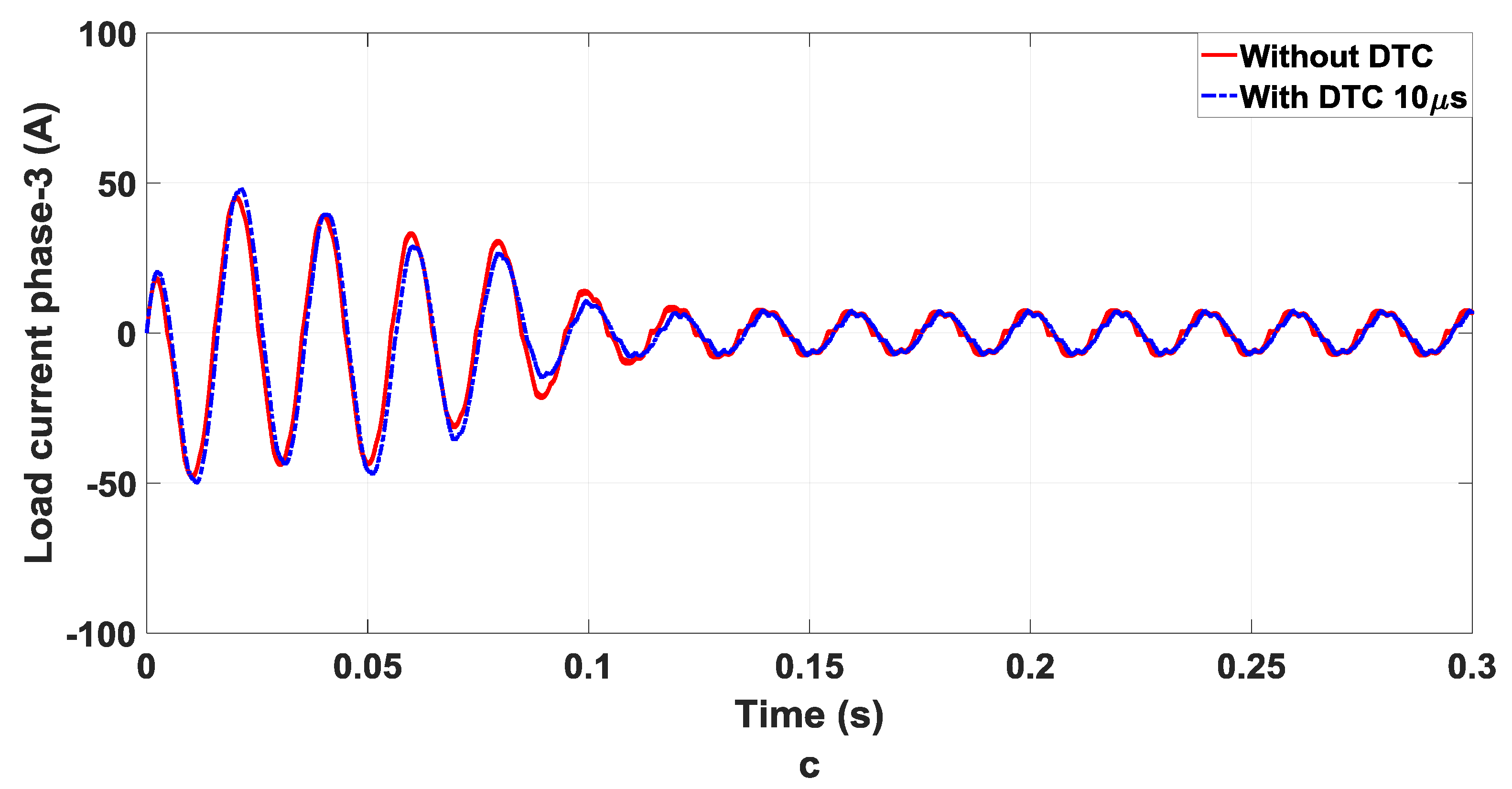

4.1. Impact of Dead Time on Load Current Waveform

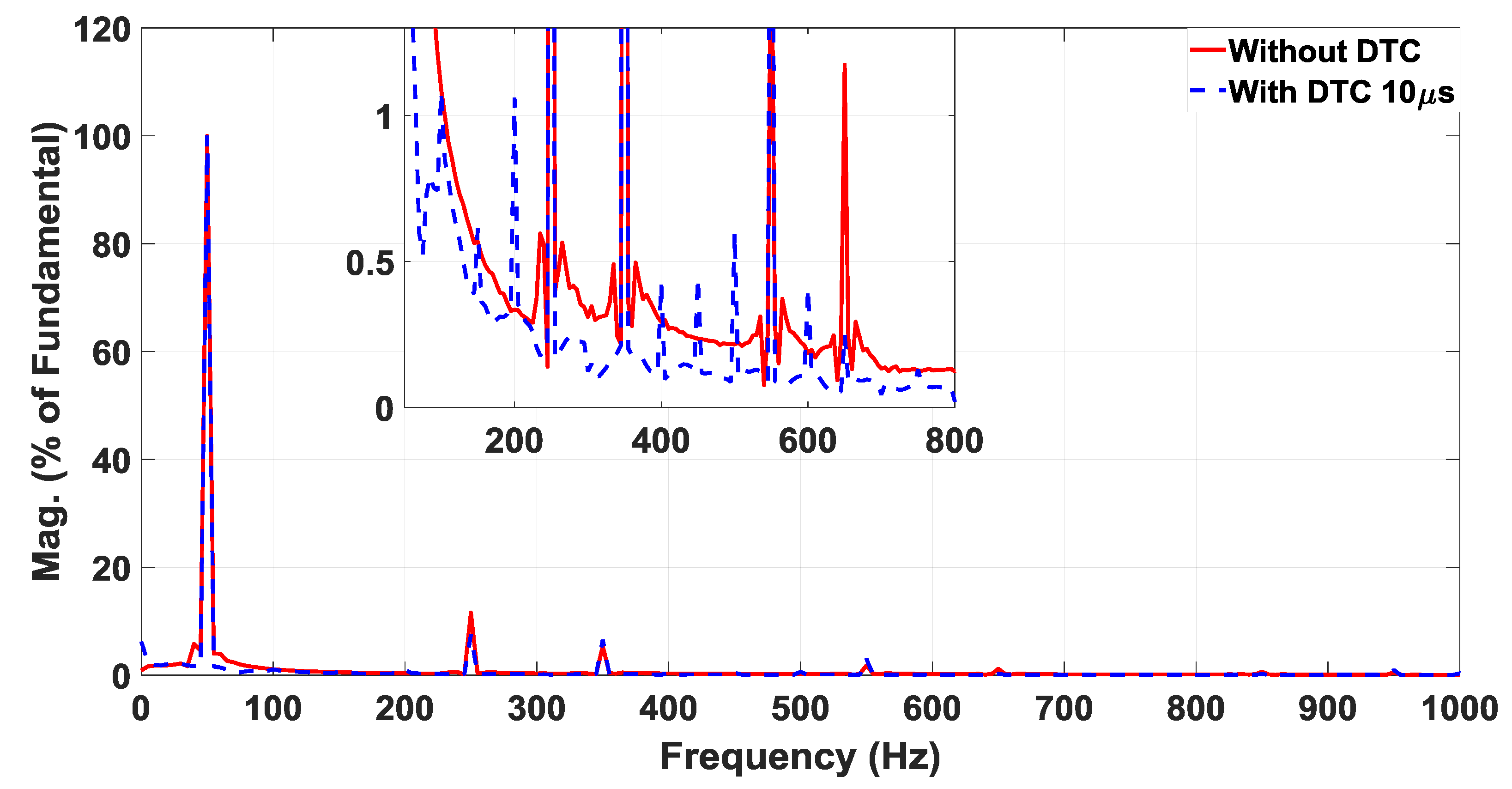

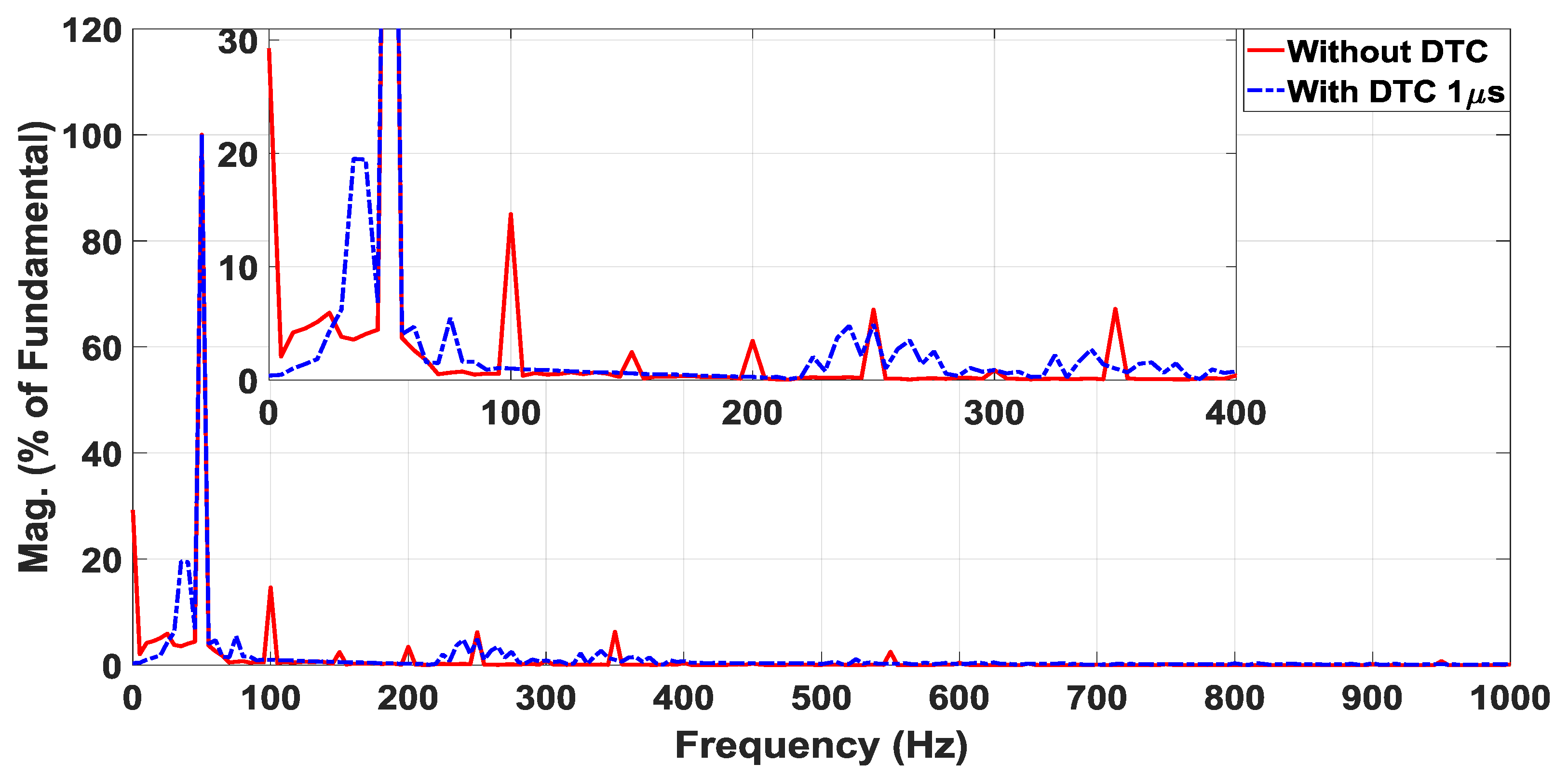

4.2. Total Harmonics and Individual Harmonics Distortions Calculation by FFT Analysis

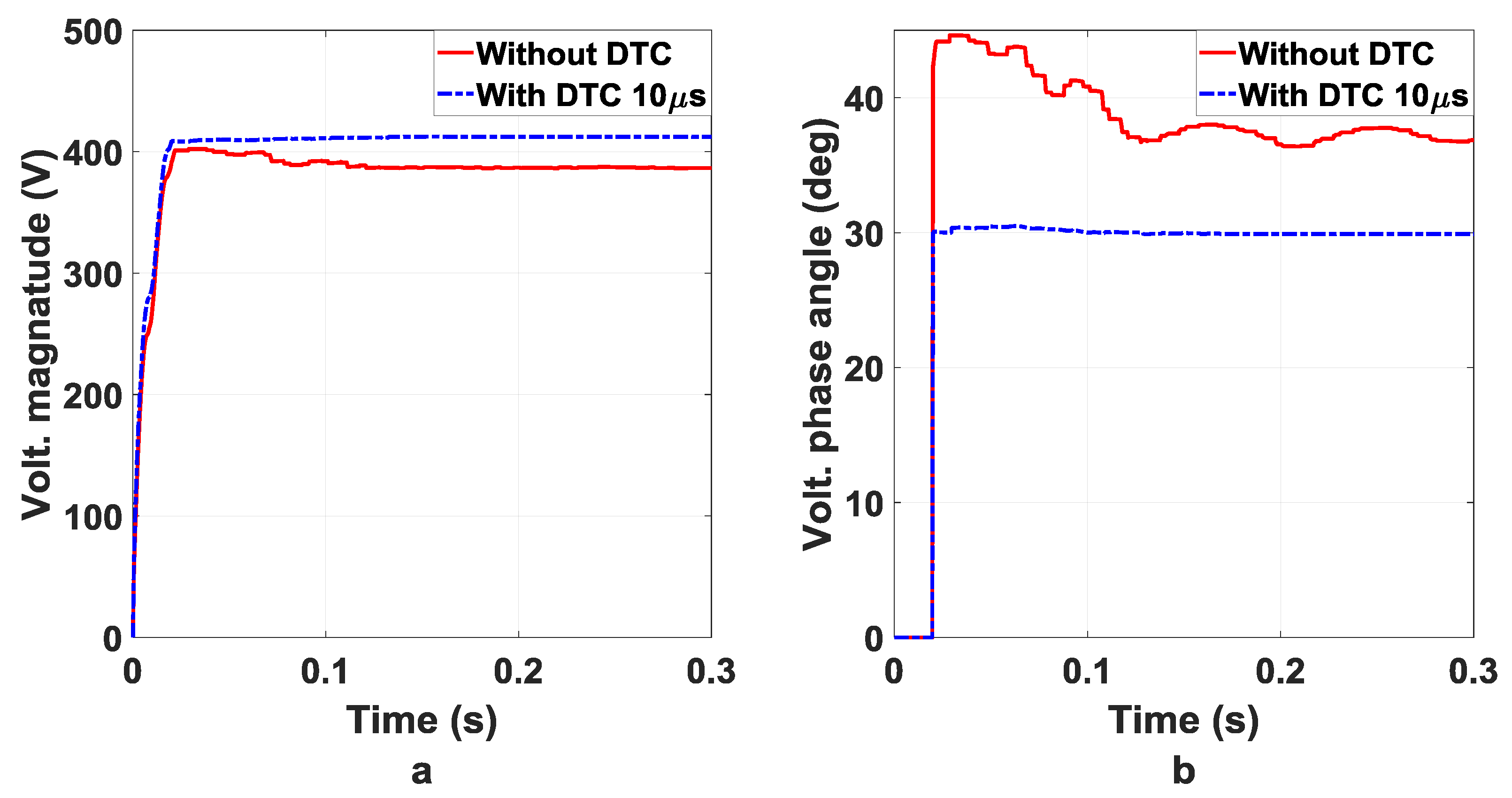

4.3. Improvement in Fundamental Voltage Magnitude and Phase Angle

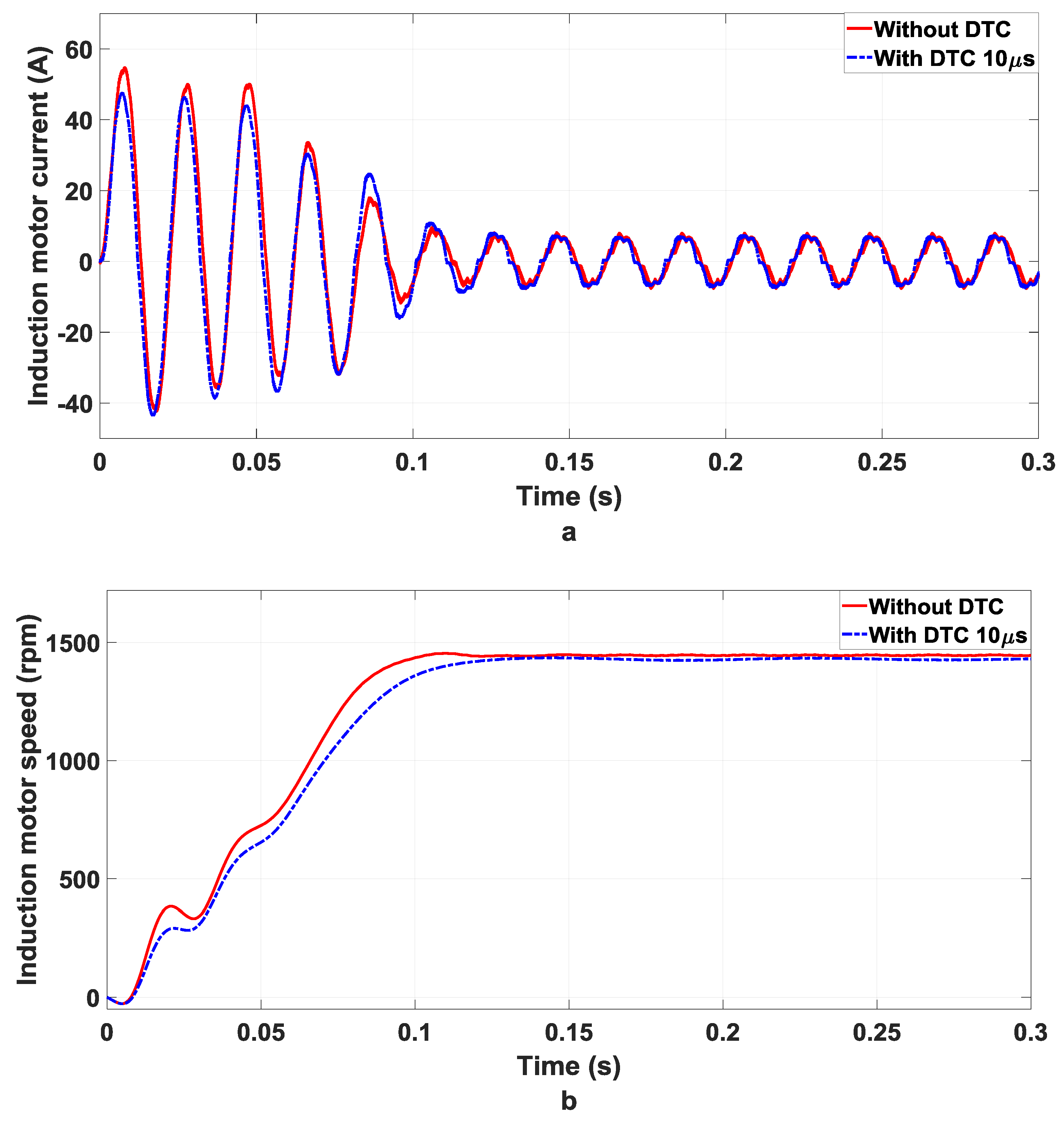

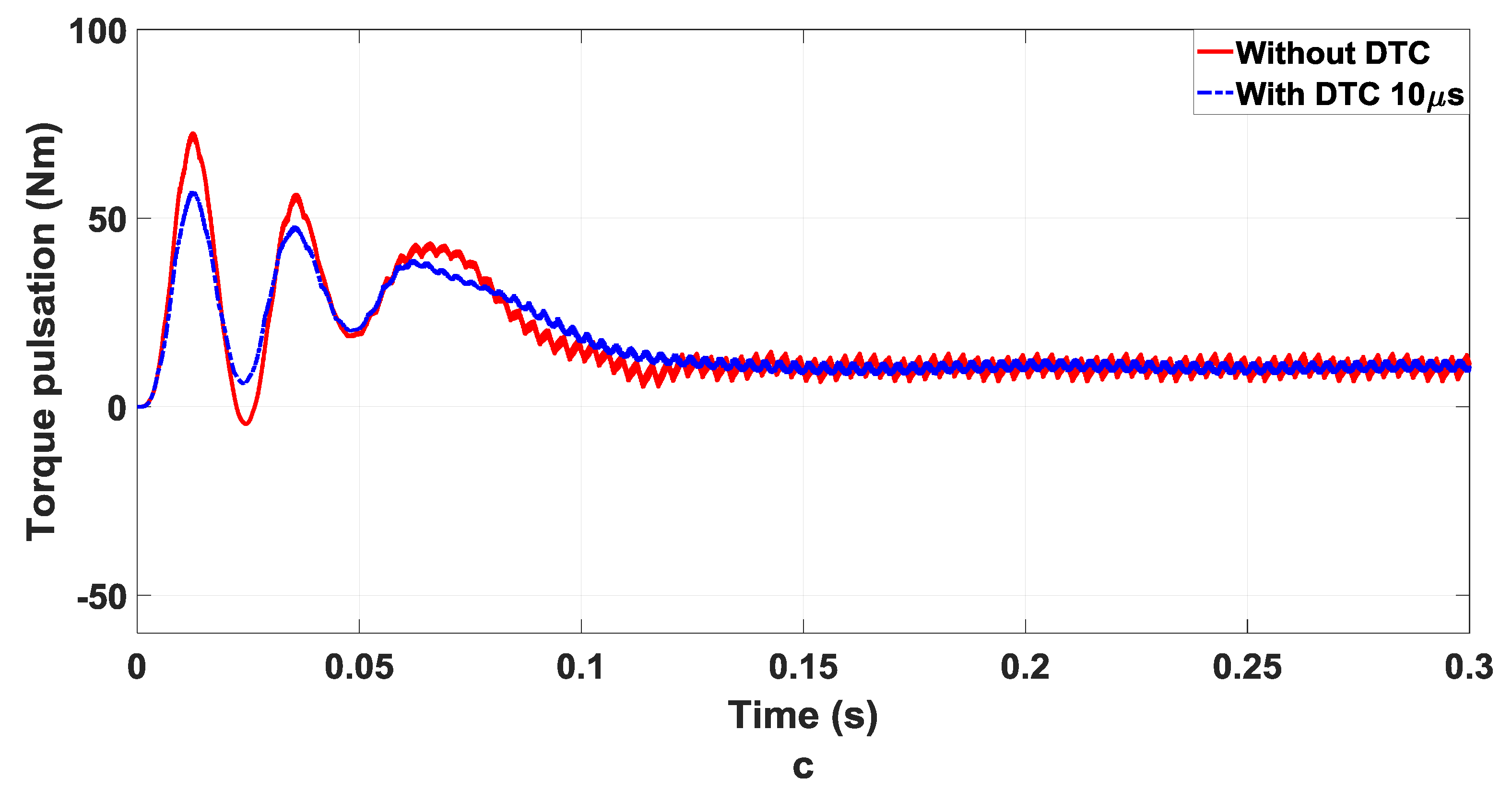

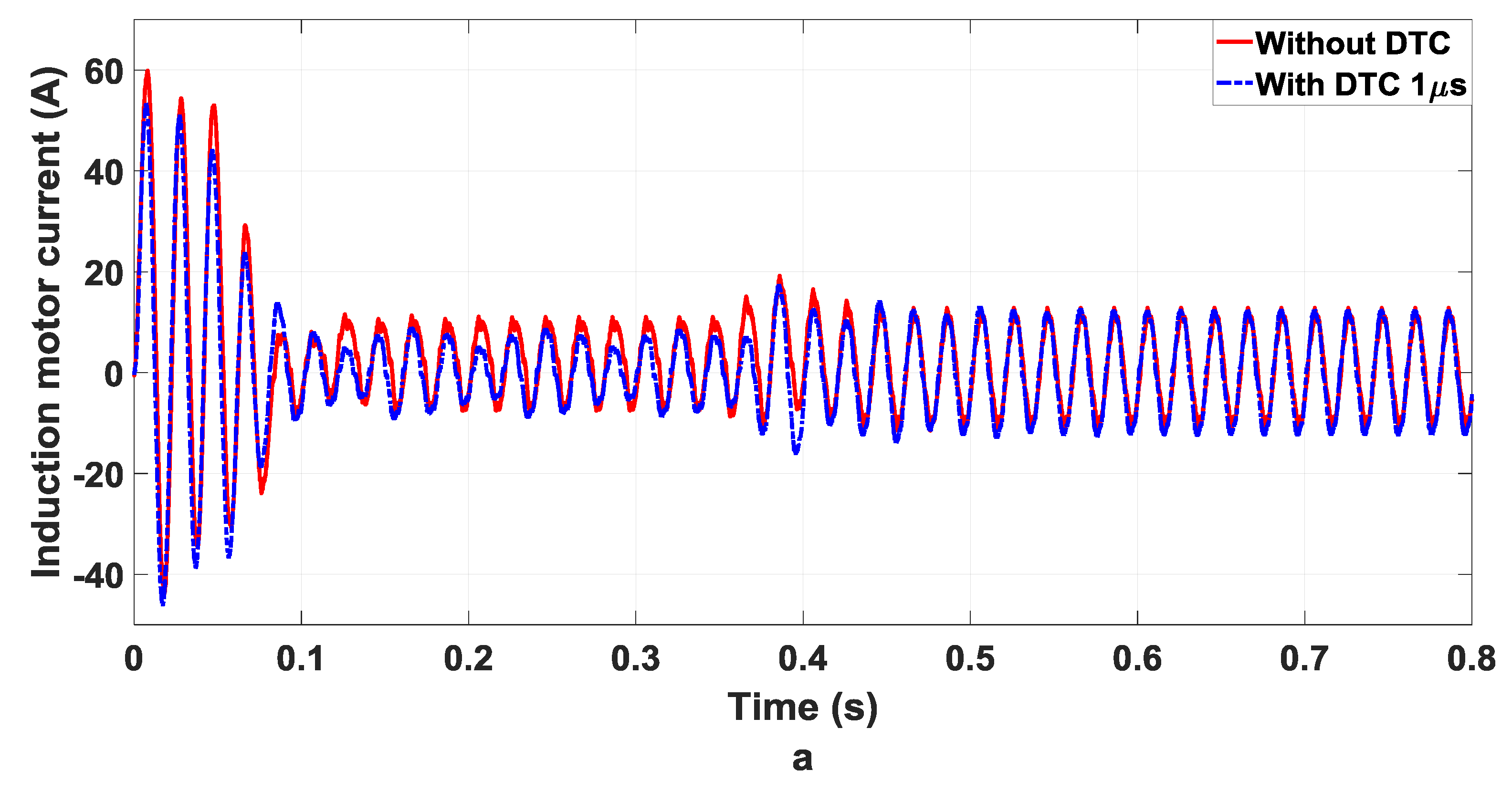

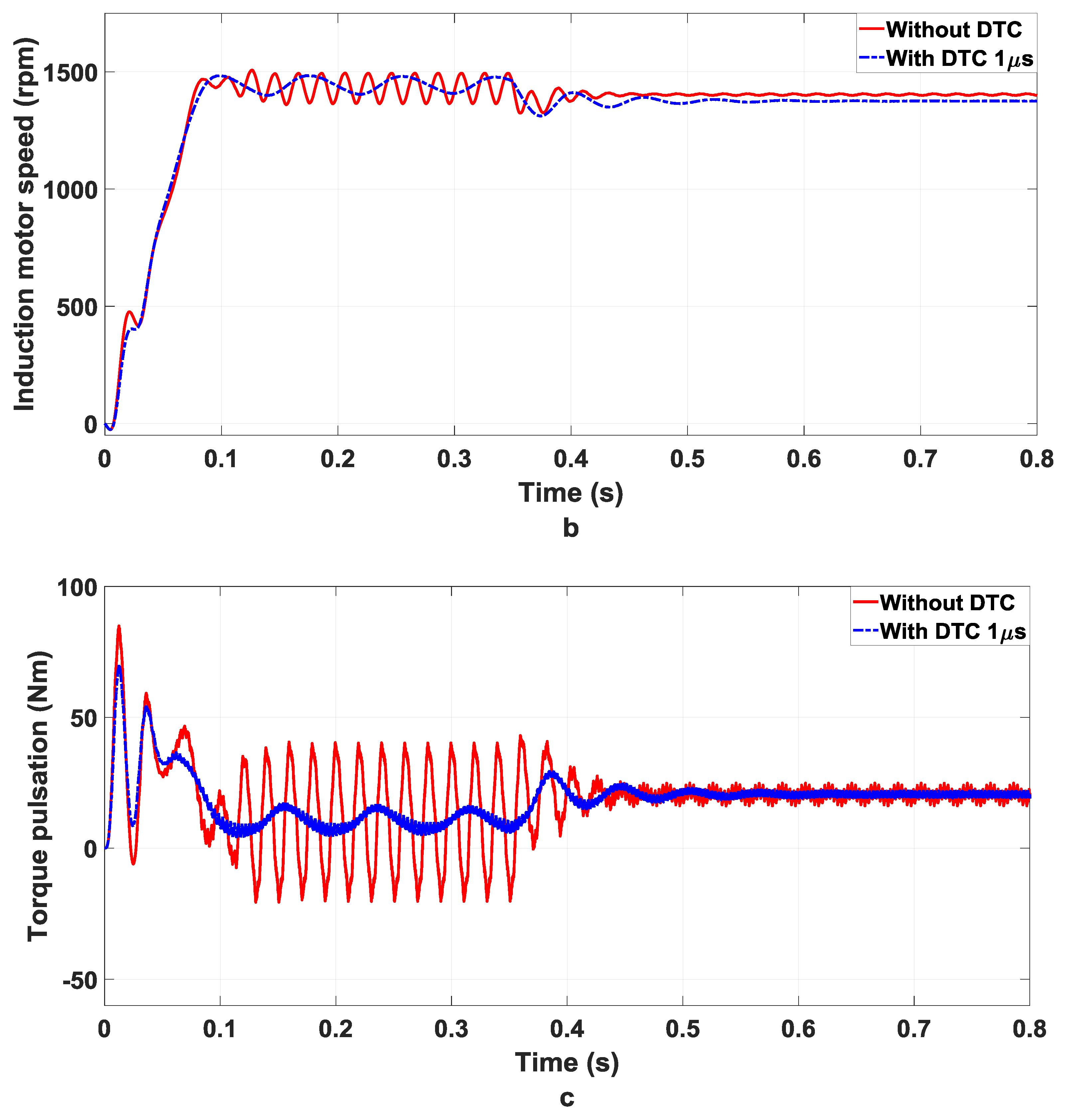

4.4. Improvement in Power Quality Parameters of Induction Motor

4.5. Case 2: Dead-Time 1 sec and Switching Frequency 1 kHz

5. Conclusions

- (a)

- Sinusoidal load current waveform has been achieved by applying dead time compensation, leading to the removal of distortions accruing from harmonics

- (b)

- Fundamental voltage magnitude has been significantly restored through the proposed DTC implementation.

- (c)

- The phase angle has been improved through the proposed DTC strategy. Additionally, the third harmonic distortion has been significantly alleviated 3.77%, through the proposed DTC strategy in Case 1 and 3.04% in Case 2.

- (d)

- Significant improvements have been achieved in the induction motor parameters post the DTC strategy application. Parameters like torque pulsation, speed, and THD which cause hindrance in smooth motor operation have been demonstrably improved through the novel technique.

Author Contributions

Funding

Conflicts of Interest

References

- Nejabatkhah, F.; Li, Y.W.; Tian, H. Power quality control of smart hybrid AC/DC microgrids: An overview. IEEE Access 2019, 7, 52295–52318. [Google Scholar] [CrossRef]

- Aziz, T.; Ahmed, M.; Nahid-Al-Masood. Investigation of harmonic distortions in photovoltaic integrated industrial microgrid. J. Renew. Sustain. Energy 2018, 10, 053507. [Google Scholar] [CrossRef]

- Abdelbaky, M.A.; Liu, X.; Jiang, D. Design and implementation of partial offline fuzzy model-predictive pitch controller for large-scale wind-turbines. Renew. Energy 2020, 145, 981–996. [Google Scholar] [CrossRef]

- Kong, X.; Ma, L.; Liu, X.; Abdelbaky, M.A.; Wu, Q. Wind Turbine Control Using Nonlinear Economic Model Predictive Control over All Operating Regions. Energies 2020, 13, 184. [Google Scholar] [CrossRef]

- Iqbal, S.; Xin, A.; Jan, M.U.; Salman, S.; Zaki, A.u.M.; Rehman, H.U.; Shinwari, M.F.; Abdelbaky, M.A. V2G Strategy for Primary Frequency Control of an Industrial Microgrid Considering the Charging Station Operator. Electronics 2020, 9, 549. [Google Scholar] [CrossRef]

- Gandoman, F.H.; Ahmadi, A.; Sharaf, A.M.; Siano, P.; Pou, J.; Hredzak, B.; Agelidis, V.G. Review of FACTS technologies and applications for power quality in smart grids with renewable energy systems. Renew. Sustain. Energy Rev. 2018, 82, 502–514. [Google Scholar] [CrossRef]

- Belov, V.; Butkina, A.; Bolschikov, F.; Leisner, P.; Belov, I. Power quality and EMC solutions in micro grids with energy-trading capability. In Proceedings of the 2014 International Symposium on Electromagnetic Compatibility, Gothenburg, Sweden, 1–4 September 2014; pp. 1203–1208. [Google Scholar]

- Standard IEC 61000-2-2. Electromagnetic Compatibility (EMC)-Part 2-2: Environment-Compatibility Levels for Low-Frequency Conducted Disturbances and Signalling in Public Low-Voltage Power Supply Systems; IEC: Geneva, Switzerland, 2002. [Google Scholar]

- Dong, H.; Yuan, S.; Han, Z.; Ding, X.; Ma, S.; Han, X. A comprehensive strategy for power quality improvement of multi-inverter-based microgrid with mixed loads. IEEE Access 2018, 6, 30903–30916. [Google Scholar] [CrossRef]

- Elbasuony, G.S.; Aleem, S.H.A.; Ibrahim, A.M.; Sharaf, A.M. A unified index for power quality evaluation in distributed generation systems. Energy 2018, 149, 607–622. [Google Scholar] [CrossRef]

- Martinenas, S.; Knezović, K.; Marinelli, M. Management of power quality issues in low voltage networks using electric vehicles: Experimental validation. IEEE Trans. Power Deliv. 2016, 32, 971–979. [Google Scholar] [CrossRef]

- Szczesniak, P. Challenges and design requirements for industrial applications of AC/AC power converters without DC-link. Energies 2019, 12, 1581. [Google Scholar] [CrossRef]

- Guha, A.; Narayanan, G. Small-signal stability analysis of an open-loop induction motor drive including the effect of inverter deadtime. IEEE Trans. Ind. Appl. 2015, 52, 242–253. [Google Scholar] [CrossRef]

- Guha, A.; Narayanan, G. Impact of undercompensation and overcompensation of dead-time effect on small-signal stability of induction motor drive. IEEE Trans. Ind. Appl. 2018, 54, 6027–6041. [Google Scholar] [CrossRef]

- Lin, Y.-K.; Lai, Y.-S. Dead-time elimination of PWM-controlled inverter/converter without separate power sources for current polarity detection circuit. IEEE Trans. Ind. Electron. 2009, 56, 2121–2127. [Google Scholar]

- Dafang, W.; Bowen, Y.; Cheng, Z.; Chuanwei, Z. A feedback-type phase voltage compensation strategy based on phase current reconstruction for ACIM drives. IEEE Trans. Power Electron. 2013, 29, 5031–5043. [Google Scholar] [CrossRef]

- Shen, Z.; Jiang, D. Dead-time effect compensation method based on current ripple prediction for voltage-source inverters. IEEE Trans. Power Electron. 2018, 34, 971–983. [Google Scholar] [CrossRef]

- Lim, J.-W.; Bu, H.; Cho, Y. Novel Dead-Time Compensation Strategy for Wide Current Range in a Three-Phase Inverter. Electronics 2019, 8, 92. [Google Scholar] [CrossRef]

- Iqbal, S.; Xin, A.; Jan, M.U.; Rehman, H.; Salman, S.; Rizvi, S.A.A. Improvement in the Efficiency of Inverter Involved in Microgrid. In Proceedings of the 2018 2nd IEEE Conference on Energy Internet and Energy System Integration (EI2), Beijing, China, 20–22 October 2018; pp. 1–5. [Google Scholar]

- Huang, Z.-L.; Jiang, Z.; Li, Z.-H. Dead-time Compensation Strategy of Three Level Inverter Based on FFT. DEStech Trans. Eng. Technol. Res. 2019. [Google Scholar] [CrossRef]

- Zhao, L.; Song, W.; Feng, J. A Compensation Method of Dead-Time and Forward Voltage Drop for Inverter Operating at Low Frequency. J. Electr. Eng. Technol. 2019, 14, 781–794. [Google Scholar] [CrossRef]

- Ji, Y.; Yang, Y.; Zhou, J.; Ding, H.; Guo, X.; Padmanaban, S. Control strategies of mitigating dead-time effect on power converters: An overview. Electronics 2019, 8, 196. [Google Scholar] [CrossRef]

- Mousavi, S.Y.M.; Jalilian, A.; Savaghebi, M. Voltage unbalance compensation by a grid connected inverter using virtual impedance and admittance control loops. In Proceedings of the 2018 9th Annual Power Electronics, Drives Systems and Technologies Conference (PEDSTC), Tehran, Iran, 13–15 February 2018; pp. 174–179. [Google Scholar]

- Wang, D.; Peng, F.; Ye, J.; Yang, Y.; Emadi, A. Dead-time effect analysis of a three-phase dual-active bridge DC/DC converter. IET Power Electron. 2017, 11, 984–994. [Google Scholar] [CrossRef]

- Kim, D.-Y.; Won, I.-K.; Lee, J.-H.; Won, C.-Y. Efficiency improvement of synchronous boost converter with dead time control for fuel cell-battery hybrid system. J. Electr. Eng. Technol. 2017, 12, 1891–1901. [Google Scholar]

- Mora, A.; Juliet, J.; Santander, A.; Lezana, P. Dead-time and semiconductor voltage drop compensation for cascaded H-bridge converters. IEEE Trans. Ind. Electron. 2016, 63, 7833–7842. [Google Scholar] [CrossRef]

- Guo, J.; Gong, X.; Zhao, F.; Wen, X. A novel dead-time compensation strategy of three-level inverter. In Proceedings of the 2014 IEEE Conference and Expo Transportation Electrification Asia-Pacific (ITEC Asia-Pacific), Beijing, China, 31 August–3 September 2014; pp. 1–5. [Google Scholar]

- Sankaran, C. Power Quality; CRC press: Boca Raton, FL, USA, 2017. [Google Scholar]

| Time (T) | Ideal O/P Voltage/Actual Voltage | Ideal O/P Voltage | Actual O/P Voltage | Dead-Time Error |

|---|---|---|---|---|

| No | Parameters | Input Values |

|---|---|---|

| 1 | Reference Signal | 50 Hz |

| 2 | Carrier Signal | 5k Hz |

| 3 | Amplitude modulation Index | 0.8 |

| 4 | DC Voltage | 700 V |

| 5 | Time Delay | 10 μs |

| 6 | 1 | |

| 7 | 0.8 | |

| 8 | Load Resistance | 12.6 |

| 9 | Load inductor | 40 mH |

| No | Parameters | Rating |

|---|---|---|

| 1 | Nominal power of IM | 5.4 HP |

| 2 | The nominal voltage of induction motor | 400 V |

| 3 | Nominal frequency of induction motor | 50 Hz |

| 4 | Speed | 1430 rpm |

| 5 | Power factor | 0.8 |

| 6 | Rated torque | 10 Nm |

| Without DTC | With DTC 10 μs | |

|---|---|---|

| Fundamental Frequency (50 Hz) | 7.437 | 6.784 |

| Total harmonics distortion THD (%) | 16.26% | 12.49% |

| Without DTC | With DTC 1 μs | |

|---|---|---|

| Fundamental Frequency (50 Hz) | 8.227 | 6.714 |

| Total harmonics distortion THD (%) | 19.20% | 16.16% |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Iqbal, S.; Xin, A.; Jan, M.U.; Abdelbaky, M.A.; Rehman, H.U.; Salman, S.; Aurangzeb, M.; Rizvi, S.A.A.; Shah, N.A. Improvement of Power Converters Performance by an Efficient Use of Dead Time Compensation Technique. Appl. Sci. 2020, 10, 3121. https://doi.org/10.3390/app10093121

Iqbal S, Xin A, Jan MU, Abdelbaky MA, Rehman HU, Salman S, Aurangzeb M, Rizvi SAA, Shah NA. Improvement of Power Converters Performance by an Efficient Use of Dead Time Compensation Technique. Applied Sciences. 2020; 10(9):3121. https://doi.org/10.3390/app10093121

Chicago/Turabian StyleIqbal, Sheeraz, Ai Xin, Mishkat Ullah Jan, Mohamed Abdelkarim Abdelbaky, Haseeb Ur Rehman, Salman Salman, Muhammad Aurangzeb, Syed Asad Abbas Rizvi, and Noor Ahmad Shah. 2020. "Improvement of Power Converters Performance by an Efficient Use of Dead Time Compensation Technique" Applied Sciences 10, no. 9: 3121. https://doi.org/10.3390/app10093121

APA StyleIqbal, S., Xin, A., Jan, M. U., Abdelbaky, M. A., Rehman, H. U., Salman, S., Aurangzeb, M., Rizvi, S. A. A., & Shah, N. A. (2020). Improvement of Power Converters Performance by an Efficient Use of Dead Time Compensation Technique. Applied Sciences, 10(9), 3121. https://doi.org/10.3390/app10093121