Optimization Technique for High-Gain CMOS Power Amplifier for 5G Applications

Abstract

:1. Introduction

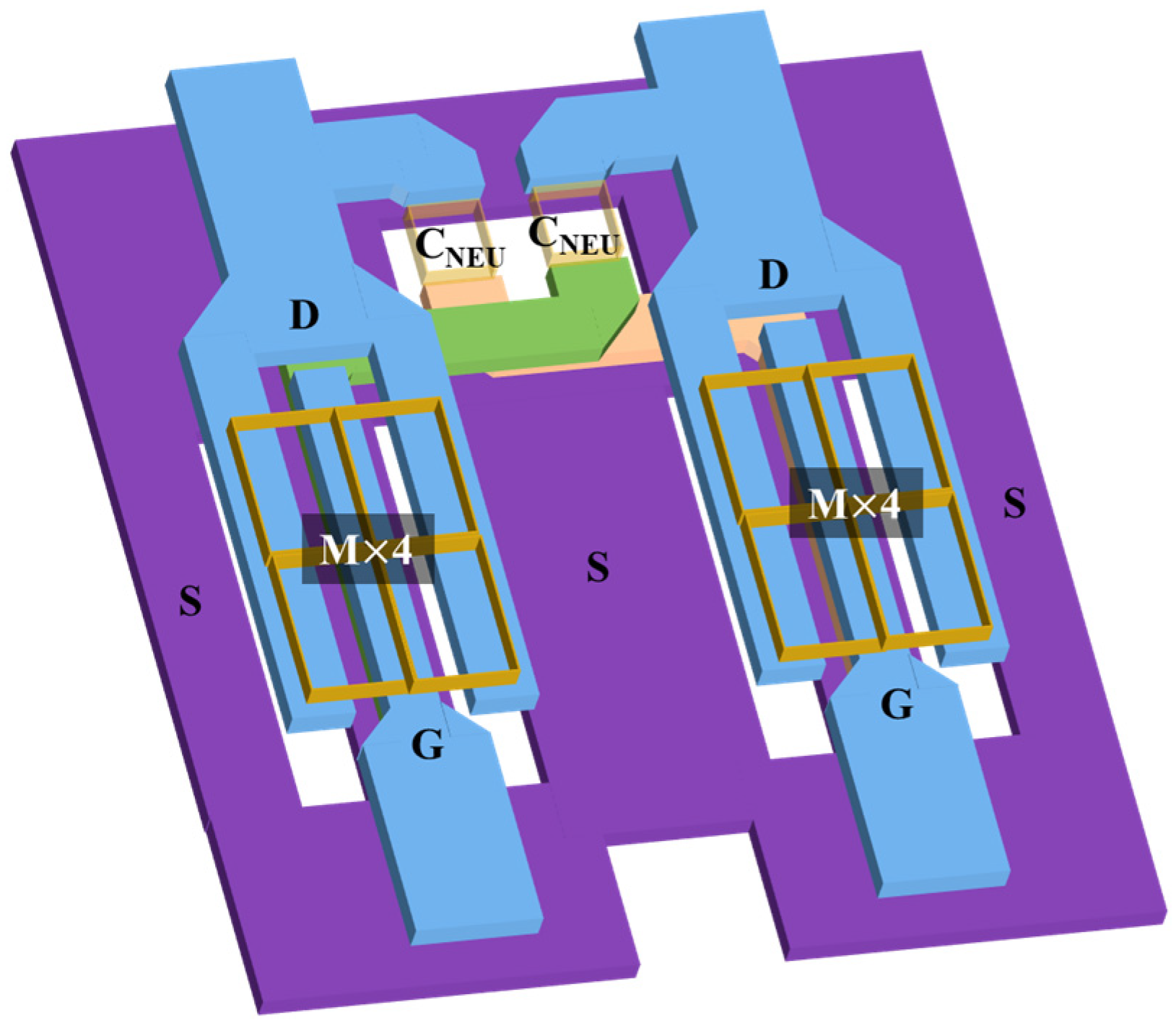

2. Design and Optimization of the Power Amplifier

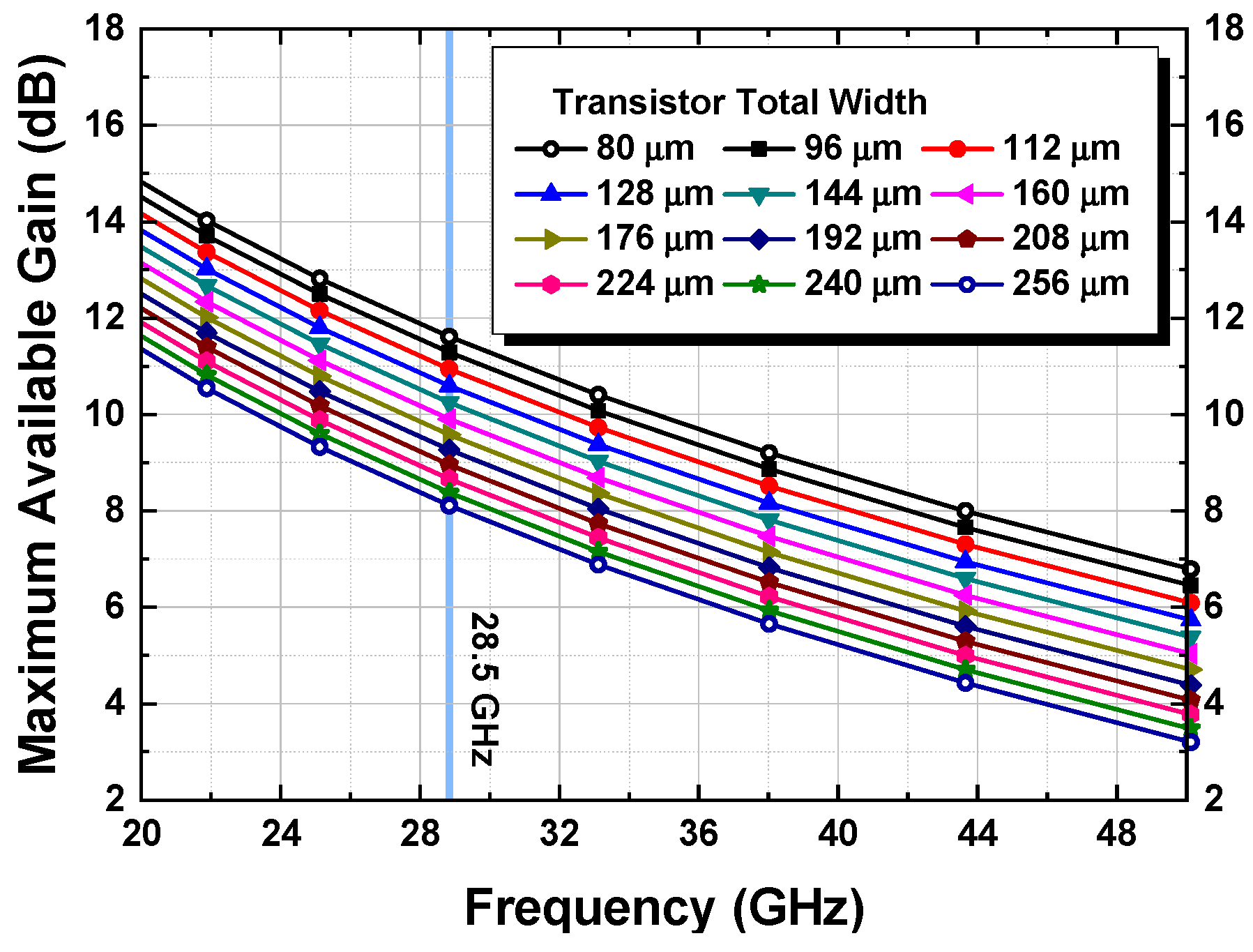

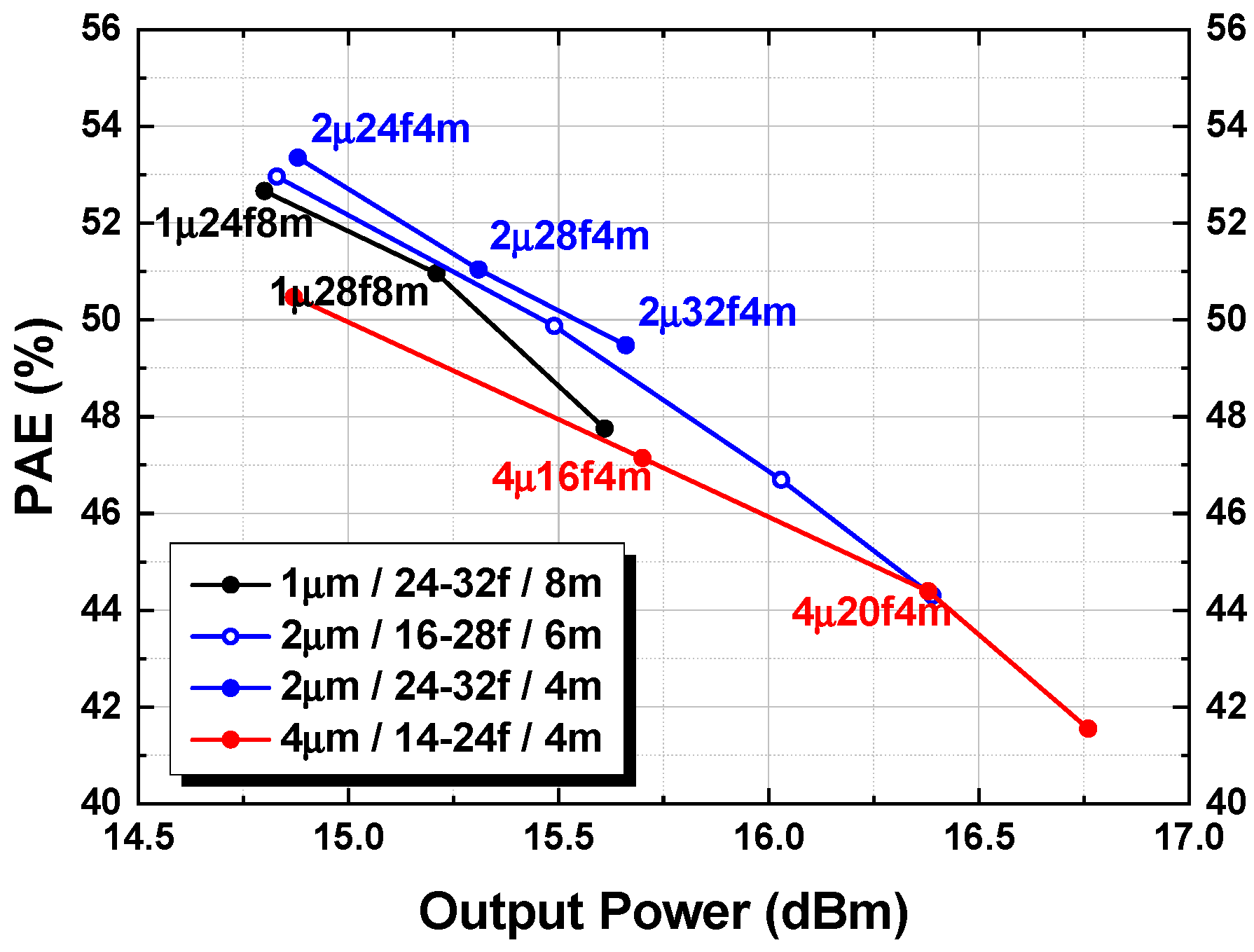

2.1. Size Determination of the Unit Amplifier Transistor

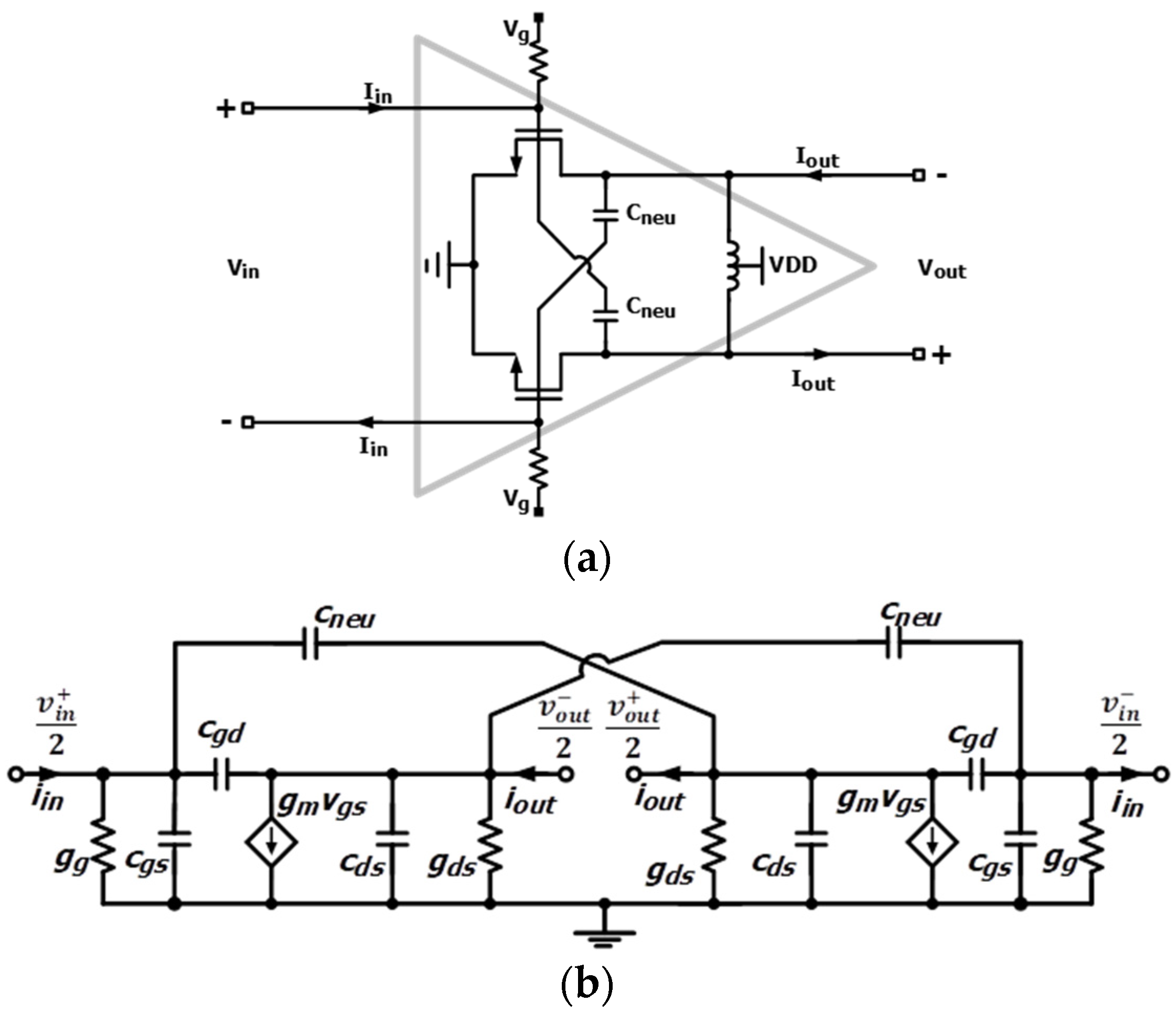

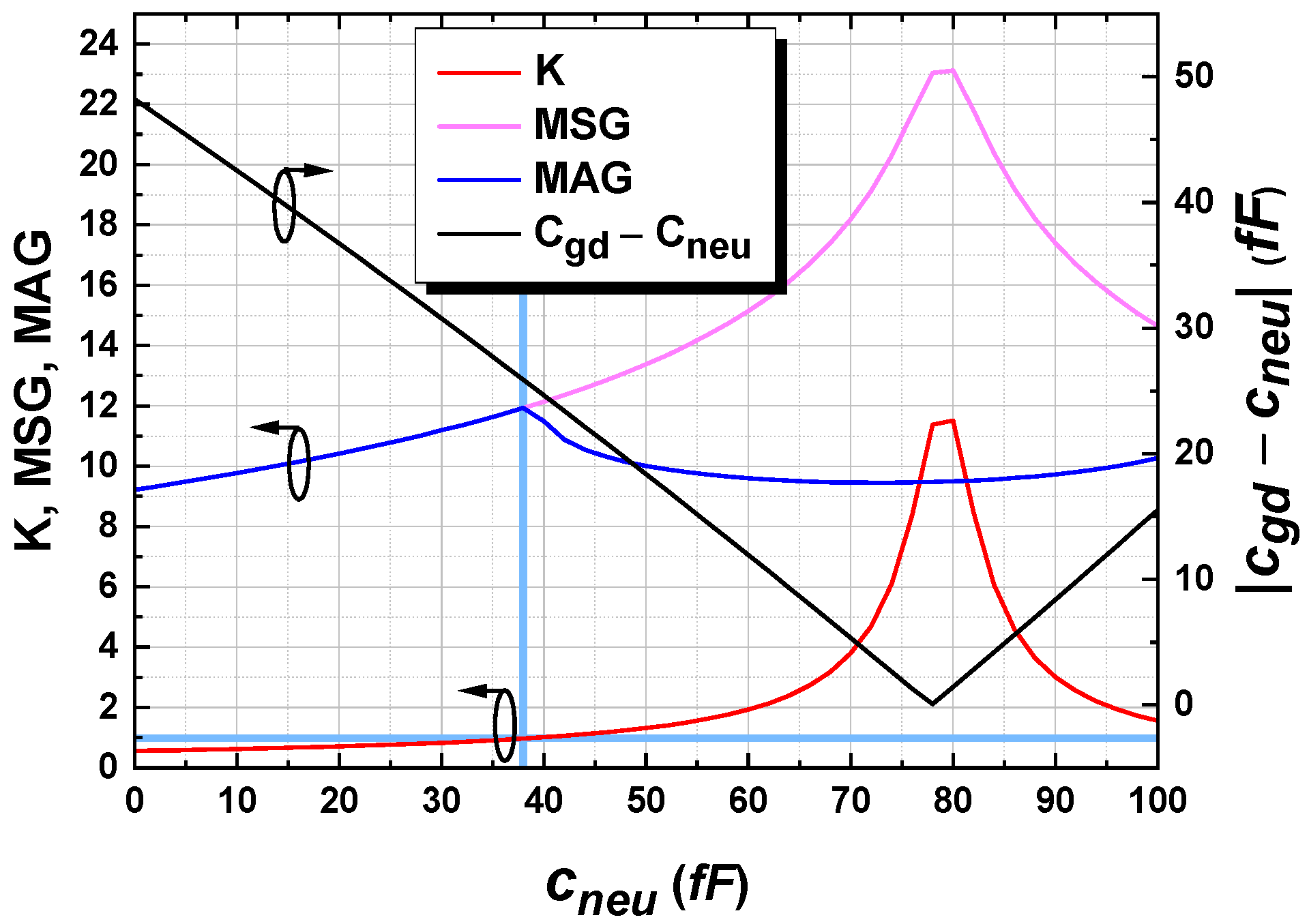

2.2. Size Determination and Analysis of the Neutralized Capacitor

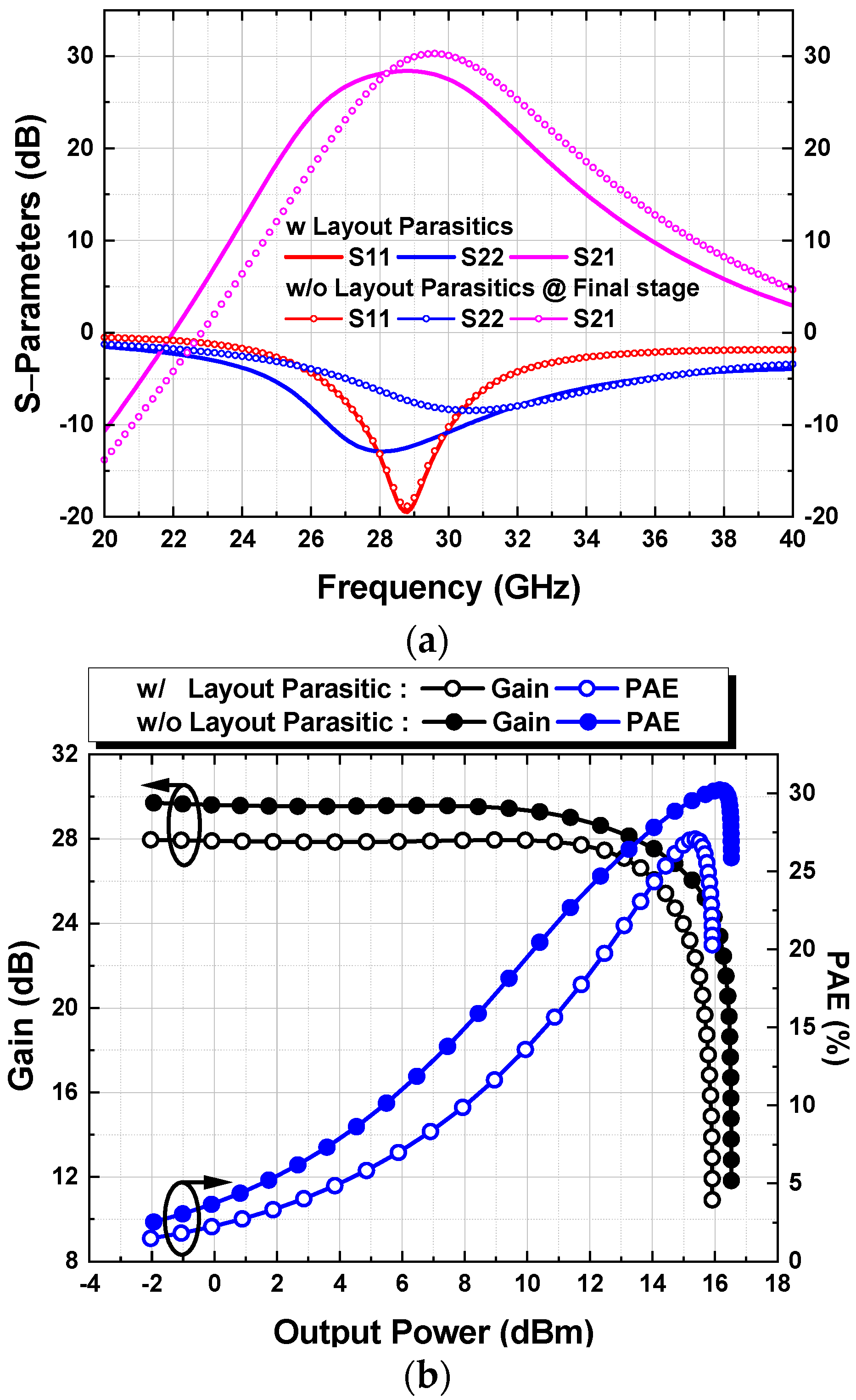

2.3. Analysis of Parasitices Caused by Power Cell Layout

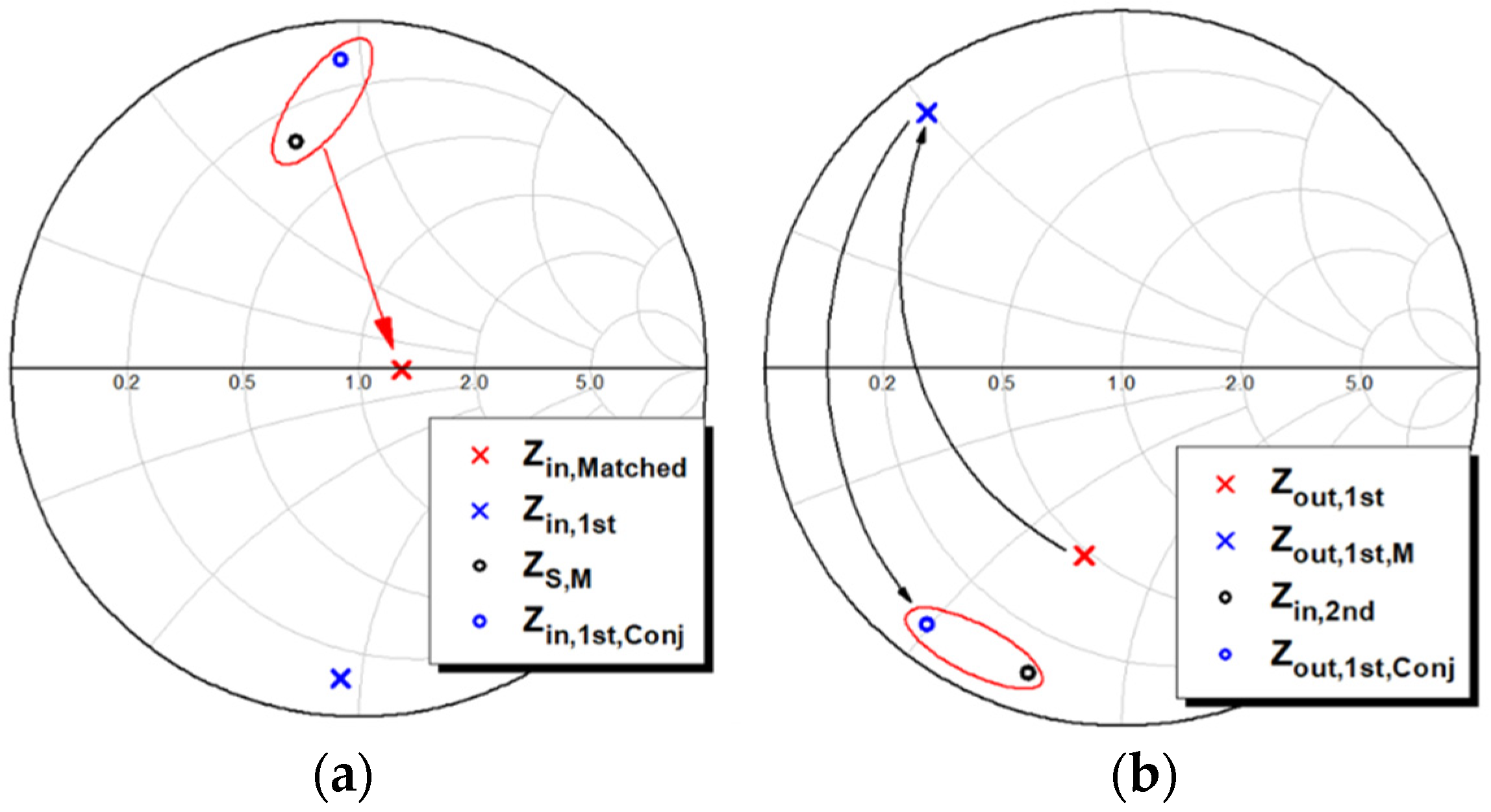

2.4. Configuration of Matching Network with Transformers

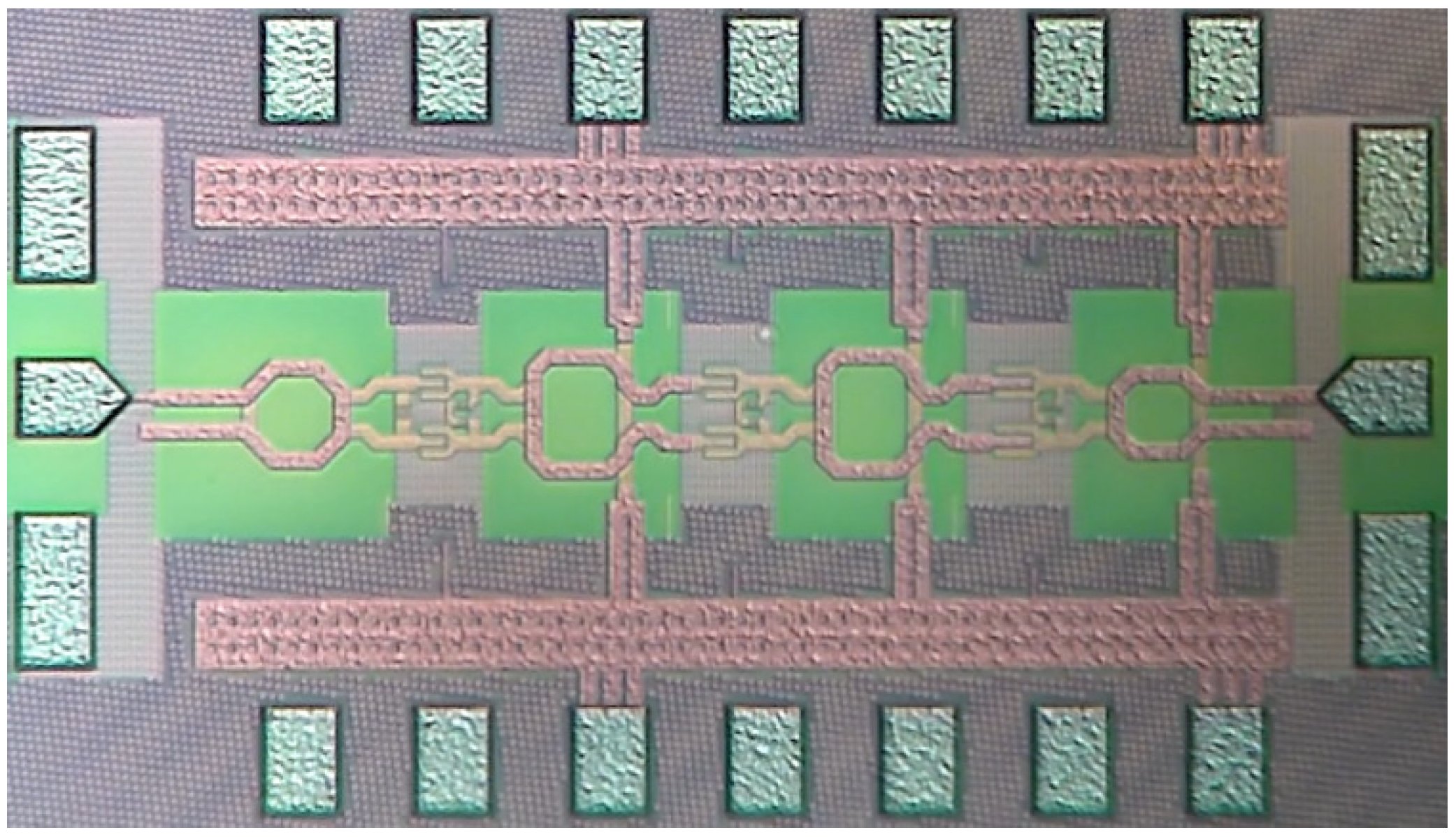

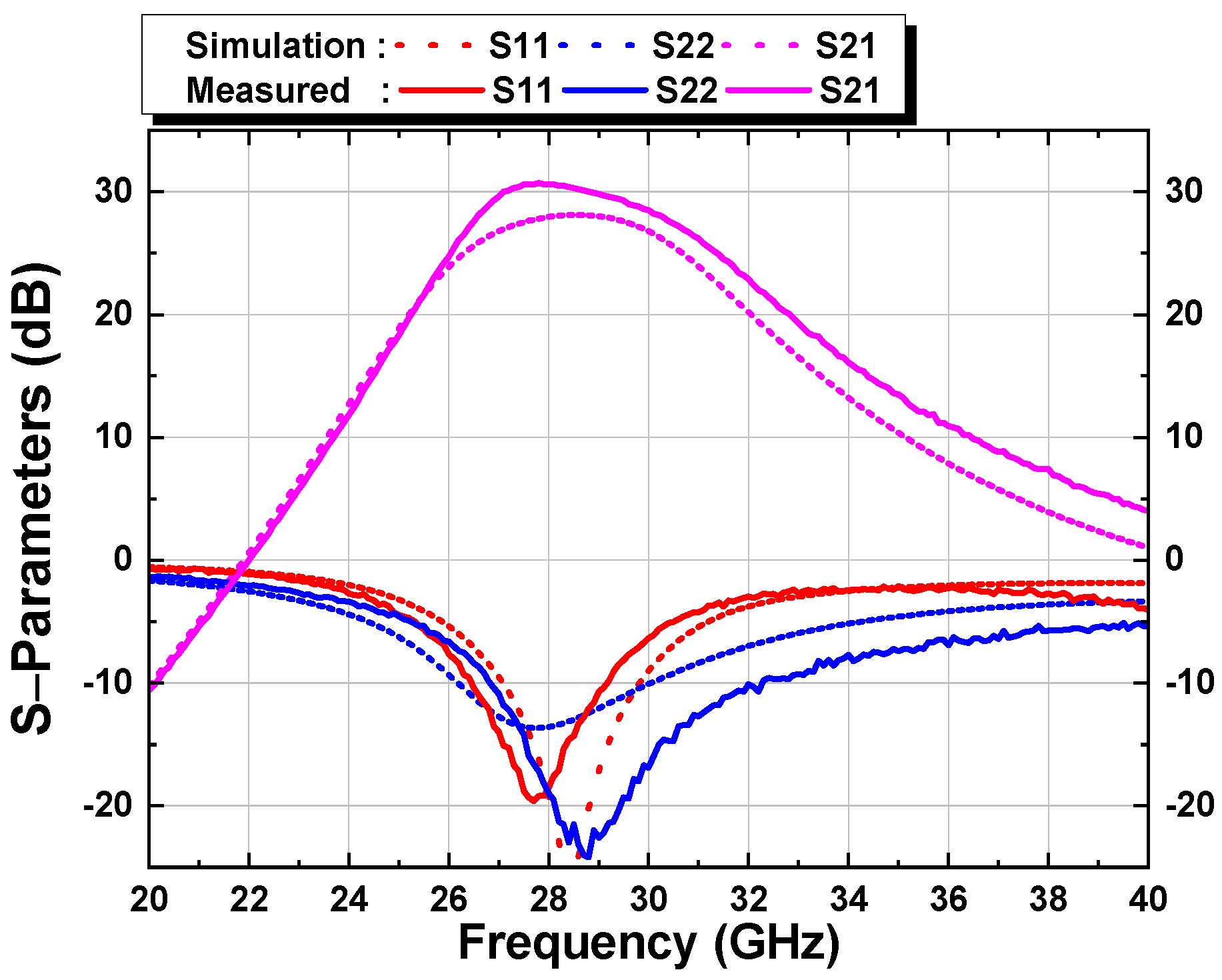

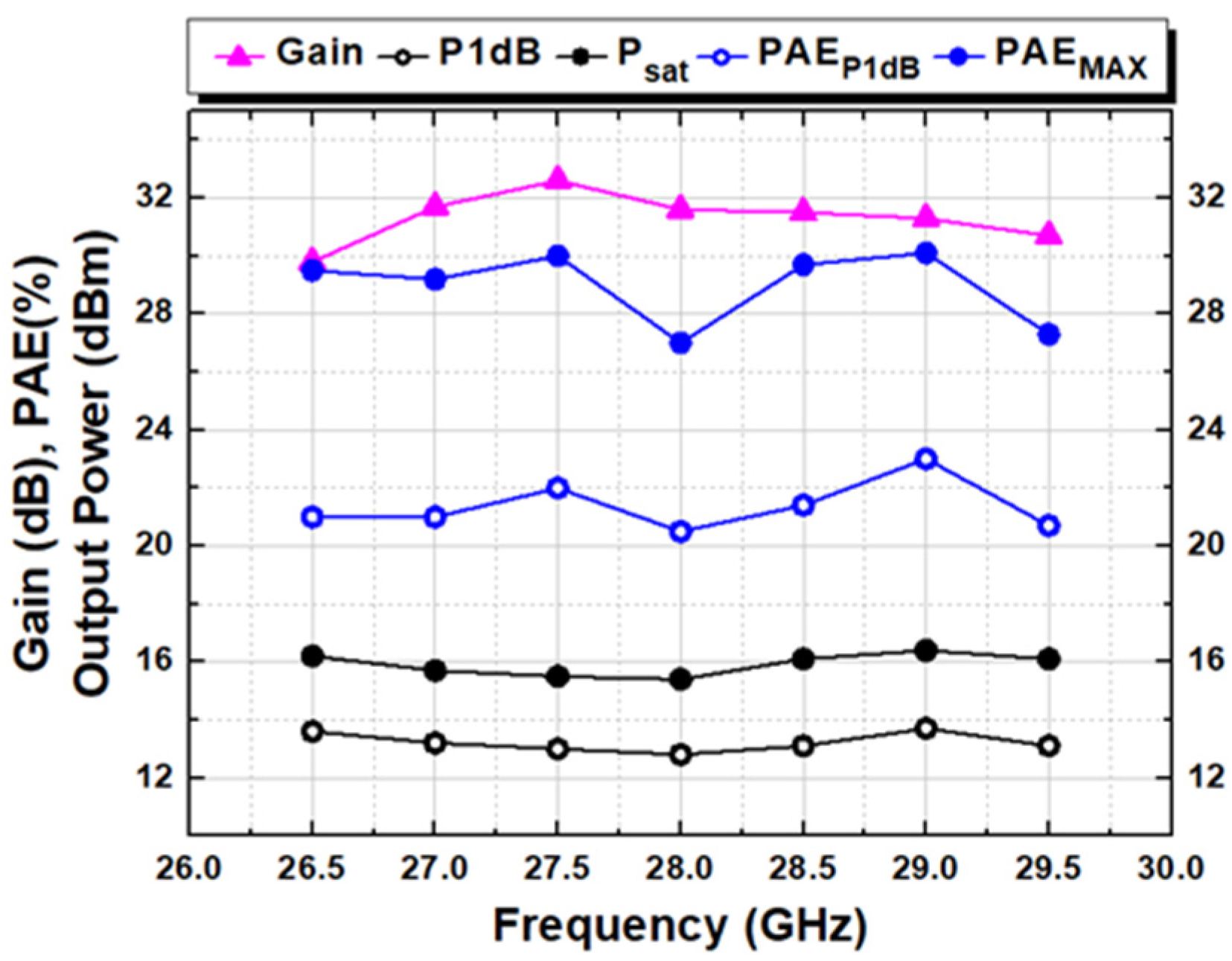

3. Measured Results

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Zong, Z.; Tang, X.; Khalaf, K.; Yan, D.; Mangraviti, G.; Nguyen, J.; Liu, Y.; Wambacq, P. A 28-GHz SOI-CMOS Doherty power amplifier with a compact transformer-based output combiner. IEEE Trans. Microw. Theory Tech. 2021, 69, 2795–2808. [Google Scholar] [CrossRef]

- Park, J.; Kang, S.; Hong, S. Design of a Ka-band cascode power amplifier linearized with cold-FET interstage matching network. IEEE Trans. Microw. Theory Tech. 2021, 69, 1429–1438. [Google Scholar] [CrossRef]

- Cho, G.; Jeong, G.; Hong, S. 28-GHz CMOS power amplifier linearized with resistive drain-body connection. IEEE Microw. Wirel. Compon. Lett. 2020, 30, 876–879. [Google Scholar] [CrossRef]

- Ding, B.; Yuan, S.; Zhao, C.; Tao, L.; Tian, T. A Ka band FMCW transceiver front-end with 2-GHz bandwidth in 65-nm CMOS. IEEE Trans. Circuits Syst. II Express Briefs 2019, 66, 212–216. [Google Scholar] [CrossRef]

- Jia, H.; Prawoto, C.C.; Chi, B.; Wang, Z.; Yue, C.P. A full Ka-band power amplifier with 32.9% PAE and 15.3-dBm power in 65-nm CMOS. IEEE Trans. Circuits Syst. I Regul. Pap. 2018, 65, 2657–2668. [Google Scholar] [CrossRef]

- Deferm, N.; Reynaert, P. CMOS at millimeter wave frequencies. In CMOS Front Ends for Millimeter Wave Wireless Communication Systems; Springer: Berlin/Heidelberg, Germany, 2015; pp. 13–25. [Google Scholar]

- Chen, Y.-C.; Lin, Y.-H.; Lin, J.-L.; Wang, H. A Ka-band transformer-based Doherty power amplifier for multi-Gb/s application in 90-nm CMOS. IEEE Microw. Wirel. Compon. Lett. 2018, 28, 1134–1136. [Google Scholar] [CrossRef]

- Indirayanti, P.; Reynaert, P. A 32-GHz 20-dBm PSAT transformer-based Doherty power amplifier for multi-Gb/s 5G applications in 28-nm bulk CMOS. In Proceedings of the 2017 IEEE Radio Frequency Integrated Circuits Symposium, Honolulu, HI, USA, 4–6 June 2017; pp. 45–48. [Google Scholar]

- Lee, J.; Hong, S. A 24–30 GHz 31.7% fractional bandwidth power amplifier with an adaptive capacitance linearizer. IEEE Trans. Circuits Syst. II Express Briefs 2021, 68, 1163–1167. [Google Scholar] [CrossRef]

- Manente, D.; Padovan, F.; Seebacher, D.; Bassi, M.; Bevilacqua, A. A 28-GHz stacked power amplifier with 20.7-dBm output P1dB in 28-nm bulk CMOS. IEEE Solid-State Circuits Lett. 2020, 3, 170–173. [Google Scholar] [CrossRef]

| Ref. | Tech. | Freq. (GHz) | Supply (V) | Psat (dBm) | P1dB (dBm) | Gain (dB) | Peak PAE (%) | Architecture |

|---|---|---|---|---|---|---|---|---|

| This work | 65 nm | 28.5 | 1.0 | 16.1 | 13.1 | 31.5 | 29.7 | Three-stage CS |

| TMTT’ 21 [2] | 65 nm | 31 | 2.2 | 17.1 | 15 | 18.9 | 38.2 | Two-stage Cascode |

| TCASII’ ‘21 [9] | 28 nm | 26 | 2.2 | 20.3 | 18.2 | 21.2 | 33.1 | Two-stage Cascode |

| SSCL’20 [10] | 28 nm | 28 | 1.8 | 21.5 | 20.7 | 20.4 | 26 | Two-Stacked Four way |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Jeong, H.; Lee, H.; Park, B.; Jang, S.; Kong, S.; Park, C. Optimization Technique for High-Gain CMOS Power Amplifier for 5G Applications. Appl. Sci. 2021, 11, 11691. https://doi.org/10.3390/app112411691

Jeong H, Lee H, Park B, Jang S, Kong S, Park C. Optimization Technique for High-Gain CMOS Power Amplifier for 5G Applications. Applied Sciences. 2021; 11(24):11691. https://doi.org/10.3390/app112411691

Chicago/Turabian StyleJeong, Hayeon, Huidong Lee, Bonghyuk Park, Seunghyun Jang, Sunwoo Kong, and Changkun Park. 2021. "Optimization Technique for High-Gain CMOS Power Amplifier for 5G Applications" Applied Sciences 11, no. 24: 11691. https://doi.org/10.3390/app112411691

APA StyleJeong, H., Lee, H., Park, B., Jang, S., Kong, S., & Park, C. (2021). Optimization Technique for High-Gain CMOS Power Amplifier for 5G Applications. Applied Sciences, 11(24), 11691. https://doi.org/10.3390/app112411691