An Energy-Efficient Strategy for Microcontrollers

Abstract

1. Introduction

- (1)

- Analytical models are designed to analyze the effect and overhead of different low power technologies.

- (2)

- A series of tests is conducted, and the power consumption of essential peripheral components shows its impact on energy consumption.

- (3)

- A method to compare and choose the optimal among different low-power technologies is proposed to apply low-power technology more appropriately and effectively.

2. Related Studies and Motivation

2.1. Related Work

2.2. Our Assumptions

3. Analytical Models

3.1. How Will Processor Clock Frequency Affect Energy Consumption?

3.2. How Will Overhead Affect Energy Consumption?

4. Experiments and Results

4.1. Measuring Methodology

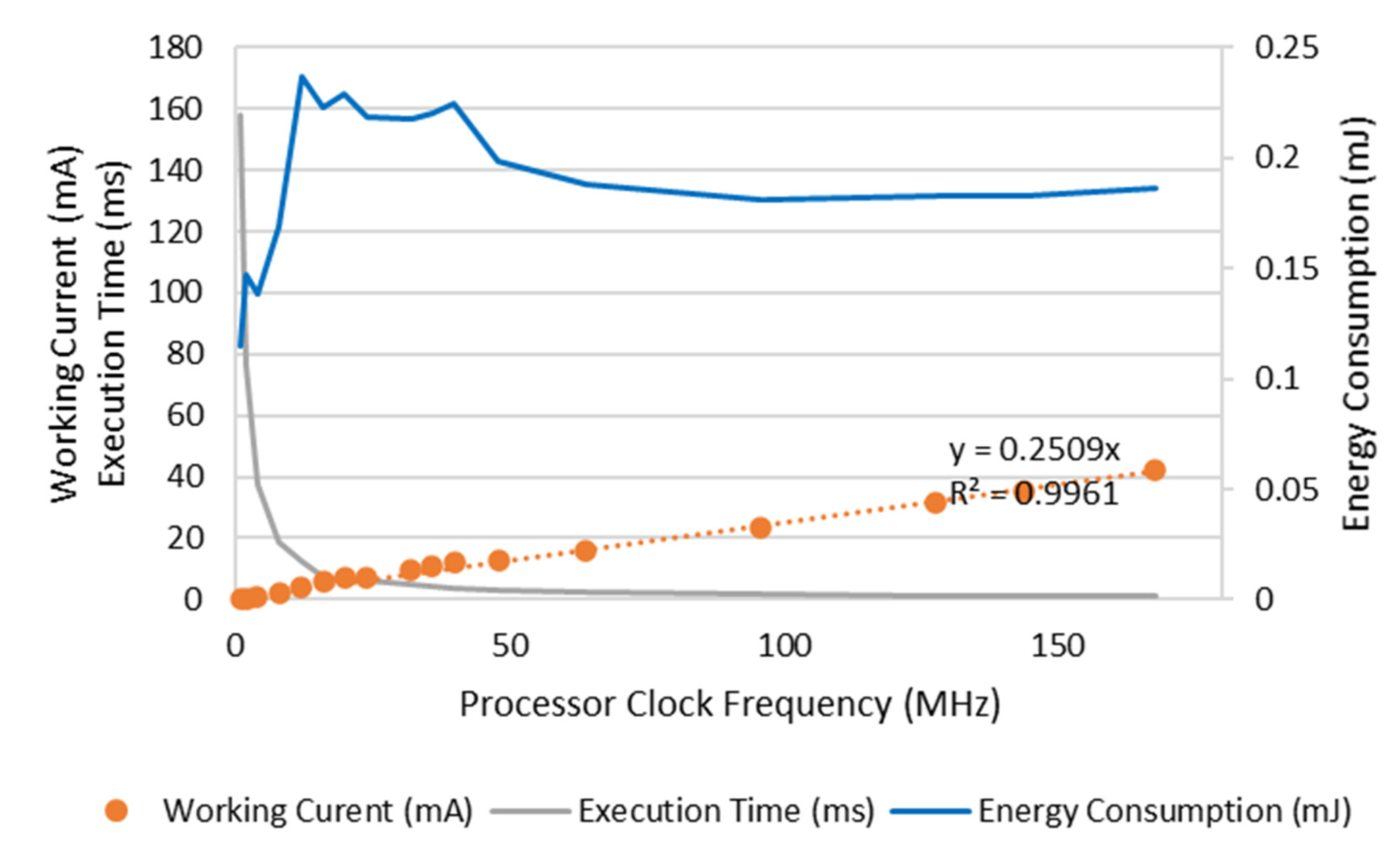

4.2. Processor Clock Frequencies and Energy Consumption

4.3. DVFS, Power Modes, and Their Overheads

- (1)

- The time overhead of processor clock frequency transitions is relatively fixed, regardless of the difference between the previous and the latter processor frequency.

- (2)

- The time overhead for STM32F407 to switch the processor frequency can be as high as approximately 70 ms.

- (3)

- Considering that the peripheral clock of STM32F407 is obtained by dividing the HCLK, adjusting the processor frequency not only brings time overhead but also makes the peripherals unable to work and communicate during this period. After the processor frequency is changed, APB1 and APB2 must be reinitialized to work with the peripherals again, making the situation even worse.

5. Analysis and Suggestions

6. Future Directions

7. Discussion and Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Dar, K.S.; Asif, S.; Islam, A. Power Management and Green Computing: An Operating System Prospective. Can. Int. J. Soc. Sci. Educ. 2015, 2, 164–183. [Google Scholar]

- Thakkar, A.; Chaudhari, K.; Shah, M. A Comprehensive Survey on Energy-Efficient Power Management Techniques. Procedia Comput. Sci. 2020, 167, 1189–1199. [Google Scholar] [CrossRef]

- Adegbija, T.; Rogacs, A.; Patel, C.; Gordon-Ross, A. Microprocessor Optimizations for the Internet of Things: A Survey. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 2018, 37, 7–20. [Google Scholar] [CrossRef]

- Sun, L.; Sheshadri, R.K.; Zheng, W.; Koutsonikolas, D. Modeling WiFi Active Power/Energy Consumption in Smartphones. In Proceedings of the 2014 IEEE 34th International Conference on Distributed Computing Systems, Madrid, Spain, 30 June–3 July 2014; pp. 41–51. [Google Scholar]

- Martinez, B.; Montón, M.; Vilajosana, I.; Prades, J.D. The Power of Models: Modeling Power Consumption for IoT Devices. IEEE Sens. J. 2015, 15, 5777–5789. [Google Scholar] [CrossRef]

- Yoon, C.; Lee, S.; Choi, Y.; Ha, R.; Cha, H. Accurate power modeling of modern mobile application processors. J. Syst. Archit. 2017, 81, 17–31. [Google Scholar] [CrossRef]

- Alawnah, S.; Sagahyroon, A. Modeling of smartphones’ power using neural networks. EURASIP J. Embed. Syst. 2017, 2017, 22. [Google Scholar] [CrossRef]

- Anantha, C.P.; Denis, D.C.; Joyce, D.C.; Yogesh, R.K. Next generation micro-power systems. In Proceedings of the 2008 IEEE Symposium on VLSI Circuits, Honolulu, HI, USA, 18–20 June 2008; pp. 2–5. [Google Scholar]

- Gollakota, S.; Reynolds, M.S.; Smith, J.R.; Wetherall, D.J. The Emergence of RF-Powered Computing. Computer 2014, 47, 32–39. [Google Scholar] [CrossRef]

- Gudan, K.; Chemishkian, S.; Hull, J.J.; Reynolds, S.M.; Thomas, S. Feasibility of wireless sensors using ambient 2.4GHz RF energy. In Proceedings of the 2012 IEEE SENSORS, Taipei, Taiwan, 28–31 October 2012. [Google Scholar]

- Li, C.; Zhang, W.; Cho, C.B.; Li, T. SolarCore: Solar energy driven multi-core architecture power management. In Proceedings of the 2011 IEEE 17th International Symposium on High Performance Computer Architecture, San Antonio, TX, USA, 12–16 February 2011; pp. 205–216. [Google Scholar]

- Raghunathan, V.; Kansal, A.; Hsu, J.; Friedman, J.; Srivastava, M. Design considerations for solar energy harvesting wireless embedded systems. In Proceedings of the IPSN 2005 Fourth International Symposium on Information Processing in Sensor Networks, Boise, ID, USA, 15 April 2005; p. 64. [Google Scholar]

- Hua, S.; Qu, G. Approaching the maximum energy saving on embedded systems with multiple voltages. In Proceedings of the IEEE/ACM International Conference on Computeraided Design, San Jose, CA, USA, 9–13 November 2003. [Google Scholar]

- Gheorghita, S.V.; Basten, T.; Corporaal, H. Application Scenarios in Streaming-Oriented Embedded System Design. In Proceedings of the International Symposium on System-on-Chip, Tampere, Finland, 14–15 November 2006. [Google Scholar]

- Choi, K.; Soma, R.; Pedram, M. Fine-grained dynamic voltage and frequency scaling for precise energy and performance tradeoff based on the ratio of off-chip access to on-chip computation times. IEEE Trans. Comput. Des. Integr. Circuits Syst. 2004, 24, 18–28. [Google Scholar] [CrossRef]

- Saewong, S.; Rajkumar, R. Practical voltage-scaling for fixed-priority RT-systems. In Proceedings of the 9th IEEE Real-Time and Embedded Technology and Applications Symposium, Toronto, ON, Canada, 30 May 2003. [Google Scholar]

- Quan, G.; Hu, X. Energy efficient fixed-priority scheduling for real-time systems on variable voltage processors. In Proceedings of the 38th Annual Design Automation Conference, Taipei, Taiwan, 9–14 October 2001. [Google Scholar]

- Kan, E.Y.Y.; Chan, W.K.; Tse, T.H. Leveraging Performance and Power Savings for Embedded Systems Using Multiple Target Deadlines. In Proceedings of the 2010 10th International Conference on Quality Software, Zhangjiajie, China, 14–15 July 2010. [Google Scholar]

- STM32F405/415, STM32F407/417, STM32F427/437 and STM32F429/439 Advanced Arm®-based 32-bit MCUs—Reference Manual. Available online: https://www.st.com/resource/en/reference_manual/dm00031020-stm32f405415-stm32f407417-stm32f427437-and-stm32f429439-advanced-armbased-32bit-mcus-stmicroelectronics.pdf (accessed on 8 March 2019).

- Li, D.; Chou, P.H.; Bagherzadeh, N. Mode selection and mode-dependency modeling for power-aware embedded systems. In Proceedings of the ASP-DAC/VLSI Design 2002, 7th Asia and South Pacific Design Automation Conference and 15h International Conference on VLSI Design, Bangalore, India, 11 January 2002. [Google Scholar]

- Hoeller, A.S.; Wanner, L.F.; Fröhlich, A.A. A Hierarchical Approach for Power Management on Mobile Embedded Systems. In Proceedings of the IFIP Working Conference on Distributed and Parallel Embedded Systems, Braga, Portugal, 11–13 October 2006. [Google Scholar]

- Huang, K.; Santinelli, L.; Chen, J.; Thiele, L.; Buttazzo, G.C. Adaptive power management for real-time event streams. In Proceedings of the 2010 15th Asia and South Pacific Design Automation Conference (ASP-DAC), Taipei, Taiwan, 18–21 January 2010. [Google Scholar]

- Bhatti, K.; Belleudy, C.; Auguin, M. Power Management in Real Time Embedded Systems through Online and Adaptive Interplay of DPM and DVFS Policies. In Proceedings of the 2010 IEEE/IFIP International Conference on Embedded and Ubiquitous Computing, Hong Kong, China, 11–13 December 2010. [Google Scholar]

- Niu, L.; Quan, G. Reducing both dynamic and leakage energy consumption for hard real-time systems. In Proceedings of the 2004 international conference on Compilers, Architecture, and Synthesis for Embedded Systems, Washington, DC, USA, 22–25 September 2004. [Google Scholar]

- Liang, J.M.; Chen, J.J.; Cheng, H.H.; Tseng, Y.C. An energy-efficient sleep scheduling with QoS consideration in 3GPP LTE-advanced networks for Internet of things. IEEE J. Emerging Sel. Topics Circuits Syst. 2013, 3, 13–22. [Google Scholar] [CrossRef]

- Ahmad, R.W.; Gani, A.; Ab Hamid, S.H.; Naveed, A.; Ko, K.; Rodrigues, J.J. A case and framework for code analysis–based smartphone application energy estimation. Int. J. Commun. Syst. 2016, 30, e3235. [Google Scholar] [CrossRef]

- Chen, N. Research and Implementation of Low Power Technology for Embedded Real-Time Operating System. Master Thesis, University of Electronic Science and Technology of China, Chengdu, China, 2015. [Google Scholar]

- Optimize Options (Using the GNU Compiler Collection (GCC)). Available online: https://gcc.gnu.org/onlinedocs/gcc/Optimize-Options.html (accessed on 31 July 2018).

- Arm Compiler User Guide. Available online: https://developer.arm.com/documentation/100748/0610 (accessed on 31 July 2018).

- Chung, E.Y.; Benini, L.; Micheli, G.D. Source code transformation based on software cost analysis. In Proceedings of the 14th International Symposium on Systems Synthesis, Montreal, QC, Canada, 30 September–3 October 2001. [Google Scholar]

- Dzhagaryan, A.; Milenković, A. Impact of thread and frequency scaling on performance and energy in modern multicores: A measurement-based study. In Proceedings of the 2014 ACM Southeast Regional Conference, Kennesaw, GA, USA, 28–29 March 2014. [Google Scholar]

- Kim, W.; Gupta, M.S.; Wei, G.; Brooks, D. System level analysis of fast, per-core DVFS using on-chip switching regulators. In Proceedings of the 2008 IEEE 14th International Symposium on High Performance Computer Architecture, Salt Lake City, UT, USA, 16–20 February 2008. [Google Scholar]

- Jiangwei, H. Partitioning the Program into different regions using dynamic and Static Approach with kernel-Assisted in Power management for Embedded System. In Proceedings of the 2006 IEEE International Conference on Information Reuse & Integration, Waikoloa, HI, USA, 16–18 September 2006. [Google Scholar]

- Pinheiro, D.; Gonc¸alves, R.; Valentin, E.; Oliveira, H.; Barreto, R. Inserting DVFS Code in Hard Real-Time System Tasks. In Proceedings of the 2017 VII Brazilian Symposium on Computing Systems Engineering, Curitiba, Brazil, 6–10 November 2017; pp. 23–30. [Google Scholar]

- Kuehn, P.J.; Mashaly, M. DVFS-Power Management and Performance Engineering of Data Center Server Clusters. In Proceedings of the 2019 15th Annual Conference on Wireless On-demand Network Systems and Services (WONS), Wengen, Switzerland, 22–24 January 2019; pp. 91–98. [Google Scholar]

- Wu, H. An Automatic Energy Consumption Measuring Platform for Embedded Systems. In Proceedings of the 2019 6th International Conference on Information Science and Control Engineering (ICISCE), Shanghai, China, 20–22 December 2019. [Google Scholar]

- Wu, H. Two Designs of Automatic Embedded System Energy Consumption Measuring Platforms Using GPIO. Appl. Sci. 2020, 10, 4866. [Google Scholar] [CrossRef]

- Series 2280S Precision Measurement, Low Noise, Programmable DC Power Supplies Datasheet. Available online: https://download.tek.com/datasheet/1KW-50894-0_2280S_Datasheet_040219.pdf (accessed on 10 June 2017).

- STM32F407/417-STMicroelectronics. Available online: https://www.st.com/en/microcontrollers-microprocessors/stm32f407-417.html (accessed on 8 March 2019).

| HCLK (MHz) | Execution Time (ms) | Energy Consumption (mJ) | Energy Saved (%) | ||

|---|---|---|---|---|---|

| Total | Processor | Peripherals | |||

| 4 | 37.680 | 1.672 | 0.168 | 1.504 | −197.0 |

| 8 | 18.693 | 0.929 | 0.169 | 0.760 | −65.0 |

| 16 | 9.350 | 0.563 | 0.223 | 0.340 | 0 |

| 32 | 4.660 | 0.414 | 0.217 | 0.197 | 26.5 |

| 48 | 3.106 | 0.330 | 0.198 | 0.132 | 41.4 |

| 64 | 2.326 | 0.282 | 0.188 | 0.094 | 49.9 |

| 96 | 1.553 | 0.244 | 0.181 | 0.063 | 56.7 |

| 128 | 1.165 | 0.230 | 0.183 | 0.047 | 59.1 |

| 168 | 0.887 | 0.222 | 0.186 | 0.036 | 60.6 |

| Mode | Regulator | Working Current (mA) | Power Consumption (mW) |

|---|---|---|---|

| Normal | N/A | 12.81379 | 64.06895 |

| Sleep | Main | 6.25984 | 31.29220 |

| Low power | 6.22557 | 31.12785 | |

| Stop | Main | 4.82017 | 24.10085 |

| Low power | 4.56274 | 22.81370 | |

| Standby | N/A | 0.92958 | 4.64790 |

| Power Mode | Return Time (μs) |

|---|---|

| Sleep | 0.6745 |

| Stop | 5.517 (clock reconfigure excluded) |

| Standby | 23.61 (clock reconfigure excluded) |

| Mode | Working Current (mA) | Power Consumption (mW) | Wake-Up Time (ms) |

|---|---|---|---|

| Active | 50.23 | 251.15 | N/A |

| Light sleep | 12.21 | 61.05 | 0.44 |

| Deep sleep | 11.07 | 55.35 | 115 |

| Clock Source and Frequency | Memory Loss Acceptable? | Sleep Time (ms) | Best Choice |

|---|---|---|---|

| HSI/HSE | Yes | Any | Standby mode |

| No | Any | Stop mode | |

| PLL | Yes | <159 | Sleep mode |

| ≥159 | Standby mode | ||

| No | <508 | Sleep mode | |

| ≥508 | Stop mode |

| Sleep Time (s) | Best Choice |

|---|---|

| <4.792 | Light sleep |

| ≥4.792 | Deep sleep |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Wu, H.; Chen, C.; Weng, K. An Energy-Efficient Strategy for Microcontrollers. Appl. Sci. 2021, 11, 2581. https://doi.org/10.3390/app11062581

Wu H, Chen C, Weng K. An Energy-Efficient Strategy for Microcontrollers. Applied Sciences. 2021; 11(6):2581. https://doi.org/10.3390/app11062581

Chicago/Turabian StyleWu, Huanjie, Chun Chen, and Kai Weng. 2021. "An Energy-Efficient Strategy for Microcontrollers" Applied Sciences 11, no. 6: 2581. https://doi.org/10.3390/app11062581

APA StyleWu, H., Chen, C., & Weng, K. (2021). An Energy-Efficient Strategy for Microcontrollers. Applied Sciences, 11(6), 2581. https://doi.org/10.3390/app11062581