A High-Throughput Vernier Time-to-Digital Converter on FPGAs with Improved Resolution Using a Bi-Time Interpolation Scheme

Abstract

:1. Introduction

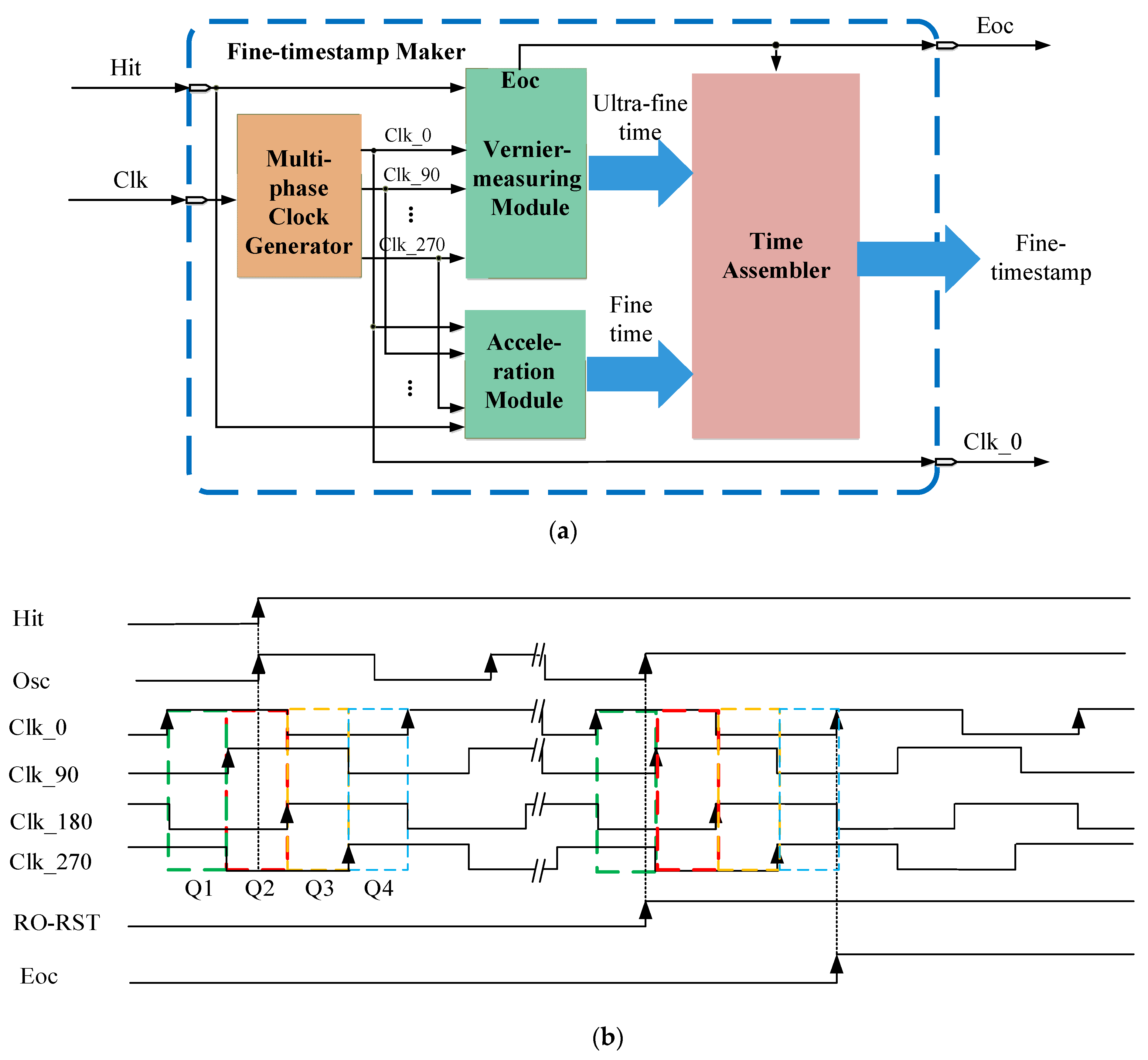

2. Fine-Timestamp Maker Design

2.1. Architecture and Circuit Design

2.2. Ring Oscillator Design

2.3. Performance Evaluation

3. Results

3.1. TDC Design

3.2. Time Interval Test Results

4. Discussion and Future Work

5. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Zhang, M.; Zhao, Y.; Han, Z.; Zhao, F. A 19 ps Precision and 170 M Samples/s Time-to-Digital Converter Implemented in FPGA with Online Calibration. Appl. Sci. 2022, 12, 3649. [Google Scholar] [CrossRef]

- Prasad, K.H.; Chandratre, V.; Sukhwani, M. An FPGA based 33-channel, 72 ps LSB time-to-digital converter. Methods Phys. Res. Sect. A Accel. Spectrom. Detect. Assoc. Equip. 2022, 1027, 166052. [Google Scholar] [CrossRef]

- Fan, H.H.; Cao, P.; Liu, S.B.; An, Q. TOT measurement implemented in FPGA TDC. Chin. Phys. C 2015, 39, 116101. [Google Scholar] [CrossRef]

- Yousif, A.S.; Haslett, J.W. A fine resolution TDC architecture for next generation PET imaging. IEEE Trans. Nucl. Sci. 2007, 54, 1574–1582. [Google Scholar] [CrossRef]

- Zheng, Z.; Zha, B.; Zhou, Y.; Huang, J.; Xuchen, Y.; Zhang, H. Single-Stage Adaptive Multi-Scale Point Cloud Noise Filtering Algorithm Based on Feature Information. Remote Sens. 2022, 14, 367. [Google Scholar] [CrossRef]

- Zanuso, M.; Madoglio, P.; Levantino, S.; Samori, C.; Lacaita, A.L. Time-to-digital converter for frequency synthesis based on a digital bang-bang DLL. IEEE Trans. Circuits Syst. I Regul. Pap. 2009, 57, 548–555. [Google Scholar] [CrossRef]

- Kim, J.-S.; Seo, Y.-H.; Suh, Y.; Park, H.-J.; Sim, J.-Y. A 300-MS/s, 1.76-ps-resolution, 10-b asynchronous pipelined time-to-digital converter with on-chip digital background calibration in 0.13-µm CMOS. IEEE J. Solid-State Circuits 2012, 48, 516–526. [Google Scholar] [CrossRef]

- Jung, S.; Kim, E.-S.; Yoo, J.; Kim, J.-Y.; Choi, J.G. An evaluation and acceptance of COTS software for FPGA-based controllers in NPPs. Ann. Nucl. Energy 2016, 94, 338–349. [Google Scholar] [CrossRef]

- Machado, R.; Cabral, J.; Alves, F.S. Recent developments and challenges in FPGA-based time-to-digital converters. IEEE Trans. Instrum. Meas. 2019, 68, 4205–4221. [Google Scholar] [CrossRef]

- Wu, J.; Shi, Z. The 10-ps wave union TDC: Improving FPGA TDC resolution beyond its cell delay. In Proceedings of the 2008 IEEE Nuclear Science Symposium Conference Record, Dresden, Germany, 19–25 October 2008; pp. 3440–3446. [Google Scholar]

- Szplet, R.; Sondej, D.; Grzeda, G. Subpicosecond-resolution time-to-digital converter with multi-edge coding in independent coding lines. In Proceedings of the 2014 IEEE International Instrumentation and Measurement Technology Conference (I2MTC) Proceedings, Montevideo, Uruguay, 12–15 May 2014; pp. 747–751. [Google Scholar]

- Won, J.Y.; Kwon, S.I.; Yoon, H.S.; Ko, G.B.; Son, J.-W.; Lee, J.S. Dual-phase tapped-delay-line time-to-digital converter with on-the-fly calibration implemented in 40 nm FPGA. IEEE Trans. Biomed. Circuits Syst. 2015, 10, 231–242. [Google Scholar] [CrossRef] [PubMed]

- Wang, Y.; Kuang, J.; Liu, C. A 3.9-ps RMS precision time-to-digital converter using ones-counter encoding scheme in a Kintex-7 FPGA. IEEE Trans. Nucl. Sci. 2017, 64, 2713–2718. [Google Scholar] [CrossRef]

- Zheng, J.; Cao, P.; Jiang, D.; An, Q. Low-cost FPGA TDC with high resolution and density. IEEE Trans. Nucl. Sci. 2017, 64, 1401–1408. [Google Scholar] [CrossRef]

- Wang, Y.; Zhou, X.; Song, Z.; Kuang, J.; Cao, Q. A 3.0-ps rms precision 277-MSamples/s throughput time-to-digital converter using multi-edge encoding scheme in a Kintex-7 FPGA. IEEE Trans. Nucl. Sci. 2019, 66, 2275–2281. [Google Scholar] [CrossRef]

- Portaluppi, D.; Pasquinelli, K.; Cusini, I.; Zappa, F. Multi-Channel FPGA Time-to-Digital Converter With 10 ps Bin and 40 ps FWHM. IEEE Trans. Instrum. Meas. 2022, 71, 1–9. [Google Scholar] [CrossRef]

- Tancock, S.; Rarity, J.; Dahnoun, N. The Wave-Union Method on DSP Blocks: Improving FPGA-based TDC resolutions by 3x with a 1.5 x area increase. IEEE Trans. Instrum. Meas. 2022, 71, 1–11. [Google Scholar] [CrossRef]

- Fries, M.D.; Williams, J.J. High-precision TDC in an FPGA using a 192 MHz quadrature clock. In Proceedings of the 2002 IEEE Nuclear Science Symposium Conference Record, Norfolk, VA, USA, 10–16 November 2002; pp. 580–584. [Google Scholar]

- Büchele, M.; Fischer, H.; Herrmann, F.; Königsmann, K.; Schill, C.; Schopferer, S. The GANDALF 128-channel time-to-digital converter. Phys. Procedia 2012, 37, 1827–1834. [Google Scholar] [CrossRef] [Green Version]

- Wang, Y.; Kuang, P.; Liu, C. A 256-channel multi-phase clock sampling-based time-to-digital converter implemented in a Kintex-7 FPGA. In Proceedings of the 2016 IEEE International Instrumentation and Measurement Technology Conference Proceedings, Taipei, Taiwan, 23–26 May 2016; pp. 1–5. [Google Scholar]

- Cui, K.; Ren, Z.; Li, X.; Liu, Z.; Zhu, R. A high-linearity, ring-oscillator-based, Vernier time-to-digital converter utilizing carry chains in FPGAs. IEEE Trans. Nucl. Sci. 2017, 64, 697–704. [Google Scholar] [CrossRef]

- Cui, K.; Ren, Z.; Li, X.; Liu, Z.; Zhu, R. Toward implementing multichannels, ring-oscillator-based, Vernier time-to-digital converter in FPGAs: Key design points and construction method. IEEE Trans. Radiat. Plasma Med. Sci. 2017, 1, 391–399. [Google Scholar] [CrossRef] [Green Version]

- Cui, K.; Li, X. A high-linearity Vernier time-to-digital converter on FPGAs with improved resolution using bidirectional-operating Vernier delay lines. IEEE Trans. Instrum. Meas. 2019, 69, 5941–5949. [Google Scholar] [CrossRef]

| Ref. | Chip | Method | Resolution (ps) | RMS (ps) | DNL (LSB) | INL (LSB) | Dead Time (ns) | Registers Cost | LUTs Cost |

|---|---|---|---|---|---|---|---|---|---|

| [11] | Spartan-6 | TDL+ multi-edge coding | 0.9 | <6 | <2.91 | <15.7 | 3 | N/S | 144 SLICES |

| [13] | Kintex-7 | TDL+ Ones-Counter coding | 3.9 | <3 | <6 | <18.8 | 3.6 | N/S | 200 SLICES |

| [15] | Kintex-7 | TDL+ multi-edge coding | 3.0 | <3 | <4.5 | <37.7 | 3.6 | N/S | 144 SLICES |

| [21] | Stratix III | Ring Oscillator | 31 | 36.1 | <0.073 | <0.091 | 256 | 319 | 104 |

| [22] | Stratix III | Ring Oscillator | 37 | 39 | −0.4~0.4 | −0.7~0.7 | 400 | 319 | 104 |

| [23] | Stratix III | Ring Oscillator +Bidirectional operating | 24.5 | 28 | −0.20~0.25 | 0.03~0.82 | 602 | 986 | 172 |

| This work | Artix-7 | Ring Oscillator +Bi-time interpolation | 20 | 15–21 | −0.71~0.06 | 0~1.04 | 58 | 35 | 31 |

| This work | Kintex-7 | Ring Oscillator +Bi-time interpolation | 20 | 15–20 | −0.51~0.06 | 0~0.94 | 58 | 35 | 31 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Xu, G.; Zha, B.; Xia, T.; Zheng, Z.; Zhang, H. A High-Throughput Vernier Time-to-Digital Converter on FPGAs with Improved Resolution Using a Bi-Time Interpolation Scheme. Appl. Sci. 2022, 12, 7674. https://doi.org/10.3390/app12157674

Xu G, Zha B, Xia T, Zheng Z, Zhang H. A High-Throughput Vernier Time-to-Digital Converter on FPGAs with Improved Resolution Using a Bi-Time Interpolation Scheme. Applied Sciences. 2022; 12(15):7674. https://doi.org/10.3390/app12157674

Chicago/Turabian StyleXu, Guangbo, Bingting Zha, Tuanjie Xia, Zhen Zheng, and He Zhang. 2022. "A High-Throughput Vernier Time-to-Digital Converter on FPGAs with Improved Resolution Using a Bi-Time Interpolation Scheme" Applied Sciences 12, no. 15: 7674. https://doi.org/10.3390/app12157674