Optimization of Data Acquisition System Based on Electrical Impedance Tomography in Dredging Engineering

Abstract

:1. Introduction

- (1)

- Signal-to-noise rate (SNR): To ensure the accuracy of measurement data, higher requirements of SNR have been put forward. However, the existing EIT data acquisition system cannot keep a high SNR under arbitrary conditions. The acquisition and processing system of EIT must be improved;

- (2)

- Acquisition rate: There is still significant room for enhancing the real-time performance of the measurement system, and the length of a single measurement cycle directly affects the data quality between the measurement results and the distribution of the medium in the pipe. Improving the EIT acquisition rate is a significant prerequisite for ensuring the accuracy of measurement results.

2. Materials and Methods

2.1. EIT System Structure

2.2. Improvement of SNR

- (1)

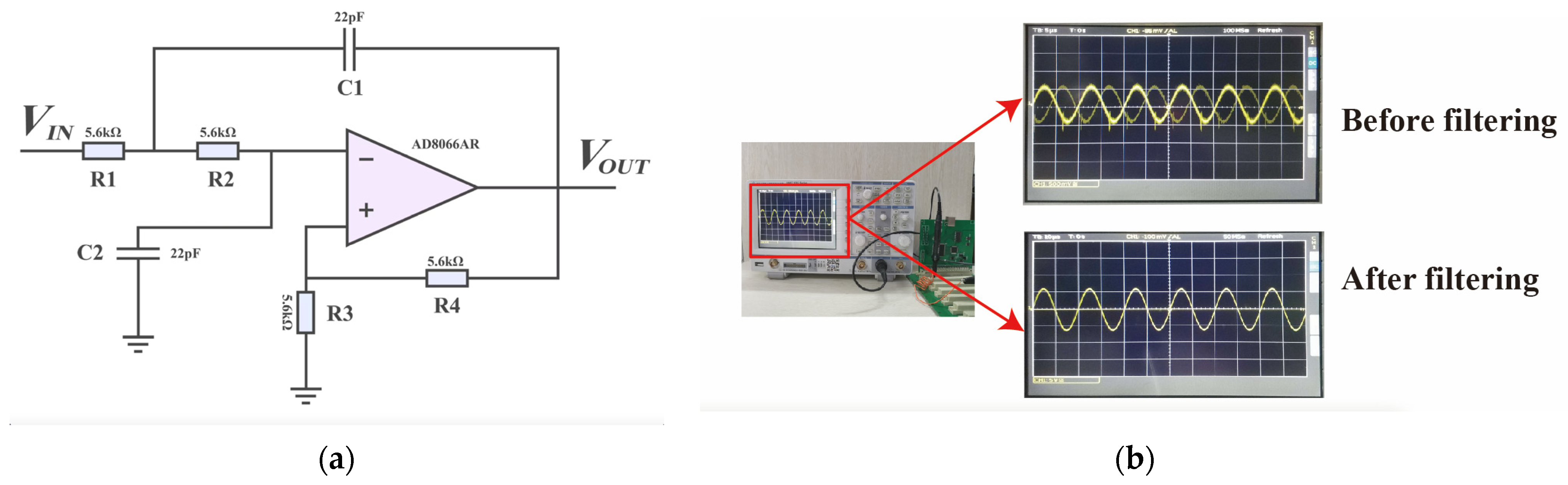

- Optimization of the measurement circuit

- (2)

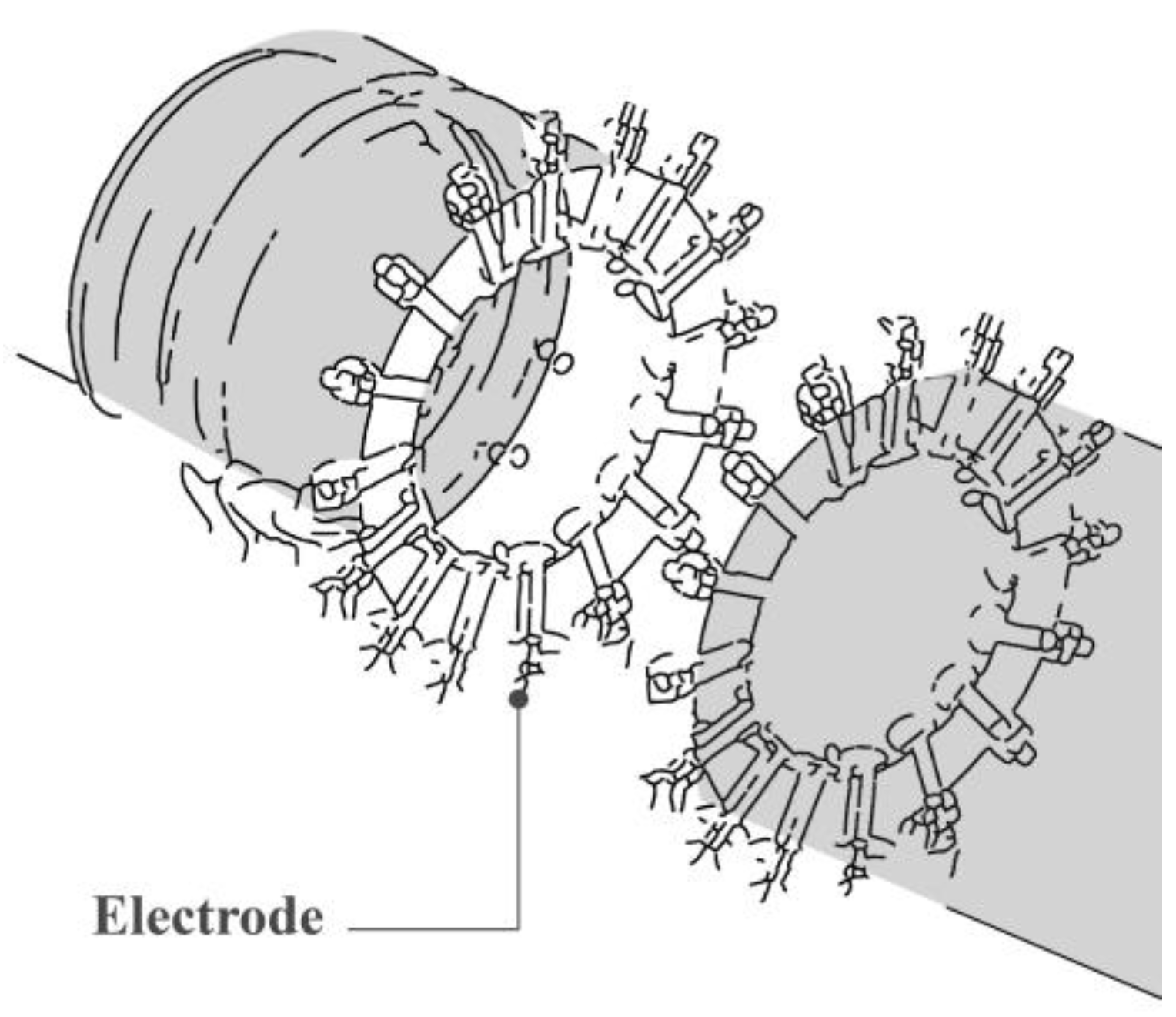

- Electrode and transmission line

2.3. Improvement of Acquisition Rate

- (1)

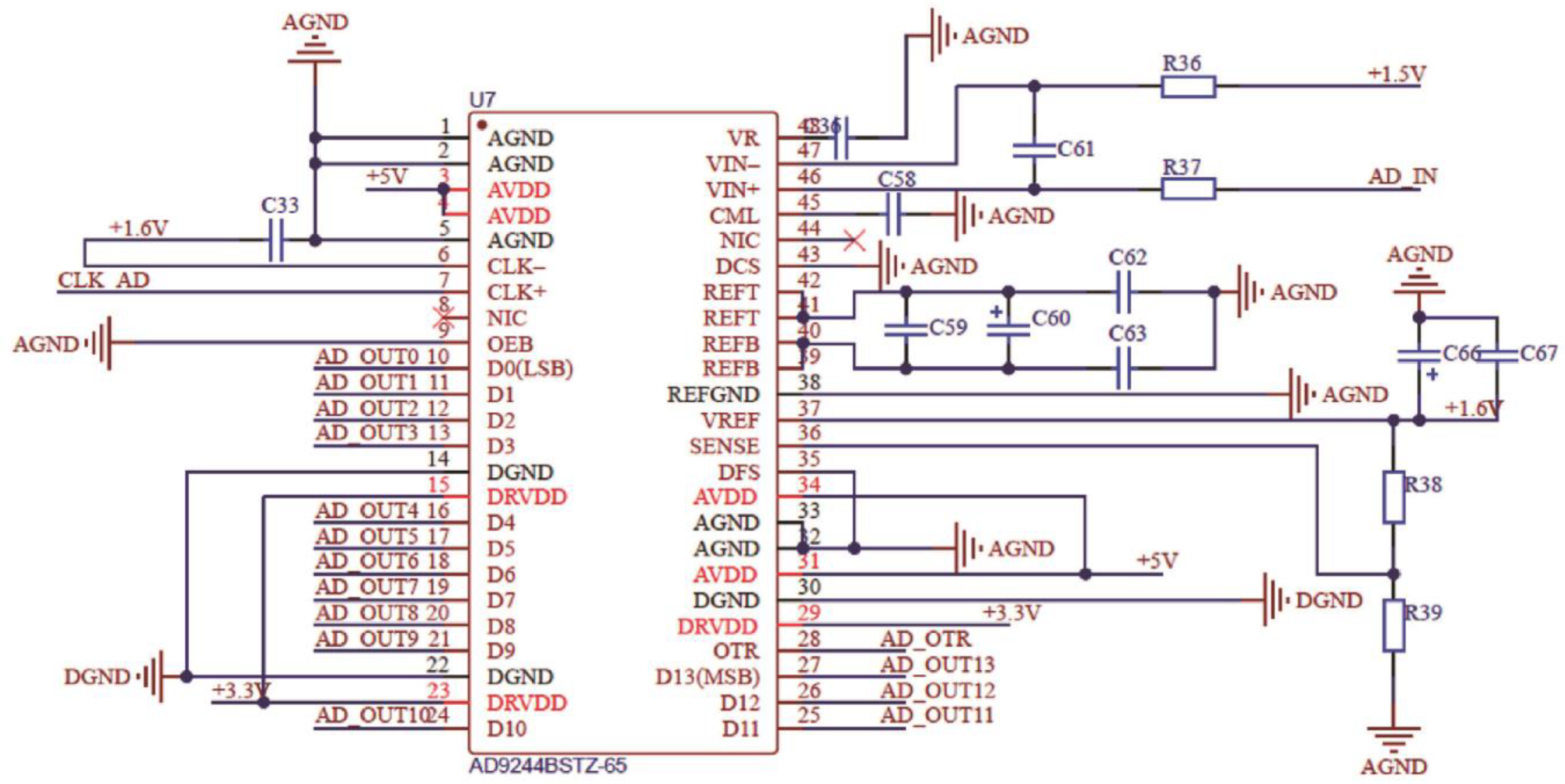

- Analog-to-digital conversion optimization

- (2)

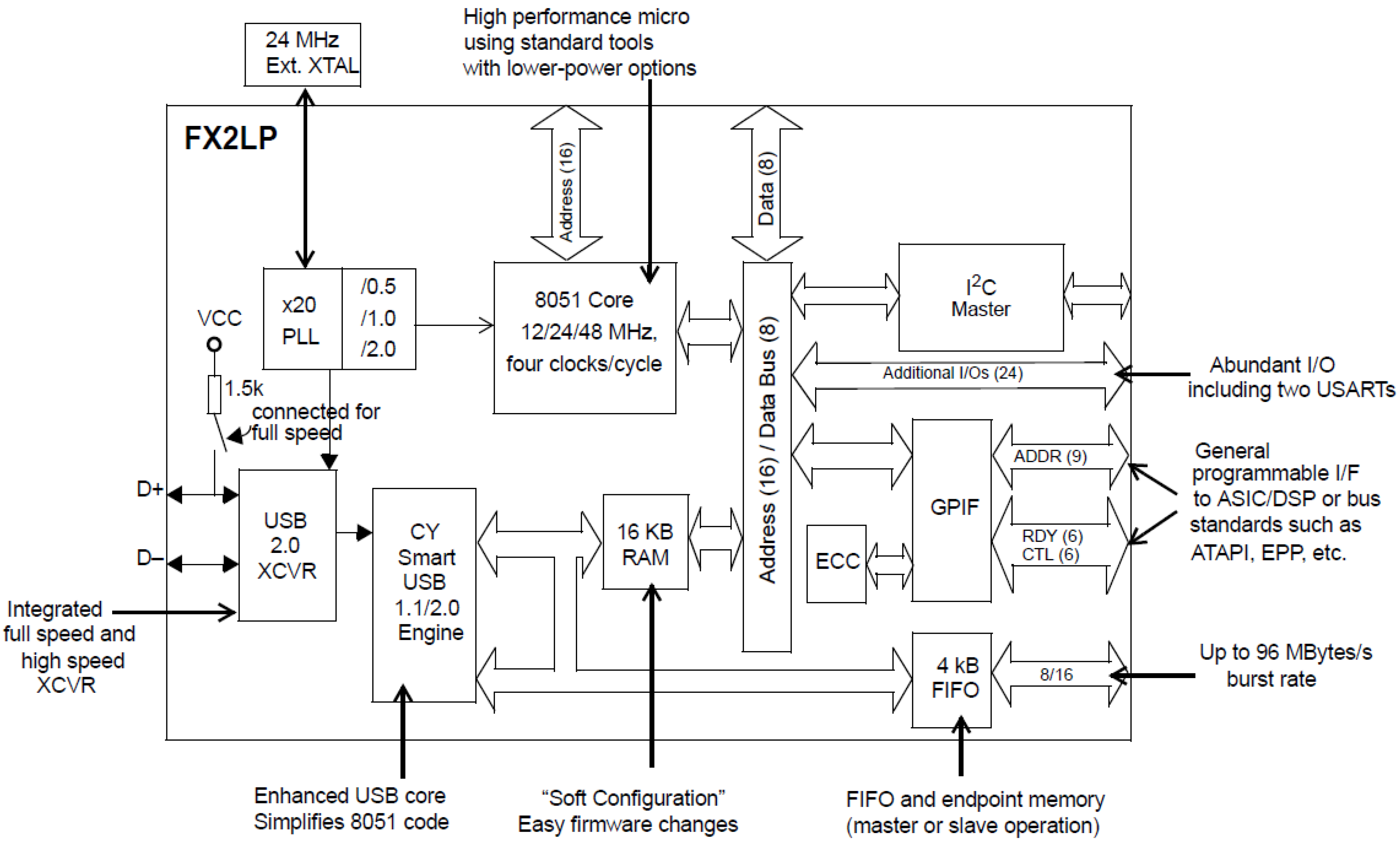

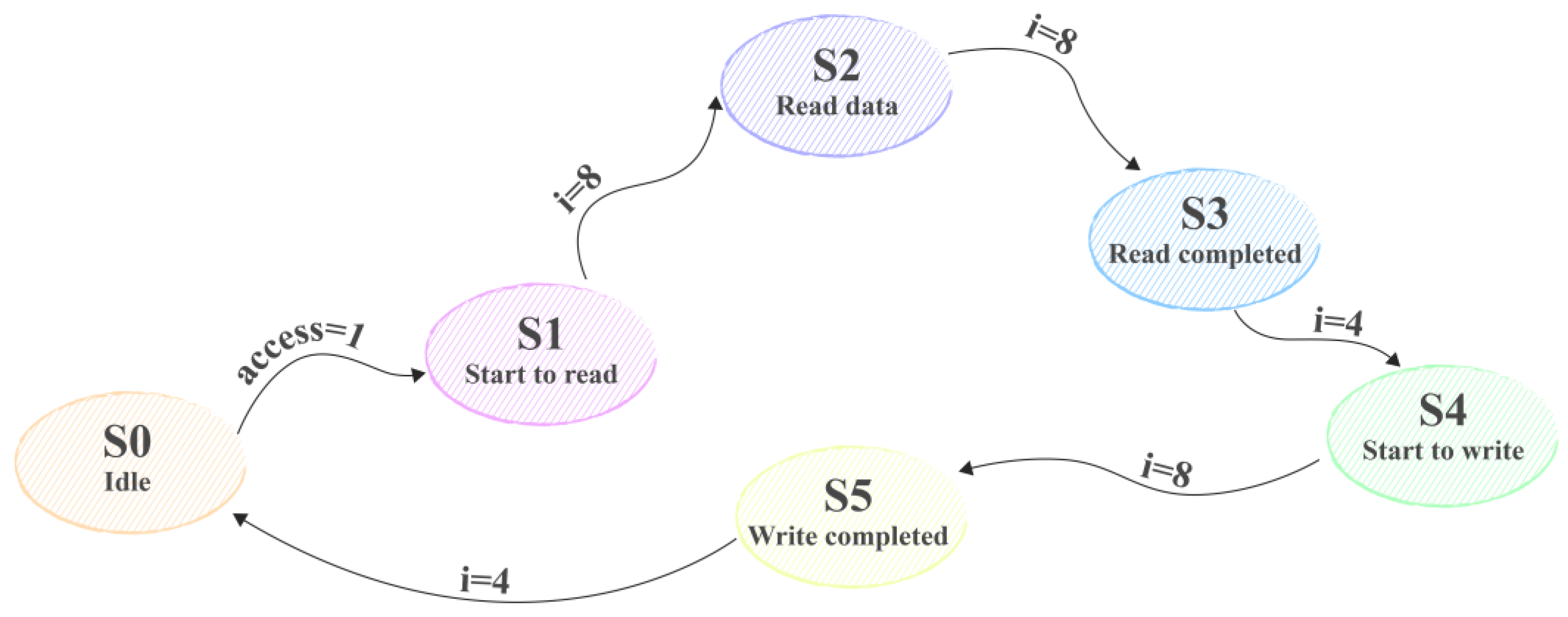

- Communication protocol optimization

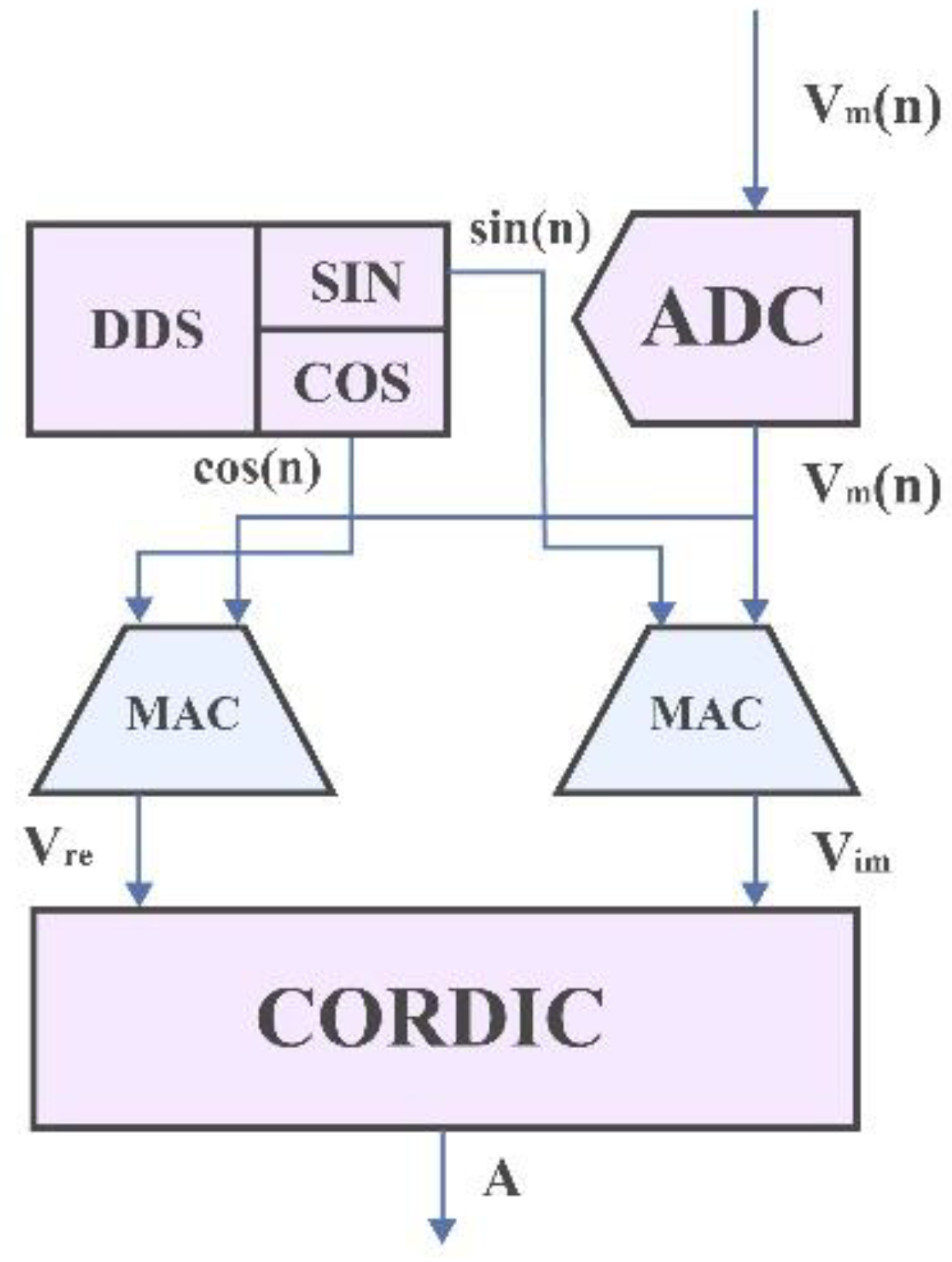

2.4. Digital Phase-Sensitive Demodulation Technique

3. Results

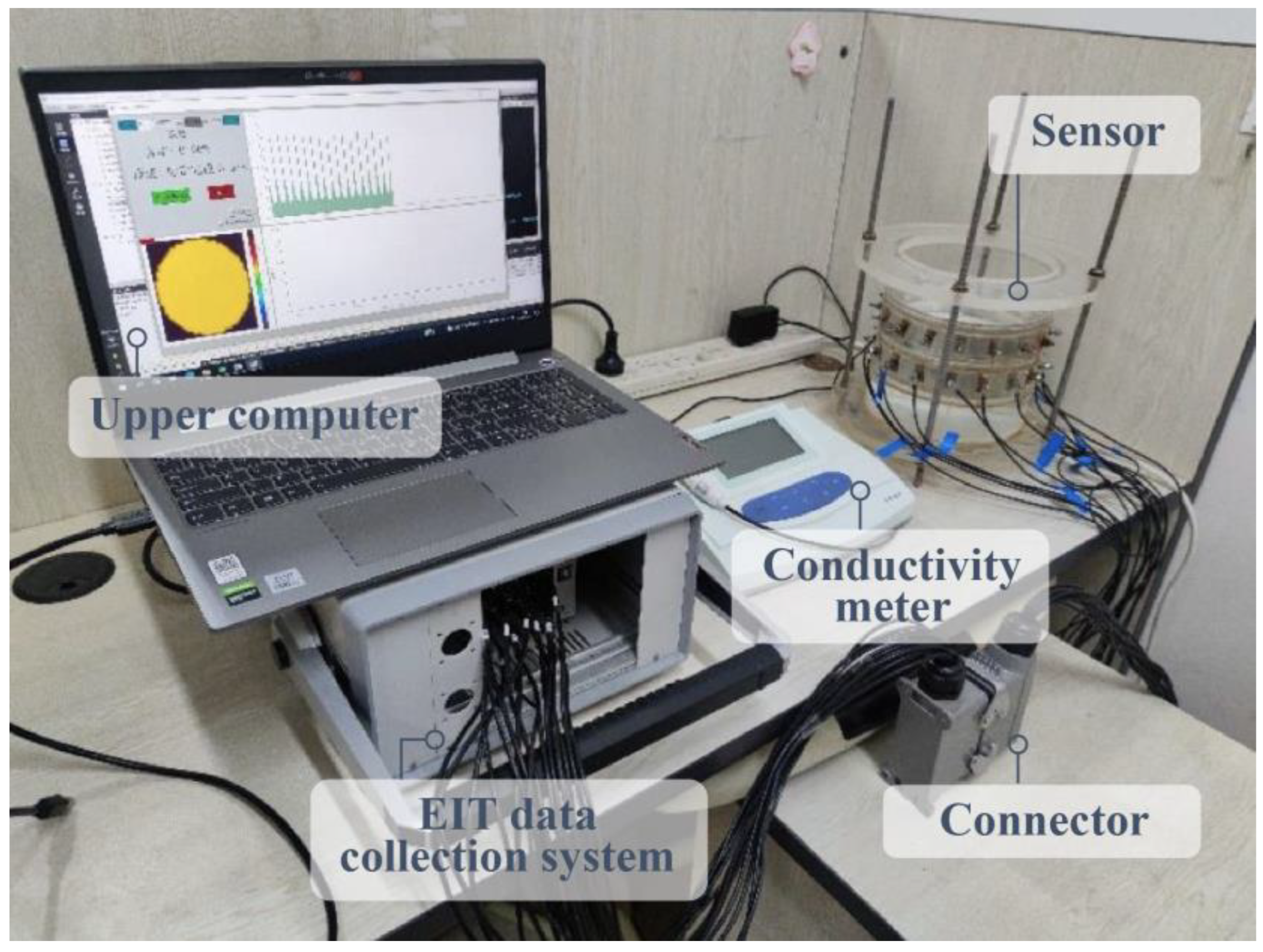

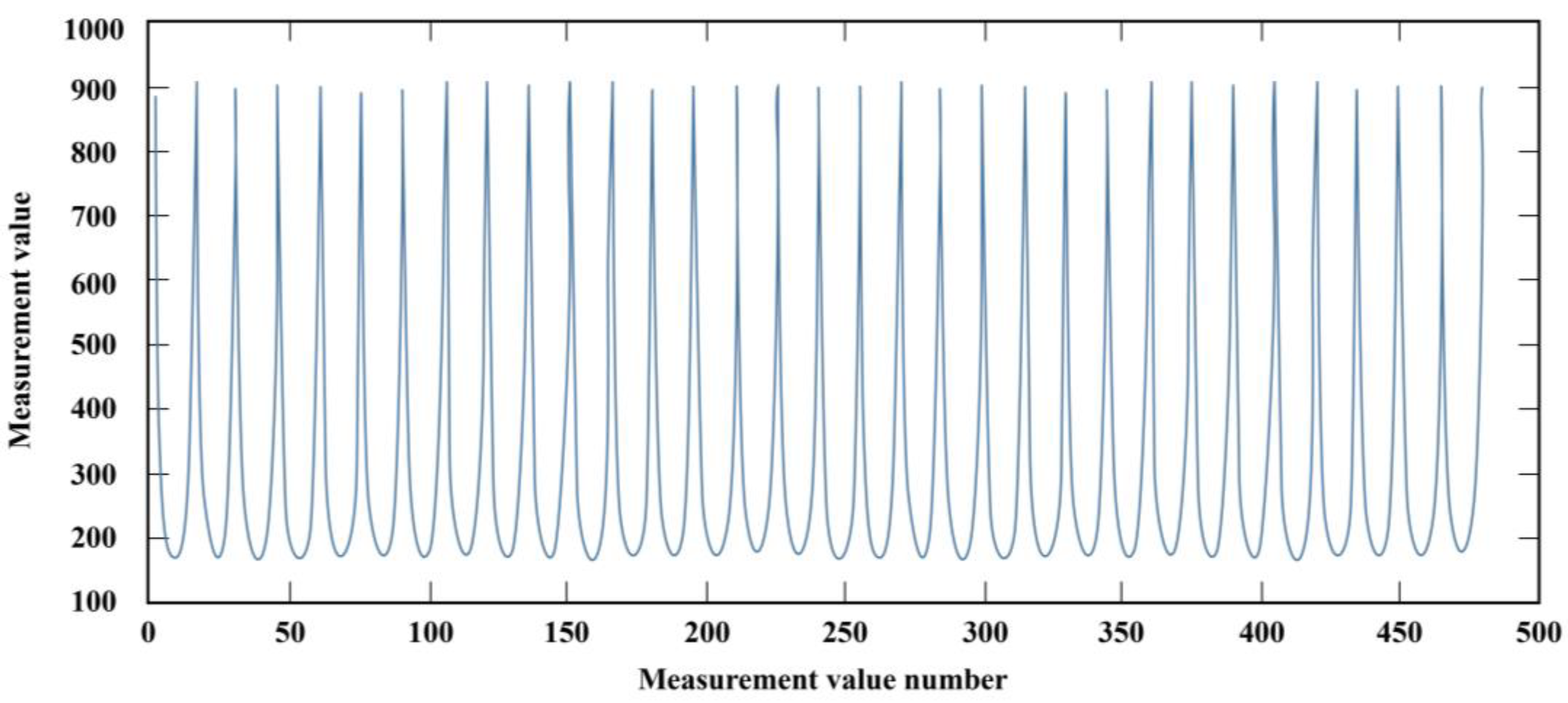

3.1. Experiment on Static Objects

3.2. Simulation Results

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Khang, H.S.; Lee, B.I.; Oh, S.H.; Woo, E.J.; Lee, S.Y.; Cho, M.H.; Kwon, O.; Yoon, J.R.; Seo, J.K. J-substitution algorithm in magnetic resonance electrical impedance tomography (MREIT): Phantom experiments for static resistivity images. IEEE Trans. Med. Imaging 2002, 21, 695–702. [Google Scholar] [CrossRef] [PubMed]

- Tan, C.; Lv, S.; Dong, F.; Takei, M. Image Reconstruction Based on Convolutional Neural Network for Electrical Resistance Tomography. IEEE Sens. J. 2019, 19, 196–204. [Google Scholar] [CrossRef]

- Brown, B.H.; Seagar, A.D. The Sheffield data collection system. Clin. Phys. Physiol. Meas. 1987, 8, 91. [Google Scholar] [CrossRef] [PubMed]

- Smith, R.W.; Freeston, I.L.; Brown, B.H. A real-time electrical impedance tomography system for clinical use-design and preliminary results. IEEE Trans. Biomed. Eng. 1995, 42, 133–140. [Google Scholar] [CrossRef] [PubMed]

- Wilson, A.; Milnes, P.; Waterworth, A.; Smallwood, R.H.; Brown, B.H. Mk3.5: A modular, multi-frequency successor to the Mk3a EIS/EIT system. Physiol. Meas. 2001, 22, 49. [Google Scholar] [CrossRef]

- Holder, D.; GonzÁlez-Correa, C.; Tidswell, T.; Gibson, A.; Cusick, G.; Bayford, R.H. Assessment and Calibration of a Low-Frequency System for Electrical Impedance Tomography (EIT), Optimized for Use in Imaging Brain Function in Ambulant Human Subjects. Ann. N. Y. Acad. Sci. 1999, 873, 512–519. [Google Scholar] [CrossRef] [PubMed]

- Halter, R.; Hartov, A.; Paulsen, K.D. Design and implementation of a high frequency electrical impedance tomography system. Physiol. Meas. 2004, 25, 379. [Google Scholar] [CrossRef]

- Sohal, H.; Wi, H.; Mcewan, A.L.; Woo, E.J.; Oh, T.I. Electrical impedance imaging system using FPGAs for flexibility and interoperability. Biomed. Eng. Online 2014, 13, 126. [Google Scholar] [CrossRef]

- Cui, Z.Q.; Wang, H.X.; Tang, L.; Zhang, L.; Chen, X.; Yan, Y. A specific data acquisition scheme for electrical tomography. In Proceedings of the 2008 IEEE Instrumentation and Measurement Technology Conference, Victoria, BC, Canada, 12–15 May 2008; pp. 726–729. [Google Scholar]

- Hou, H.L.; Wang, H.X.; Chen, X.Y. A biological electrical impedance imaging hardware system based on multi period undersampling technology. Chin. J. Sens. Actuators 2015, 28, 211–216. [Google Scholar]

- Wang, Z.Y.; Yue, S.H.; Li, Q.; Liu, X.; Wang, H.; McEwan, A. Unsupervised Evaluation and Optimization for Electrical Impedance Tomography. IEEE Trans. Instrum. Meas. 2021, 70, 1–12. [Google Scholar] [CrossRef]

- Zhao, Y.; Wang, P.; Zhang, Z.L.; He, W. Research on swept frequency electrical impedance tomography system. Chin. Med. Equip. J. 2005, 26, 3–5. [Google Scholar]

- Wu, J.C.; Yue, S.H.; Ma, H.T. An experimental device for calibration of concentration and velocity of two-phase flow based on electrical impedance measurement system. In Proceedings of the 2021 IEEE International Instrumentation and Measurement Technology Conference (I2MTC), Glasgow, UK, 17–20 May 2021; pp. 1–5. [Google Scholar]

- Xin, C.H. Electrical Impedance Tomography Design and Calculation Technology for Fraction Estimation in Dredging Engineering. Master’s Thesis, Tianjin University, Tianjin, China, 2022. [Google Scholar]

- Wang, P. Electrical Resistance Tomography (ERT) Technology and Its Application in Two-Phase Flow Detection. Doctoral Dissertation, Xidian University, Xi’an, China, 2012. [Google Scholar]

- Kousaka, H.; Ono, K. Numerical Analysis of the Electromagnetic Fields in a Microwave Plasma Source Excited by Azimuthally Symmetric Surface Waves. Jpn. J. Appl. Phys. 2002, 41, 2199. [Google Scholar] [CrossRef]

- Mcadams, E.T.; Jossinet, J.; Lackermeier, A.; Risacher, F. Factors affecting electrode-gel-skin interface impedance in electrical impedance tomography. Med. Biol. Eng. Comput. J. Int. Fed. Med. Biol. Eng. 1996, 34, 397–408. [Google Scholar] [CrossRef] [PubMed]

- Wang, M.; Dickin, F.J. Electrical resistance tomography of metal walled vessels and pipes. Electron. Lett. 1994, 30, 771–773. [Google Scholar] [CrossRef]

- Weinman, J.; Mahler, J. An analysis of electrical properties of metal electrodes. Med. Electron. Biol. Eng. 1964, 2, 299–310. [Google Scholar] [CrossRef]

- Xu, Y.B. Research on Communication Method of Electrical Resistance Tomography System Based on USB Technology. Master Dissertation, Tianjin University, Tianjin, China, 2004. [Google Scholar]

- Wang, M.; Ma, Y.X.; Holliday, N.; Dai, Y.; Williams, R.A.; Lucas, G. A high-performance EIT system. IEEE Sens. J. 2005, 5, 289–299. [Google Scholar] [CrossRef]

- Wang, B.L.; Huang, Z.Y.; Li, H.Q. Development of a new data acquisition system for electrical capacitance tomography. Chin. J. Sci. Instrum. 2001, 22, 424–427. [Google Scholar]

- Yang, D.Y.; Xu, C.L.; Zhou, B.; Wang, S.M. A small aperture high pressure capacitance tomography system based on PCI bus. Chin. J. Sci. Instrum. 2007, 28, 1399–1404. [Google Scholar]

- Cui, Z.Q.; Wang, H.X. Improvements on real-time performance of electrical capacitance tomography. Chin. J. Sci. Instrum. 2010, 31, 1939–1945. [Google Scholar]

- Chen, X.Y.; Sun, L.; Chu, M.L. Research on embedded electrical impedance measurement system. Chin. J. Electron Devices 2017, 40, 430–434. [Google Scholar]

- Halter, R.J.; Hartov, A.; Paulsen, K.D. A Broadband High-Frequency Electrical Impedance Tomography System for Breast Imaging. IEEE Trans. Biomed. Eng. 2008, 55, 650–659. [Google Scholar] [CrossRef] [PubMed]

| Step 1: Generate a digital sine wave from FPGA. |

| Step 2: Drive an external DA conversion chip to generate an AC signal. |

| Step 3: Load filtered smooth signal to the sensor electrode. |

| Step 4: Measure the current signal and convert it into a digital signal through an AD conversion chip. |

| Step 5: Transfer the digital signal to FPGA for demodulation to obtain its amplitude. |

| Step 6: Process the data collected by the EIT system through the upper computer. |

| Material | Resistivity (Ω∙m) | Yield Strength (MPa) | Electrochemical Characteristics | Price (RMB/ton) |

|---|---|---|---|---|

| Copper | 1.72 × 10−8 | 343 | Strong stability and corrosion resistance | 62,980 |

| Titanium | 4.2 × 10−7 | 300 | Good stability and corrosion resistance | 62,210 |

| Carbon | 3.5 × 10−6 | 9.3 | Non-metallic, corrosion-resistant | 2000 |

| Tungsten | 5.48 × 10−8 | - | Strong stability and corrosion resistance | 116,000 |

| Stainless steel | 7.3 × 10−7 | 207 | Moderate stability, not resistant to corrosion | 15,625 |

| Chip | Maximum Sampling Rate (MSPS) | Packaging Type | Resolution Ratio/Bit Wide (bit) | SNR (dB) |

|---|---|---|---|---|

| AD9240 | 10 | MQFP-44 | 14 | 78.5 |

| AD9244 | 65 | LQFP-48 | 14 | 75.3 |

| LTC2239 | 80 | QFN-32 | 10 | 61.6 |

| ADS4149 | 250 | VQFN-48 | 14 | 72.2 |

| Data Transmission Method | Rate | Distance | Characteristic |

|---|---|---|---|

| USB2.0 | 480 Mbps | 5 m | Low-cost, widely used |

| RS-232/485 | 115,200 bps | 1200 m | Simple but low-speed |

| Ethernet(IEEE 802.3ab) | 1 Gbps | Hundreds of kilometers | Relatively complex, capable of remote communication |

| Firewire(IEEE 1394c-2006) | 800 Mbps | 4.5 m | Less CPU usage, reliability, and high-cost |

| PCI(PCI-X 3.0) | 4266 MB/s | - | Belongs to the local bus |

| Measurement Data Number | σx | SNR (dB) | |

|---|---|---|---|

| 60 | 898 | 0 | / |

| 182 | 410.98 | 0.0408 | 80.0656 |

| 283 | 293 | 0 | / |

| 290 | 197.9950 | 0.0705 | 68.9652 |

| 327 | 236.98 | 0.0408 | 75.0986 |

| 396 | 180.9900 | 0.0995 | 65.1967 |

| 442 | 174.0016 | 0.0407 | 72.5998 |

| 473 | 169.9983 | 0.0408 | 72.3976 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Liu, N.; Yue, S.; Wang, Y. Optimization of Data Acquisition System Based on Electrical Impedance Tomography in Dredging Engineering. Appl. Sci. 2023, 13, 9931. https://doi.org/10.3390/app13179931

Liu N, Yue S, Wang Y. Optimization of Data Acquisition System Based on Electrical Impedance Tomography in Dredging Engineering. Applied Sciences. 2023; 13(17):9931. https://doi.org/10.3390/app13179931

Chicago/Turabian StyleLiu, Ning, Shihong Yue, and Yibo Wang. 2023. "Optimization of Data Acquisition System Based on Electrical Impedance Tomography in Dredging Engineering" Applied Sciences 13, no. 17: 9931. https://doi.org/10.3390/app13179931