1. Introduction

A digital-to-time converter (DTC) is similar to a digital-to-analog converter (DAC), except that DTC converts digital values to time interval signals. DTCs are widely used in atomic frequency standards, high-precision positioning [

1,

2], time-correlated single-photon counting instruments (TCSPC), and measurement instruments [

3,

4,

5,

6] such as the very large scale integration (VLSI) functional tester [

7].

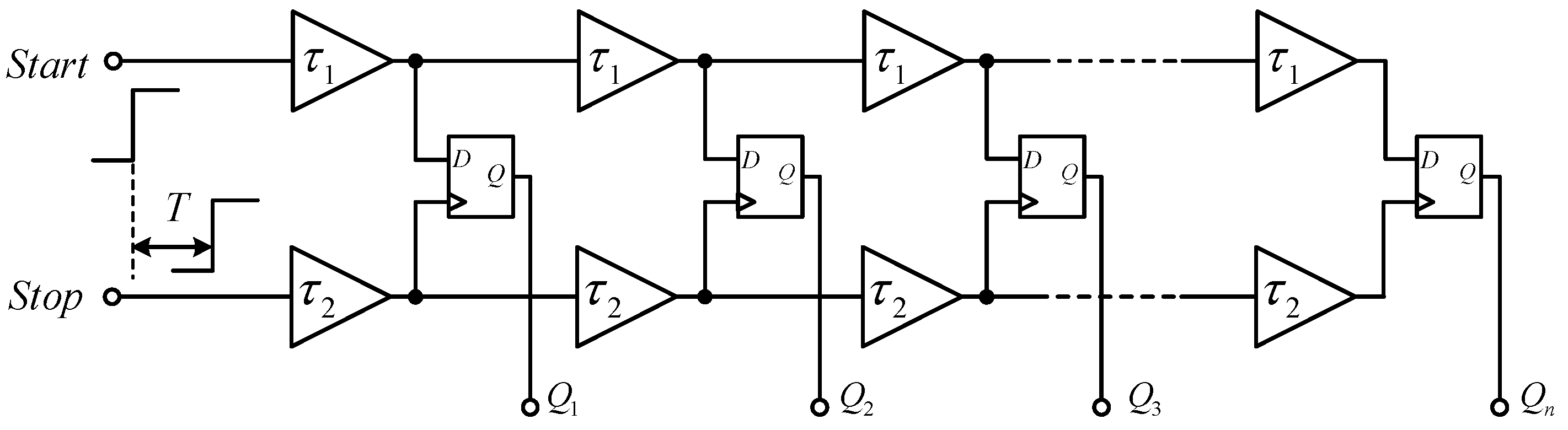

The counting method is a widely used DTC method, which is realized by counting periods of a reference clock. The counting method is simple in implementation and large in dynamic range. However, its resolution is limited to several nanoseconds, which is determined by the frequency of the reference clock. Taking advantage of the technique of the Application Specific Integrated Circuit (ASIC), DTCs implemented in ASIC devices (ASIC-based DTCs) have been proposed [

1,

2,

3,

4,

7]. The best resolution of the ASIC-based DTC is better than 1 ps [

3], which is realized by combining the ASIC technique and the capacitor charging principle. However, these DTCs are sensitive to variations in temperature and voltage owing to the use of analog devices. Moreover, DTCs implemented in ASIC devices is high in cost and long in time to market.

With the development of commercial integrated circuits, DTCs implemented in FPGA (field programmable gate array) devices (FPGA-based DTCs) have attracted an increasing amount of research interest in recent years. Compared with ASIC-based DTCs, FPGA-based DTCs have the advantage of a low cost and a short time to market. Many DTCs implemented in the FPGA are realized by phase shifting [

6,

8,

9], and the obtained resolution is about 8 ps. FPGA-based DTCs are mostly based on a Vernier delay line, a tapped delay line [

10], and a Vernier ring oscillator [

5]. A DTC with a resolution of 11 ps was implemented in a Xilinx Kintex-7 FPGA device based on a tapped delay line [

10]. A DTC based on a Vernier ring oscillator and the Altera Stratix-III FPGA device was proposed [

5], whose theoretical resolution was 1.58 ps.

DTCs with high resolution are mainly implemented in ASIC devices, which have the advantages of fully customized circuits and reasonably precise control of the internal propagation delay. However, it is difficult for FPGA-based DTCs to obtain high resolutions due to the additional delay introduced by the unpredictability of the routing strategy. Therefore, FPGA-based DTCs with a 1 ps resolution are very valuable for practical applications, but also very challenging for research.

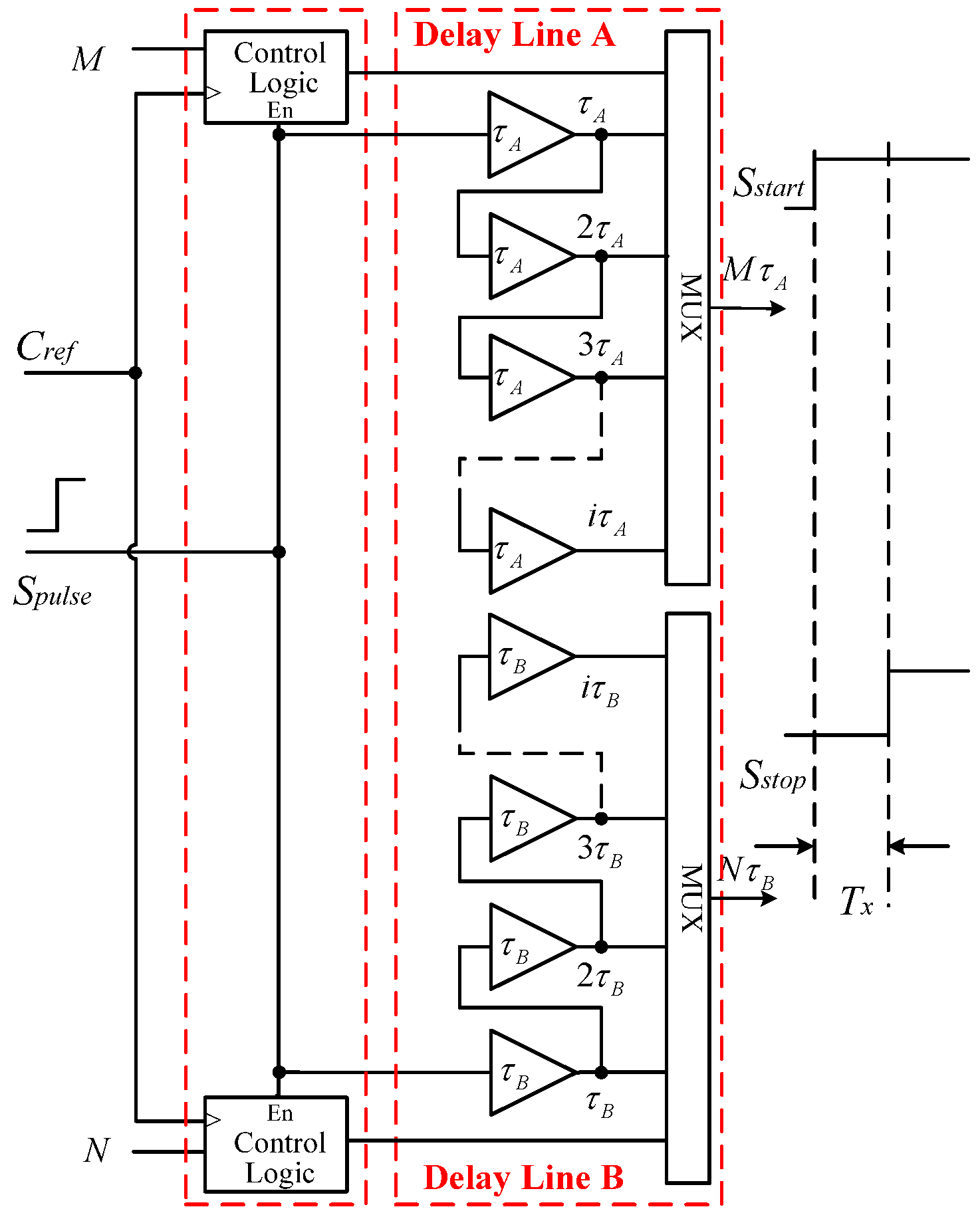

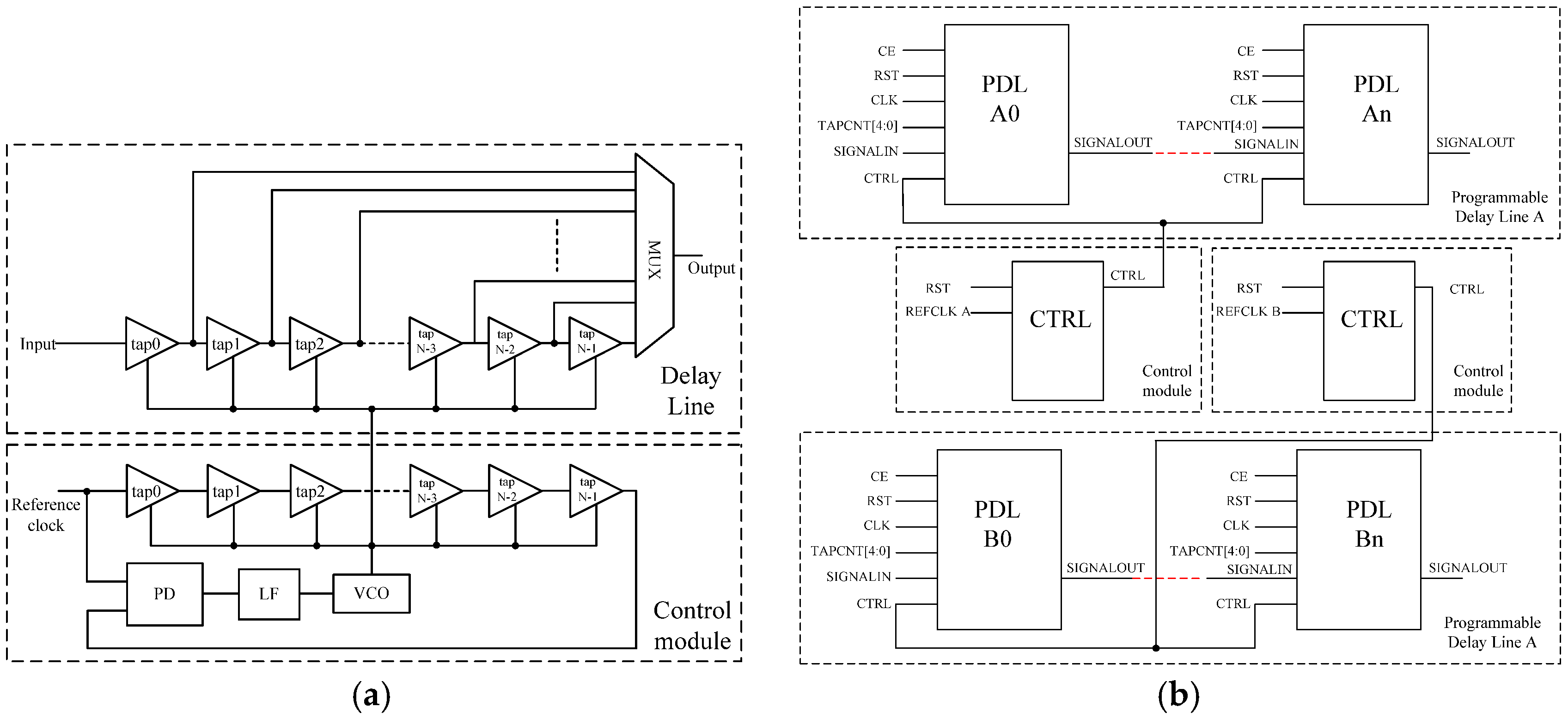

In this paper, a novel realization of a DTC based on an FPGA device is proposed and tested. The obtained resolution is 1.02 ps, and the dynamic range is 590 ns. The proposed DTC benefits much from the coarse and fine Vernier delay line constructed by PDLs, which ensures a high performance delay. Meantime, the control module of PDL (programmable delay line) adopts a programmable close-loop feedback mechanism to adjust the tap delay of the delay lines, which improves the nonlinearity and stability of the DTC. Compared with the normal DTCs implemented in FPGA/ASIC devices, the proposed DTC achieves a higher resolution and improved nonlinearity and stability.

The remainder of the paper is organized as follows.

Section 2 describes the principle and structure of the proposed DTC.

Section 3 presents the realization of the DTC system.

Section 4 shows the experimental results, and

Section 5 summarizes the paper.

3. Circuit Implementation

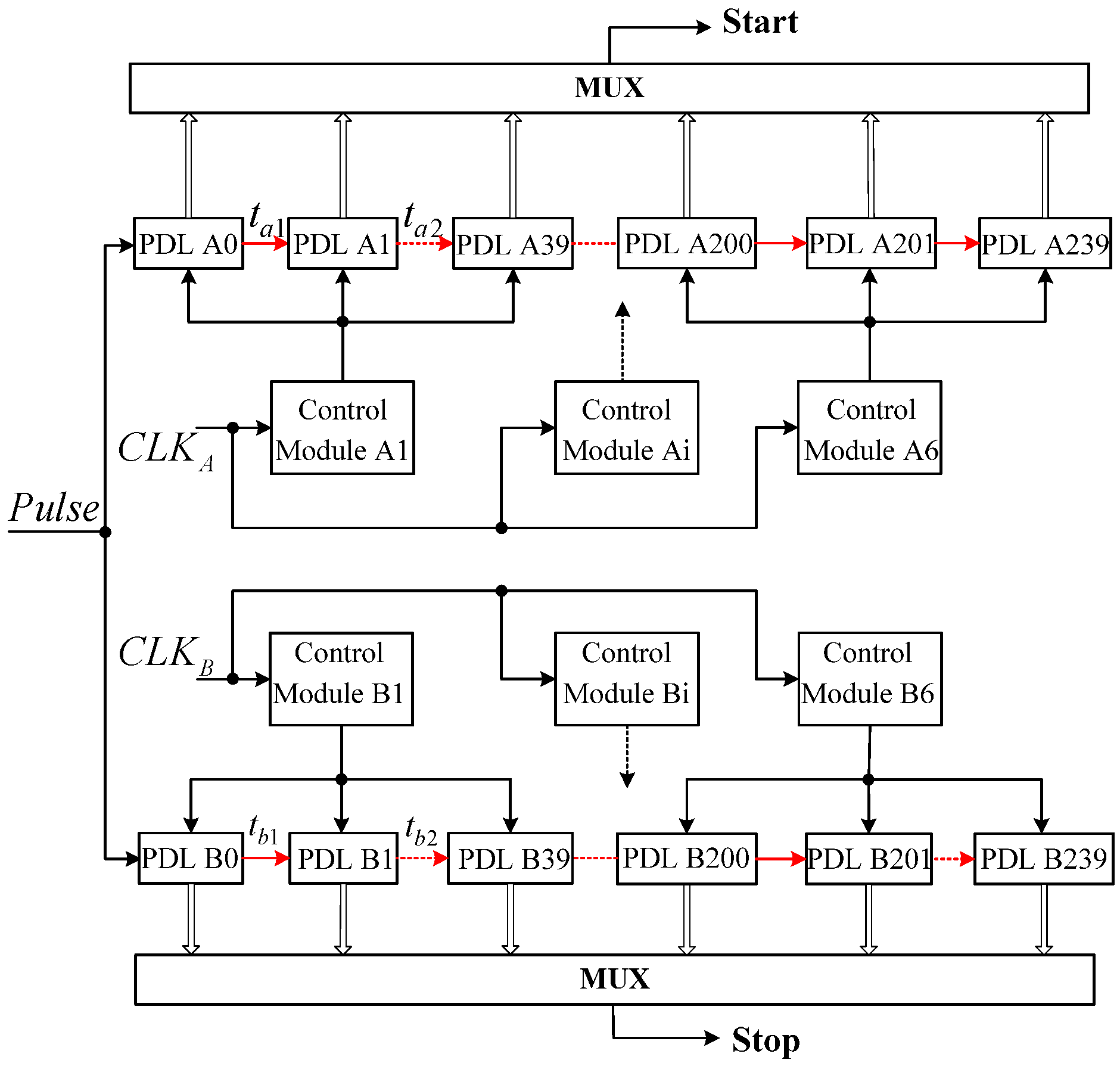

The DTC shown in

Figure 5 is implemented in the Xilinx Virtex-6 FPGA chip. Part of the place and route of the Vernier delay line constructed by PDLs is shown in

Figure 6. In the figure, the delay line on the left is the Start delay line, and the delay line on the right is the Stop delay line. The cyan lines are the propagation paths between the PDLs. In the figure, 1.459 ns is the path delay between PDL A68 and PDL A69, and 1.446 ns is the path delay between PDL B68 and PDL B69, which corresponds with

Figure 7. The control modules of the Start delay line are marked in red, and those of the Stop delay line are marked in blue. The green lines indicate the controlling boundary of a single control module.

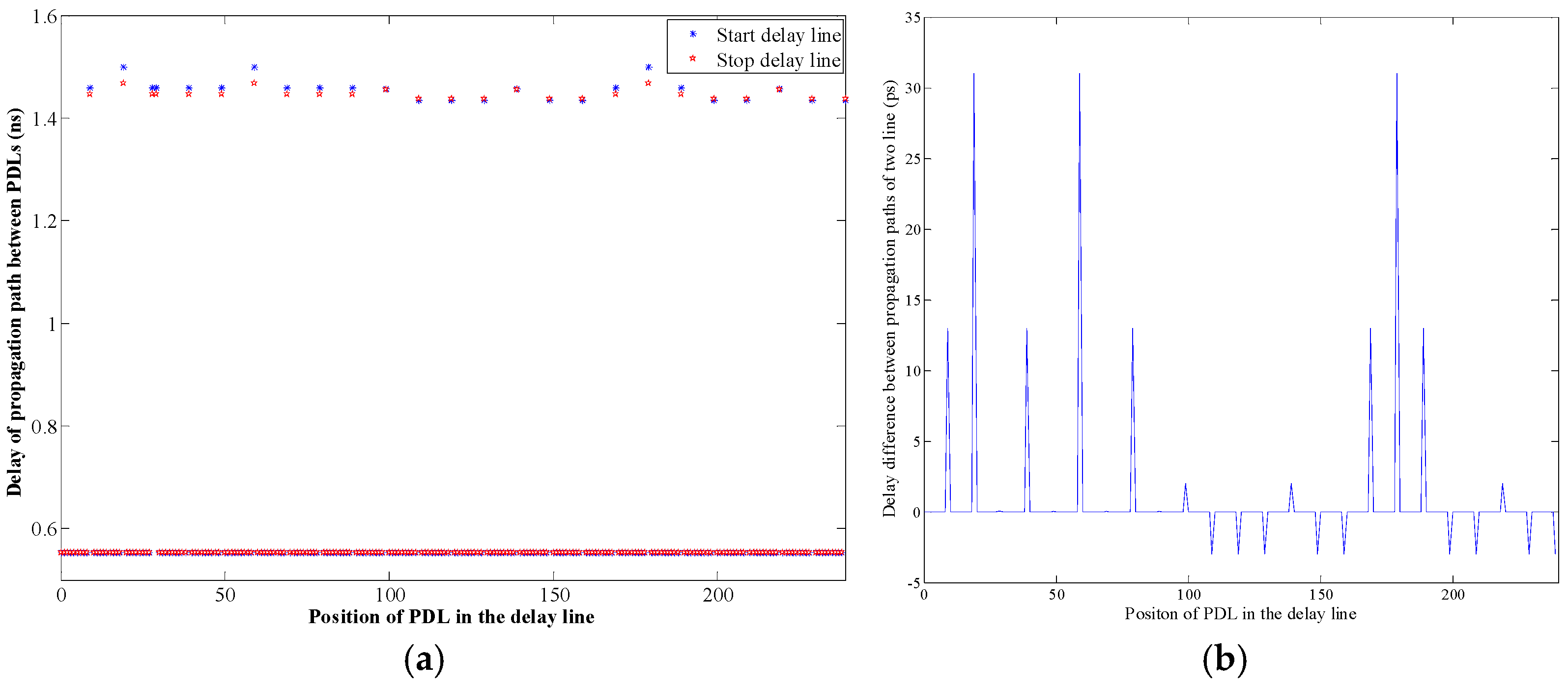

One of the most important delays that may affect the performance of the DTC is the delay of propagation paths between the PDLs. The time delay of the propagation paths (

ta and

tb in

Figure 5) is shown in

Figure 7a, and the data are obtained from the FPGA editor (a design tool of the Xilinx ISE design suite). In the figure, most of the propagation paths on the Start delay line and the Stop delay line are equal and can be offset. The largest delay difference is 31 ps as shown in

Figure 7b. The integral delay difference between the Start delay line and the Stop delay line is 202 ps. The measurement error introduced by the propagation paths is a fixed error and can be compensated.

Another delay is the intrinsic delay of PDL, which is about 400 ps [

12,

13]. The intrinsic delay indicates the time delay of a PDL when the number of working delay taps is set to 0. For a delay line with 240 PDLs, the intrinsic delay is about 100 ns. However, the intrinsic delay is identical on both lines. In the design shown in

Figure 5, the time interval signals (Start and Stop) is generated at the last PDL of the delay lines, which does not need multiplexers to collect and select the output signal. By doing this, the measurement error caused by the intrinsic delay of PDL can be offset completely.

4. Experiments

4.1. Setup of Experiments

For function verification and performance evaluation, the Xilinx Virtex-6 FPGA chip is adopted for circuit realization. The evaluation board ML605 (designed by Xilinx Inc., San Jose, CA, USA) is used. The reference clock of the board is a crystal oscillator with a frequency of 200 MHz. CLKA and CLKB are generated by the Mixed-Mode Clock Managers (MMCMs), which is realized by multiplying or fractional dividing the reference clock. CLKA and CLKB are connected to global clock buffers, which is a dedicated interconnect network specifically designed to reach all clock inputs of the various resources inside an FPGA chip. These networks feature low skew and low duty cycle distortion, low power, and improved jitter tolerance.

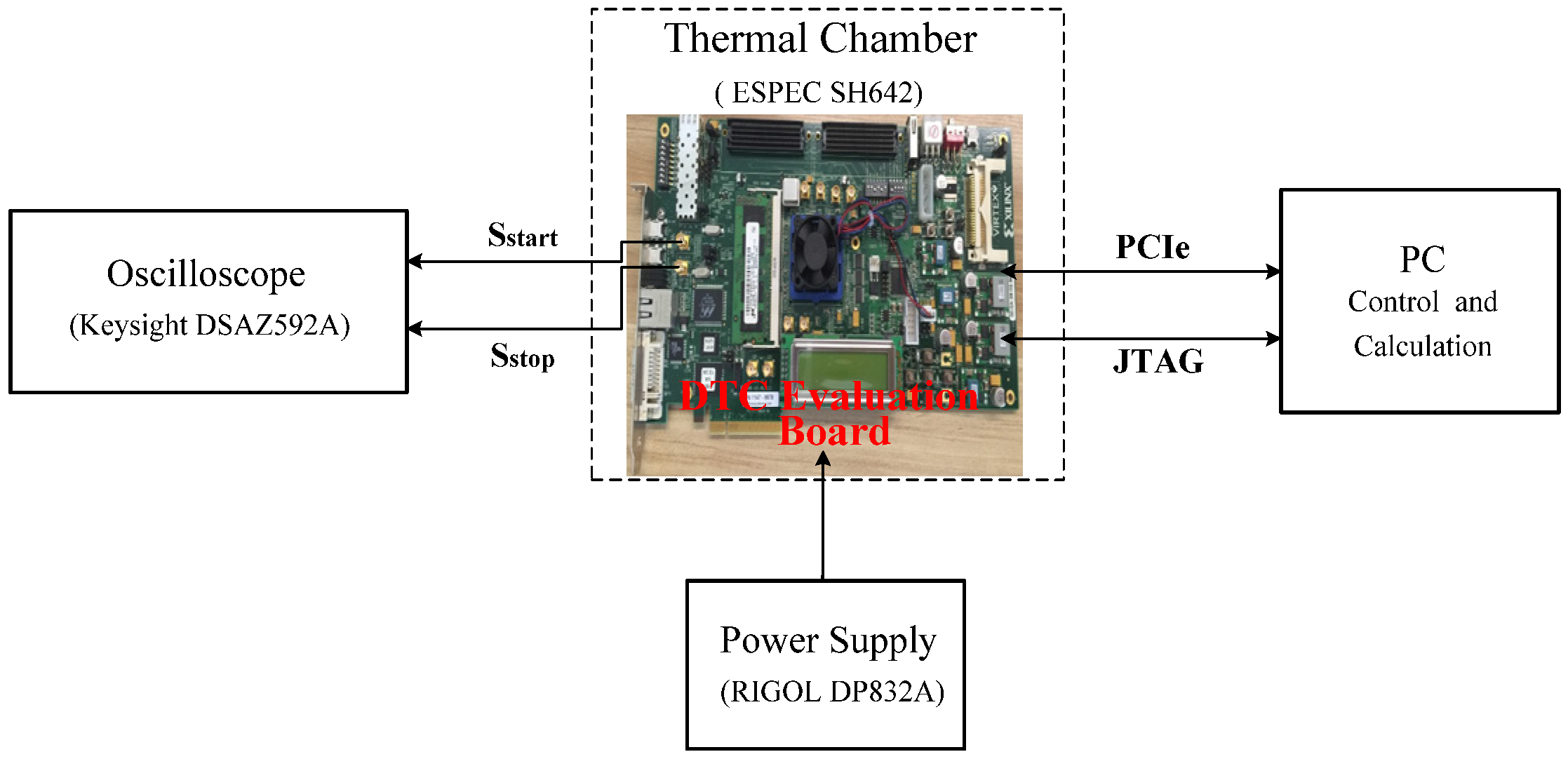

The DTC evaluation board communicates with the PC via PCI (peripheral component interconnect) Express interface. The time interval signal generated is outputted through the SMA (small-motion accelerometer) connector, which has the advantage of low noise. The test system of the DTC is shown in

Figure 8. The evaluation board is supplied by RIGOL DP832A (RIGOL Technologies Inc., Beijing, China), and a digital oscilloscope (Keysight DSAZ592A, Keysight Technologies, Santa Rosa, CA, USA) is employed to measure the time interval generated. Additionally, a thermal chamber (ESPEC SH642, designed by ESPEC Corp., Osaka, Japan) is utilized to evaluate the temperature stability of the DTC.

4.2. Analysis of Clock Jitter and Phase Noise

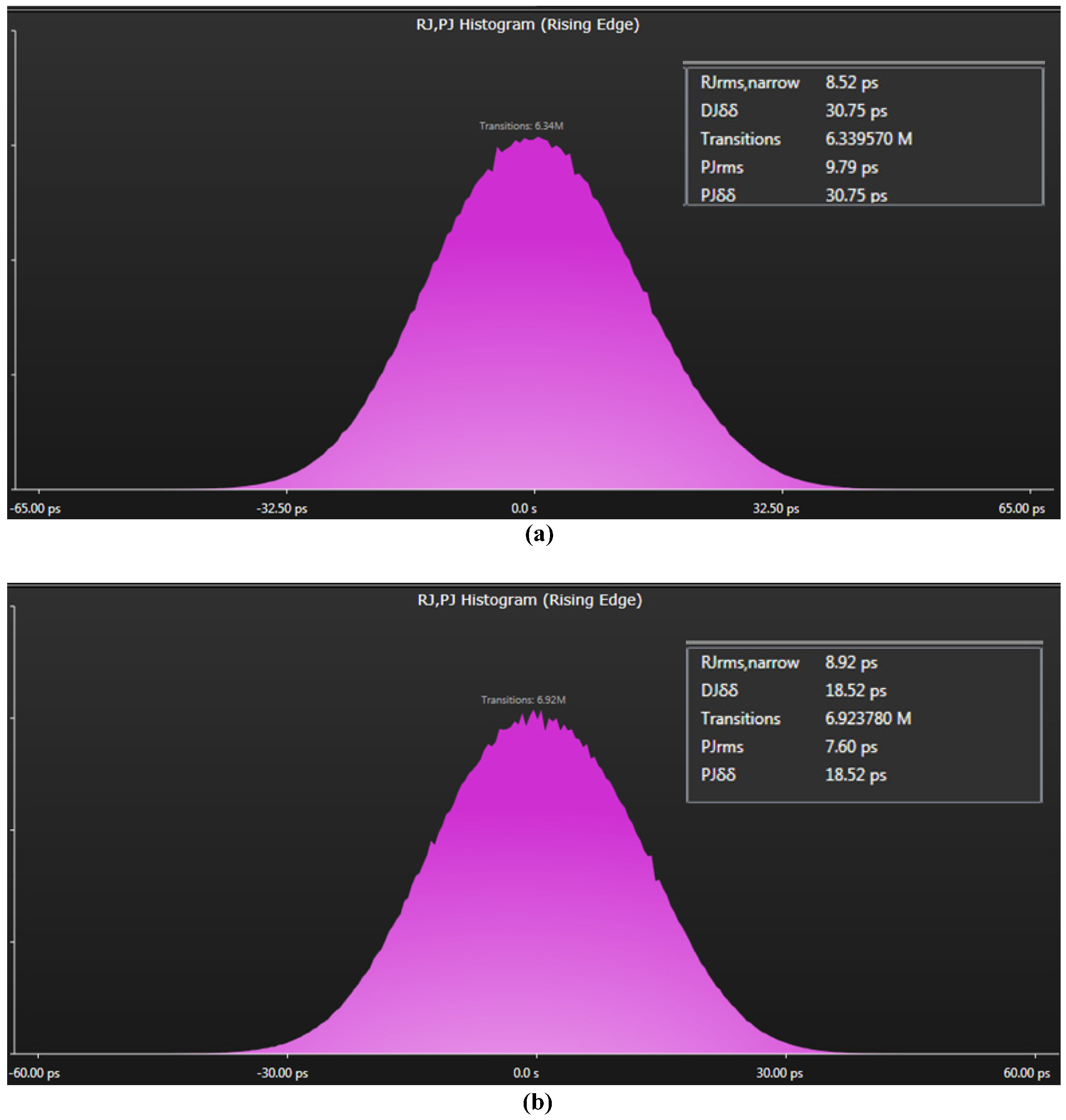

In this paper, CLKA and CLKB are generated by the MMCMs. The input clock is from an oven controlled crystal oscillator (OCXO) with a frequency stability of ±0.3 ppb. In the realization, the MMCM (mixed-mode clock managers) parameter is enabled to minimize output jitter. Experiments are conducted to measure the jitter of CLKA and CLKB.

Figure 9 shows the Random Jitter, Period Jitter (RJ, PJ) Histogram of CLKA and CLKB, which is obtained above 6 × 10

6 transitions. The RJ of CLKA is 8.52 ps, and the PJ of CLKA is 9.79 ps. The RJ of CLKB is 8.92 ps, and the PJ of CLKB is 7.60 ps. Here, all the values are root mean square (RMS) values.

The influence of the jitter on the performance of the proposed DTC is analyzed in two aspects. First, the difference in RJ between CLKA and CLKB is −0.4 ps, and that of PJ is 2.39 ps. The proposed DTC is based on the Vernier delay line structure, which is a symmetrical structure. The clock jitter exists on both of the delay lines. Then, the influence of jitter of CLKA and CLKB on the DTC can be offset by the two delay lines to some degree. Second, the control module of the PDL is a close-loop structure, which can reduce the jitter of the clocks.

The period jitter of CLKA and CLKB is related to the phase noise. The relation between the period jitter and the phase noise can be calculated from Equation (9) [

14]. In Equation (9),

JPER is the period jitter,

fc is the clock frequency, and

L(

f) is the phase noise spectrum. The period jitter of CLKA and CLKB are shown in

Figure 9, and both of them are <10 ps. The phase noise and jitter of CLKA and CLKB can transmit to the control modules of PDL and affect the time delay of delay taps. The largest jitter on tap delay of PDL is ±5 ps [

13]. Though the theoretical resolution of the proposed DTC is 1 ps, and the measurement accuracy is lower, which is about 10 ps (RMS value).

4.3. Average Resolution and Nonlinearity Tests

The performance of the Virtex-6 DTC is measured within the range of 0~500 ns. When CNT

A and CNT

B are both 0, the obtained time interval is 205 ps. When CNT

A and CNT

B are both 96, the obtained time interval is 303 ps. Therefore, the obtained average resolution is (303 − 205)/96 = 1.02 ps. According to

Figure 7, a 202 ps fixed error is introduced by the delay difference between the propagation paths of the Start delay line and the Stop delay line. Therefore, calibration work is done by adding the time delay of the Stop delay line by 205 ps.

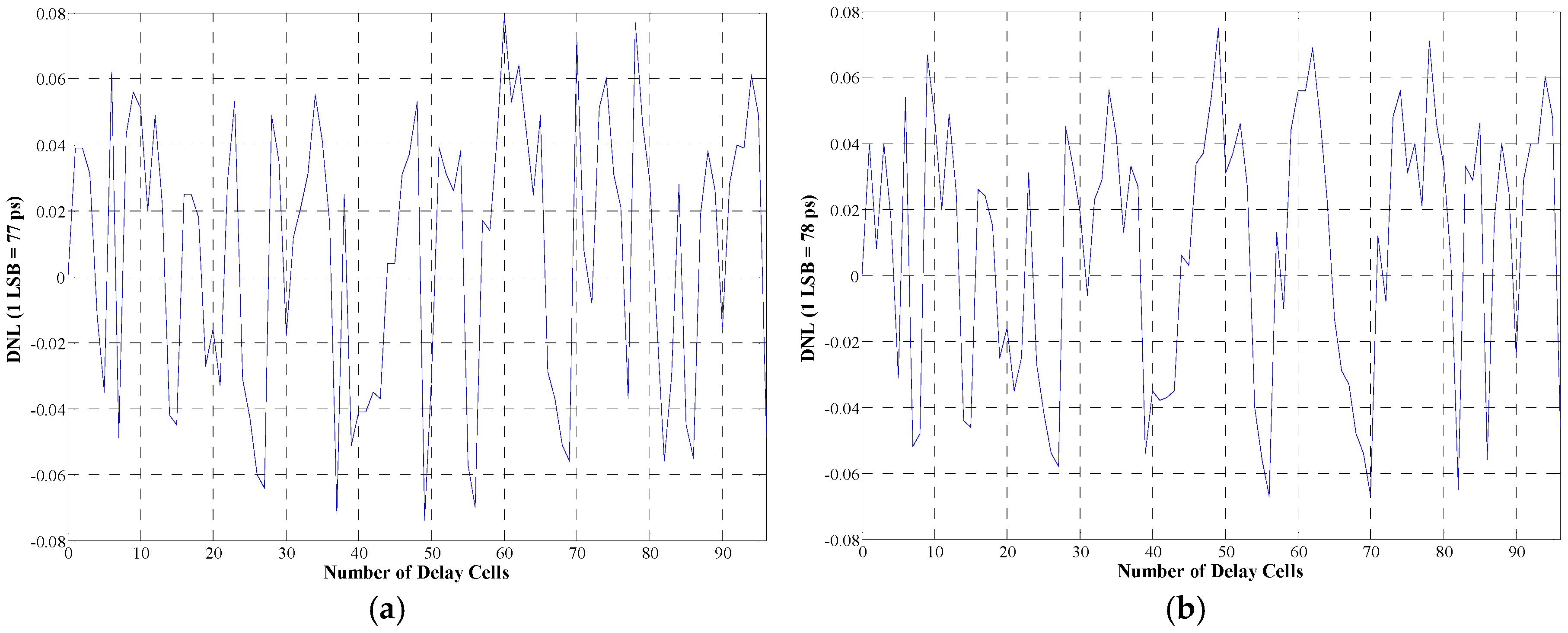

The DNL of the delay cells in PDLs are tested and analyzed. The DNL of delay cells in PDL A237~PDL A239 and PDL B237~PDL B239 are shown in

Figure 10. The nonlinearity tests are performed in 96 taps. In the tests, we set the number of delay taps within the range of 0~96 and measure the time delay between the input of PDL A237 and the output of PDL A239 through the oscilloscope. The DNL of delay cells can be calculated from the measurement results. The DNL of delay cells in PDL A237~PDL A239 is −0.074~+0.079 LSB (least significant bit, 1 LSB = 77 ps). The DNL of delay cells in PDL B237~PDL B239 is measured with the same method, and the obtained DNL is −0.065~+0.075 LSB (1 LSB = 78 ps). The DNL of delay cells in PDL A237~PDL A239 and PDL B237~PDL B239 indicates the nonlinearity of the delay cells in two PDL delay lines. The largest DNL error is about 6 ps, which is mainly introduced by the jitter of clock signals and the jitter of the control module of PDL.

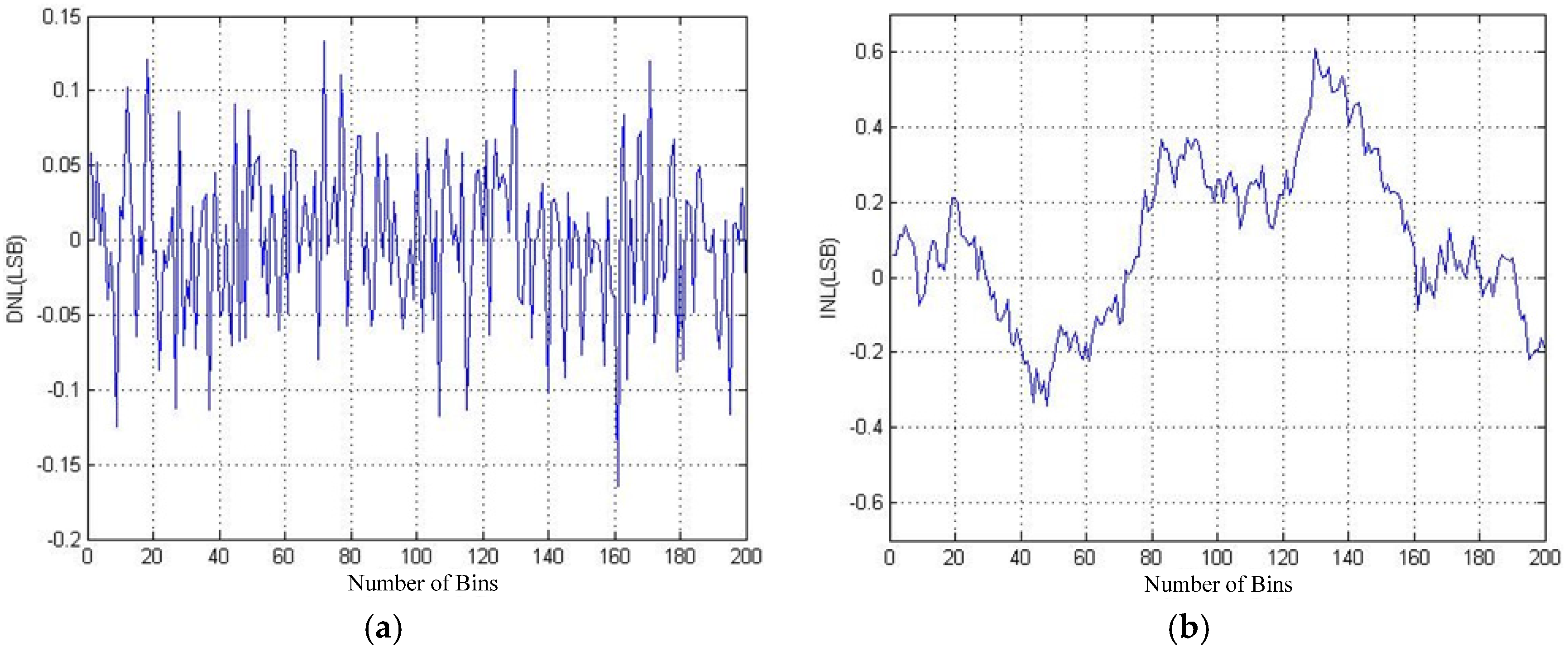

The DNL and INL (integral nonlinearity) of the proposed Virtex-6 FPGA-based DTC are shown in

Figure 11. The delay characteristic and the structure of all the PDLs in the delay line are nearly the same. The nonlinearity tests are performed in 200 bins. The DNL is −0.17~+0.13 LSB and the INL is −0.35~+0.62 LSB. The operation range of the proposed DTC is as large as 590 ns. Time intervals larger than 96 ps are generated by increasing the number of delay taps in Line B and have good delay linearity, which is benefited from the structure of the programmable delay line. Therefore, the nonlinearities are measured within the range of 5 ns and can indicate the nonlinearities of the proposed DTC within the operation range.

4.4. Temperature and Voltage Stability Tests

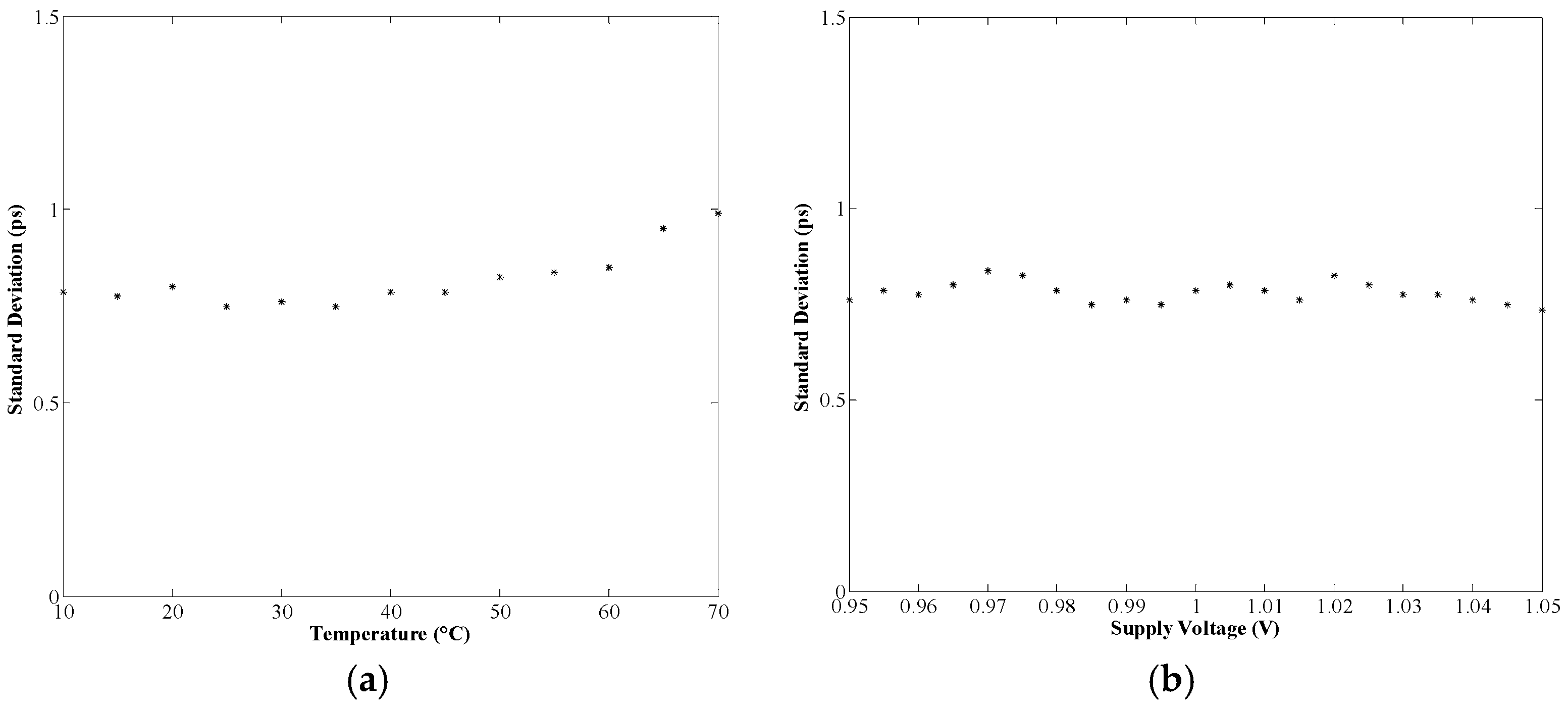

The temperature stability of the proposed DTC is tested on the evaluation board with the help of a thermal chamber. A constant time interval (5 ns) is generated under different temperature, in a range of 10~70 °C. The time interval is measured by the digital oscilloscope, and measurement under a temperature is repeated 50 times. The standard deviation under different temperature is shown in

Figure 12a, which indicates that the proposed DTC is less sensitive to variations of temperature when compared with other DTCs implemented in a similar FPGA device [

10].

The voltage tests are performed using the DC power supply RIGOL DP832A (RIGOL Technologies Inc., Beijing, China). The nominal operating voltage of the DTC board is 1 V, which is the internal supply voltage of the FPGA device. In the tests, the supply voltage of the FPGA is changed within the range of 0.95~1.05 V with an interval of 5 mV. A constant time interval (5 ns) is generated under different supply voltages at an ambient temperature of 25 °C. The time interval is measured by the digital oscilloscope, and measurement under a temperature is repeated 50 times. The standard deviation of the measurement results is shown in

Figure 12b. In the figure, with the change of supply voltage, the largest differences in standard deviation is less than 0.5 ps, which indicates that the proposed DTC is not sensitive to variations of supply voltage.

4.5. Comparison with Other DTCs

Table 1 compares the performance of the proposed DTC with previous work. Compared with other DTCs implemented in an FPGA device, the proposed DTC achieves the best resolution. The dynamic range and the linearity are also good among the DTCs in the table. The jitter and skew of the proposed DTC is larger than ASIC-based DTCs. That is mainly because the circuit and architecture of ASIC-based DTC is fully customized, while the FPGA is commercial and its architecture is not specialized for DTC.