Optimization of Additive and Current Conditions for Void-Free Filled Through-Silicon Via

Abstract

:Featured Application

Abstract

1. Introduction

2. Materials and Methods

3. Results and Discussion

3.1. Effect of Pretreatment

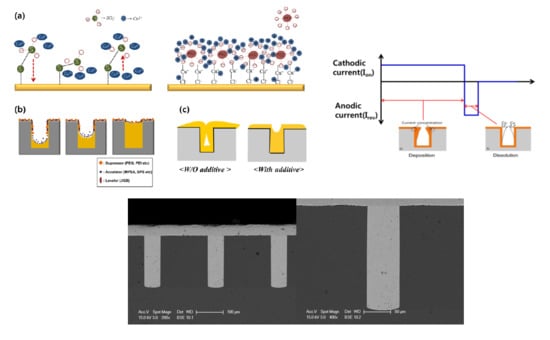

3.2. Cyclic Voltammetry (CV) Analysis

3.3. Tendency of Plating by Additive

3.4. Effect of On-Reverse Current Condition

4. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Hong, S.C.; Lee, W.G.; Kim, W.J.; Kim, J.H.; Jung, J.P. Reduction of defects in TSV filled with Cu by high-speed 3-step PPR for 3D Si chip stacking. Microelectron. Reliab. 2011, 51, 2228–2235. [Google Scholar] [CrossRef]

- Lu, Y.; Cao, H.Y.; Sun, Q.; Ling, H.Q.; Li, M.; Sun, J.Y. Investigation of competitive adsorption between accelerator and suppressor in TSV copper electroplating. Presented at the 13th International Conference on Electronic Packaging Technology & High Density Packaging, Guilin, China, 13–16 August 2012. [Google Scholar]

- Datta, M. Electrochemical processing technologies in chip fabrication: Challenges and opportunities. Electrochim. Acta 2003, 48, 2975–2985. [Google Scholar] [CrossRef]

- Li, Q.; Ling, H.Q.; Cao, H.Y.; Bian, Z.Y.; Li, M.; Mao, D. Through silicon via filling by copper electroplating in acidic cupric methanesulfonate bBath. Presented at the 2009 International Conference on Electronic Packaging Technology & High Density Packaging, Beijing, China, 10–13 August 2009. [Google Scholar]

- Zhang, Y.; Ding, G.; Wang, H.; Cheng, P.; Liu, R. Optimization of innovative approaches to the shortening of filling times in 3D integrated through-silicon vias (TSVs). J. Micromech. Microeng. 2015, 25, 045009. [Google Scholar] [CrossRef]

- Ngansso, S.; Fischer, P. TSV Through silicon via technology for 3D-integration. Presented at the 2010 IEEE International Memory Workshop, Seoul, Korea, 16–19 May 2010. [Google Scholar]

- Liu, D.P.; Park, S.B. Three-dimensional and 2.5 dimensional interconnection technology: State of the art. J. Electron. Packag. 2014, 136, 014001. [Google Scholar] [CrossRef]

- Radisic, A.; Lühn, O.; Philipsen, H.G.G.; El-Mekki, Z.; Honore, M.; Rodet, S.; Armini, S.; Drijbooms, C.; Bender, H.; Ruythooren, W. Copper plating for 3D interconnects. Microelectron. Eng. 2012, 88, 701–704. [Google Scholar] [CrossRef]

- Luhn, O.; Hoof, C.V.; Ruythoorenb, W.; Celis, J.P. Filling of microvia with an aspect ratio of 5 by copper electrodeposition. Electrochim. Acta 2009, 54, 2504–2508. [Google Scholar] [CrossRef]

- Chuang, H.C.; Lai, W.H.; Sanchez, J. An investigation of supercritical-CO2 copper electroplating parameters for application. J. Micromech. Microeng. 2015, 25, 015004. [Google Scholar] [CrossRef]

- Sokmen, U.; Stranz, A.; Fundling, S.; Wehmann, H.H.; Bandalo, V.; Bora, A.; Tornow, M.; Waag, A.; Peiner, E. Capabilities of ICP-RIE cryogenic dry etching of silicon: Review of exemplary microstructures. J. Micromech. Microeng. 2009, 19, 105005. [Google Scholar] [CrossRef]

- Elgrishi, N.M.; Rountree, K.J.; McCarthy, B.D.; Rountree, E.S.; Eisenhart, T.T.; Dempsey, J.L. A practical beginner’s guide to cyclic voltammetry. J. Chem. Educ. 2018, 95, 197–206. [Google Scholar] [CrossRef]

- Hasegawa, M.; Negishi, Y.; Nakanishi, T.; Osaka, T. Effects of additives on copper electrodeposition in submicrometer trenches. J. Electrochem. Soc. 2005, 152, C221–C228. [Google Scholar] [CrossRef]

- Moffat, T.P.; Wheeler, D.; Josell, D. Electrodeposition of copper in the SPS-PEG-Cl additive system. J. Electrochem. Soc. 2004, 151, C262–C271. [Google Scholar] [CrossRef]

- Yang, Z.; Wang, X.; Li, N.; Wang, Z.; Wang, Z. Design and achievement of a complete bottom-up electroless copper filling for sub-micrometer trenches. Electrochim. Acta 2011, 56, 3317–3321. [Google Scholar] [CrossRef]

- Dow, W.P.; Yen, M.Y.; Liao, S.Z.; Chiu, Y.D.; Huang, H.C. Filling mechanism in microvia metallization by copper electroplating. Electrochim. Acta 2008, 53, 8228–8237. [Google Scholar] [CrossRef]

- Tan, M.; Harb, J.N. Additive behavior during copper electrodeposition in solutions containing ClÀ, PEG, and SPS. J. Electrochem. Soc. 2003, 150, C420–C425. [Google Scholar] [CrossRef]

- Son, H.J.; Kim, T.Y.; Suh, S.J. A study on through-silicon-via using tri-block copolymer and pulse electroplating. J. Nanosci. Nanotechnol. 2016, 16, 8396–8401. [Google Scholar] [CrossRef]

- Chiu, Y.D.; Dow, W.P. Accelerator screening by cyclic voltammetry for microvia filling by copper electroplating. J. Electrochem. Soc. 2013, 160, D3021–D3027. [Google Scholar] [CrossRef]

- Dow, W.P.; Huang, H.S.; Yen, M.Y.; Huang, H.C. Influence of convection-dependent adsorption of additives on microvia filling by copper electroplating. J. Electrochem. Soc. 2005, 152, C425–C434. [Google Scholar] [CrossRef]

- Hofmann, L.; Ecke, R.; Schulz, S.E.T. Gessner, Investigations regarding through silicon via filling for 3D integration by periodic pulse reverse plating with and without additives. Microelectron. Eng. 2011, 88, 705–708. [Google Scholar] [CrossRef]

- Jin, S.H.; Wang, G.; Yoo, B.Y. Through-silicon-via (TSV) filling by electrodeposition of Cu with pulse current at ultra-short duty cycle. J. Electrochem. Soc. 2013, 160, D3300–D3305. [Google Scholar] [CrossRef]

| The Virgin Makeup Solution (VMS) | Additive | ||

|---|---|---|---|

| CuSO4·5H2O | 0.79 M | poly(ethylene glycol) (PEG) | 100–500 ppm |

| H2SO4 | 1.02 M | bis-(3-sodiumsulfopropyl disulfide) (SPS) | 1–5 ppm |

| Cl− | 1.4 mM | Janus Green B (JGB) | 10–50 ppm |

| On current | 10 mA/cm2 |

| Reverse current | 8, 16, 24 mA/cm2 |

| On time | 80 ms |

| Reverse time | 20 ms |

© 2018 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Shin, S.-H.; Kim, T.-Y.; Park, J.-H.; Suh, S.-J. Optimization of Additive and Current Conditions for Void-Free Filled Through-Silicon Via. Appl. Sci. 2018, 8, 2135. https://doi.org/10.3390/app8112135

Shin S-H, Kim T-Y, Park J-H, Suh S-J. Optimization of Additive and Current Conditions for Void-Free Filled Through-Silicon Via. Applied Sciences. 2018; 8(11):2135. https://doi.org/10.3390/app8112135

Chicago/Turabian StyleShin, Se-Hee, Tea-Yoo Kim, Jong-Hwan Park, and Su-Jeong Suh. 2018. "Optimization of Additive and Current Conditions for Void-Free Filled Through-Silicon Via" Applied Sciences 8, no. 11: 2135. https://doi.org/10.3390/app8112135

APA StyleShin, S.-H., Kim, T.-Y., Park, J.-H., & Suh, S.-J. (2018). Optimization of Additive and Current Conditions for Void-Free Filled Through-Silicon Via. Applied Sciences, 8(11), 2135. https://doi.org/10.3390/app8112135