Bridgeless Buck-Boost PFC Rectifier with Positive Output Voltage

Abstract

:1. Introduction

2. Overall System Configuration

- Step 1

- Under the input nominal voltage of 110 Vrms and rated output power, the integral gain ki is first set to zero, and then the proportional gain kp is gradually increased, so that the value of kp stops being increased until the output voltage reaches 75% of the desired value.

- Step 2

- Under the same conditions, the value of kp obtained from step 1 is fixed, and then the value of ki is gradually increased, so that the output voltage is stabilized at the desired value without oscillation.

- Step 3

- Under the input nominal voltage of 110 Vrms but different output powers, the values of kp and ki are finely tuned, so that the output voltage is stabilized at the desired value for all the output power range.

- Step 4

- Change the input voltage levels, and repeat step 3, so that the output voltage is stabilized at the desired value for all the input voltage range and all the output power range.

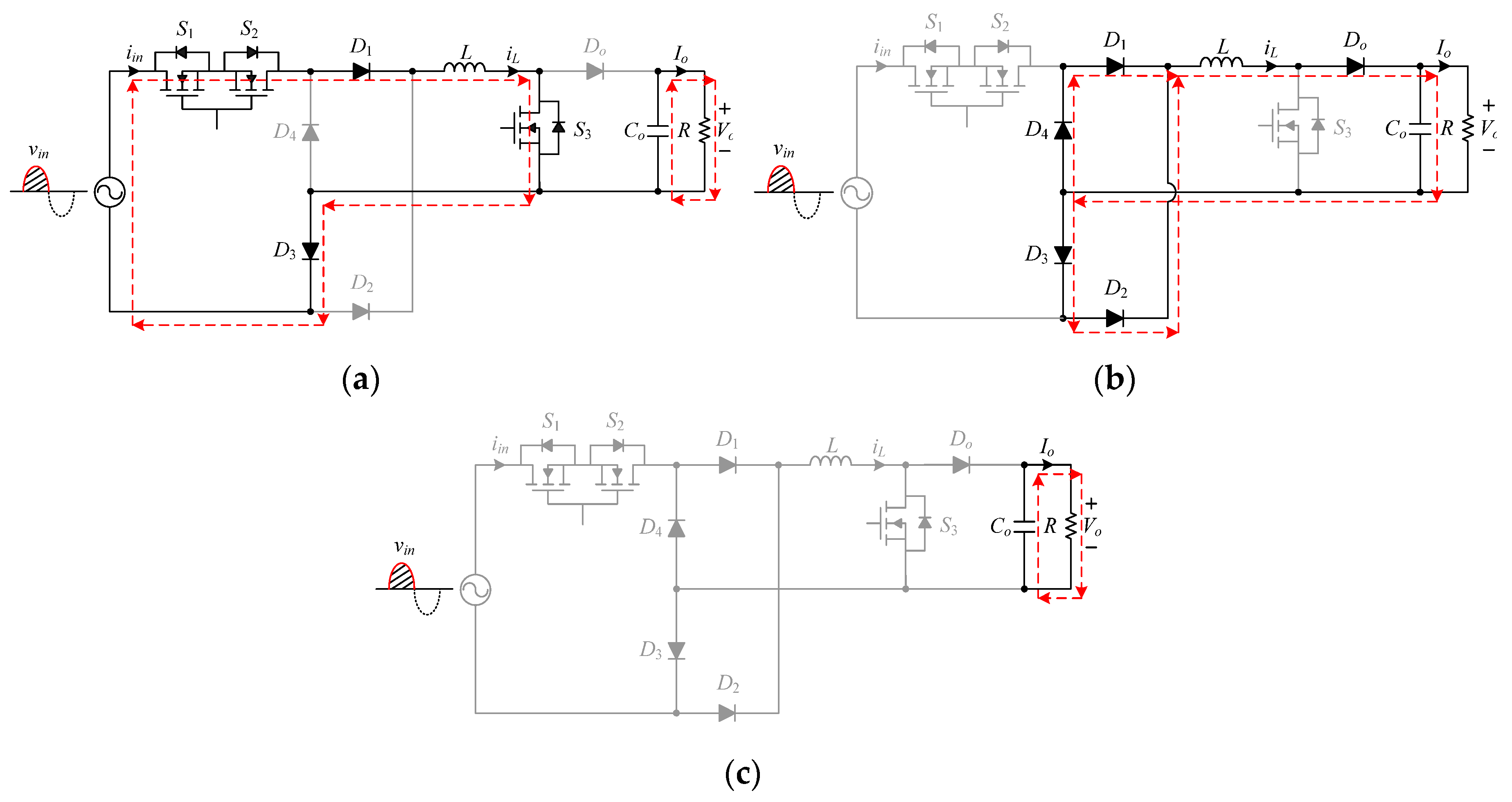

3. Basic Operating Principles

- (1).

- All the switches, diodes, inductor and capacitor are considered as ideal.

- (2).

- The PWM signals for S1, S2 and S3 are the same.

- (3).

- The value of Co is large enough to render the voltage across it constant at Vo.

- (4).

- The circuit operates in the DCM.

- (1)

- State 1 []: As the voltage vin is positive, S1, S2, S3, D1, and D3 are ON, whereas D2, D4, and Do are OFF. During this state, the current iin flows through S1, S2, S3, D1, D3, and L, as shown in Figure 3a. At the same time, as shown in Figure 2, the voltage across L is vin, making L magnetized and the current iL increasing linearly. Moreover, the output energy needed is offered by Co.

- (2)

- State 2 []: As the input voltage is still positive, S1, S2, and S3 are OFF, whereas D1, D2, D3, D4 and Do are ON. During this state, the current iin is zero, whereas the current iL continuously flows through these five diodes, as shown in Figure 3b. At the same time, as shown in Figure 2, the voltage across L is , rendering L is demagnetized and the current iL decreasing linearly. In addition, the output energy needed is provided by the energy stored in L.

- (3)

4. Design Considerations

4.1. Inductor Design

4.2. Output Capacitor Design

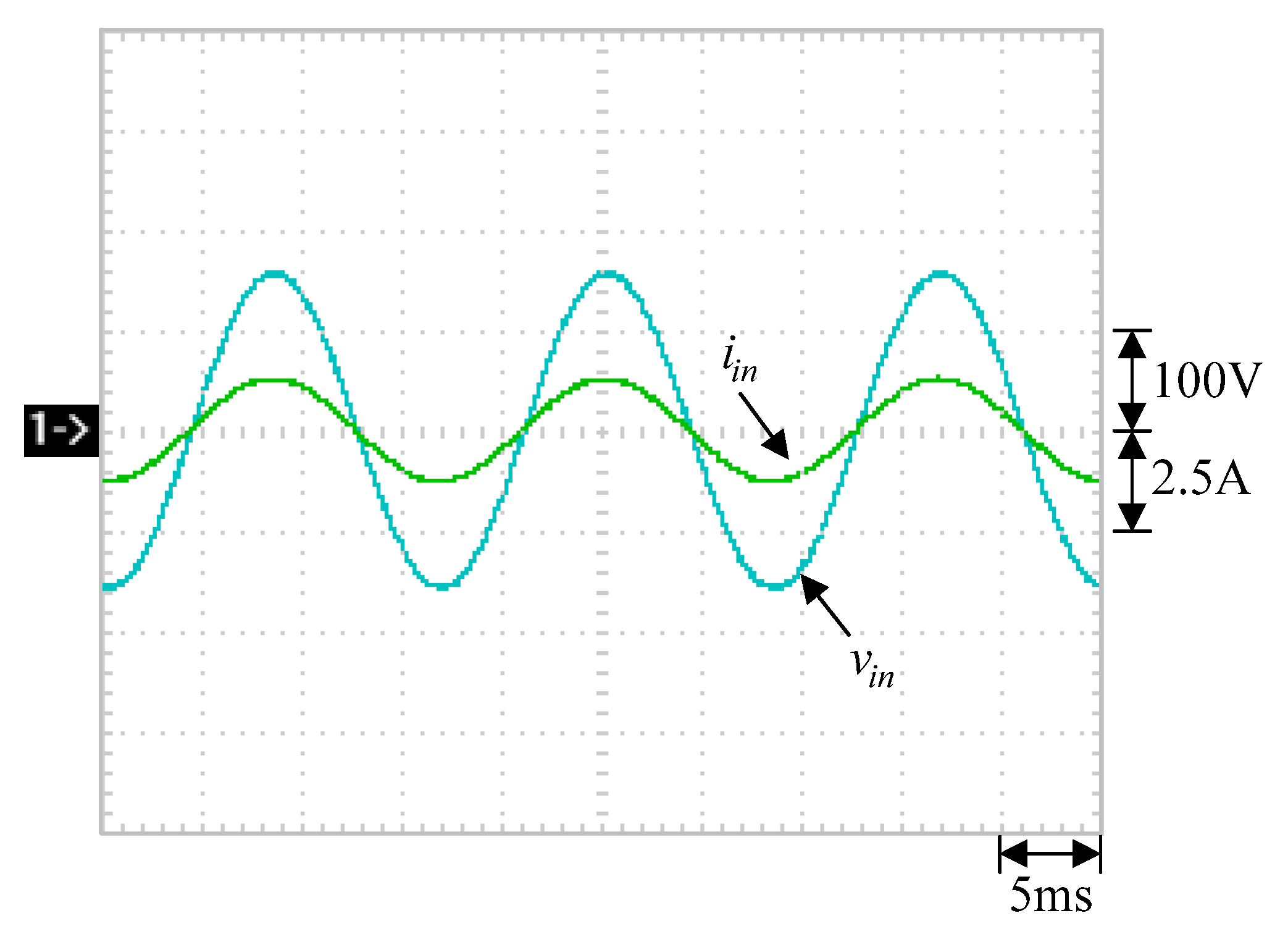

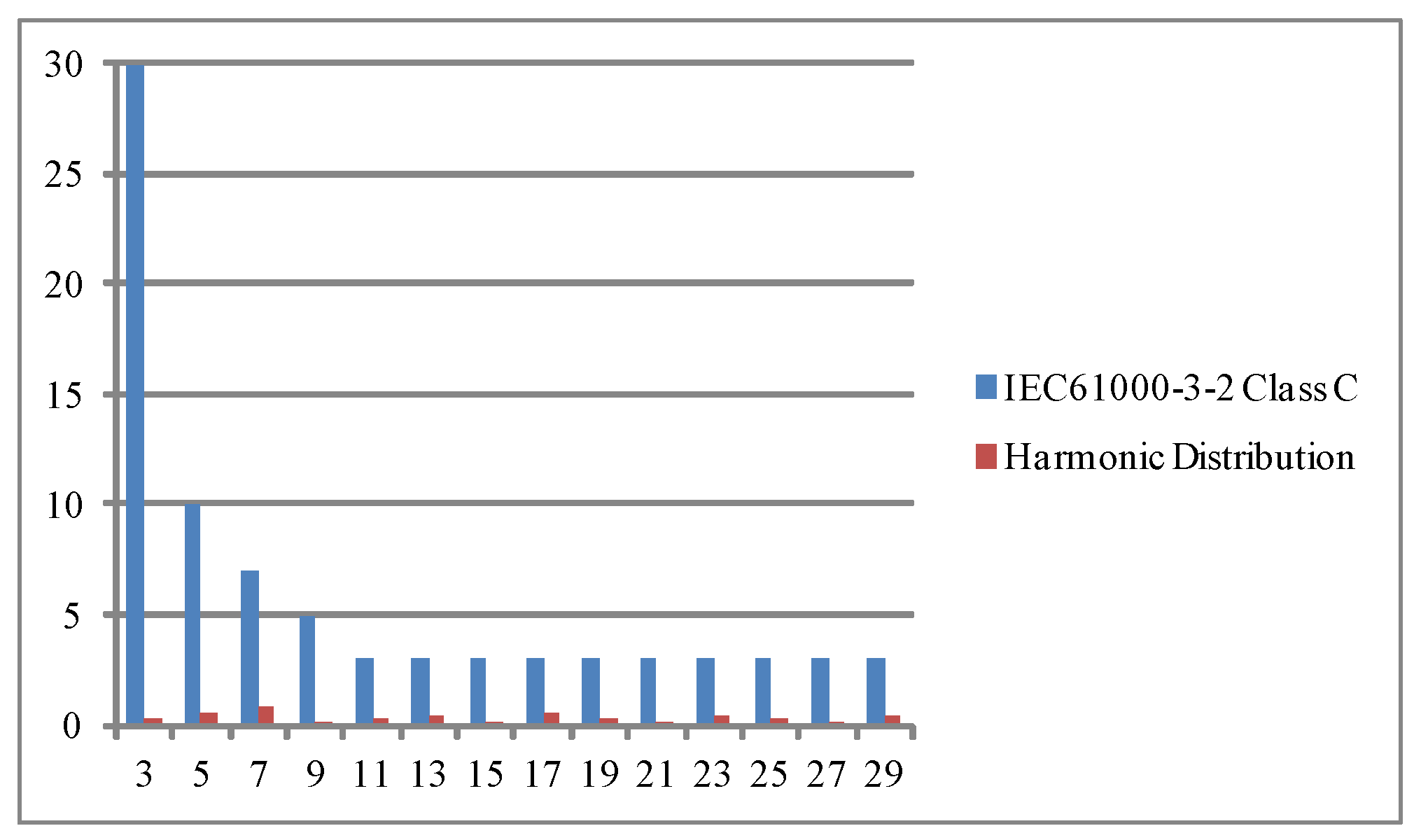

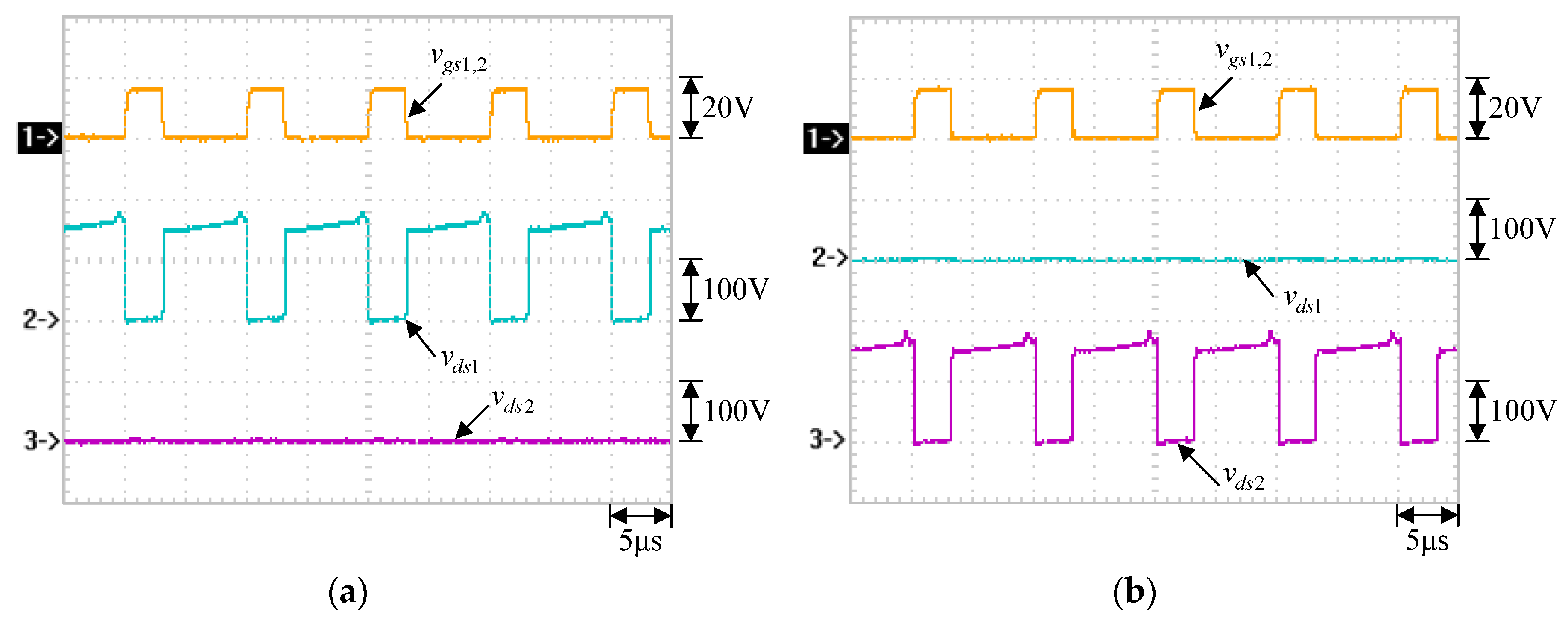

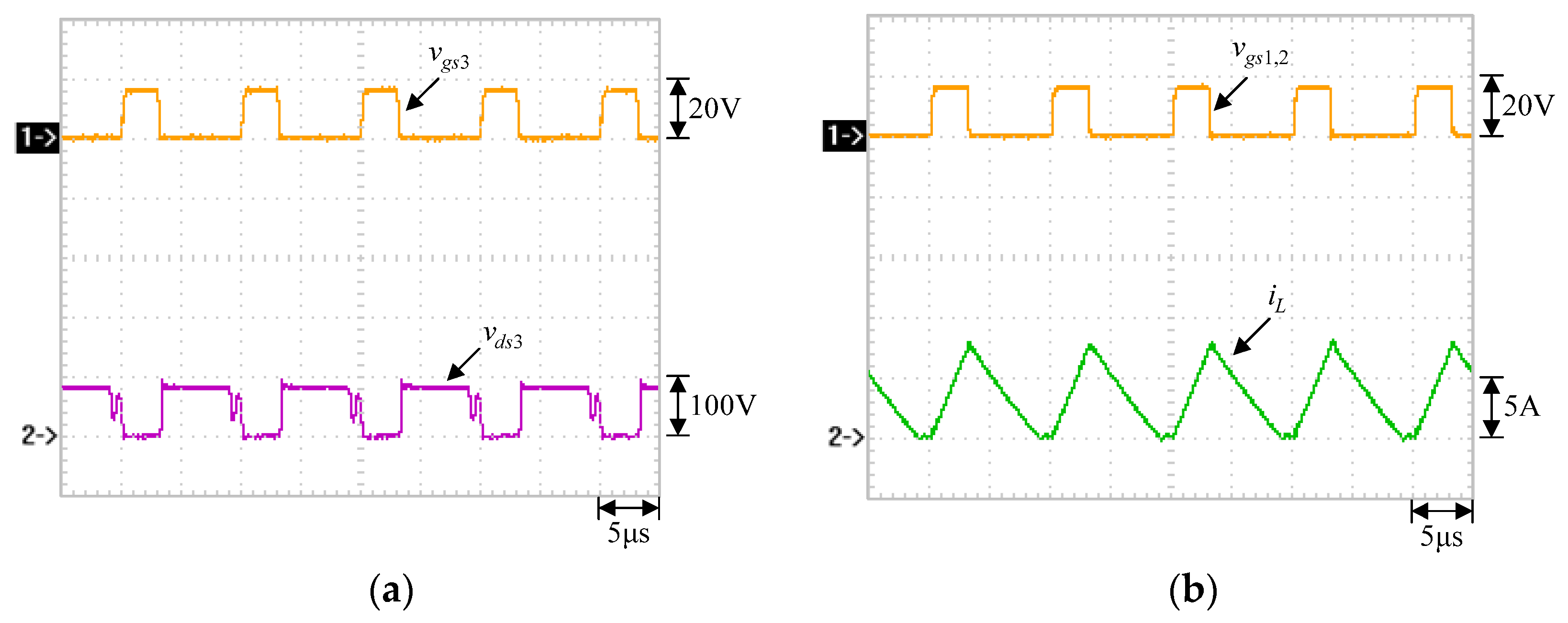

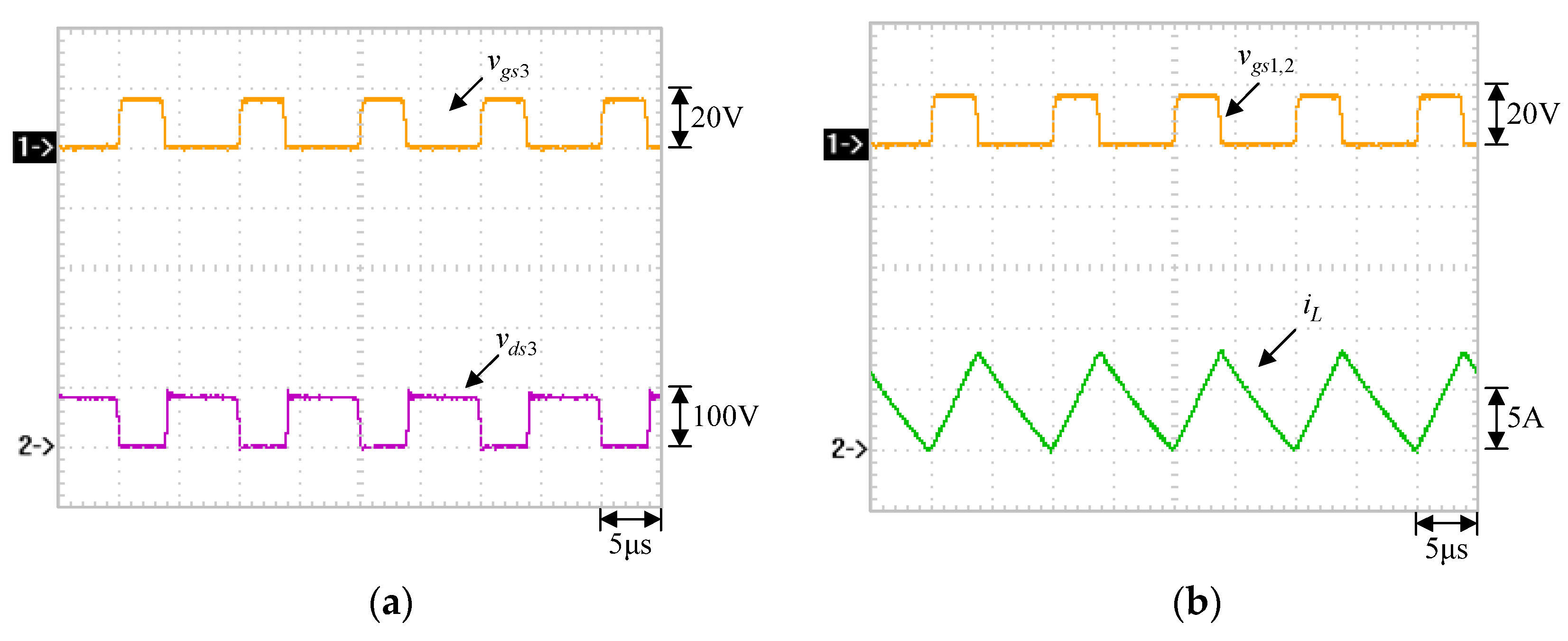

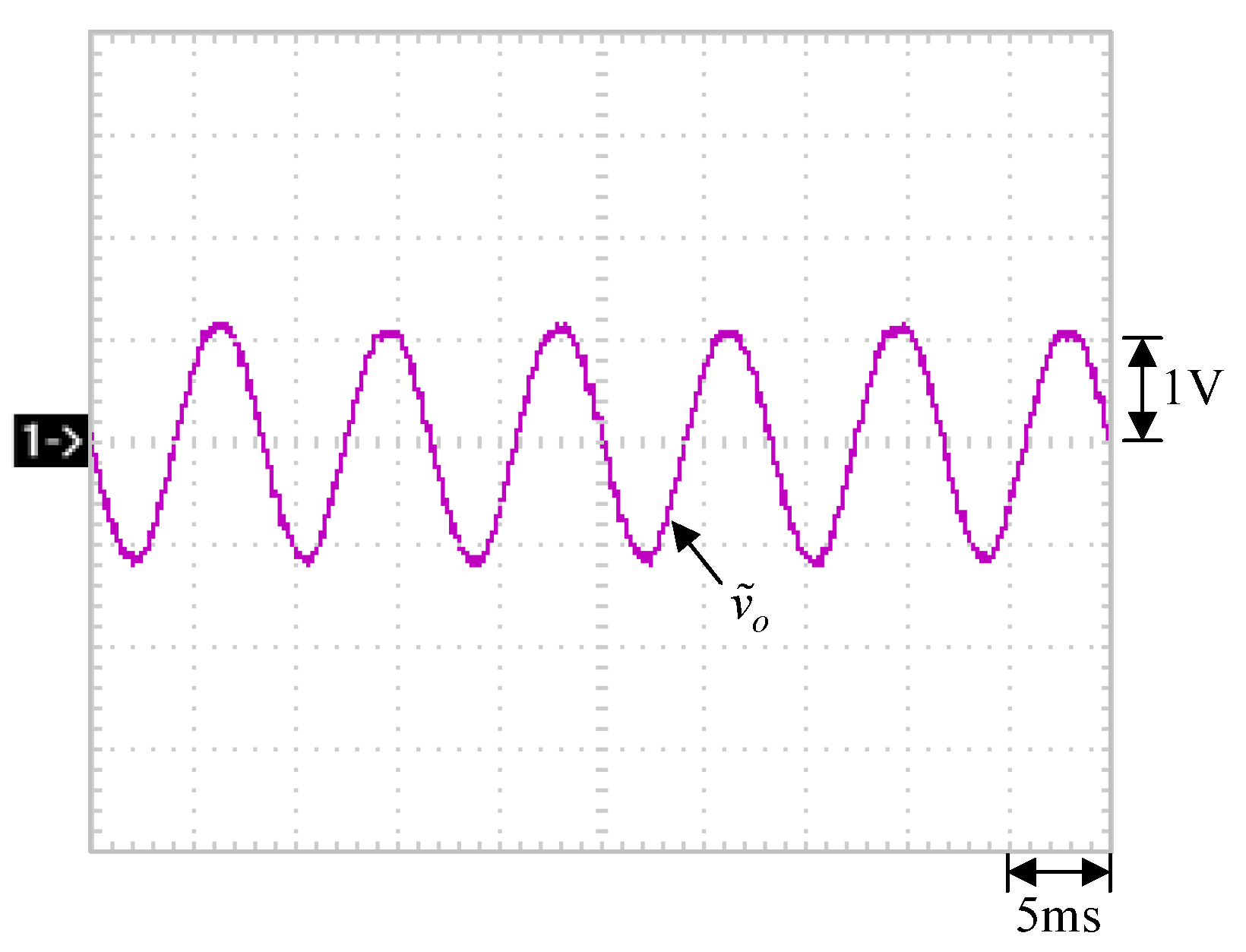

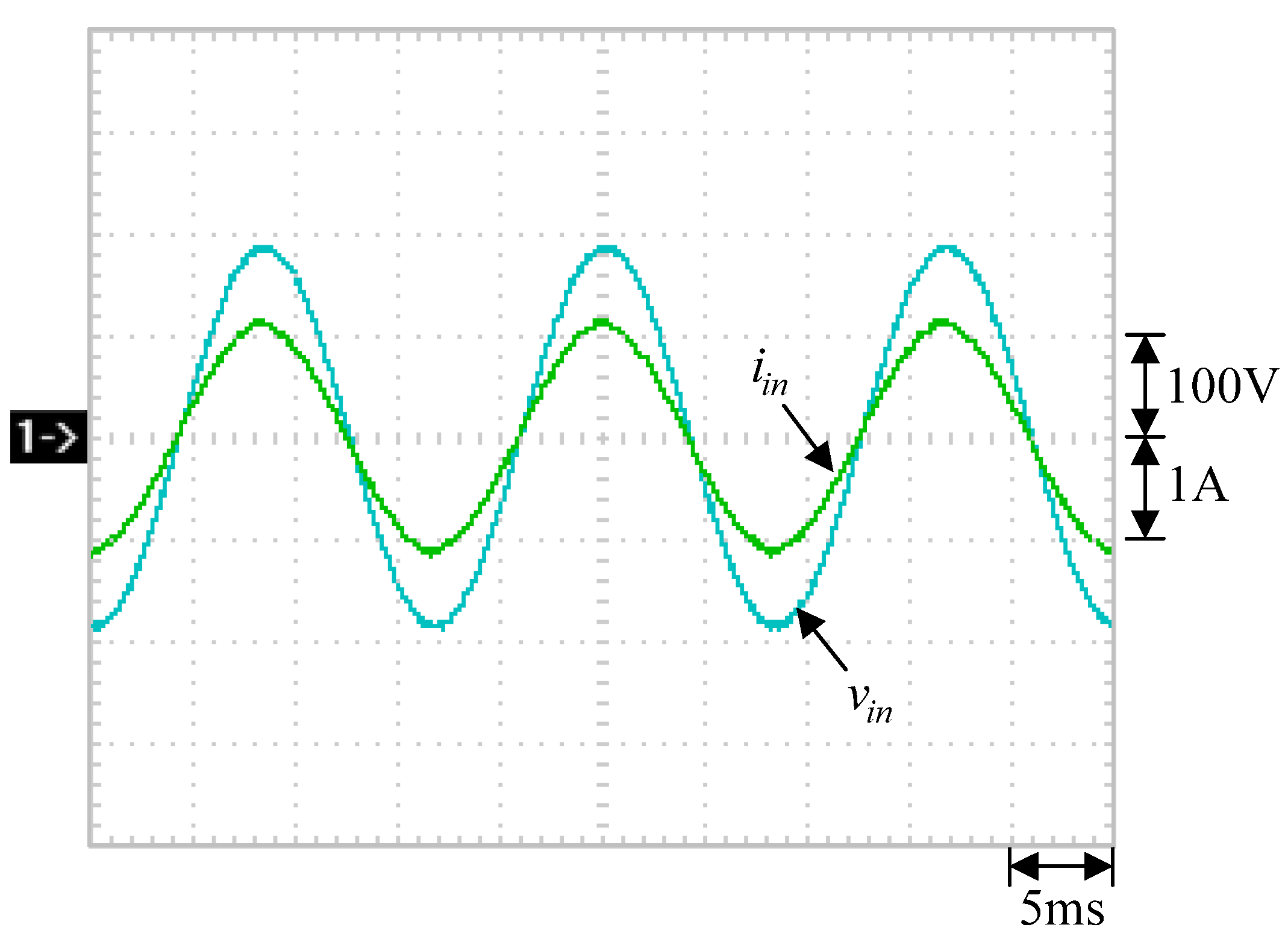

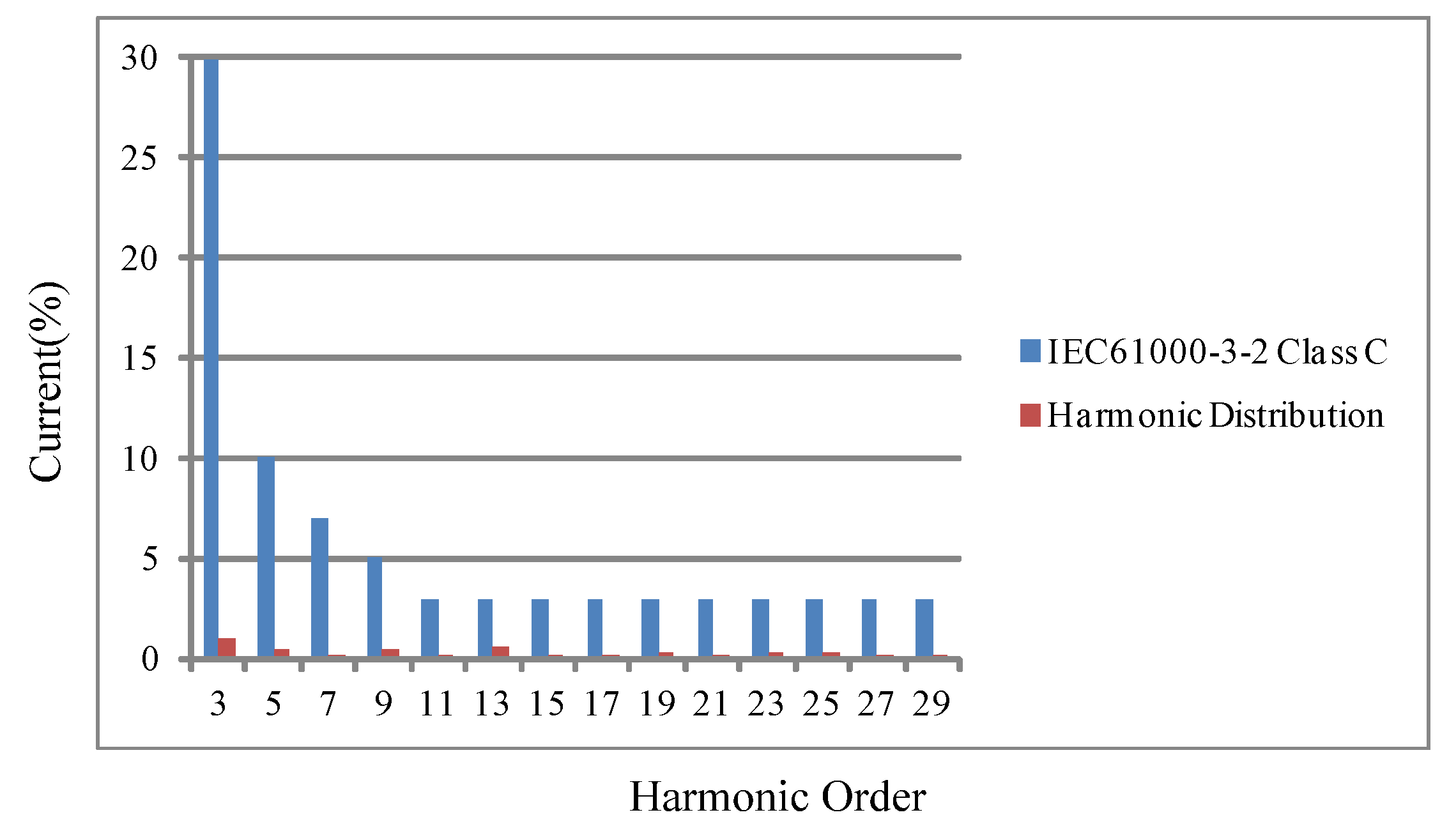

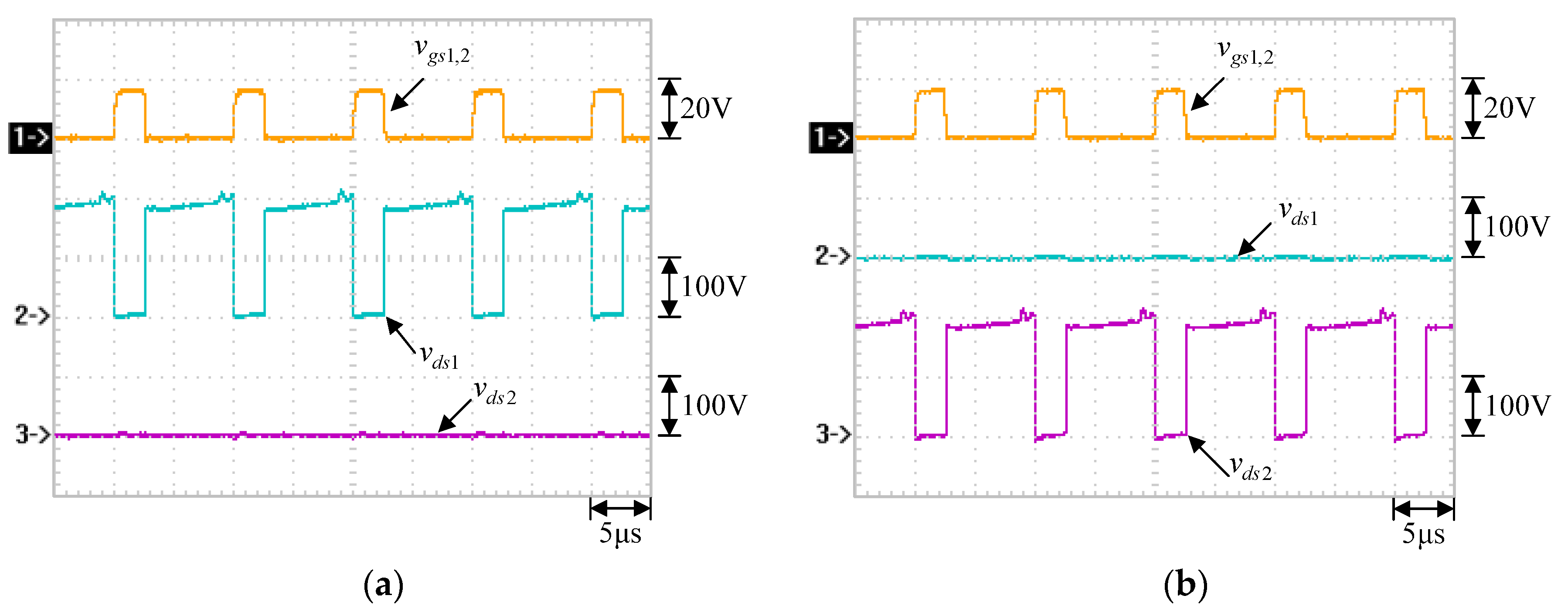

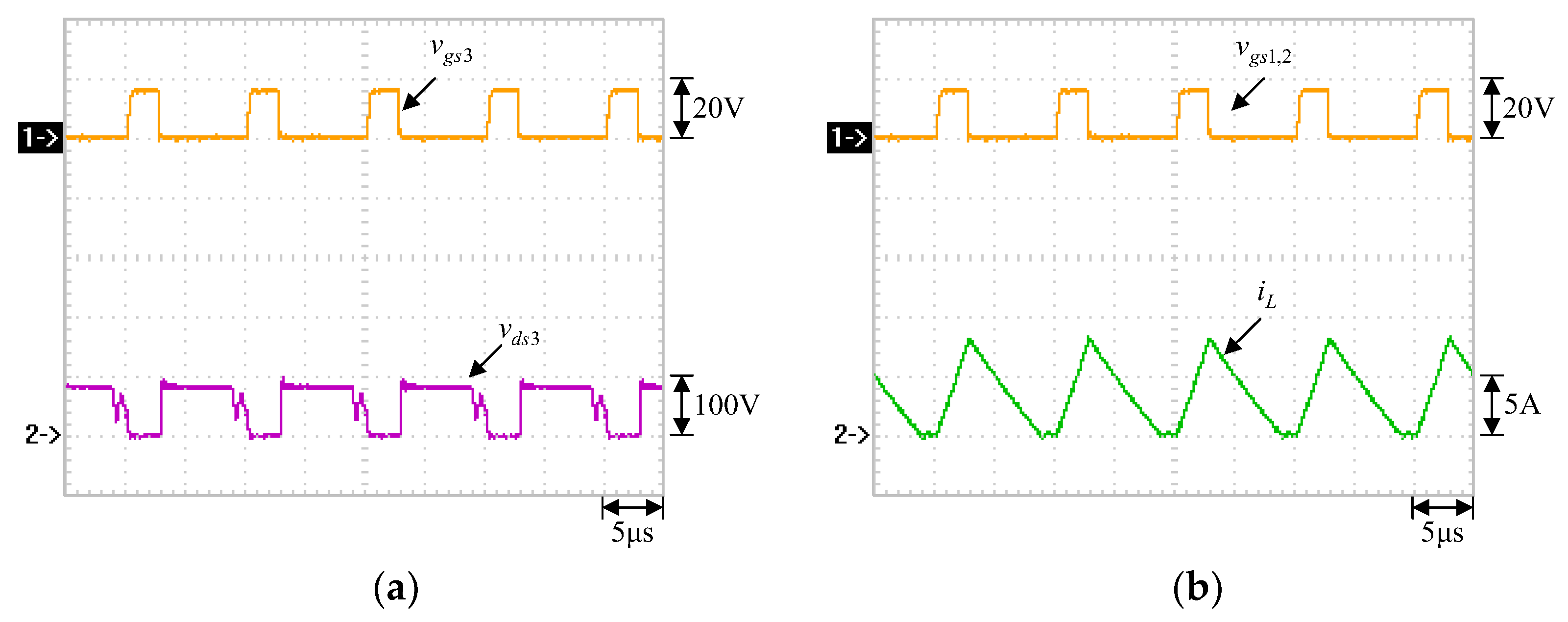

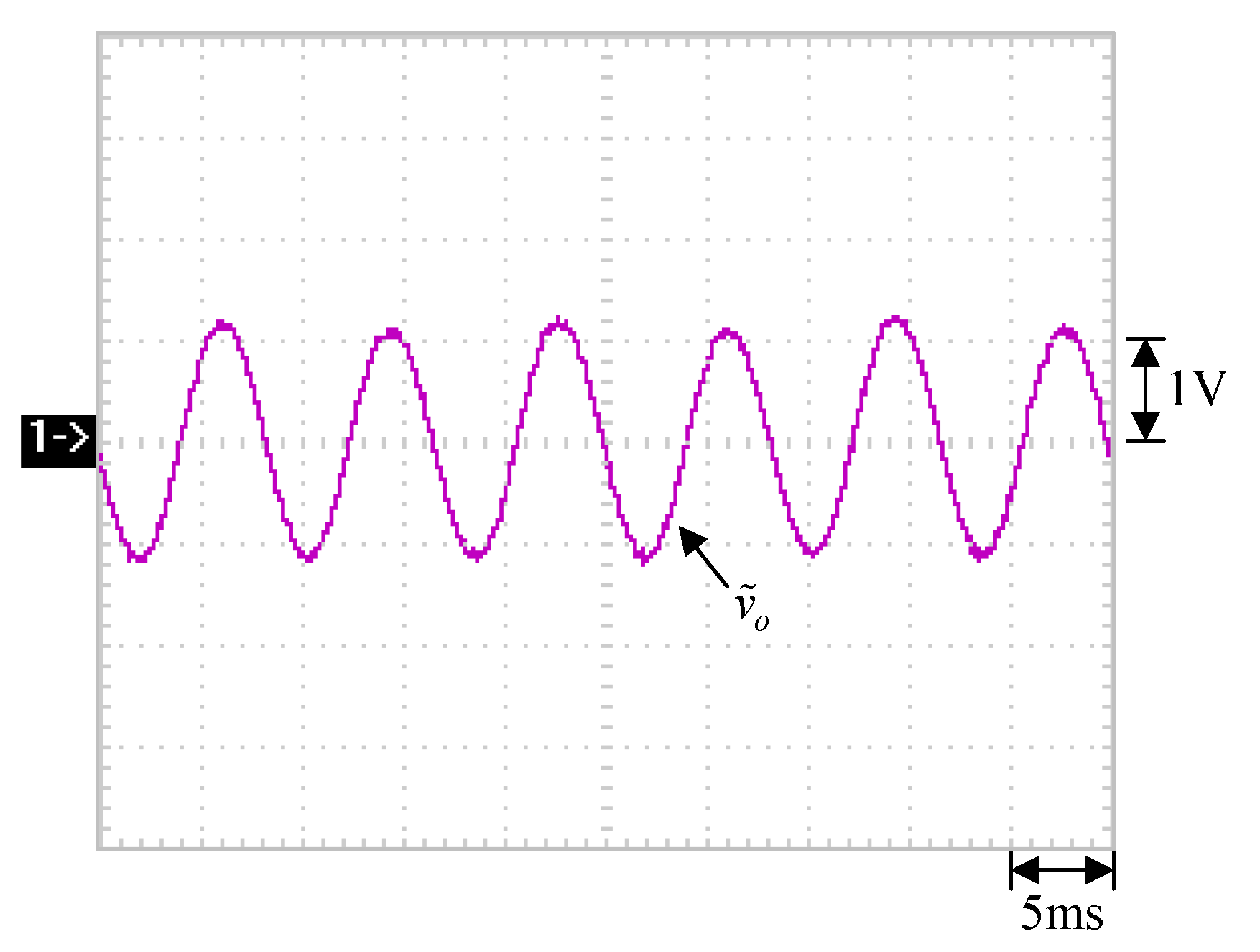

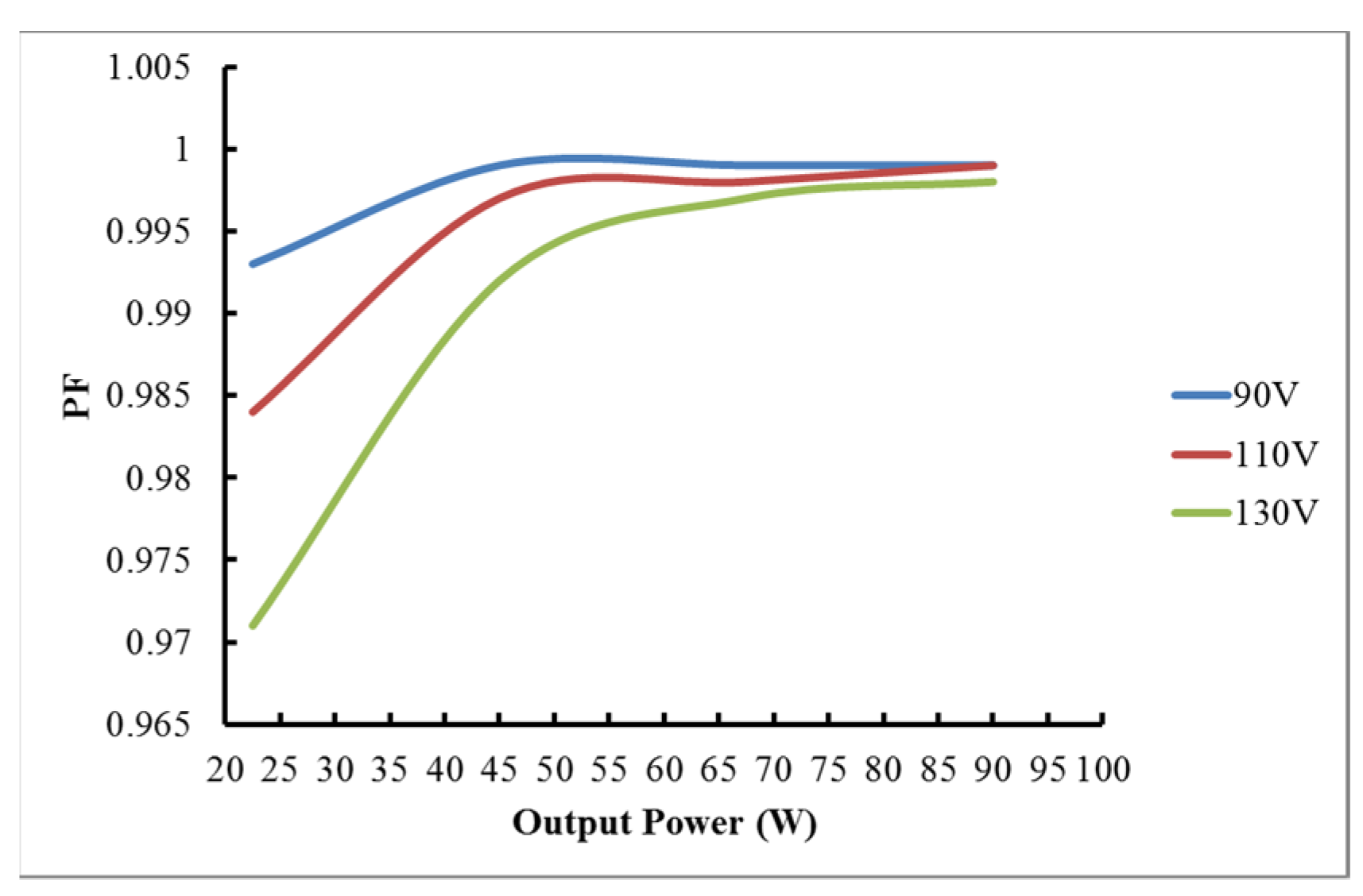

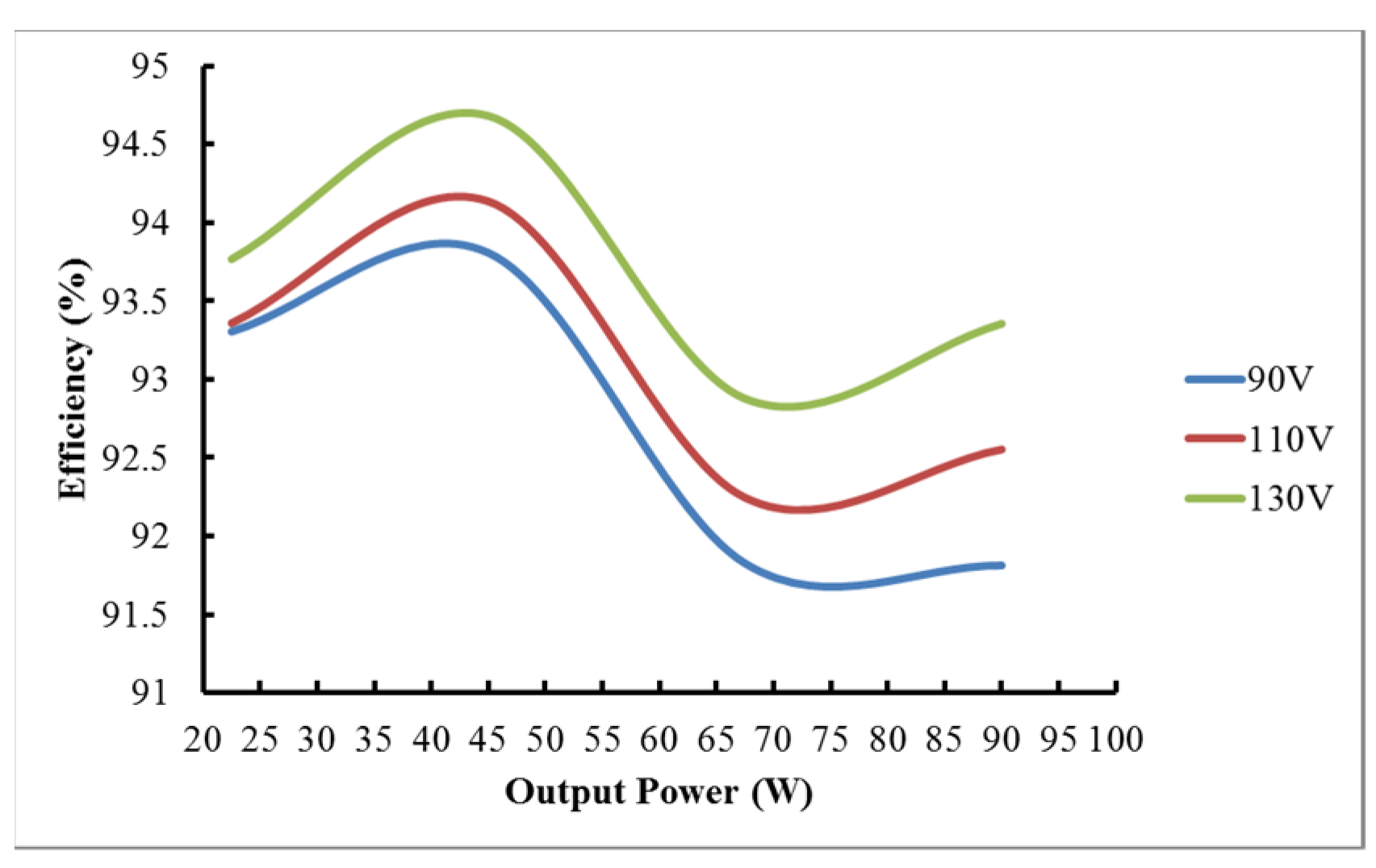

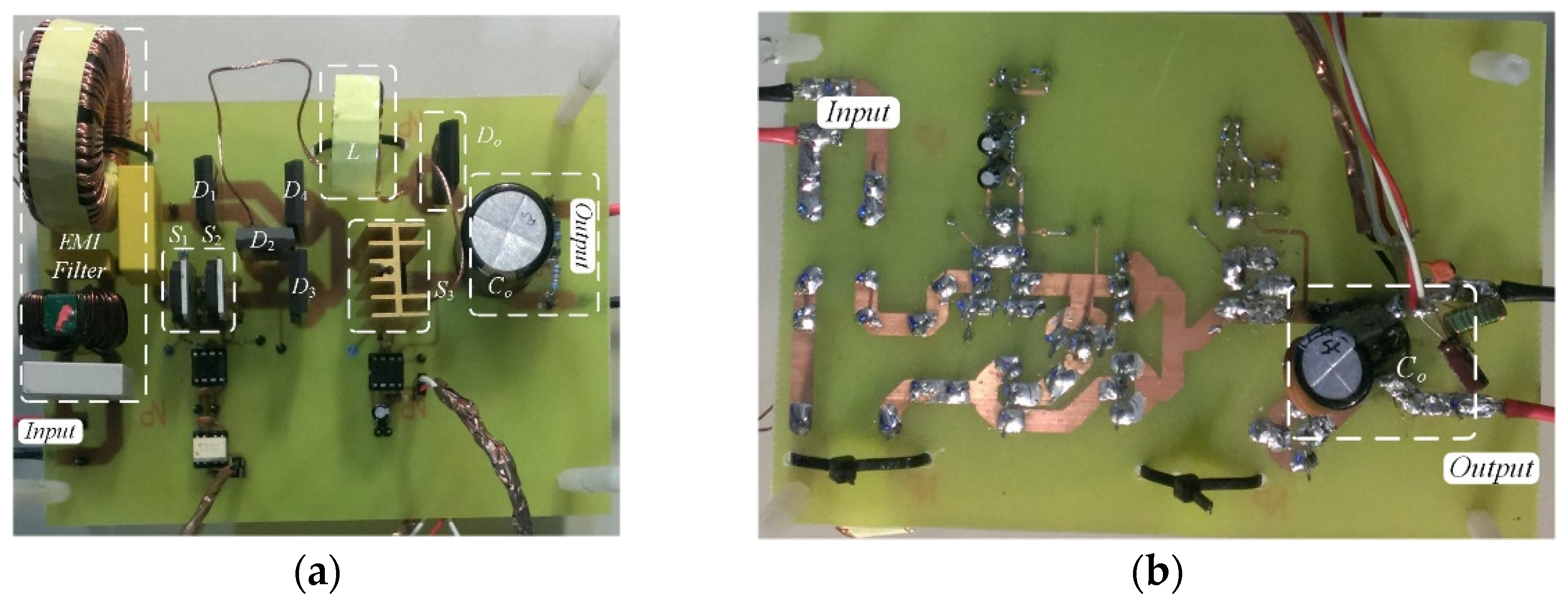

5. Experimental Results

6. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- IEC61000-3-2. Electromagnetic Compatibility (EMC)-Part3-2: Limits–Limits for Harmonic Current Emissions (Equipment Input Current ≤ 16 A Per Phase); International Electrotechnical Commission (IEC): Geneva, Switzerland, 2005. [Google Scholar]

- Prasad, A.R.; Ziogas, P.D.; Mania, S. A novel passive waveshaping method for single-phase diode rectifiers. IEEE Trans. Ind. Electron. 1990, 37, 521–530. [Google Scholar] [CrossRef]

- Seidel, A.R.; Bisogno, F.E.; Pappis, D.; Dalla Costa, M.A.; do Prado, R.N. Simple valley-fill self-oscillating electronic ballast with low crest factor using pulse-frequency modulation. In Proceedings of the 38th IAS Annual Meeting on Conference Record of the Industry Applications Conference, Salt Lake City, UT, USA, 12–16 October 2003; pp. 779–784. [Google Scholar]

- Umesh, S.; Venkatesha, L.; Usha, A. Active power factor correction technique for single phase full bridge rectifier. In Proceedings of the 2014 International Conference on Advances in Energy Conversion Technologies (ICAECT), Anipal, India, 23–25 January 2014; pp. 130–135. [Google Scholar]

- Wu, H.; Ge, H.; Xu, Y.; Zhang, W. The power factor correction of three-phase to single-phase matrix converter with an active power decoupling capacity. In Proceedings of the 2014 International Conference on Advances in Energy Conversion Technologies (ICAECT), Manipal, India, 23–25 January 2014; pp. 1–5. [Google Scholar]

- Zhang, J.; Shao, J.; Xu, P.; Lee, F.C.; Jovanovic, M.M. Evaluation of input current in the critical mode boost PFC converter for distributed power systems. In Proceedings of the APEC 2001 Sixteenth Annual IEEE Applied Power Electronics Conference and Exposition (Cat. No.01CH37181), Anaheim, CA, USA, 4–8 March 2001; Volume 1, pp. 130–136. [Google Scholar]

- Das, P.; Pahlevaninezhad, M.; Drobnik, J.; Moschopoulos, G.; Jain, P.K. A nonlinear controller based on a discrete energy function for an AC/DC boost PFC converter. IEEE Trans. Power Electron. 2013, 28, 5458–5476. [Google Scholar] [CrossRef]

- Pahlevani, M.; Pan, S.; Eren, S.; Bakhshai, A.; Jain, P. An adaptive nonlinear current observer for boost PFC AC/DC converters. IEEE Trans. Ind. Electron. 2014, 61, 6720–6729. [Google Scholar] [CrossRef]

- Vahedi, H.; Al-Haddad, K. A novel multilevel multioutput bidirectional active buck PFC rectifier. IEEE Trans. Ind. Electron. 2016, 63, 5442–5450. [Google Scholar] [CrossRef]

- Keogh, B.; Young, G.; Wegner, H.; Gillmor, C. Design considerations for high efficiency buck PFC with half-bridge regulation stage. In Proceedings of the 2010 Twenty-Fifth Annual IEEE Applied Power Electronics Conference and Exposition (APEC), Palm Springs, CA, USA, 21–25 February 2010; pp. 1384–1391. [Google Scholar]

- Wu, X.; Yang, J.; Zhang, J.; Xu, M. Design considerations of soft-switched buck PFC converter with constant on-time (COT) control. IEEE Trans. Power Electron. 2011, 26, 3144–3152. [Google Scholar] [CrossRef]

- Nishida, Y.; Motegi, S.; Maeda, A. A single-phase buck-boost AC-to-DC converter with high-quality input and output waveforms. In Proceedings of the 1995 IEEE International Symposium on Industrial Electronics, Dubrovnik, Croatia, 10–14 January 1995; Volume 1, pp. 433–438. [Google Scholar]

- Morizane, T.; Shimomori, W.; Taniguchi, K.; Kimura, N.; Ogawa, M. PWM technique for non-isolated three-phase soft-switching buck-boost PFC converter. In Proceedings of the 2007 Power Conversion Conference, Nagoya, Japan, 2–5 April 2007; pp. 1280–1285. [Google Scholar]

- He, M.; Zhang, F.; Xu, J.; Yang, P.; Yan, T. High-efficiency two-switch tri-state buck-boost power factor correction converter with fast dynamic response and low-inductor current ripple. IET Power Electron. 2013, 6, 1544–1554. [Google Scholar] [CrossRef]

- Tsai, H.-Y.; Hsia, T.-H.; Chen, D. A family of zero-voltage-transition bridgeless power-factor-correction circuits with a zero-current-switching auxiliary switch. IEEE Trans. Ind. Electron. 2011, 58, 1848–1855. [Google Scholar] [CrossRef]

- Mahdavi, M.; Farzanehfard, H. Bridgeless SEPIC PFC rectifier with reduced components and conduction losses. IEEE Trans. Ind. Electron. 2011, 58, 4153–4160. [Google Scholar] [CrossRef]

- Jovanovic, M.M.; Jang, Y. Bridgeless high-power-factor buck converter. IEEE Trans. Power Electron. 2011, 26, 602–611. [Google Scholar]

- Sebastian, J.; Cobos, J.A.; Lopera, J.M.; Uceda, J. The determination of the boundaries between continuous and discontinuous conduction modes in PWM DC-to-DC converters used as power factor preregulators. IEEE Trans. Power Electron. 1995, 10, 574–582. [Google Scholar] [CrossRef]

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Hwu, K.-I.; Tai, Y.-K.; He, Y.-P. Bridgeless Buck-Boost PFC Rectifier with Positive Output Voltage. Appl. Sci. 2019, 9, 3483. https://doi.org/10.3390/app9173483

Hwu K-I, Tai Y-K, He Y-P. Bridgeless Buck-Boost PFC Rectifier with Positive Output Voltage. Applied Sciences. 2019; 9(17):3483. https://doi.org/10.3390/app9173483

Chicago/Turabian StyleHwu, Kuo-Ing, Yu-Kun Tai, and Yu-Ping He. 2019. "Bridgeless Buck-Boost PFC Rectifier with Positive Output Voltage" Applied Sciences 9, no. 17: 3483. https://doi.org/10.3390/app9173483

APA StyleHwu, K.-I., Tai, Y.-K., & He, Y.-P. (2019). Bridgeless Buck-Boost PFC Rectifier with Positive Output Voltage. Applied Sciences, 9(17), 3483. https://doi.org/10.3390/app9173483