Quantitative Analysis of Positive-Bias-Stress-Induced Electron Trapping in the Gate Insulator in the Self-Aligned Top Gate Coplanar Indium–Gallium–Zinc Oxide Thin-Film Transistors

Abstract

:1. Introduction

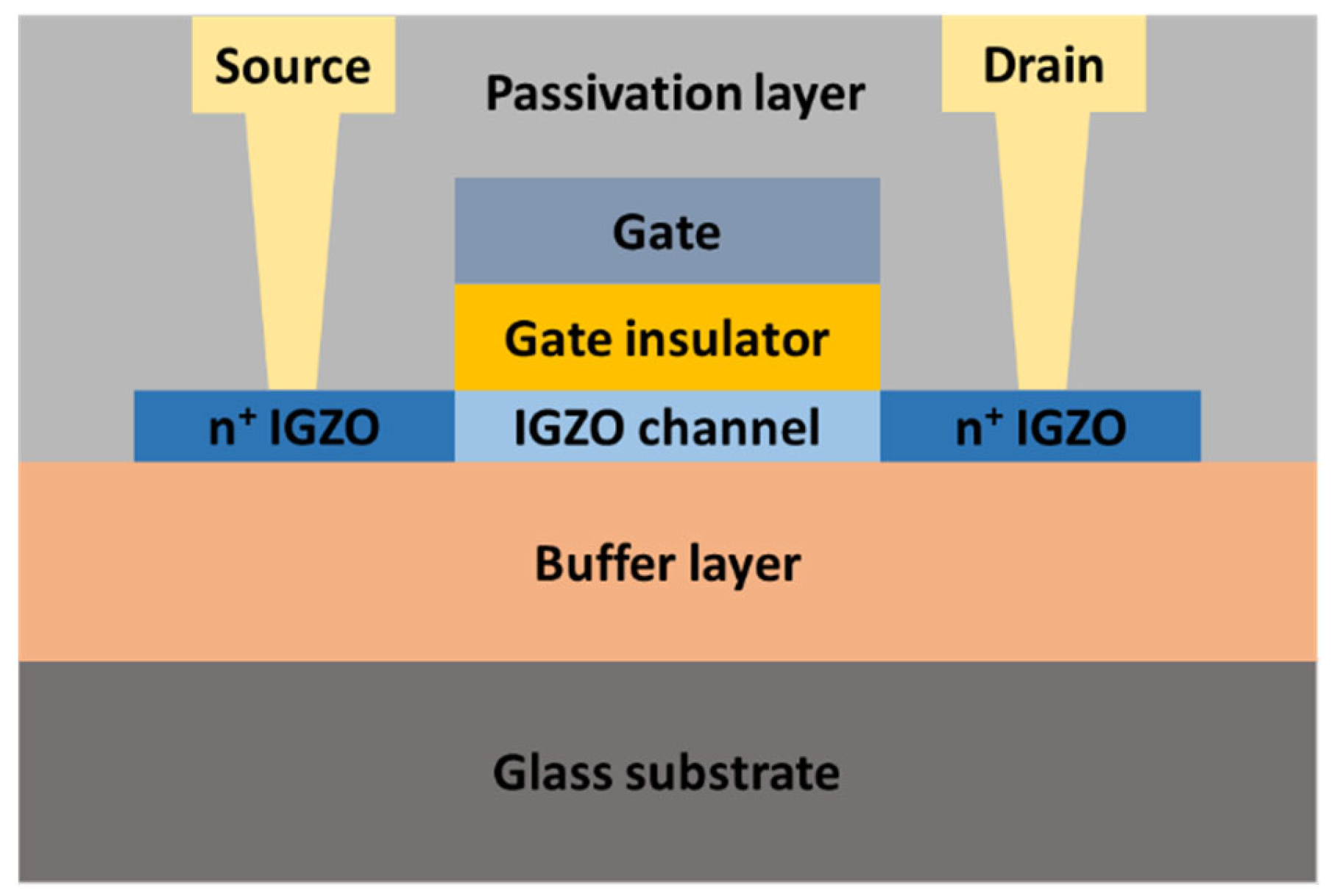

2. Experimental Section

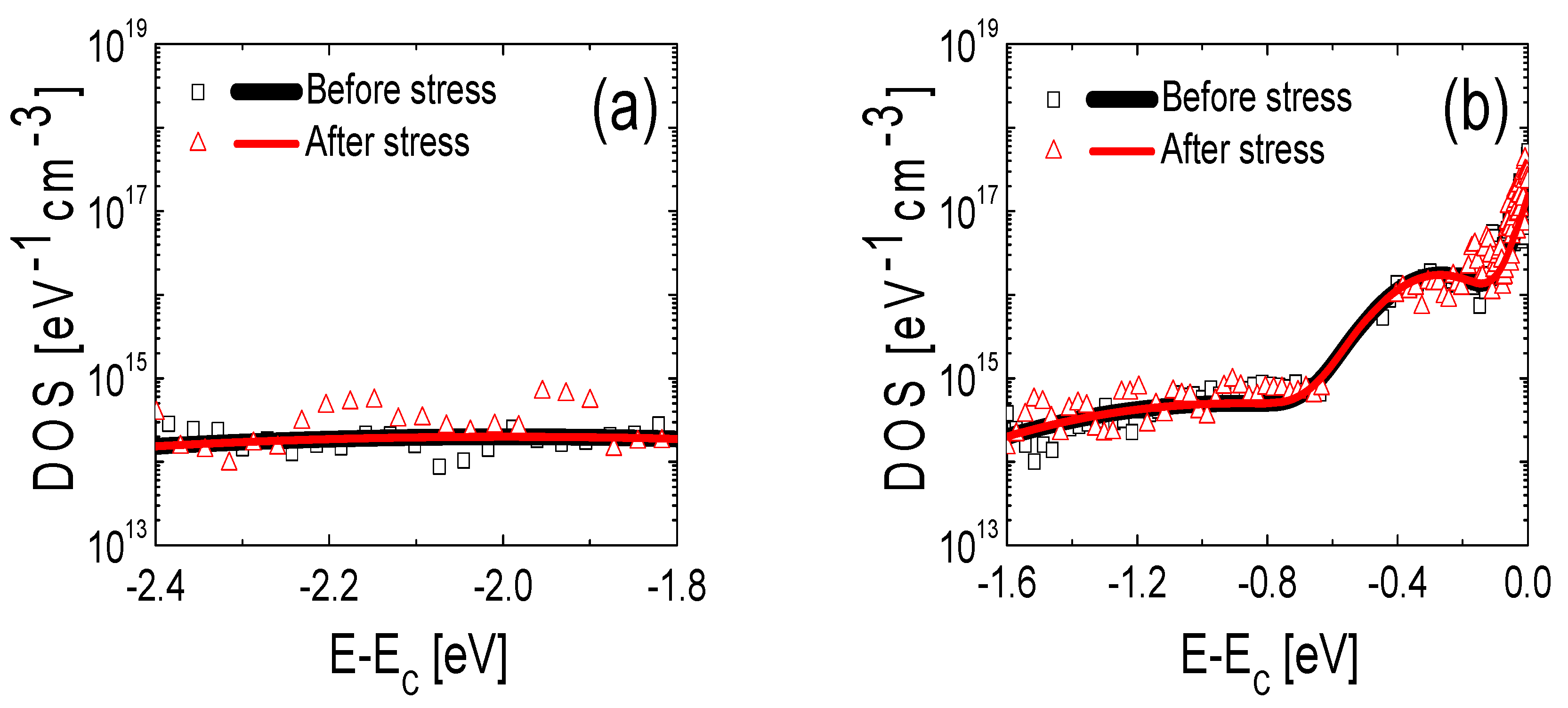

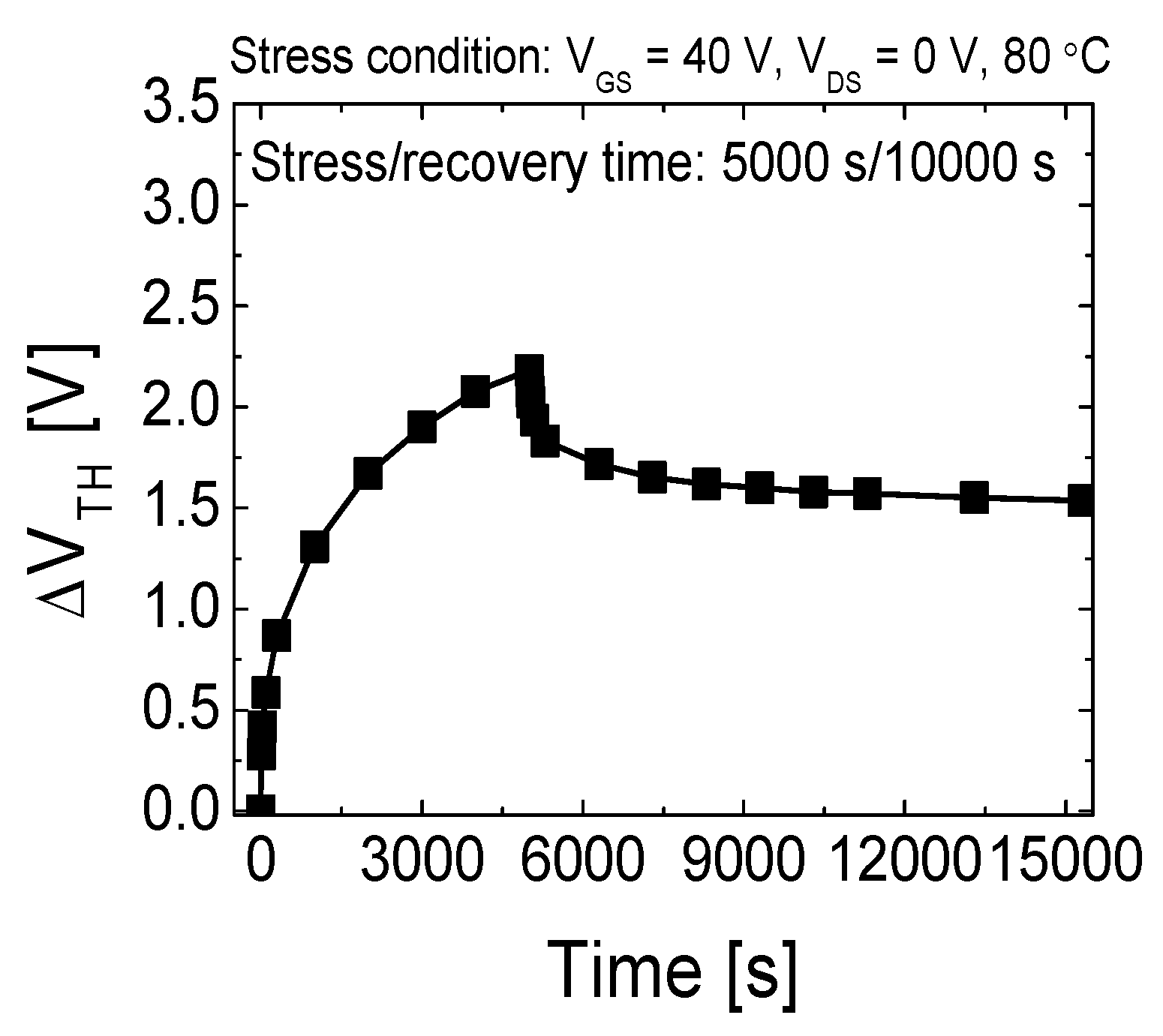

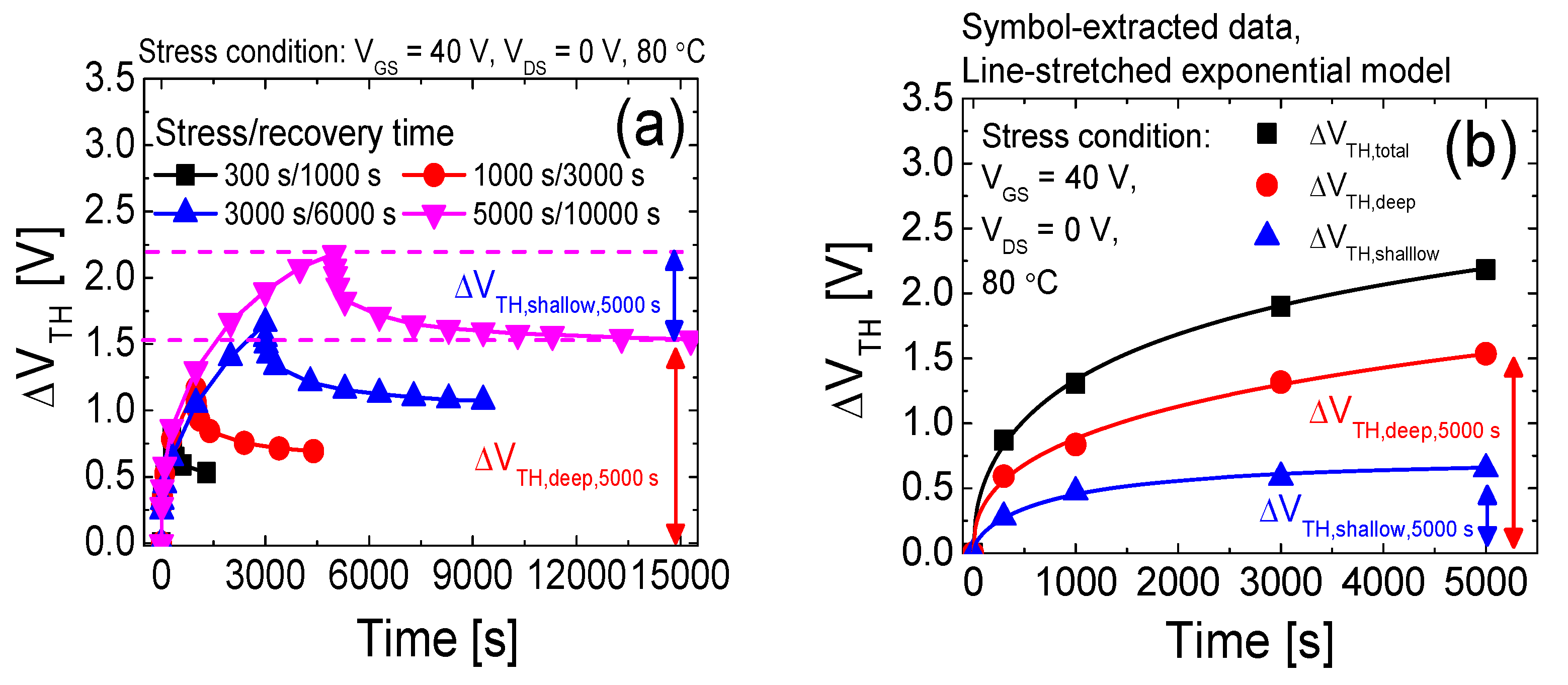

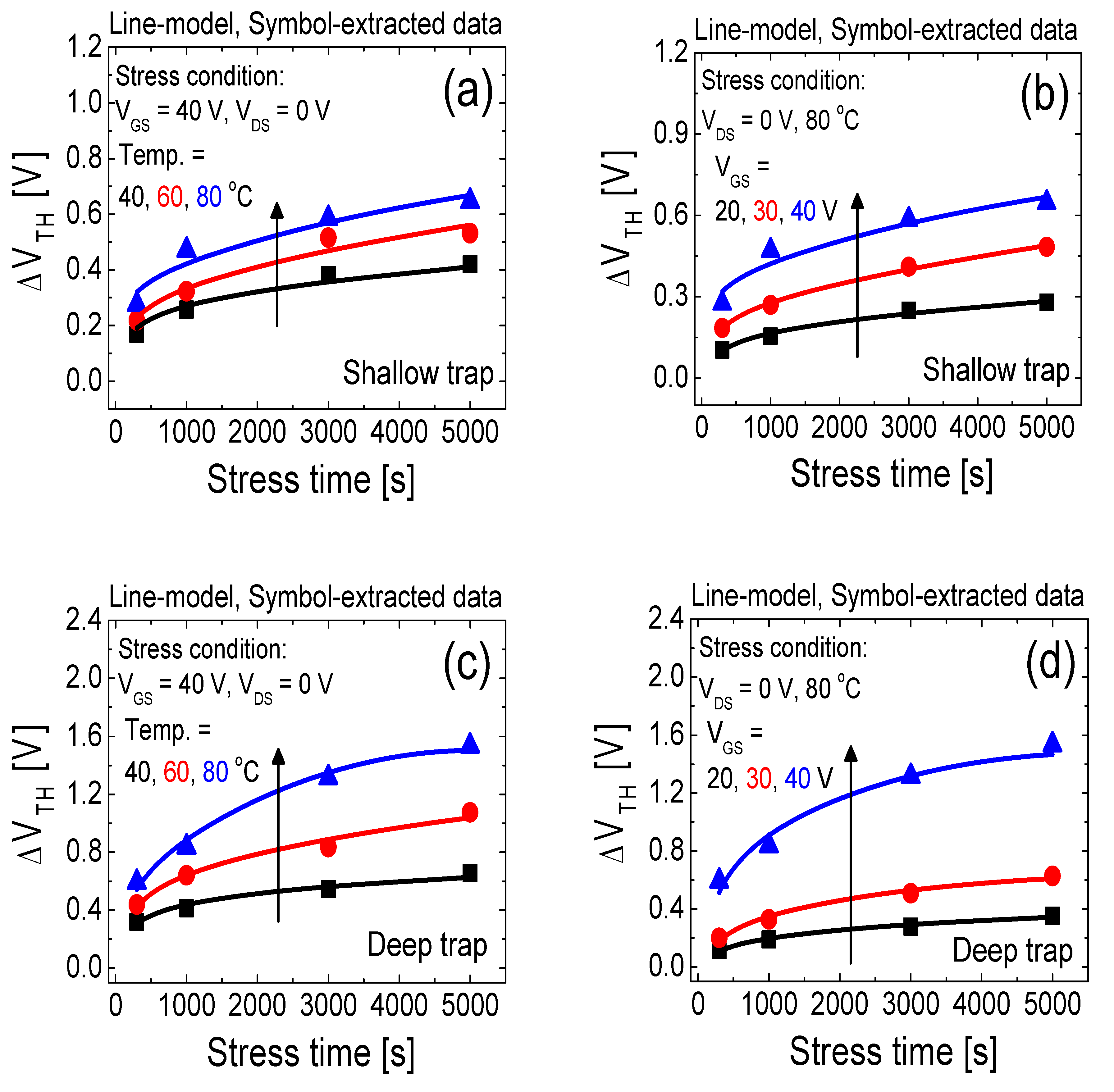

3. Results and Discussion

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Kamiya, T.; Nomura, K.; Hosono, H. Present status of amorphous In–Ga–Zn–O thin-film transistors. Sci. Technol. Adv. Mater. 2010, 11, 044305. [Google Scholar] [CrossRef]

- Tripathi, A.K.; Smits, E.C.P.; Van Der Putten, J.B.P.H.; Van Neer, M.; Myny, K.; Nag, M.; Steudel, S.; Vicca, P.; O’Neill, K.; Van Veenendaal, E.; et al. Low-voltage gallium-indium-zinc-oxide thin film transistors based logic circuits on thin plastic foil: Building blocks for radio frequency identification application. Appl. Phys. Lett. 2011, 98, 162102. [Google Scholar] [CrossRef]

- Park, J.S.; Maeng, W.; Kim, H.; Park, J. Review of recent developments in amorphous oxide semiconductor thin-film transistor devices. Thin Solid Film. 2012, 520, 1679–1693. [Google Scholar] [CrossRef]

- Lin, C.-L.; Chang, W.-Y.; Hung, C.-C. Compensating pixel circuit driving AMOLED display with a-IGZO TFTs. IEEE Electron Dev. Lett. 2013, 34, 1166–1168. [Google Scholar] [CrossRef]

- Mo, Y.G.; Kim, M.; Kang, C.K.; Jeong, J.H.; Park, Y.S.; Choi, C.G.; Kim, H.D.; Kim, S.S. Amorphous-oxide TFT backplane for large-sized AMOLED TVs. J. Soc. Inf. Disp. 2012, 19, 16–20. [Google Scholar] [CrossRef]

- Liu, H.; Hussain, S.; Kang, J. Improvement in sensitivity of an indirect-type organic X-ray detector using an amorphous IGZO interfacial layer. J. Instrum. 2020, 15, P02002. [Google Scholar] [CrossRef]

- Hoshino, K.; Hong, D.; Chiang, H.Q.; Wager, J.F. Constant-voltage-bias stress testing of a-IGZO thin-film transistors. IEEE Trans. Electron Devices 2009, 56, 1365–1370. [Google Scholar] [CrossRef]

- Ji, K.H.; Kim, J.I.; Mo, Y.G.; Jeong, J.H.; Yang, S.; Hwang, C.S.; Park, S.H.K.; Ryu, M.K.; Lee, S.Y.; Jeong, J.K. Comparative Study on Light-Induced Bias Stress Instability of IGZO Transistors with SiNx and SiO2 Gate Dielectrics. IEEE Electron Device Lett. 2010, 31, 1404–1406. [Google Scholar] [CrossRef]

- Fomani, A.A.; Nathan, A. Metastability Mechanisms in Thin Film Transistors Quantitatively Resolved Using Post-Stress Relaxation of Threshold Voltage. J. Appl. Phys. 2011, 109, 084521–084526. [Google Scholar] [CrossRef]

- Xu, P.R.; Yao, R.H. Threshold-voltage shift model based on electron tunneling under positive gate bias stress for amorphous InGaZnO thin-film transistors. Displays 2018, 53, 14–17. [Google Scholar] [CrossRef]

- Oh, S.; Baeck, J.H.; Bae, J.U.; Park, K.-S.; Kang, I.B. Effect of interfacial excess oxygen on positive-bias temperature stress instability of self-aligned coplanar In-Ga-Zn-O thin-film transistors. Appl. Phys. Lett. 2016, 108, 141604. [Google Scholar] [CrossRef]

- Kim, D.H.; Choi, S.; Jang, J.; Kang, H.; Kim, D.M.; Choi, S.-J.; Kim, Y.-S.; Oh, S.; Baeck, J.H.; Bae, J.U.; et al. Experimental decomposition of the positive bias temperature stress-induced instability in self-aligned coplanar InGaZnO thin-film transistors and its modeling based on the multiple stretched-exponential function. J. Soc. Inf. Disp. 2017, 25, 98–107. [Google Scholar] [CrossRef]

- Harrell, W.R.; Frey, J. Observation of Poole-Frenkel Effect Saturation in SiO2 and Other Insulating Films. Thin Solid Films 1999, 352, 195–204. [Google Scholar] [CrossRef]

- Palit, S.; Alam, M.A. Theory of charging and charge transport in “intermediate” thickness dielectrics and its implications for characterization and reliability. J. Appl. Phys. 2012, 111, 054112. [Google Scholar] [CrossRef] [Green Version]

- Ma, Q.; Zhou, X.-Y.; Hsu, Y.-J.; Wu, Y.-C.; Zhang, S.-D. Excellent uniformity and reliability top-gate self-aligned IGZO TFTs with Cu electrode. SID Symp. Dig. Tech. Pap. 2020, 51, 184–186. [Google Scholar] [CrossRef]

- Song, Z.; Wang, G.; Chen, J.; Gu, P.; Liu, F.; Xie, D.; Liu, W.; Sun, H.; Song, Y.S.; Yan, L.; et al. 24.4: High Performance Top-gate Self-aligned Coplanar a-IGZO TFTs with Light Shielding Metal Design. SID Symp. Dig. Tech. Pap. 2018, 49, 259–262. [Google Scholar] [CrossRef]

- Hong, S.Y.; Kim, H.J.; Kim, D.H.; Jeong, H.Y.; Song, S.H.; Cho, I.T.; Noh, J.Y.; Yun, P.S.; Lee, S.W.; Park, K.S.; et al. Study on the Lateral Carrier Diffusion and Source-Drain. Series Resistance in Self-Aligned Top.-Gate Coplanar InGaZnO Thin-Film Transistors. Sci. Rep. 2019, 9, 6588. [Google Scholar] [CrossRef]

- Bae, H.; Choi, H.; Jun, S.; Jo, C.; Kim, Y.H.; Hwang, J.S.; Ahn, J.; Oh, S.; Bae, J.-U.; Choi, S.-J.; et al. Single-Scan Monochromatic Photonic Capacitance-Voltage Technique for Extraction of Subgap DOS Over the Bandgap in Amorphous Semiconductor TFTs. IEEE Electron Dev. Lett. 2013, 34, 1524–1526. [Google Scholar] [CrossRef]

- Choi, S.; Jang, J.; Kang, H.; Baeck, J.H.; Bae, J.U.; Park, K.-S.; Yoon, S.Y.; Kang, I.B.; Kim, D.M.; Choi, S.-J.; et al. Systematic decomposition of the positive bias stress instability in self-aligned coplanar In-Ga-Zn-O thin-film transistors. IEEE Electron Dev. Lett. 2017, 38, 580–583. [Google Scholar] [CrossRef]

- Lee, H.-W.; Choi, H.-S.; Cho, W.-J. Improving Charge Trapping/Detrapping Characteristics of Amorphous In-Ga-ZnO Thin-Film-Transistors Using Microwave Irradiation. J. Nanosci. Nanotechnol. 2019, 19, 6164–6169. [Google Scholar] [CrossRef]

- Hsieh, H.H.; Kamiya, T.; Nomura, K.; Hosono, H.; Wu, C.C. Modeling of amorphous InGaZnO4 thin film transistors and their subgap density of states. Appl. Phys. Lett. 2008, 92, 10–13. [Google Scholar] [CrossRef]

- Yoon, S.J.; Seong, N.J.; Choi, K.J.; Shin, W.C.; Yoon, S.M. Investigations on the bias temperature stabilities of oxide thin film transistors using In–Ga–Zn–O channels prepared by atomic layer deposition. RSC Adv. 2018, 8, 25014–25020. [Google Scholar] [CrossRef] [Green Version]

- Chen, T.-C.; Chang, T.-C.; Tsai, C.-T.; Hsieh, T.-Y.; Chen, S.-C.; Lin, C.-S.; Hung, M.-C.; Tu, C.-H.; Chang, T.-C.; Chen, P.-L. Behaviors of InGaZnO thin film transistor under illuminated positive gate-bias stress. Appl. Phys. Lett. 2010, 97, 112104. [Google Scholar] [CrossRef]

- Koelmans, H.; De Graaff, H.C. Drift phenomena in CdSe thin film FET’s. Solid State Electron. 1967, 10, 997–1000. [Google Scholar] [CrossRef]

- Jonscher, A.K. Energy losses in hopping conduction at high electric fields. J. Phys. C 1971, 4, 1331–1340. [Google Scholar] [CrossRef]

- Wang, L.L.; Liu, T.C.; Cai, Y.; Zhang, S. Thin-film transistor Vth shift model based on kinetics of electron transfer in gate dielectric. IEEE Trans. Electron Devices 2014, 61, 1436–1443. [Google Scholar] [CrossRef]

- Wang, L.L.; He, H.; Liu, X.; Deng, W.; Zhang, S. Charge Trapping Model for Temporal Threshold Voltage Shift in a-IGZO TFTs Considering Variations of Carrier Density in Channel and Electric Field in Gate Insulator. IEEE Trans. Electron. Devices 2015, 62, 2219–2225. [Google Scholar] [CrossRef]

- Fomani, A.A. Threshold Voltage Instability and Relaxation in Hydrogenated Amorphous Silicon Thin Film Transistors. Master’s Thesis, Waterloo University, Waterloo, ON, Canada, 2005. [Google Scholar]

- Eoin, P.; Robertson, J. Theory of defects in vitreous silicon dioxide. Phys. Rev. B 1983, 27, 3780–3795. [Google Scholar]

- Warren, W.L.; Lenahan, P.M.; Robinson, B.; Stathis, J.H. Neutral E’ centers in microwave downstream plasma-enhanced chemical-vapor-deposited silicon dioxide. Appl. Phys. Lett. 1988, 53, 482. [Google Scholar] [CrossRef]

- Pantelides, S.T.; Lu, Z.-Y.; Nicklaw, C.; Bakos, T.; Rashkeev, S.N.; Fleetwood, D.M.; Schrimpfc, R.D. The E′ center and oxygen vacancies in SiO2. J. Non-Cryst. Solids 2008, 354, 217–223. [Google Scholar] [CrossRef]

- El-Sayed, A.-M.; Watkins, M.B.; Shluger, A.L.; Afanas’ev, V.V. Identification of intrinsic electron trapping sites in bulk amorphous silica from ab initio calculations. Microelectron. Eng. 2013, 109, 68–71. [Google Scholar] [CrossRef] [Green Version]

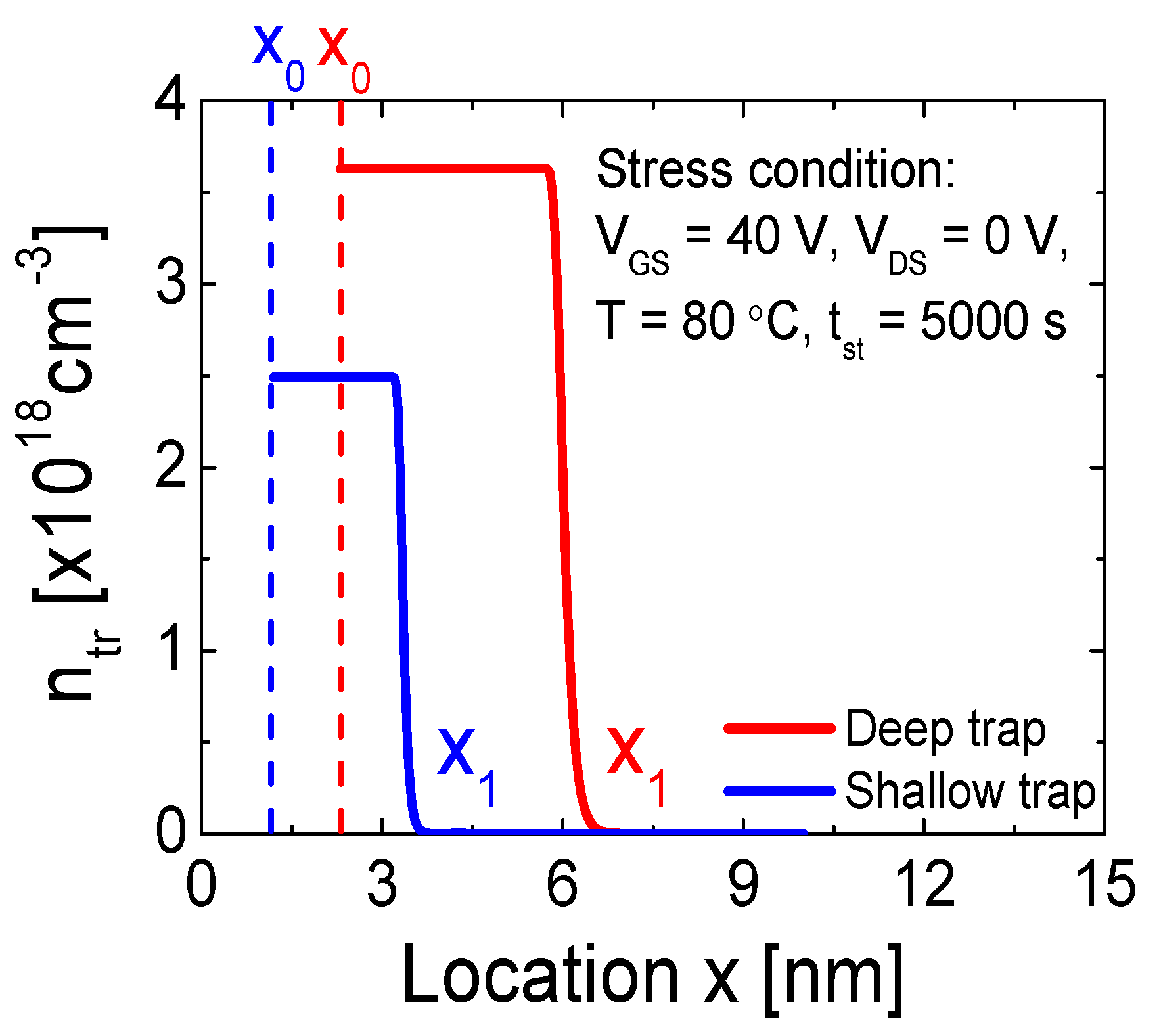

| Parameter | Shallow Trap | Deep Trap |

|---|---|---|

| ntr (cm−3) | 2.49 × 1018 | 3.63 × 1018 |

| EOT (eV) | 3.41 | 1.63 |

| x0 (nm) | 1.2 | 2.3 |

| x1 (nm) | 3.3 | 5.9 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Kim, D.-H.; Jeong, H.-S.; Lee, D.-H.; Bae, K.-H.; Lee, S.; Kim, M.-H.; Lim, J.-H.; Kwon, H.-I. Quantitative Analysis of Positive-Bias-Stress-Induced Electron Trapping in the Gate Insulator in the Self-Aligned Top Gate Coplanar Indium–Gallium–Zinc Oxide Thin-Film Transistors. Coatings 2021, 11, 1192. https://doi.org/10.3390/coatings11101192

Kim D-H, Jeong H-S, Lee D-H, Bae K-H, Lee S, Kim M-H, Lim J-H, Kwon H-I. Quantitative Analysis of Positive-Bias-Stress-Induced Electron Trapping in the Gate Insulator in the Self-Aligned Top Gate Coplanar Indium–Gallium–Zinc Oxide Thin-Film Transistors. Coatings. 2021; 11(10):1192. https://doi.org/10.3390/coatings11101192

Chicago/Turabian StyleKim, Dae-Hwan, Hwan-Seok Jeong, Dong-Ho Lee, Kang-Hwan Bae, Sunhee Lee, Myeong-Ho Kim, Jun-Hyung Lim, and Hyuck-In Kwon. 2021. "Quantitative Analysis of Positive-Bias-Stress-Induced Electron Trapping in the Gate Insulator in the Self-Aligned Top Gate Coplanar Indium–Gallium–Zinc Oxide Thin-Film Transistors" Coatings 11, no. 10: 1192. https://doi.org/10.3390/coatings11101192

APA StyleKim, D.-H., Jeong, H.-S., Lee, D.-H., Bae, K.-H., Lee, S., Kim, M.-H., Lim, J.-H., & Kwon, H.-I. (2021). Quantitative Analysis of Positive-Bias-Stress-Induced Electron Trapping in the Gate Insulator in the Self-Aligned Top Gate Coplanar Indium–Gallium–Zinc Oxide Thin-Film Transistors. Coatings, 11(10), 1192. https://doi.org/10.3390/coatings11101192