Simple Technique to Improve Essentially the Performance of One-Stage Op-Amps in Deep Submicrometer CMOS Technologies

Abstract

1. Introduction

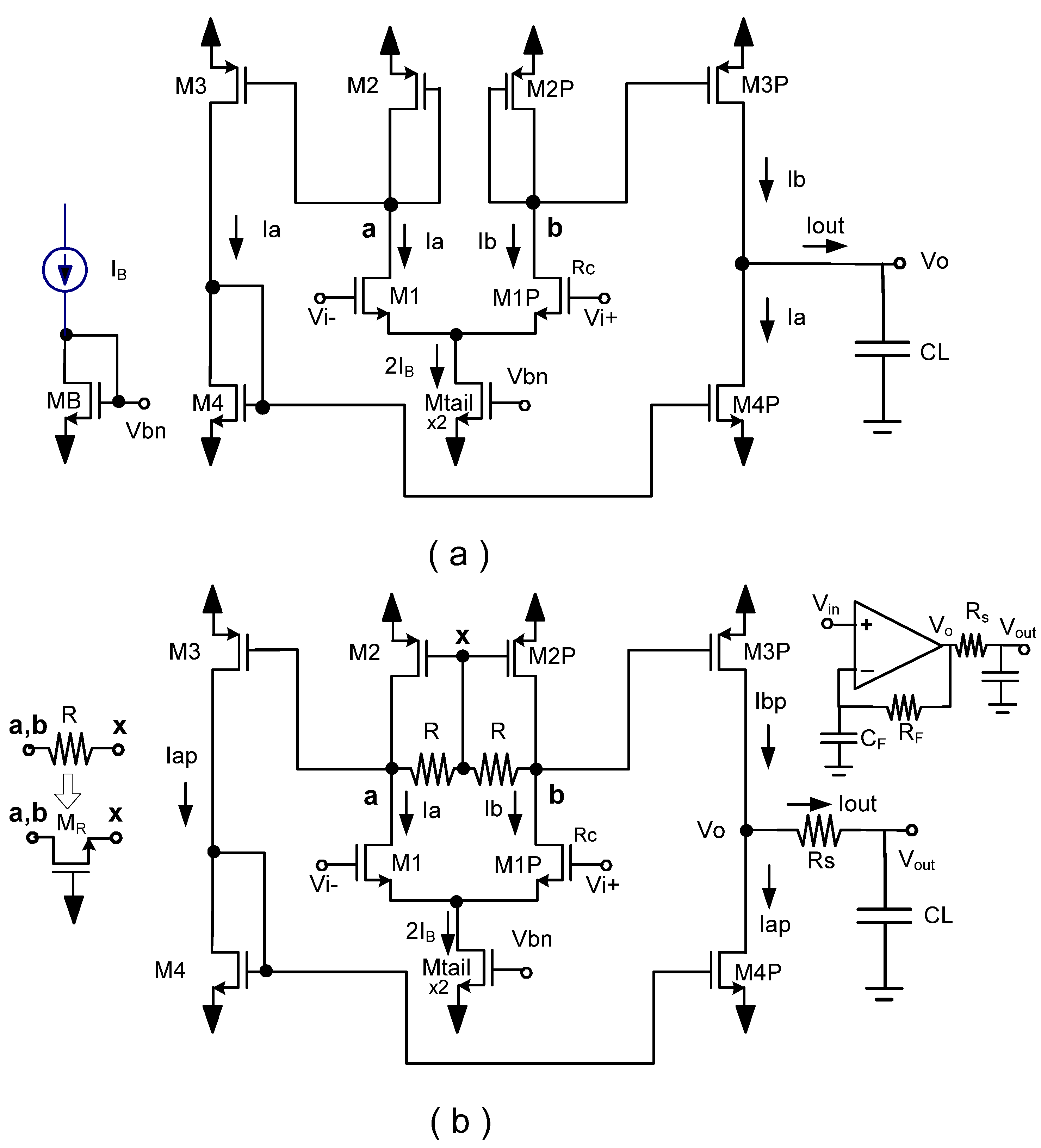

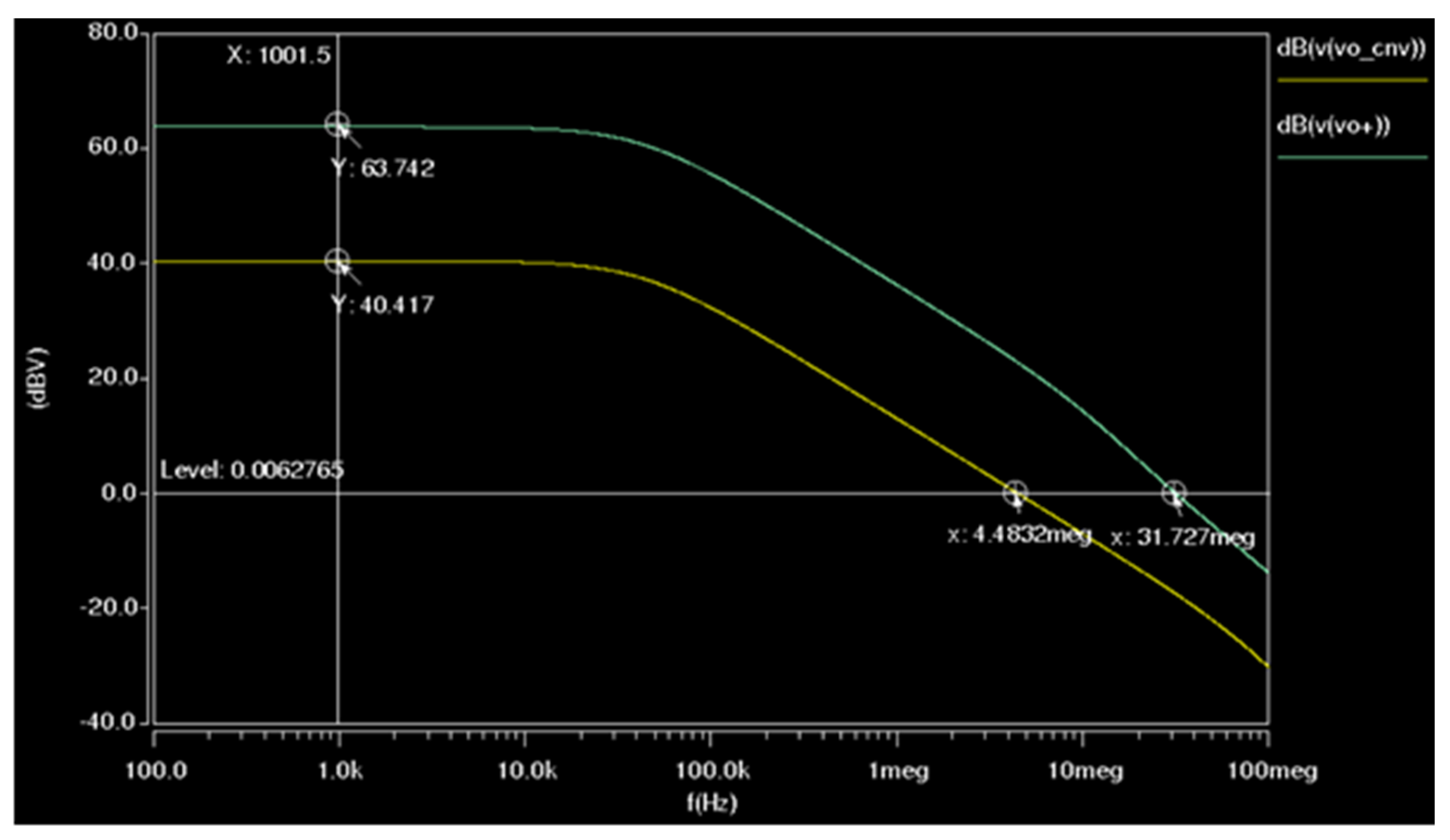

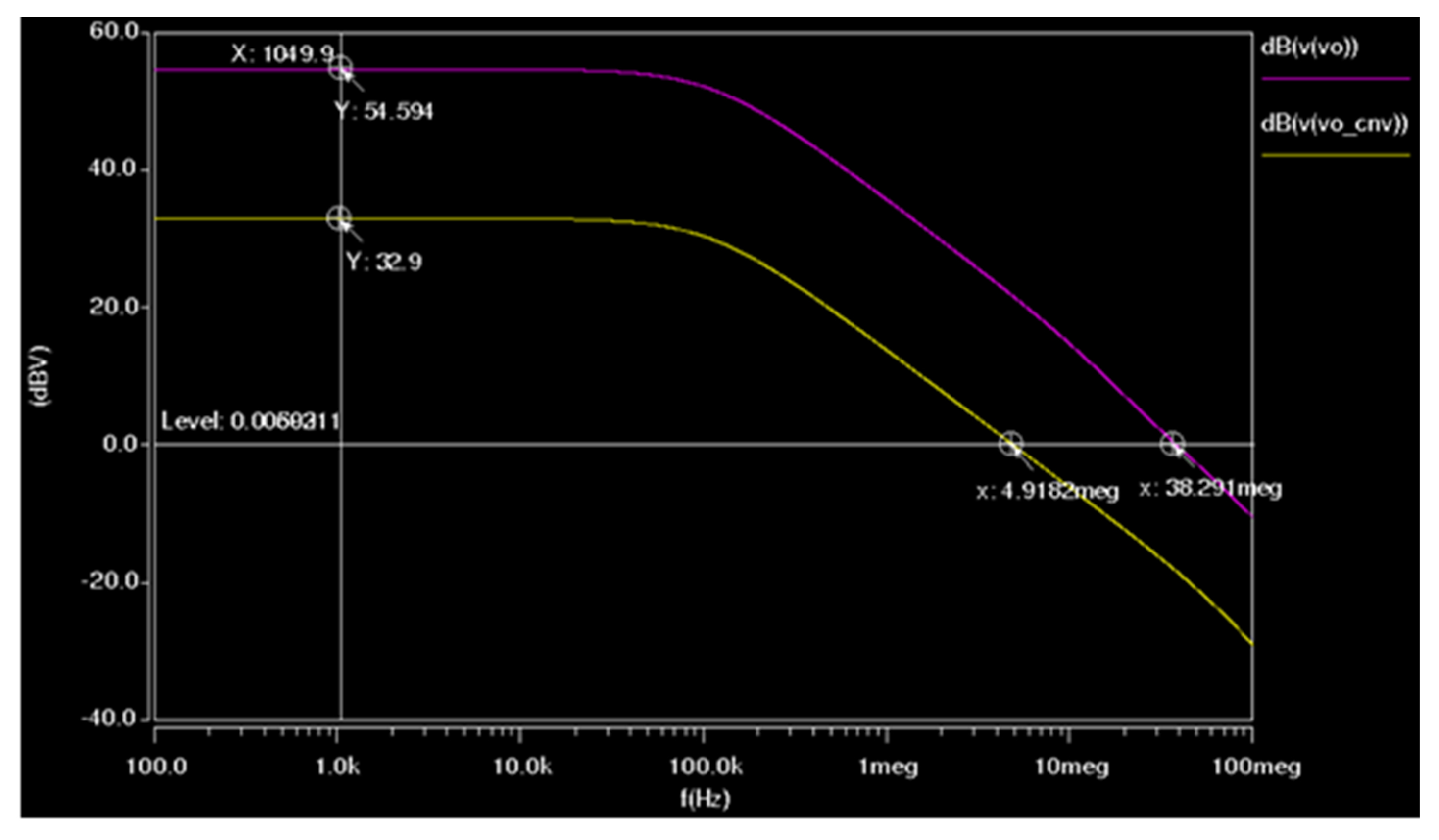

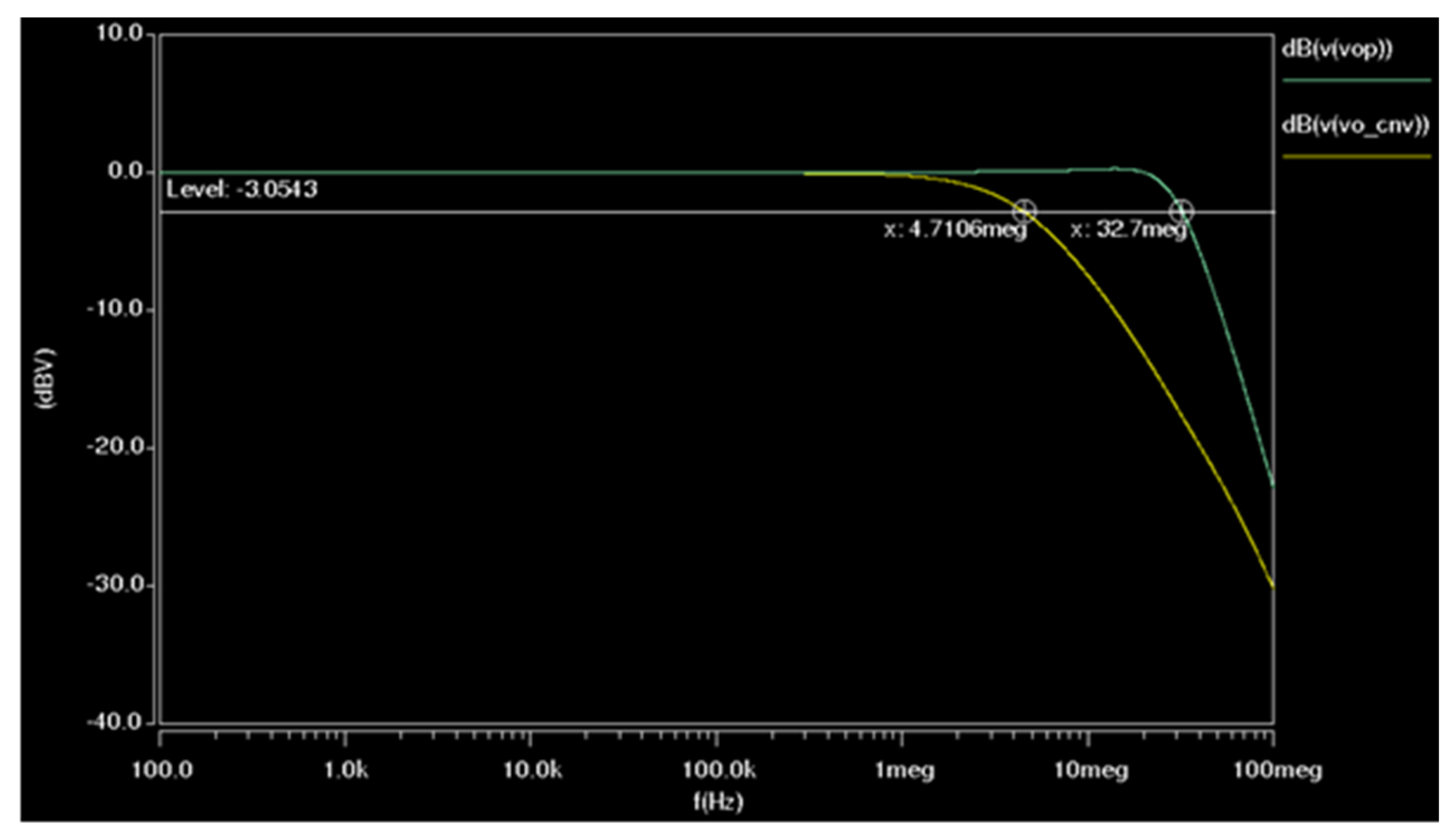

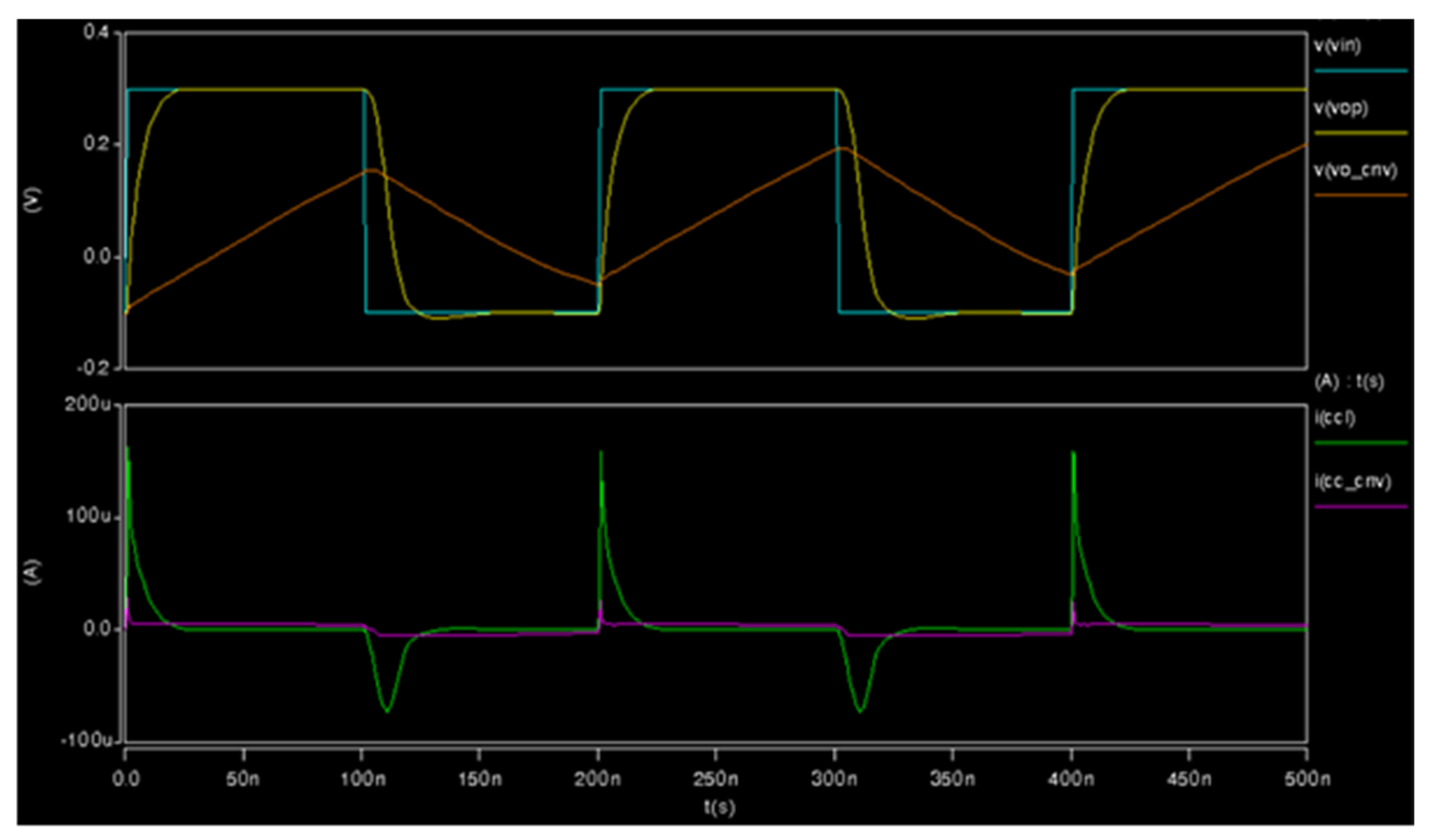

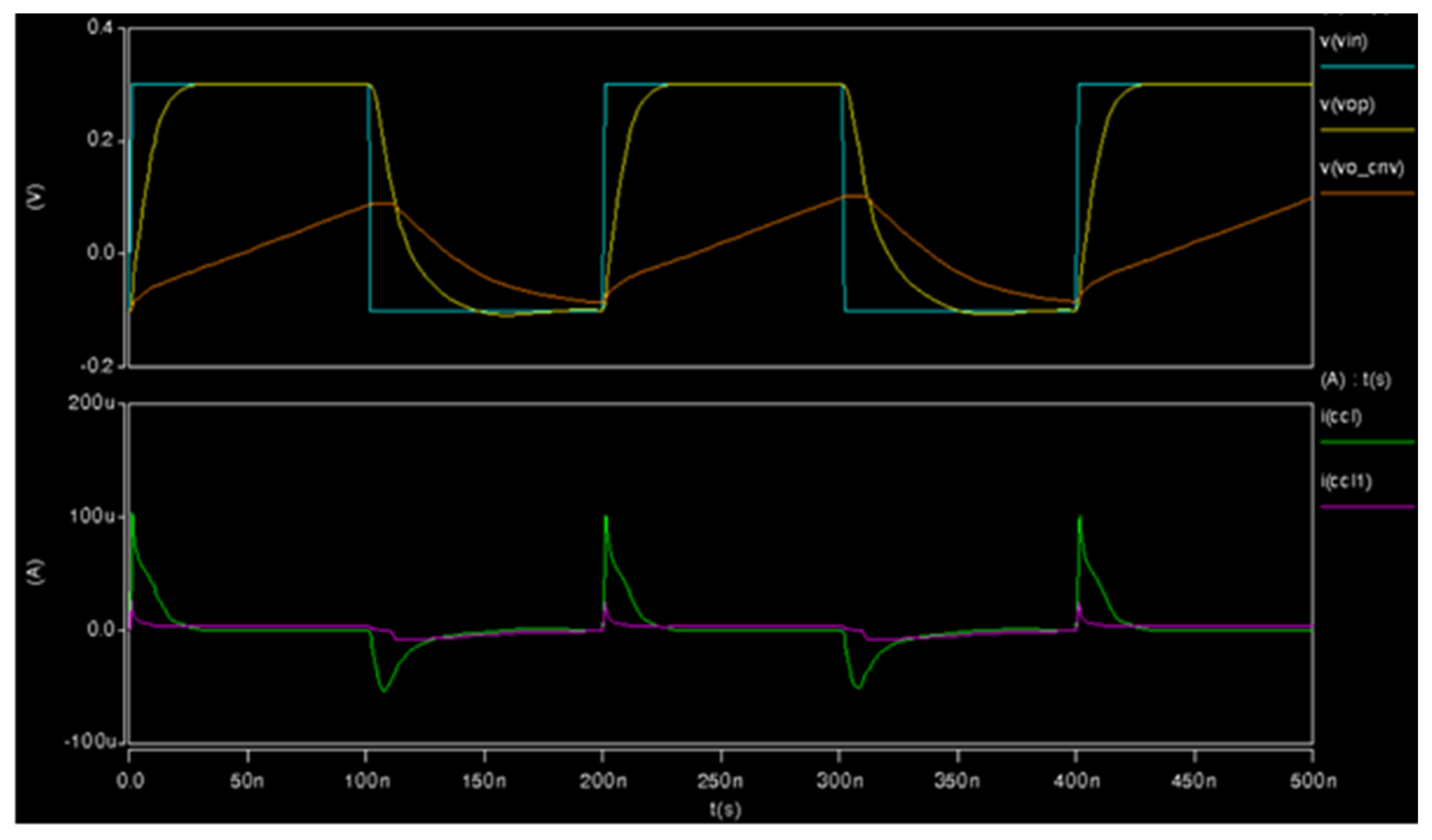

2. OTAs with Resistive Local Common Mode Feedback

3. Simulation Results

4. Discussion

- (A)

- The figures of merit in all technologies are a factor higher than 10 in OTAs with RLCMFB.

- (B)

- All figures of merit of OTAs with resistive local common mode feedback increase as the feature size of a CMOS technology decrease. One of the reasons is that supply voltages and static power dissipation also decrease with decreasing feature sizes and the standard figures of merit are inversely proportional to static power dissipation.

- (C)

- The main objective of this paper was to show that, even with relatively low CL values, it is possible to achieve significant performance enhancement factors (~1000%) using RLCMFB in current CMOS technologies. It might be possible to achieve even larger performance improvement factors by optimizing the OTA design (W/L values, R, Ibias, Rs) for each technology.

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Canizzaro, S.O.; Grasso, A.D.; Mita, R.; Palumbo, G. Design procedures for three-stage CMOS OTAs with nested-Miller compensation. IEEE Trans. Circuits Syst. I Regul. Pap. 2007, 54, 933–940. [Google Scholar] [CrossRef]

- Razavi, B. Operational Amplifiers. In Design of Analog CMOS Integrated Circuits, 1st ed.; McGraw-Hill: New York, NY, USA, 2001; pp. 291–324. [Google Scholar]

- Ramirez-Angulo, J.; Holmes, M. Simple technique using Local CMFB to enhance Slew Rate and bandwidth of one-Stage CMOS op-amps. Electron. Lett. 2002, 38, 1409–1411. [Google Scholar] [CrossRef]

- Harrison, J.; Weste, N. A 500 MHz CMOS anti-alias filter using feed-forward op-amps with local common-mode feedback. In Proceedings of the IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 13 February 2003. [Google Scholar]

- Baswa, S.; Ramirez-Angulo, J.; Lopez-Martin, A.J.; Carvajal, R.G.; Bikumandla, M. Rail-to-Rail super Class AB CMOS Operational Amplifiers. Electron. Lett. 2005, 41, 1–2. [Google Scholar] [CrossRef]

- Chawla, R.; Adil, F.; Serrano, G.; Hasler, P.E. Programmable Gm-C filters using floating-gate operational transconductance amplifiers. IEEE Trans. Circuits Syst. I Regul. Pap. 2007, 54, 481–491. [Google Scholar] [CrossRef]

- Harrison, J.; Weste, N. 350 MHz Opamp-RC filter in 0.18 µm CMOS. Electron. Lett. 2002, 38, 259–260. [Google Scholar] [CrossRef]

- Motlak, H.J.; Ahmad, S.N. A Novel Design Technique of One Stage CMOS OTA For High Frequency Applications. Frequenz 2007, 61, 182–188. [Google Scholar] [CrossRef]

- Rakshitdatta, K.S.; Krishnapura, N. On Slew Rate Enhancement in Class-A Opamps Using Local Common-Mode Feedback. In Proceedings of the 28th International Conference on VLSI Design, Bangelore, India, 3–7 January 2015. [Google Scholar]

- Schreier, R.E.; Caldwell, T. Amplifier Design. Available online: http://individual.utoronto.ca/schreier/lectures/9-6.pdf (accessed on 10 April 2022).

- Generic SPICE Simulation Parameters from North Carolina State University. Available online: https://eda.ncsu.edu/ncsu-cdk/ (accessed on 4 October 2022).

- The MOSIS Service. Available online: https://www.mosis.com/university-support (accessed on 5 October 2022).

- Ragheb, A.N.; Kim, H. Ultra-low power OTA based on bias recycling and subthreshold operation with phase margin enhancement. Microelectron. J. 2017, 60, 94–101. [Google Scholar] [CrossRef]

- Feizbakhsh, S.V.; Yosefi, G. An enhanced fast slew rate recycling folded cascode Op-Amp with general improvement in 180 nm CMOS process. AEU-Int. J. Electron. Commun. 2019, 101, 200–217. [Google Scholar] [CrossRef]

- Kuo, P.-Y.; Tsai, S.-D. An Enhanced Scheme of Multi-Stage Amplifier With High-Speed High-Gain Blocks and Recycling Frequency Cascode Circuitry to Improve Gain-Bandwidth and Slew Rate. IEEE Access 2019, 7, 130820–130829. [Google Scholar] [CrossRef]

- Kuo, P.-Y.; Liao, H.-W.; Peng, J.-S. An Improved Recycling Folded-Cascode Amplifier with High Unity-Gain Frequency. In Proceedings of the 2020 IEEE International Conference on Consumer Electronics-Taiwan (ICCE-Taiwan), Taoyuan, Taiwan, 28–30 September 2020; pp. 1–2. [Google Scholar]

- Kim, J.; Song, S.; Roh, J. A High Slew-Rate Enhancement Class-AB Operational Transconductance Amplifier (OTA) for Switched-Capacitor (SC) Applications. IEEE Access 2020, 8, 226167–226175. [Google Scholar] [CrossRef]

- Nandi, G.; Yadav, S.; Kondekar, P. A Fast Settling, High Slew Rate CMOS Recycling Folded Cascode Operational Transconductance Amplifier (OTA) for High Speed Applications. In Proceedings of the 2021 12th International Conference on Computing Communication and Networking Technologies (ICCCNT), Kharagpur, India, 6–8 July 2021; pp. 1–6. [Google Scholar]

| VDD/VSS (V) | Tech. Topology | Aol (dB) | PM (°) | GB/fz/fpab (MHz) | SR+ (V/μs) | SR− (V/μs) | IO+peak (µA) | IO−peak (µA) | Rs (kΩ) | FOMSS/LS/GLB | |

|---|---|---|---|---|---|---|---|---|---|---|---|

| ±0.4 | 22 | RLCMFB | 46.7 | 61 | 30.4/39.8/53 | 66 | −36.4 | 159.2 | −73 | 2 | 15.2/18/16.5 |

| CNV | 25.3 | 91 | 4.3 | 2 | −2.2 | 5 | −5.5 | 0 | 1/0.55/0.75 | ||

| ±0.45 | 45 | RLCMFB | 63.7 | 58 | 31.7/31.8/47 | 43.1 | −22 | 101.8 | −51 | 2.5 | 14.2/9.8/11.8 |

| CNV | 50.7 | 88 | 4.5 | 2.4 | −2.2 | 5 | −5 | 0 | 1/0.55/0.74 | ||

| ±0.45 | 90 | RLCMFB | 60.8 | 68 | 38.4/26.5/54.9 | 42.1 | −22.3 | 105.4 | −45.7 | 3 | 17/9.8/12.9 |

| CNV | 32.9 | 89 | 4.8 | 2.4 | −2 | 5 | −5 | 0 | 1/0.44/0.66 | ||

| ±0.9 | 180 | RLCMFB | 58.3 | 53 | 29/26.5/20.4 | 43.8 | −24.9 | 99.3 | −52.1 | 3 | 6.5/5.6/6 |

| CNV | 34.3 | 87 | 5 M | 2.2 | −2.1 | 5 | −5 | 0 | 0.55/0.24/0.36 | ||

| Parameters | [13] 2017 | [14] 2019 | [15] 2019 | [16] 2020 | [17] 2020 | [18] 2021 | This Work | This Work | This Work | This Work |

|---|---|---|---|---|---|---|---|---|---|---|

| CMOS process (nm) | 180 | 180 | 180 | 180 | 180 | 180 | 180 | 90 | 45 | 22 |

| Vsupply (V) | 0.5 | 1.2 | 1.8 | 1.8 | 1.8 | 1.8 | 1.8 | 0.9 | 0.9 | 0.8 |

| ItotQ (µA) | 7.9 | 700 | 530 | 260 | - | 400 | 10 | 10 | 10 | 10 |

| CL (pF) | 1 | 10 | 5 | 5.6 | 8 | 18 | 2 | 2 | 2 | 2 |

| Aol (dB) | 50 | 75 | 105.5 | 90.1 | 68 | 73.4 | 58.3 | 60.8 | 63.7 | 46.7 |

| GB (MHz) | 16.6 | 185 | 231.7 | 157 | 172.5 | 224 | 29 | 38.4 | 31.7 | 30.4 |

| PM (degree) | 72 | 71 | 53 | 62.1 | 48.7 | 69 | 61 | 56 | 68 | 53 |

| SR+/SR− (V/µs) | 4.25 | 99 | 13.2 | 64 | 212 | 110 | 44/25 | 42/22 | 43/22 | 66/36 |

| FOMSS (MHz pF/µW) | 4.2 | 2.2 | 1.21 | 1.87 | 1.21 | 5.6 | 6.5 | 17 | 14.2 | 15.2 |

| FOMLS ((V/µs)pF/µW) | 1.076 | 1.17 | 0.007 | 0.76 | 0.34 | 2.75 | 5.6 | 9.8 | 9.8 | 18 |

| FOMGLB = (FOMLSFOMSS)1/2 | 2.12 | 1.61 | 0.09 | 1.19 | 0.64 | 4 | 6 | 12.9 | 11.8 | 16.5 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Ramirez-Angulo, J.; Diaz-Armendariz, A.; Molinar-Solis, J.E.; Diaz-Sanchez, A.; Huerta-Chua, J. Simple Technique to Improve Essentially the Performance of One-Stage Op-Amps in Deep Submicrometer CMOS Technologies. J. Low Power Electron. Appl. 2023, 13, 4. https://doi.org/10.3390/jlpea13010004

Ramirez-Angulo J, Diaz-Armendariz A, Molinar-Solis JE, Diaz-Sanchez A, Huerta-Chua J. Simple Technique to Improve Essentially the Performance of One-Stage Op-Amps in Deep Submicrometer CMOS Technologies. Journal of Low Power Electronics and Applications. 2023; 13(1):4. https://doi.org/10.3390/jlpea13010004

Chicago/Turabian StyleRamirez-Angulo, Jaime, Alejandra Diaz-Armendariz, Jesus E. Molinar-Solis, Alejandro Diaz-Sanchez, and Jesus Huerta-Chua. 2023. "Simple Technique to Improve Essentially the Performance of One-Stage Op-Amps in Deep Submicrometer CMOS Technologies" Journal of Low Power Electronics and Applications 13, no. 1: 4. https://doi.org/10.3390/jlpea13010004

APA StyleRamirez-Angulo, J., Diaz-Armendariz, A., Molinar-Solis, J. E., Diaz-Sanchez, A., & Huerta-Chua, J. (2023). Simple Technique to Improve Essentially the Performance of One-Stage Op-Amps in Deep Submicrometer CMOS Technologies. Journal of Low Power Electronics and Applications, 13(1), 4. https://doi.org/10.3390/jlpea13010004