A Time-Mode PWM 1st Order Low-Pass Filter †

Abstract

1. Introduction

2. Implementation of the Time-Mode PWM Low-Pass Filter

2.1. Top-Level Architecture

2.2. Time-Mode PWM Building Blocks

2.2.1. Time Register Based on Gate-Controlled Current Source

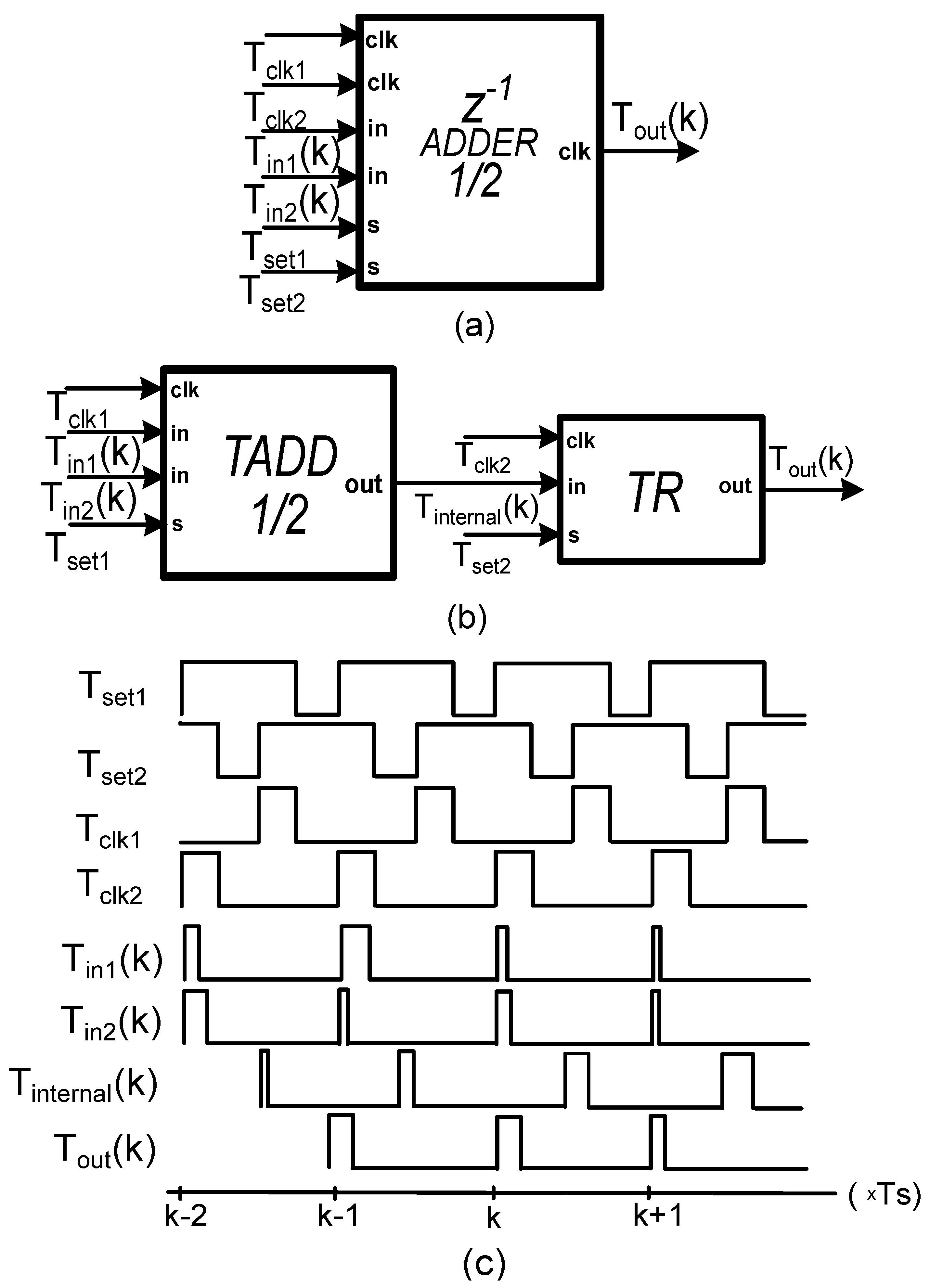

2.2.2. Time-Adder Core Implementation with Gain ½

2.2.3. Implementation of a z−1 Operator Using a Time Register

2.2.4. Implementation of the z−1 Time Adder with Gain ½

3. Discharging Slope Digital Calibration

4. Simulation Results

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Asada, K.; Nakura, T.; Iizuka, T.; Ikeda, M. Time-Domain Approach for Analog Circuits in Deep Sub-Micron LSI. IEICE Electron. Express 2018, 15, 20182001. [Google Scholar] [CrossRef]

- Roberts, G.W.; Ali-Bakhshian, M. A Brief Introduction to Time-to-Digital and Digital-to-Time Converters. IEEE Trans. Circuits Syst. II Express Briefs 2010, 57, 153–157. [Google Scholar] [CrossRef]

- Lee, D.; Lee, D.; Lee, T.; Kim, Y.H.; Kim, L.S. An Integrated Time Register and Arithmetic Circuit with Combined Operation for Time-Domain Signal Processing. In Proceedings of the 2015 IEEE International Symposium on Circuits and Systems, Lisbon, Portugal, 24–27 May 2015; pp. 1830–1833. [Google Scholar] [CrossRef]

- Elgreatly, A.; Dessouki, A.; Mostafa, H.; Abdalla, R.; El-Rabaie, E. A Novel Highly Linear Voltage-to-Time Converter (VTC) Circuit for Time-Based Analog-to-Digital Converters (ADC) Using Body Biasing. Electronics 2020, 9, 2033. [Google Scholar] [CrossRef]

- Pekau, H.; Yousif, A.; Haslett, J.W. A CMOS Integrated Linear Voltage-to-Pulse-Delay-Time Converter for Time Based Analog-to-Digital Converters. In Proceedings of the IEEE International Symposium on Circuits and Systems, Kos, Greece, 21–24 May 2006; pp. 2373–2376. [Google Scholar] [CrossRef]

- Kwon, H.J.; Lee, J.S.; Kim, B.; Sim, J.Y.; Park, H.J. Analysis of an Open-Loop Time Amplifier with a Time Gain Determined by the Ratio of Bias Current. IEEE Trans. Circuits Syst. II Express Briefs 2014, 61, 481–485. [Google Scholar] [CrossRef]

- Yuan, F. Design Techniques of All-Digital Arithmetic Units for Time-Mode Signal Processing. IET Circuits Devices Syst. 2018, 12, 753–763. [Google Scholar] [CrossRef]

- Ali-Bakhshian, M.; Roberts, G.W. Digital Storage, Addition and Subtraction of Time-Mode Variables. Electron. Lett. 2011, 47, 910–911. [Google Scholar] [CrossRef]

- Panetas-Felouris, O.; Vlassis, S. A 3rd-Order FIR Filter Implementation Based on Time-Mode Signal Processing. Electronics 2022, 11, 902. [Google Scholar] [CrossRef]

- Abdelfattah, M.; Roberts, G.W.; Chodavarapu, V.P. All-Digital Time-Mode Elliptic Filters Based on the Operational Simulation of LC Ladders. In Proceedings of the IEEE International Symposium on Circuits and Systems, Melbourne, VIC, Australia, 1–5 June 2014; pp. 2125–2128. [Google Scholar] [CrossRef]

- Abdelfattah, M.; Roberts, G.W. All-Digital Time-Mode Direct-Form All-Pole Biquadratic Filter Realization. IEEE Trans. Circuits Syst. II Express Briefs 2017, 64, 1262–1266. [Google Scholar] [CrossRef]

- Ali-Bakhshian, M.; Roberts, G.W. A Digital Implementation of a Dual-Path Time-to-Time Integrator. IEEE Trans. Circuits Syst. I Regul. Pap. 2012, 59, 2578–2591. [Google Scholar] [CrossRef]

- Karmakar, A.; De Smedt, V.; Leroux, P. Pseudo-Differential Time-Domain Integrator Using Charge-Based Time-Domain Circuits. In Proceedings of the 2021 IEEE 12th Latin America Symposium on Circuits and System (LASCAS), Arequipa, Peru, 21–24 February 2021; IEEE: Piscataway, NJ, USA; pp. 1–4. [Google Scholar]

- Park, Y.J.; Jarrett-Amor, D.; Yuan, F. Time Integrator for Mixed-Mode Signal Processing. In Proceedings of the IEEE International Symposium on Circuits and Systems, Montreal, QC, Canada, 22–25 May 2016; pp. 826–829. [Google Scholar] [CrossRef]

- Kim, D.; Kim, K.; Yu, W.; Cho, S. A Second-Order ΔΣ Time-to-Digital Converter Using Highly Digital Time-Domain Arithmetic Circuits. IEEE Trans. Circuits Syst. II Express Briefs 2019, 66, 1643–1647. [Google Scholar] [CrossRef]

- Yuan, F. CMOS Time-to-Digital Converters for Mixed-Mode Signal Processing. J. Eng. 2014, 2014, 140–154. [Google Scholar] [CrossRef]

- Ziabakhsh, S.; Gagnon, G.; Roberts, G.W. A Second-Order Bandpass ΔΣ Time-to-Digital Converter with Negative Time-Mode Feedback. IEEE Trans. Circuits Syst. I Regul. Pap. 2019, 66, 1355–1368. [Google Scholar] [CrossRef]

- Razavi, B. The Z-Transform for Analog Designers [The Analog Mind]. IEEE Solid-State Circuits Mag. 2020, 12, 8–14. [Google Scholar] [CrossRef]

- Pagkalos, K.P.; Panetas-Felouris, O.; Vlassis, S. Charge-Based Time Registers for z−1 Implementation. In Proceedings of the Panhellenic Conference on Electronics & Telecommunications, Tripolis, Greece, 2–3 December 2022; pp. 1–6. [Google Scholar] [CrossRef]

- Panetas-Felouris, O.; Vlassis, S. A Time-Domain Z−1 Circuit with Digital Calibration. J. Low Power Electron. Appl. 2022, 12, 3. [Google Scholar] [CrossRef]

- Ravinuthula, V.; Garg, V.; Harris, J.G.; Fortes, J.A.B. Time-Mode Circuits for Analog Computation. Int. J. Circuit Theory Appl. 2009, 37, 631–659. [Google Scholar] [CrossRef]

| Units | Min. | Typ. | Max. | |

|---|---|---|---|---|

| Fsampling | MHz | 5 | ||

| Gain @ 58.59 kHz | dB | −0.045 | −0.031 | 0.106 |

| fcut.off | MHz | 1.2273 | 1.2323 | 1.2352 |

| Power Consumption | μW | 59.04 | ||

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Pagkalos, K.P.; Panetas-Felouris, O.; Vlassis, S. A Time-Mode PWM 1st Order Low-Pass Filter. J. Low Power Electron. Appl. 2023, 13, 32. https://doi.org/10.3390/jlpea13020032

Pagkalos KP, Panetas-Felouris O, Vlassis S. A Time-Mode PWM 1st Order Low-Pass Filter. Journal of Low Power Electronics and Applications. 2023; 13(2):32. https://doi.org/10.3390/jlpea13020032

Chicago/Turabian StylePagkalos, Konstantinos P., Orfeas Panetas-Felouris, and Spyridon Vlassis. 2023. "A Time-Mode PWM 1st Order Low-Pass Filter" Journal of Low Power Electronics and Applications 13, no. 2: 32. https://doi.org/10.3390/jlpea13020032

APA StylePagkalos, K. P., Panetas-Felouris, O., & Vlassis, S. (2023). A Time-Mode PWM 1st Order Low-Pass Filter. Journal of Low Power Electronics and Applications, 13(2), 32. https://doi.org/10.3390/jlpea13020032