An Extended Range Divider Technique for Multi-Band PLL

Abstract

:1. Introduction

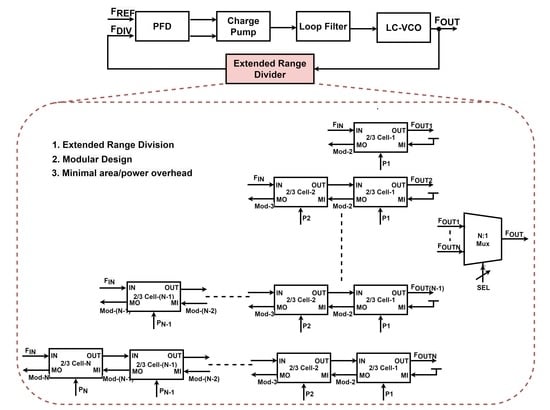

- An extended range division is achieved using conventional blocks;

- The modular nature of the proposed approach makes the layout compact, thereby minimizing the area overhead;

- The digital divider design of the MMD up to sub-10 GHz reduces the power overhead.

2. Feedback Divider in PLL: An Overview

2.1. Programmable Counter Based Divider

- The value of PC (P) is always greater than SC (S);

- Initially, is high and both and start counting in mode;

- As P > S, first reaches end-of-count (EOC) and changes from high to low;

- The remaining cycles are counted in N mode.

2.2. Multi Modulus Divider Topologies

3. Extended Range Divider Topologies

4. Proposed Extended Range MMD Structure

4.1. D-flip–flop Structures for Divider

4.2. Circuit Implementation

5. Design of L5/S Band Dual VCO PLL

5.1. VCO, CML Divider, and MUX

5.2. PFD, CP, and Loop Filter

6. Measurement Results

7. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Datta, A.K.; Patel, R. CPU Scheduling for Power/Energy Management on Multicore Processors Using Cache Miss and Context Switch Data. IEEE Trans. Parallel Distrib. Syst. 2013, 25, 1190–1199. [Google Scholar] [CrossRef]

- Xing, Y.; Liu, F.; Xiao, N.; Chen, Z.; Lu, Y. Capability for Multi-Core and Many-Core Memory Systems: A Case-Study with Xeon Processors. IEEE Access 2019, 7, 47655–47662. [Google Scholar] [CrossRef]

- Available online: https://www.analog.com/en/products/adf4355-2.html (accessed on 31 January 2022).

- Available online: https://www.st.com/resource/en/datasheet/stw81200.pdf (accessed on 31 January 2022).

- El Alaoui Ismaili, Z.; Ismaili, A.; Ajib, W.; Gagnon, F.; Nabki, F. A 0.13 μm CMOS fully integrated 0.1 to 12 GHz frequency synthesizer for avionic SDR applications. In Proceedings of the IEEE International Symposium on Circuits and Systems (ISCAS) 2017, Baltimore, MD, USA, 28–31 May 2017; pp. 1–4. [Google Scholar]

- Kim, N.-S.; Rabaey, J.M. A 3–10 mW, 3.1–10.6 GHz integer-N QPLL with reference spur reduction technique for UWB-based cognitive radios. In Proceedings of the IEEE Radio Frequency Integrated Circuits Symposium, Phoenix, AZ, USA, 17–19 May 2015; pp. 67–70. [Google Scholar]

- Yu, S.-A.; Kinget, P. A 0.65-V 2.5-GHz Fractional-N Synthesizer with Two-Point 2-Mb/s GFSK Data Modulation. IEEE J. Solid-State Circuits 2009, 44, 411–2425. [Google Scholar] [CrossRef]

- Ko, J.; Kim, J.; Cho, S.; Lee, K. A 19-mW 2.6-mm/sup 2/ L1/L2 dual-band CMOS GPS receiver. IEEE J. Solid-State Circuits 2005, 40, 1414–1425. [Google Scholar]

- Li, S.; Li, J.; Gu, X.; Wang, H.; Li, C.; Wu, J.; Ta, M. Reconfigurable All-Band RF CMOS Transceiver for GPS/GLONASS/Galileo/Beidou with Digitally Assisted Calibration. IEEE Trans. Very Large Scale Integr. Syst. 2015, 23, 1814–1827. [Google Scholar] [CrossRef]

- Razavi, B. RF Microelectronics, 2nd ed.; Prentice-Hall: Upper Saddle River, NJ, USA, 2011. [Google Scholar]

- Vaucher, C.; Kasperkovitz, D. A wide-band tuning system for fully integrated satellite receivers. IEEE J. Solid-State Circuits 1998, 33, 987–997. [Google Scholar] [CrossRef]

- Vaucher, C.S.; Ferencic, I.; Locher, M.; Sedvallson, S.; Voegeli, U.; Wang, Z. A family of low-power truly modular programmable dividers in standard 0.35-/spl mu/m CMOS technology. IEEE J. Solid-State Circuits 2000, 35, 1039–1045. [Google Scholar] [CrossRef]

- Elkholy, A.; Saxena, S.; Nandwana, R.K.; Elshazly, A. A 2.0–5.5 GHz Wide Bandwidth Ring-Based Digital Fractional-N PLL With Extended Range Multi-Modulus Divider. IEEE J. Solid-State Circuits 2016, 51, 1771–1784. [Google Scholar] [CrossRef]

- Gundla, A.R.; Chen, T. A low power frequency synthesizer for biosensor applications in the MedRadio band. In Proceedings of the IEEE International Midwest Symposium on Circuits and Systems, Lisbon, Portugal, 24–27 October 2015; pp. 1–4. [Google Scholar]

- Kim, K.-Y.; Min, Y.-J.; Kim, S.-W.; Park, J. Low-power programmable divider with a shared counter for frequency synthesiser. IET Circuits Devices Syst. 2011, 5, 170–176. [Google Scholar] [CrossRef]

- Gangasani, G.R.; Kinget, P.R. A 0.5 V, 9-GHz Sub-Integer Frequency Synthesizer Using Multi-Phase Injection-Locked Prescaler for Phase-Switching-Based Programmable Division with Automatic Injection-Lock Calibration in 45-nm CMOS. IEEE Trans. Circuits Syst. II Express Briefs 2019, 66, 803–807. [Google Scholar] [CrossRef]

- Som, I.; Sarangi, S.; Bhattacharyya, T.K. A 7.1-GHz 0.7-mW Programmable Counter with Fast EOC Generation in 65-nm CMOS. IEEE Trans. Circuits Syst. II Express Briefs 2020, 67, 2397–2401. [Google Scholar] [CrossRef]

- Lin, C.-S.; Chien, H.; Wey, C. A 5.5-GHz 1-mW Full-Modulus-Range Programmable Frequency Divider in 90-nm CMOS Process. IEEE Trans. Circuits Syst. II Express Briefs 2011, 58, 550–554. [Google Scholar] [CrossRef]

- Ergintav, A.; Herzel, F.; Borngraeber, J.; Ng, H.J.; Kissinger, D. Low-power and low-noise programmable frequency dividers in a 130 nm SiGe BiCMOS technology. In Proceedings of the IEEE 15th International New Circuits and Systems Conference (NEWCAS), Strasbourg, France, 25–28 June 2017; pp. 105–108. [Google Scholar]

- Ergintav, A.; Herzel, F.; Fischer, G.; Kissinger, D. A Study of Phase Noise and Frequency Error of a Fractional-N PLL in the Course of FMCW Chirp Generation. IEEE Trans. Circuits Syst. I Regul. Pap. 2019, 66, 1670–1680. [Google Scholar] [CrossRef]

- Kim, N.-S.; Rabaey, J.M. A 3.1–10.6-GHz 57-Bands CMOS Frequency Synthesizer for UWB-Based Cognitive Radios. IEEE Trans. Microw. Theory Tech. 2018, 66, 4134–4146. [Google Scholar] [CrossRef]

- Kulkarni, P.; Garg, S.; Agrawal, S.; Baghini, M.S. Low Power Extended Range Multi-Modulus Divider Using True-Single-Phase-Clock Logic. In Proceedings of the IEEE 34th International Conference on VLSI Design (VLSID), Virtual, 20–24 April 2021; pp. 99–104. [Google Scholar]

- Soares, J.N.; Van Noije, W.A.M. A 1.6-GHz dual modulus prescaler using the extended true-single-phase-clock CMOS circuit technique (E-TSPC). IEEE J. Solid-State Circuits 1999, 34, 97–102. [Google Scholar] [CrossRef] [Green Version]

- Yu, X.P.; Do, M.A.; Lim, W.M.; Yeo, K.S.; Ma, J.-G. Design and Optimization of the Extended True Single-Phase Clock-Based Prescaler. IEEE Trans. Microw. Theory Tech. 2006, 54, 3828–3835. [Google Scholar] [CrossRef]

- Kathiah, S.; Aniruddhan, S. Replica bias scheme for efficient power utilization in high-frequency CMOS digital circuits. In Proceedings of the IEEE International Symposium on Circuits and Systems (ISCAS), Victoria, Australia, 1–5 June 2014; pp. 1002–1005. [Google Scholar]

- Peerla, R.S.; Chary, P.; Dutta, A.; Sahoo, B.D. A Dual VCO Based L5/S Band PLL with Extended Range Divider for IRNSS Application. In Proceedings of the IEEE International Symposium on Circuits and Systems (ISCAS), Austin, TX, USA, 28 May–1 June 2022; pp. 1699–1703. [Google Scholar]

- Jin, J.; Yu, X.; Liu, X.; Lim, W.M.; Zhou, J. A wideband voltage-controlled oscillator with gain linearized varactor bank. IEEE Trans. Components Packag. Manuf. Tech. 2014, 4, 905–910. [Google Scholar] [CrossRef]

- Razavi, B. Design of CMOS Phase-Locked Loops: From Circuit Level to Architecture Level; Cambridge University Press: Cambridge, UK, 2020. [Google Scholar]

- Wang, Y.; Wang, Y.; Wu, Z.; Quan, Z.; Liou, J.J. A Programmable Frequency Divider with a Full Modulus Range and 50% Output Duty Cycle. IEEE Access 2020, 8, 102032–102039. [Google Scholar] [CrossRef]

| Input | Output | ||

|---|---|---|---|

| X | 0 | ||

| 0 | 1 | ||

| 1 | 1 |

| CML | TSPC | E-TSPC | |

|---|---|---|---|

| Speed | High | Moderate | High |

| Input Swing | Low | Rail-to-Rail | Rail-to-Rail |

| Output Swing | Low | Rail-to-Rail | Rail-to-Rail |

| Output Phases | Diff. | Diff./Single | Diff./Single |

| Input Clock | Diff. | Single | Single |

| Power | High | Low | Moderate |

| Single 2/3 Cell | Complete ER-MMD | |||

|---|---|---|---|---|

| ON State | OFF State | All Sets ON | Single Set ON | |

| 15 fF | 12 fF | 120 fF | 96 fF | |

| Band | S Band | Division Range | |

|---|---|---|---|

| MMD control bits | P[4:0] | P[5:0] | |

| SEL = 0 | Yes | No | 32 to 63 |

| SEL = 1 | No | Yes | 64 to 127 |

| S-Band | -Band | |

|---|---|---|

| VCO Frequency (MHz) | 4700–5200 | 2200–2400 |

| LO Frequency (MHz) | 2350–2600 | 1100–1200 |

| Center Frequency (MHz) | 2495.02 | 1178.45 |

| Current (mA) | 3.5 | 5 |

| PN @ 1 MHz (dBc/Hz) | −120 | −120 |

| PN @ 100 KHz (dBc/Hz) | −90 | −90 |

| This Work | [29] | [5] | [6] | |

|---|---|---|---|---|

| Technology (nm) | 65 | 180 | 130 | 65 |

| Division Ratio | 2–511 | 1–256 | 128–192 | 24–80 |

| Supply (V) | 1 | 1.8 | 1.2 | 1 |

| Max. Frequency (GHz) | 6 | 2.3 | 3 | 6.5 |

|

PN at 1 MHz offset (dBc/Hz) | −155 | −140 | NA | −141 |

| Div. Power (mW) | 0.5 | 3.4 | NA | 1 |

| Power Efficiency (GHz/mW) | 12 | 0.68 | NA | 6.25 |

| 50% Output Duty Cycle | No | Yes | No | No |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Shaik Peerla, R.; Dutta, A.; Sahoo, B.D. An Extended Range Divider Technique for Multi-Band PLL. J. Low Power Electron. Appl. 2023, 13, 43. https://doi.org/10.3390/jlpea13030043

Shaik Peerla R, Dutta A, Sahoo BD. An Extended Range Divider Technique for Multi-Band PLL. Journal of Low Power Electronics and Applications. 2023; 13(3):43. https://doi.org/10.3390/jlpea13030043

Chicago/Turabian StyleShaik Peerla, Rizwan, Ashudeb Dutta, and Bibhu Datta Sahoo. 2023. "An Extended Range Divider Technique for Multi-Band PLL" Journal of Low Power Electronics and Applications 13, no. 3: 43. https://doi.org/10.3390/jlpea13030043

APA StyleShaik Peerla, R., Dutta, A., & Sahoo, B. D. (2023). An Extended Range Divider Technique for Multi-Band PLL. Journal of Low Power Electronics and Applications, 13(3), 43. https://doi.org/10.3390/jlpea13030043