Reliability Enhancement Methods for Relaxation Oscillator with Delay Time Cancellation

Abstract

:1. Introduction

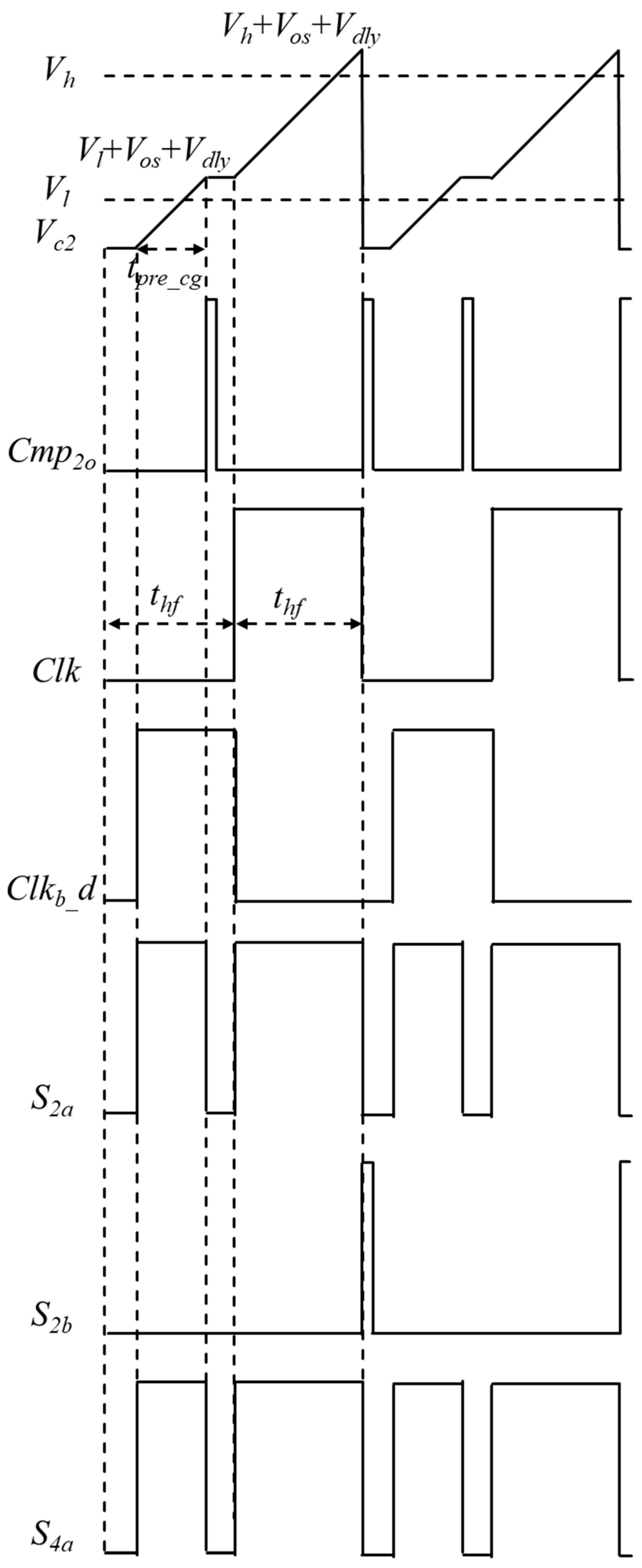

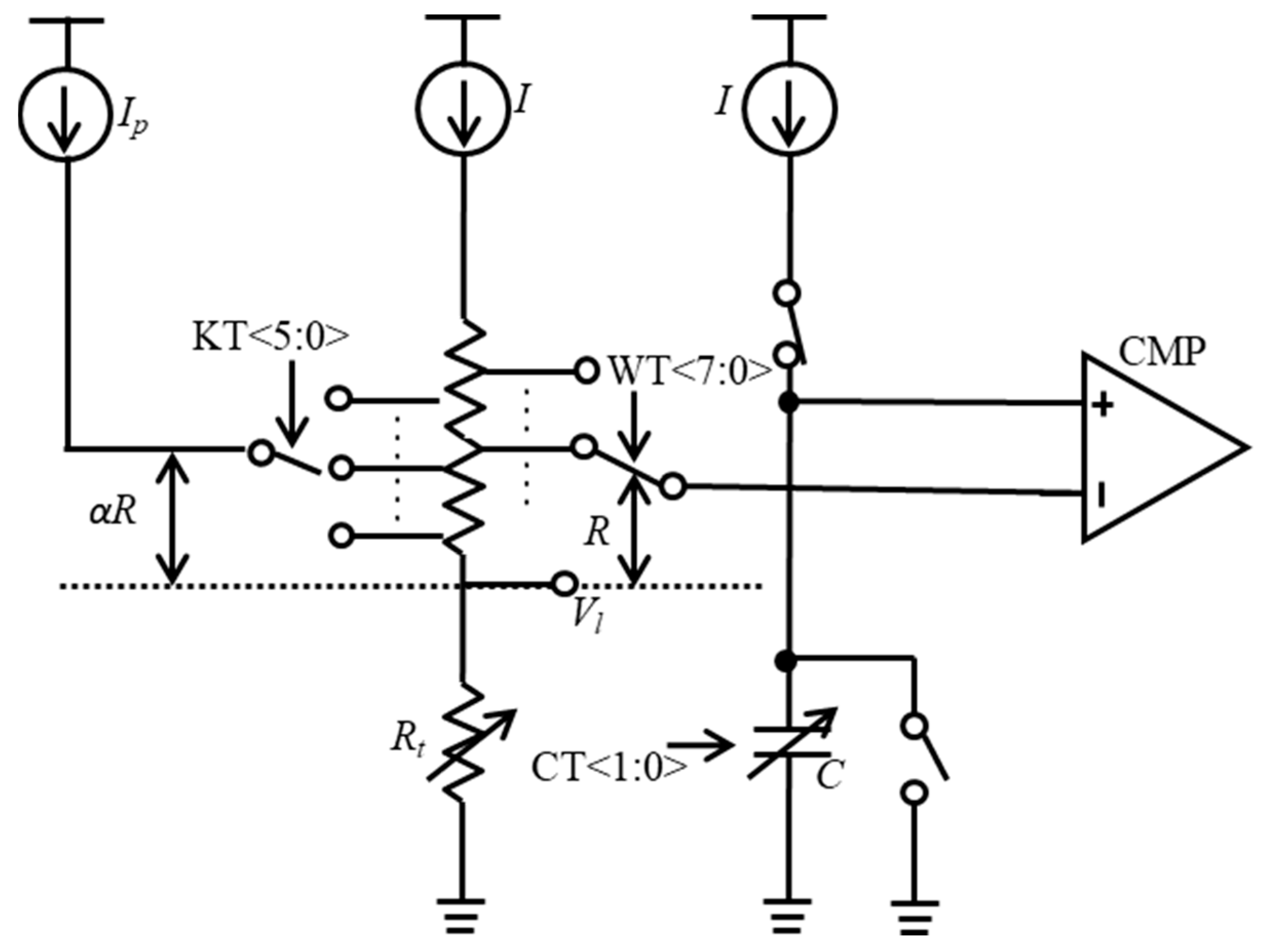

2. Principle of Delay Time Cancellation

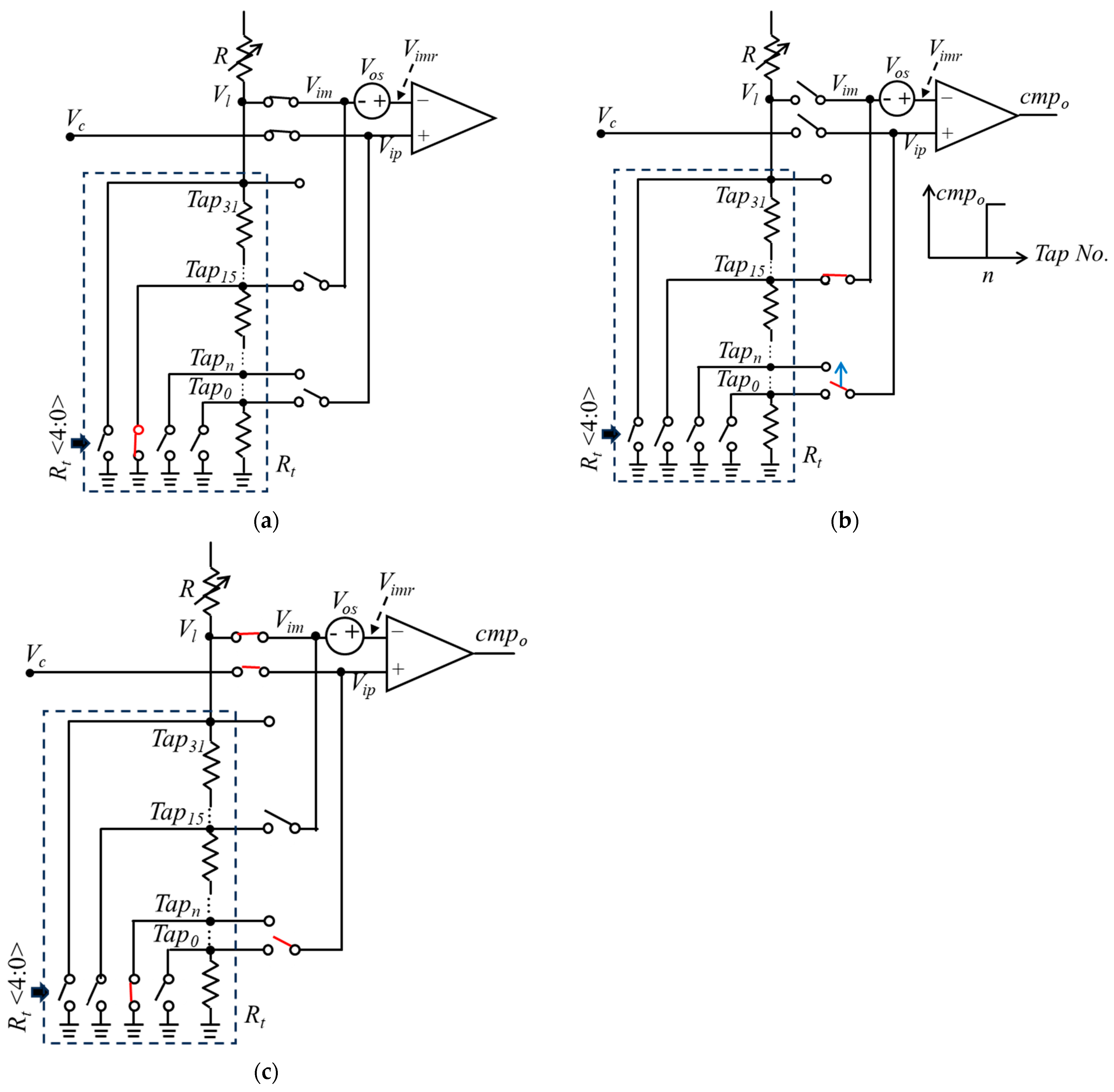

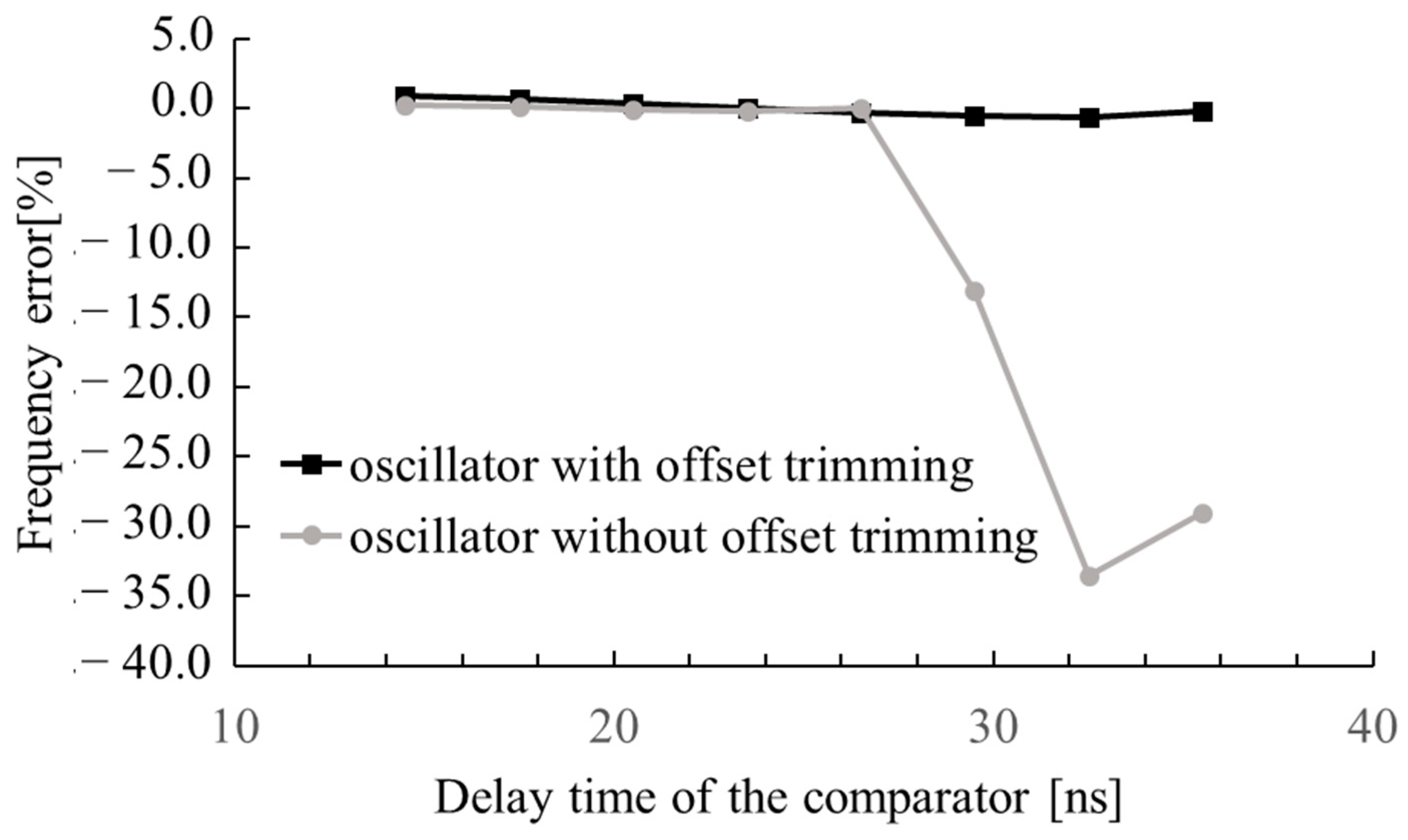

3. Tolerance Limit of the DTC Technique and Offset Trimming

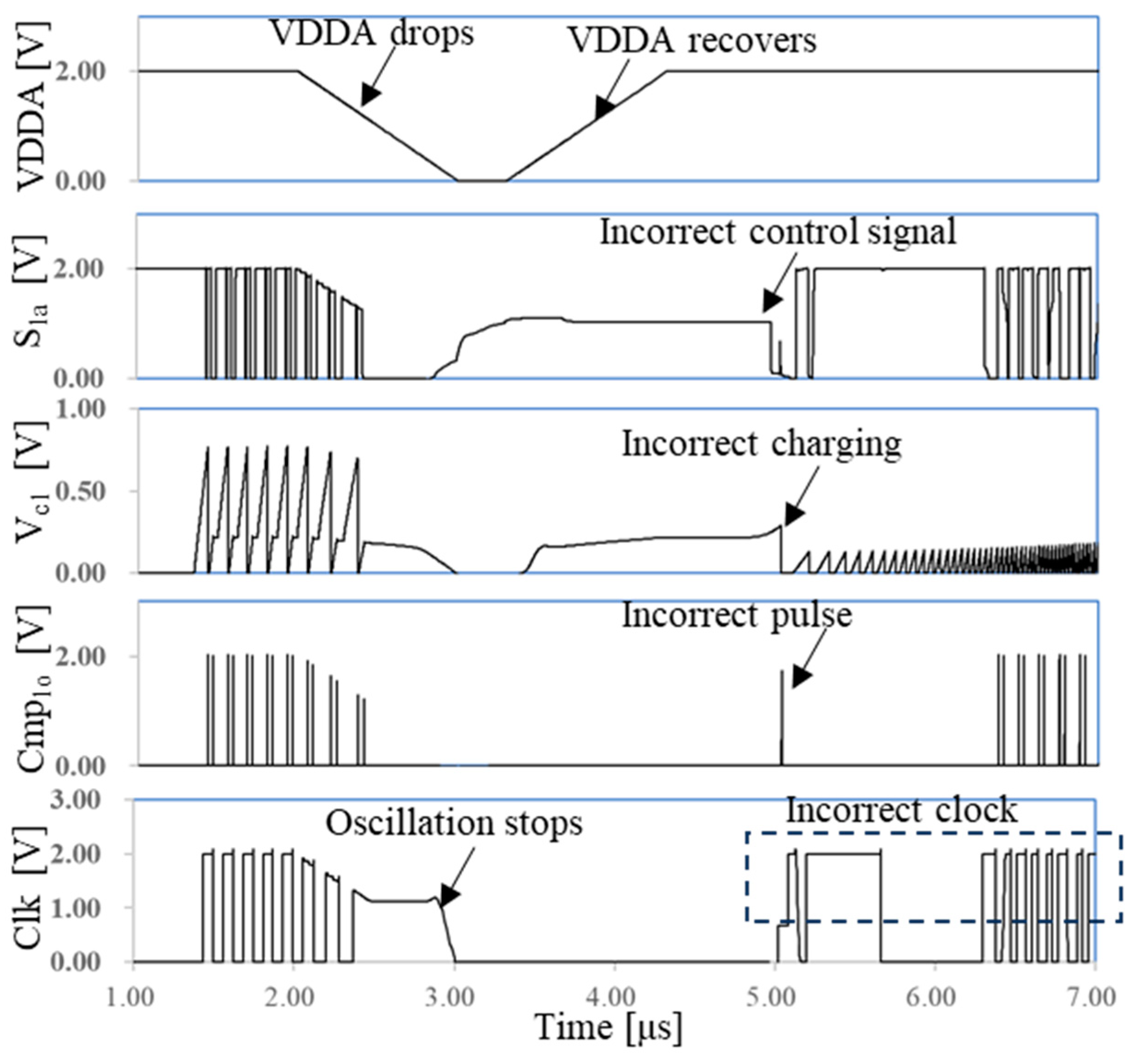

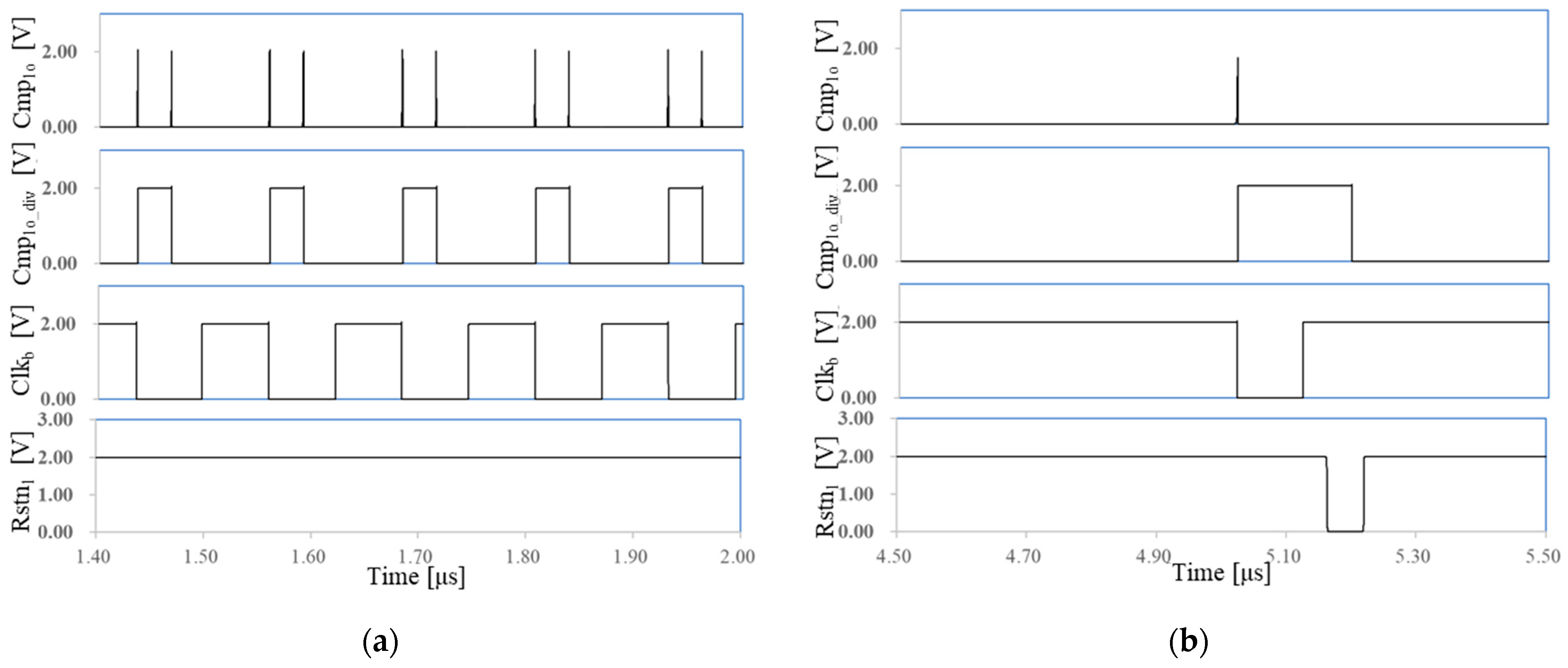

4. Error State Detection and Recovery Circuit

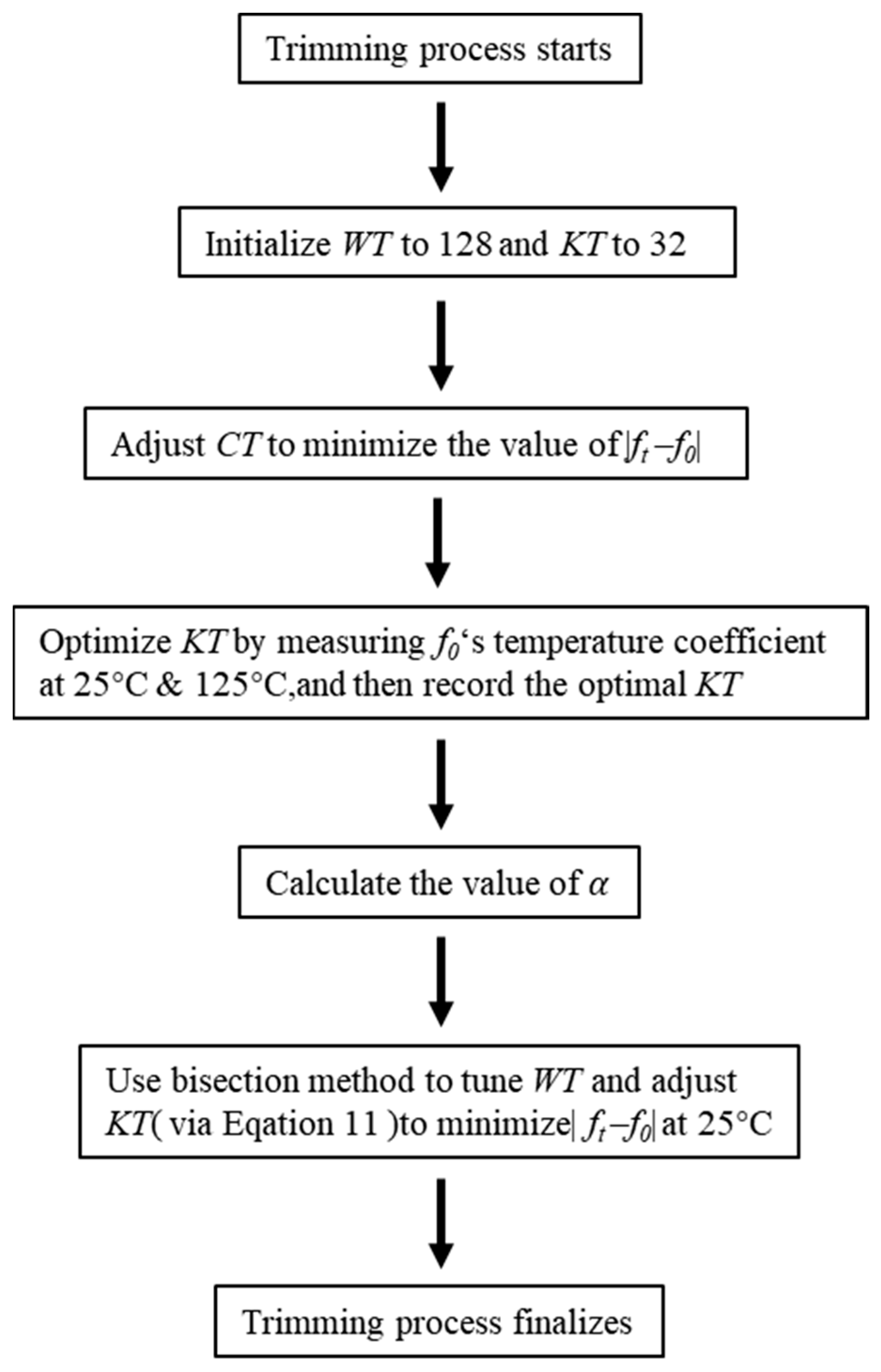

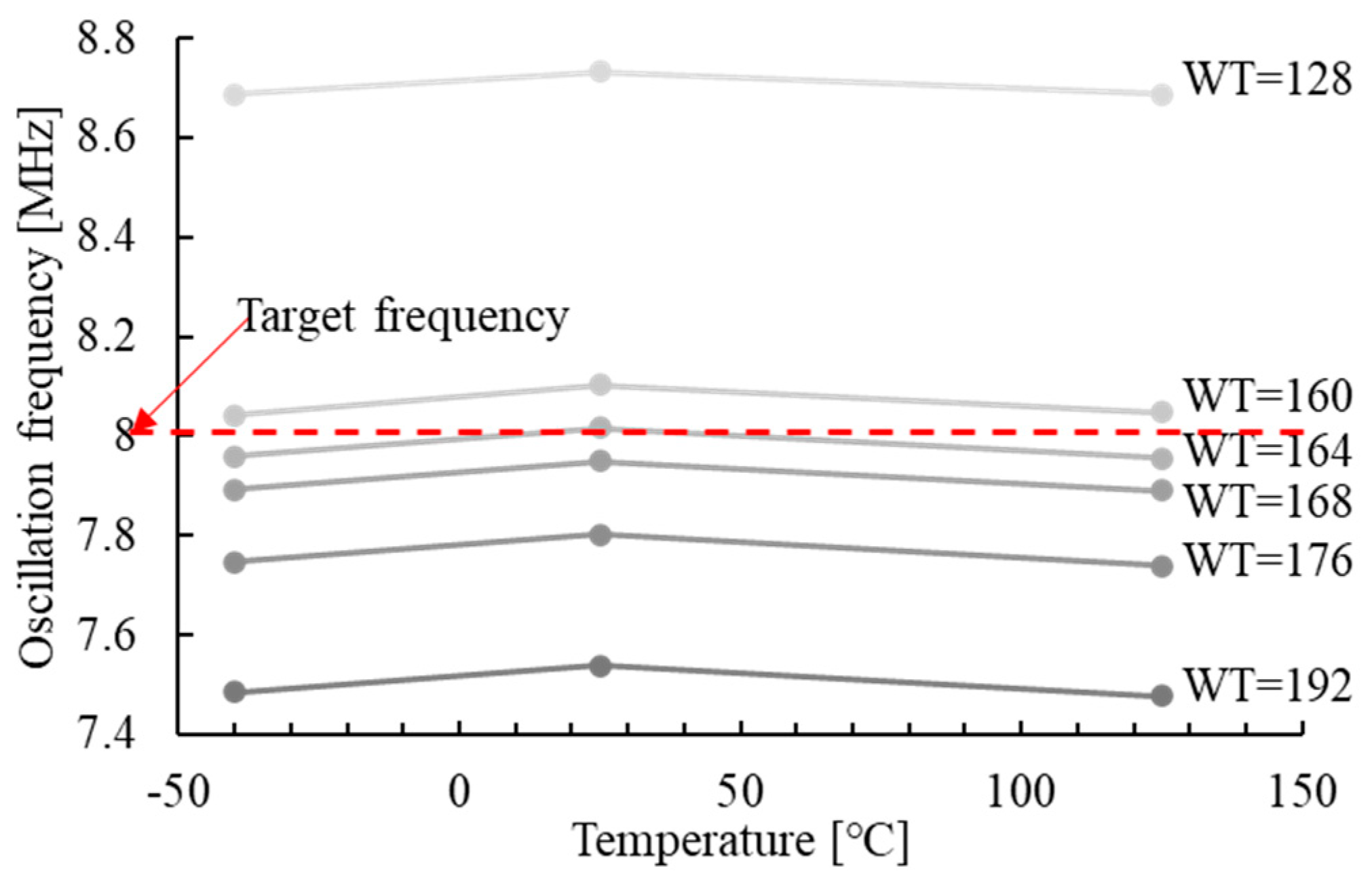

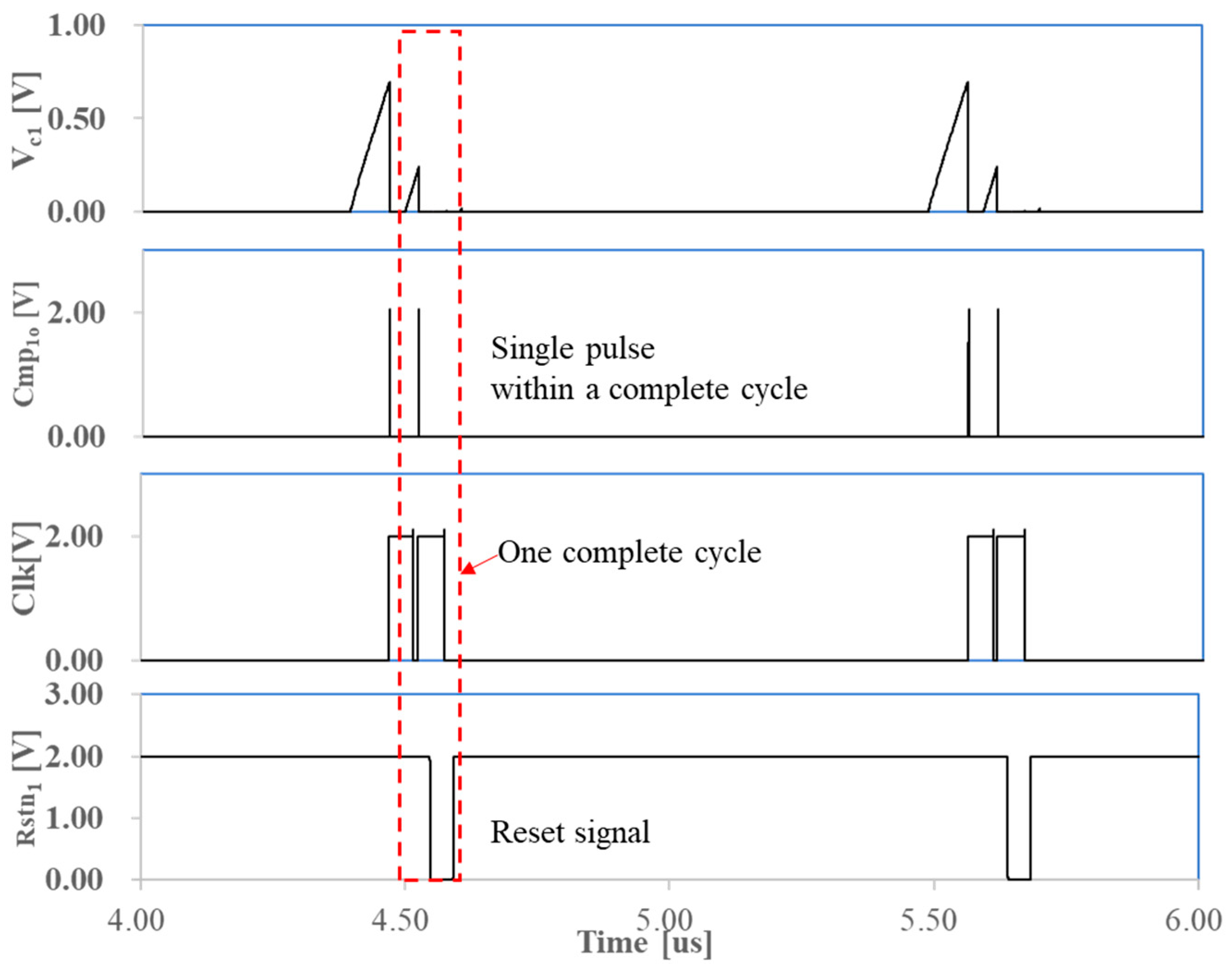

5. Frequency-Trimming Method

- When WT is equal to WT3, the oscillation frequency is less than ft.

- When WT is equal to WT1, the oscillation frequency is greater than ft.

- When WT is equal to WT1, Rstn1 outputs a reset signal.

6. Simulation Results

7. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Ichihashi, M.; Harada, S.; Kanaya, H. 3.3-mA 2.8-GHz bufferless LC oscillator directly driving a 10-mm on-chip clock distribution line. IEICE Electron. Express 2019, 16, 20190301. [Google Scholar] [CrossRef]

- Xu, Z.; Kawahara, T. A Saturating-Integrator-Based Behavioral Model of Ring Oscillator Facilitating PLL Design. IEICE Trans. Electron. 2017, E100C, 370–372. [Google Scholar] [CrossRef]

- Duran, C.; Wachs, M.; Huntington, A.; Ardila, J.; Kang, J.; Amaya, A.; Gomez, H.; Romer, J.; Fernandez, L.; Flechas, F.; et al. An Energy-Efficient RISC-V RV32IMAC Microcontroller for Periodical-Driven Sensing Applications. In Proceedings of the IEEE Custom Integrated Circuits Conference (CICC), Boston, MA, USA, 22–25 March 2020. [Google Scholar]

- Xia, J.; Chen, Z. A 36 MHz Relaxation Oscillator with ±0.2% Temperature Variation for MCU Application. In Proceedings of the IEEE 4th International Conference on Circuits and Systems (ICCS), Chengdu, China, 23–26 September 2022. [Google Scholar]

- Wang, T.; Griffith, D.; Ahmed, M.G.; Zhu, J.; Wei, D.; Elkholy, A.; Elmallah, A.; Hanumolu, P.K. A 6 μW ± 50 ppm/°C ± 1500 ppm/V 1.5 MHz RC Oscillator Using Self-Regulation. IEEE Trans. Circuits Syst. II Express Briefs 2019, 66, 1297–1301. [Google Scholar]

- Sun, J.; Han, Y.; Qian, Y. A low power low supply sensitivity current-mode relaxation oscillator. IEICE Electron. Express 2014, 11, 20140877. [Google Scholar] [CrossRef]

- Paidimarri, A.; Griffith, D.; Wang, A.; Burra, G.; Chandrakasan, A.P. An RC Oscillator with Comparator Offset Cancellation. IEEE J. Solid-State Circuits 2016, 51, 1866–1877. [Google Scholar] [CrossRef]

- Li, Z.; Li, Z.; Zhao, H.; Zhao, H.; Yin, J.; Yin, J.; Qiao, S.; Qiao, S.; Zhou, Y.; Zhou, Y. A fully integrated RC oscillator with adaptive-body-biasing. IEICE Electron. Express 2022, 19, 20220102. [Google Scholar] [CrossRef]

- Chiang, Y.-H.; Liu, S.-I. A Submicrowatt 1.1-MHz CMOS Relaxation Oscillator with Temperature Compensation. IEEE Trans. Circuits Syst. II Express Briefs 2013, 60, 837–841. [Google Scholar] [CrossRef]

- Mikulić, J.; Schatzberger, G.; Barić, A. A 1-MHz on-chip relaxation oscillator with comparator delay cancelation. In Proceedings of the 43rd IEEE European Solid State Circuits Conference, Leuven, Belgium, 11–14 September 2017. [Google Scholar]

- Tokunaga, Y.; Sakiyama, S.; Matsumoto, A.; Dosho, S. An on-chip CMOS relaxation oscillator with voltage averaging feedback. IEEE J. Solid-State Circuits 2010, 45, 1150–1158. [Google Scholar] [CrossRef]

- Lu, S.-Y.; Liao, Y.-T. A low-power, differential relaxation oscillator with the self-threshold-tracking and swing-boosting techniques in 0.18-μm CMOS. IEEE J. Solid-State Circuits 2019, 54, 392–402. [Google Scholar]

- Khashaba, A.; Zhu, J.; Ahmed, M.; Pal, N.; Hanumolu, P.K. A 34 µW 32 MHz RC oscillator with ±530 ppm inaccuracy from −40 °C to 85 °C and 80 ppm/V supply sensitivity enabled by pulse-density modulated resistors. In Proceedings of the IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 16–20 February 2020. [Google Scholar]

- Zhang, G.; Cao, L.; Yayama, K.; Katsushima, A.; Miki, T. A differential on chip oscillator with 1.47-μs startup time and 3.3-ppm/°C temperature coefficient of frequency. IEICE Trans. Fundam. Electron. Commun. Comput. Sci. 2021, E104.A, 499–505. [Google Scholar]

- Pan, S.; Cheng, Y.; Wu, G.; Wang, Z.; Makinwa, K.A.A.; Wu, H. 3.2 A 0.028 mm2 32 MHz RC Frequency Reference in 0.18 μm CMOS with ±900 ppm Inaccuracy from −40 °C to 125 °C and ±1600 ppm Inaccuracy after Accelerated Aging. In Proceedings of the IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 13 November 2024; pp. 56–58. [Google Scholar]

- Chiang, Y.-H.; Liu, S.-I. Nanopower CMOS Relaxation Oscillators With Sub-100 ppm/°C Temperature Coefficient. IEEE Trans. Circuits Syst. II Express Briefs 2014, 61, 661–665. [Google Scholar]

- Huang, K.-K.; Wentzloff, D.D. A 1.2-MHz 5.8-μW Temperature-Compensated Relaxation Oscillator in 130-nm CMOS. IEEE Trans. Circuits Syst. II Express Briefs 2014, 61, 334–338. [Google Scholar]

- Zhou, W.; Goh, W.L.; Gao, Y. A 3-MHz 17.3-μW 0.015% Period Jitter Relaxation Oscillator with Energy Efficient Swing Boosting. IEEE Trans. Circuits Syst. II Express Briefs 2020, 67, 1745–1749. [Google Scholar]

- Liu, Y.; Zhu, Z.; Bao, R.; Lin, J.; Yin, J.; Li, Q.; Mak, P.-I.; Yang, S. A Compact Sub-nW/kHz Relaxation Oscillator Using a Negative-Offset Comparator with Chopping and Piecewise Charge-Acceleration in 28-nm CMOS. IEEE Trans. Circuits Syst. I Regul. Pap. 2024, 71, 515–525. [Google Scholar] [CrossRef]

- Lei, K.-M.; Mak, P.-I.; Martins, R.P. A 0.35-V 5200-μm2 2.1-MHz Temperature-Resilient Relaxation Oscillator With 667 fJ/Cycle Energy Efficiency Using an Asymmetric Swing-Boosted RC Network and a Dual-Path Comparator. IEEE J. Solid-State Circuits 2021, 56, 2701–2710. [Google Scholar] [CrossRef]

- Tokairin, T.; Nose, K.; Takeda, K.; Noguchi, K.; Maeda, T.; Kawai, K.; Mizuno, M. A 280 nW, 100 kHz, 1-cycle start-up time, on-chip CMOS relaxation oscillator employing a feedforward period control scheme. In Proceedings of the 2012 Symposium on VLSI Circuits (VLSIC), Honolulu, HI, USA, 13–15 June 2012; pp. 16–17. [Google Scholar]

- Aiello, O.; Crovetti, P.; Alioto, M. A Sub-Leakage PW-Power HZ-Range Relaxation Oscillator Operating with 0.3 V–1.8 V Unregulated Supply. In Proceedings of the 2018 IEEE Symposium on VLSI Circuits, Honolulu, HI, USA, 18–22 June 2018; pp. 119–120. [Google Scholar]

- Jeong, S.; Lee, I.; Blaauw, D.; Sylvester, D. A 5.8 nW CMOS Wake-Up Timer for Ultra-Low-Power Wireless Applications. IEEE J. Solid-State Circuits 2015, 50, 1754–1763. [Google Scholar] [CrossRef]

- Wang, H.; Mercier, P.P. A Reference-Free Capacitive-Discharging Oscillator Architecture Consuming 44.4 pW/75.6 nW at 2.8 Hz/6.4 kHz. IEEE J. Solid-State Circuits 2016, 51, 1423–1435. [Google Scholar] [CrossRef]

- Nadeau, P.M.; Paidimarri, A.; Chandrakasan, A.P. Ultra Low-Energy Relaxation Oscillator With 230 fJ/cycle Efficiency. IEEE J. Solid-State Circuits 2016, 51, 789–799. [Google Scholar] [CrossRef]

- Lee, J.; George, A.K.; Je, M. An Ultra-Low-Noise Swing-Boosted Differential Relaxation Oscillator in 0.18-μm CMOS. IEEE J. Solid-State Circuits 2020, 55, 2489–2497. [Google Scholar] [CrossRef]

- Choe, K.; Bernal, O.D.; Nuttman, D.; Je, M. A precision relaxation oscillator with a self-clocked offset-cancellation scheme for implantable biomedical SoCs. In Proceedings of the 2009 IEEE International Solid-State Circuits Conference-Digest of Technical Papers, San Francisco, CA, USA, 8–12 February 2009; pp. 402–403,403a. [Google Scholar]

| [6] | [7] | [8] | [9] | [10] | [16] | |

| Process [nm] | 180 | 65 | 55 | 180 | 350 | 180 |

| Freq. [Hz] | 100 k | 18.5 k | 33 k | 1.1 M | 1 M | 28 k |

| Current eff. [μA/MHz] | 5.4 | 7 | 9.24 | 0.4 | 63.6 | 1.19 |

| Temp. sen. [ppm/°C] | 51 | 85 | 58 | 64 | 48 | 95.5 |

| Temp. range [°C] | −40~85 | −40~90 | −40~125 | −20~80 | −40~125 | −20~80 |

| Line sen. [%/V] | 0.4 | 5 | 0.75 | 3 | 0.28 | 3 |

| *2 FoM [μA·(108 MHz·°C·V)−1] | 110.6 | 2972.9 | 403.3 | 83.3 | 863.9 | 340.9 |

| Trimming points for temperature compensation | - | - | - | - | - | - |

| Type of results | Simulation | Measurement | Simulation | Measurement | Measurement | Measurement |

| [17] | [18] | [19] | [20] | [21] | [22] | |

| Process [nm] | 130 | 65 | 28 | 28 | 90 | 180 |

| Freq. [Hz] | 1.2 M | 3 M | 28.5 k | 2.1 M | 100 k | 4 |

| Current eff. [μA/MHz] | 4.83 | 5.77 | 1.21 | 1.85 | 3.5 | 2.08 |

| Temp. sen. [ppm/°C] | 296 | 133.3 | 33.3 | 158 | 104.6 | 40,000 |

| Temp. range [°C] | −40~80 | 0~90 | −40~85 | −20~120 | −40~90 | −20~40 |

| Line sen. [%/V] | 3.6 | 0.6 | 1.9 | 26.8 | 9.37 | 10 |

| *2 FoM [μA·(108 MHz·°C·V)−1] | 5150.4 | 461.3 | 76.8 | 7841.5 | 3431.4 | 830,000 |

| Trimming points for temperature compensation | - | - | 1 | 3 | - | - |

| Type of results | Measurement | Measurement | Measurement | Measurement | Measurement | Measurement |

| [23] | [24] | [25] | [26] | [27] | This Work | |

| Process [nm] | 180 | 65 | 180 | 180 | 130 | 40 |

| Freq. [Hz] | 11 | 2.8 | 18 | 10.5 M | 3.2 M | 8 M |

| Current eff. [μA/MHz] | 439.4 | 31.7 | 0.39 | 14.95 | 8.48 | 3.6 |

| Temp. sen. [ppm/°C] | 45 | 1260 | 20,000 | 137 | 1253 | 48 *2 291 |

| Temp. range [°C] | −10~90 | −40~60 | −30~60 | −40~125 | −20~60 | −40~125 |

| Line sen. [%/V] | 1 | 8.63 | 24.4 | 4.4 | 0.4 | 0.275 |

| *1 FoM [μA·(108 MHz·°C·V)−1] | 19,800 | 345,000 | 190,000 | 9010 | 4250 | 48 |

| Trimming points for temperature compensation | - | - | - | - | - | 2 |

| Type of results | Measurement | Measurement | Measurement | Measurement | Measurement | Simulation |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Xu, K.; Dai, H.; Wu, Z.; Huang, Z.; Zhang, G.; Yu, X.; Wang, W.; Xuan, G. Reliability Enhancement Methods for Relaxation Oscillator with Delay Time Cancellation. J. Low Power Electron. Appl. 2024, 14, 47. https://doi.org/10.3390/jlpea14040047

Xu K, Dai H, Wu Z, Huang Z, Zhang G, Yu X, Wang W, Xuan G. Reliability Enhancement Methods for Relaxation Oscillator with Delay Time Cancellation. Journal of Low Power Electronics and Applications. 2024; 14(4):47. https://doi.org/10.3390/jlpea14040047

Chicago/Turabian StyleXu, Kunpeng, Hongguang Dai, Zhanxia Wu, Zhibo Huang, Guoqiang Zhang, Xiaopeng Yu, Wechang Wang, and Gang Xuan. 2024. "Reliability Enhancement Methods for Relaxation Oscillator with Delay Time Cancellation" Journal of Low Power Electronics and Applications 14, no. 4: 47. https://doi.org/10.3390/jlpea14040047