A 0.7 V, Ultra-Wideband Common Gate LNA with Feedback Body Bias Topology for Wireless Applications

Abstract

:1. Introduction

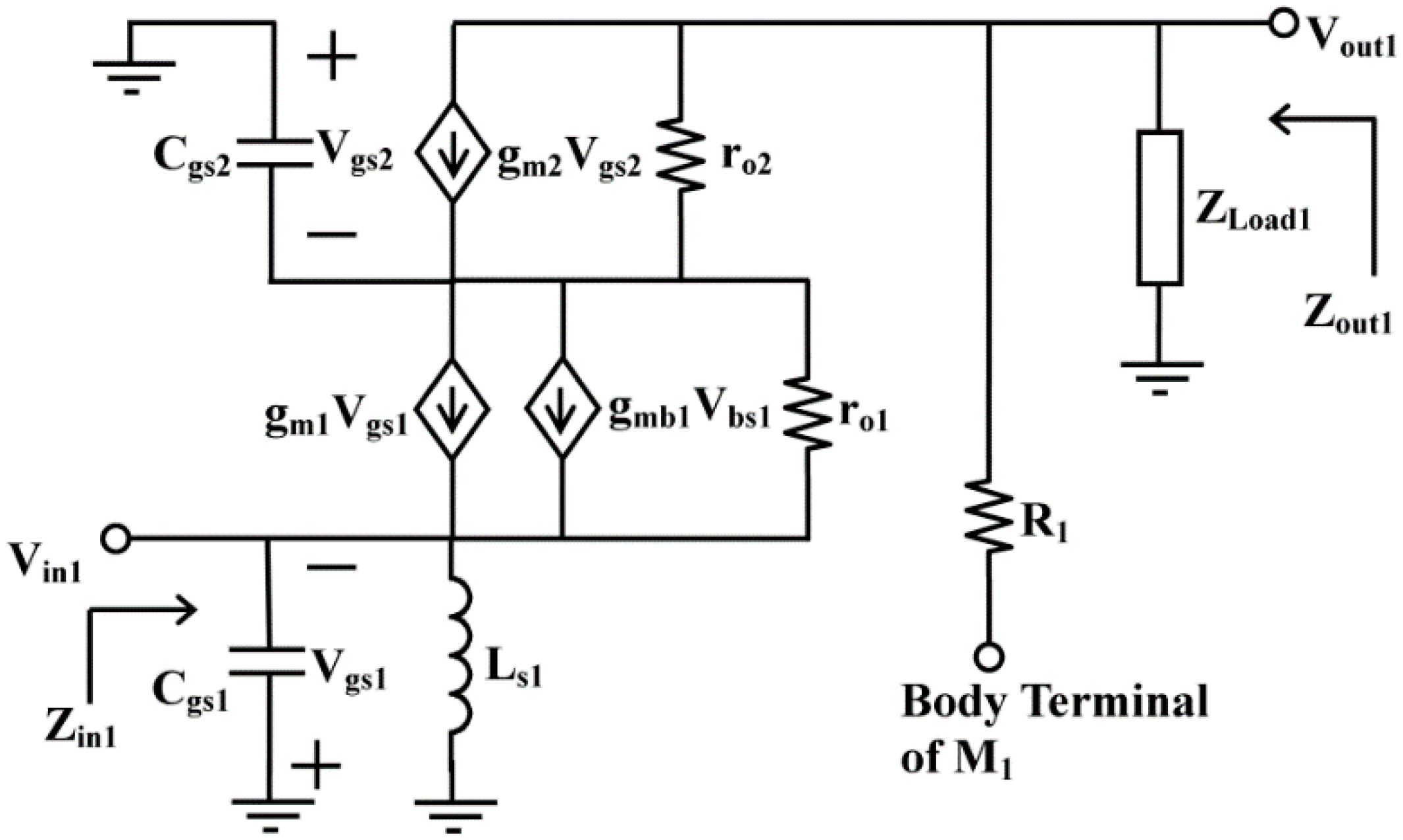

2. Operational Principle and Circuit Implementation

2.1. Forward Body Baising to Decrease Power Consumption

2.2. Frequency Response of S11 and S22

2.3. Noise Figure Analysis

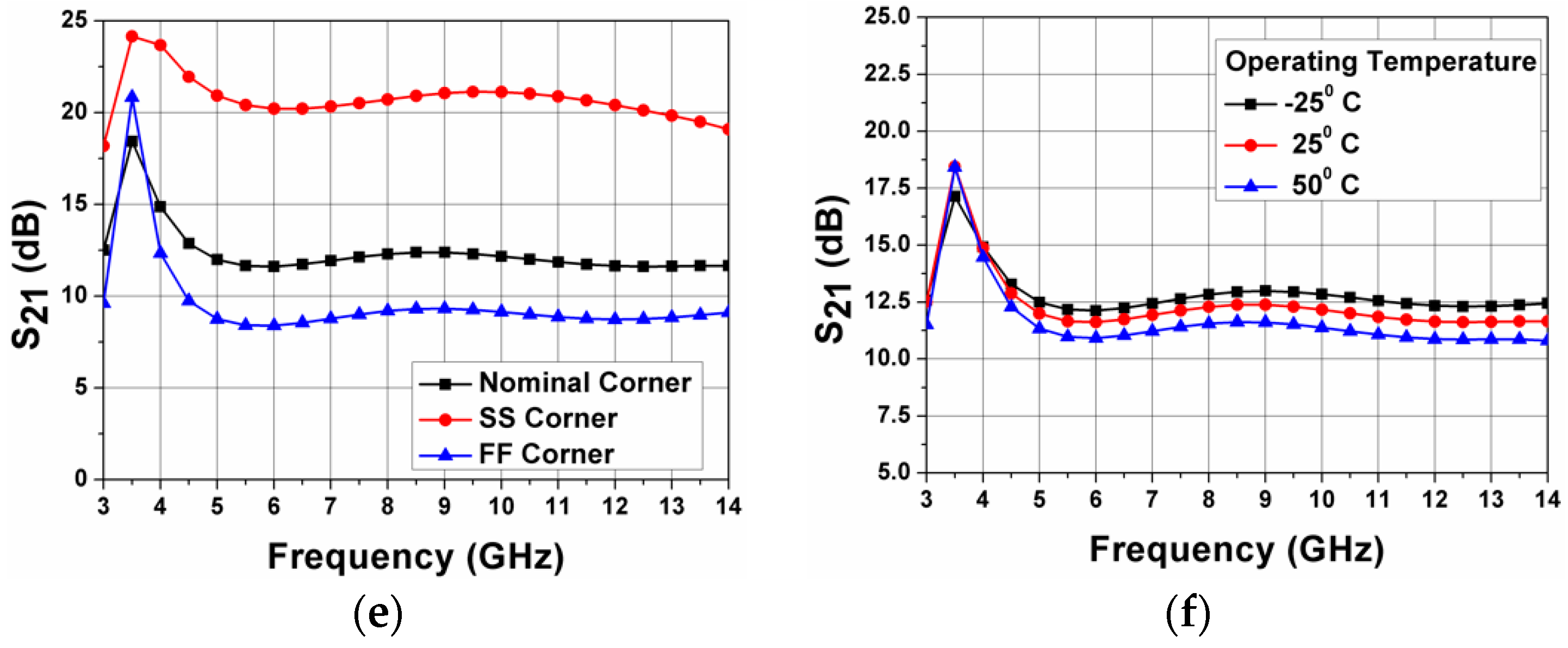

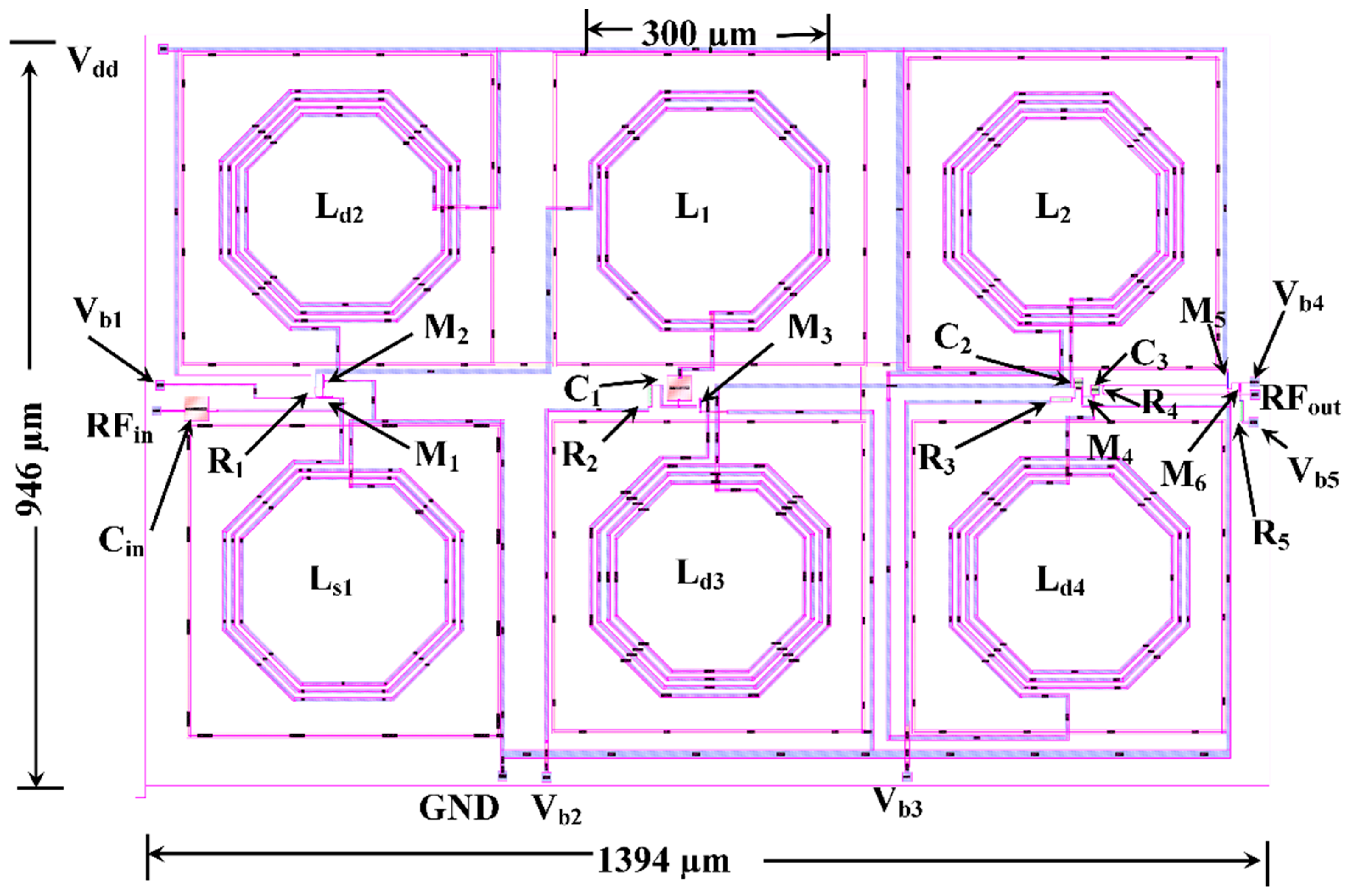

3. Simulation Results

4. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Ultra-Wide-Band (UWB). First Report and Order Transl.; Federal Communications Commission (FCC): Washington, DC, USA, 2002.

- Shim, J.; Yang, T.; Jeong, J. Design of low power CMOS ultra wideband low noise amplifier using noise cancelling technique. Microelectron. J. 2013, 44, 821–826. [Google Scholar] [CrossRef]

- Pandey, S.; Singh, J. A low power and high gain CMOS LNA for UWB applications in 90nm CMOS process. Microelectron. J. 2015, 46, 390–397. [Google Scholar] [CrossRef]

- Lu, Y.; Yeo, K.S.; Cabuk, A.; Ma, J.; Do, M.A.; Lu, Z. A novel CMOS low noise amplifier design for 3.1 to 10.6 GHz ultra-wide-band wireless receivers. IEEE Trans. Circuits Syst. 2006, 53, 1683–1692. [Google Scholar] [CrossRef]

- Lo, Y.T.; Kiang, J.F. Design of wideband LNAs using parallel-to-series resonant matching network between common-gate and common-source stages. IEEE Trans. Microw. Theory Tech. 2011, 59, 2285–2294. [Google Scholar] [CrossRef]

- Bi, Y.; Yuan, J.S.; Jin, Y. Beyond the interconnections: Split manufacturing in RF designs. Electronics 2015, 4, 541–564. [Google Scholar] [CrossRef]

- Bi, Y.; Shamsi, K.; Yuan, J.S.; Gaillardon, P.E.; Micheli, G.D.; Yin, X.; Hu, X.S.; Niemier, M.; Jin, Y. Emerging technology based design of primitives for hardware security. ACM J. Emerg. Technol. Comput. Syst. 2016, 13, 3. [Google Scholar] [CrossRef]

- Nakhlestani, A.; Hakimi, A.; Movahhedi, M. A novel configuration for UWB LNA suitable for low power and low voltage applications. Microelectron. J. 2012, 43, 444–451. [Google Scholar] [CrossRef]

- Arshad, S.; Zafar, F.; Ramzan, R.; Wahab, Q. Wideband and multiband CMOS LNAs: State-of-the-art and future prospects. Microelectron. J. 2013, 44, 774–786. [Google Scholar] [CrossRef]

- Chen, H.K.; Lin, Y.S.; Lu, S.S. Analysis and design of a 1.6–28 GHz compact wideband LNA in 90nm CMOS using a π-match input network. IEEE Trans. Microw. Theory Tech. 2010, 58, 2092–2104. [Google Scholar] [CrossRef]

- Parvizi, M.; Allidina, K.; Gamal, M.N.E. A sub-mW, ultra-low-voltage, wideband low-noise amplifier design technique. IEEE Trans. Very Large Scale Integr. Syst. 2015, 23, 1111–1122. [Google Scholar] [CrossRef]

- Huang, D.; Diao, S.; Qian, W.; Lin, F. A resistive feedback LNA in 65 nm CMOS with a gate inductor for bandwidth extension. Microelectron. J. 2015, 46, 103–110. [Google Scholar] [CrossRef]

- Feng, C.; Yu, X.; Lu, Z.; Lim, W.; Sui, W. 3–10 GHz self biased resistive feedback LNA with inductive source degeneration. Electron. Lett. 2013, 49, 387–388. [Google Scholar] [CrossRef]

- Hampel, S.; Schmitz, O.; Tiebout, M.; Rolfes, I. Inductorless 1–10.5 GHz wideband LNA for multistandard applications. In Proceedings of the IEEE Asian Solid State Circuit Conference, Taipei, Taiwan, 16–18 November 2009; pp. 269–272. [Google Scholar]

- Kytonaki, E.S.; Simitsakis, P.; Bazigos, A.; Papananos, Y. Design and implementation of a 1-V transformer feedback low-noise amplifier (LNA) at 5–6 GHz, in 90 nm complementary metal-oxide-semiconductor (CMOS) process. Int. J. Electron. 2011, 98, 235–248. [Google Scholar] [CrossRef]

- Chang, T.; Chen, J.; Rigge, L.A.; Lin, J. ESD-protected wideband CMOS LNAs using modified resistive feedback techniques with chip-on-board packaging. IEEE Trans. Microw. Theory Tech. 2008, 6, 1817–1826. [Google Scholar] [CrossRef]

- Arshad, S.; Ramzan, R.; Muhammad, K.; Wahab, Q. A sub-10mW, noise cancelling, wideband LNA for UWB applications. Int. J. Electron. Commun. 2015, 69, 109–118. [Google Scholar] [CrossRef]

- Machiels, B.; Reynaert, P.; Steyaert, M. Power efficient distributed Low Noise Amplifier in 90 nm CMOS. In Proceedings of the IEEE International Symposium on Radio Frequency Integrated Circuits, Anaheim, CA, USA, 23–25 May 2010; pp. 131–134. [Google Scholar] [CrossRef]

- Mæland, K.; Kjelgård, K.G.; Lande, T.S. CMOS distributed amplifiers for UWB radar. In Proceedings of the IEEE International Symposium on Circuits and Systems, Lisbon, Portugal, 24–27 May 2015; pp. 1298–1301. [Google Scholar] [CrossRef]

- Saberkari, A.; Kazemi, S.; Shirmohammadli, V.; Yagoub, M.C.E. gm-boosted flat gain UWB low noise amplifier with active inductor-based input matching network. Integr. VLSI J. 2016, 52, 323–333. [Google Scholar] [CrossRef]

- Rashtian, H.; Mirabbasi, S. Applications of body biasing in multistage CMOS low noise amplifiers. IEEE Trans. Circuits Syst. 2014, 6, 1638–1647. [Google Scholar] [CrossRef]

- Wan, Q.; Wang, Q.; Zheng, Z. Design and analysis of a 3.1–10.6 GHz UWB low noise amplifier with forward body bias technique. Int. J. Electron. Commun. 2015, 69, 119–125. [Google Scholar] [CrossRef]

- Sansen, W.M. Analog Design Essentials; Springer: New York, NY, USA, 2006. [Google Scholar]

- Mohan, S.S.; del Mar Hershenson, M.; Boyd, S.P.; Lee, T.H. Simple Accurate Expressions for Planar Spiral Inductances. IEEE J. Solid-State Circuits 1999, 34, 1419–1424. [Google Scholar] [CrossRef]

- Alvadi-Rad, H.; Ziabakhsh, S.; Yaqoub, M.C.E. A 1.2 V CMOS common-gate low noise amplifier for UWB wireless communications. J. Circuits Syst. Comput. 2013, 22, 1350052. [Google Scholar] [CrossRef]

- Hayati, M.; Cheraghaliei, S.; Zrghami, S. Design of UWB low noise amplifier using noise-canceling and current-reused techniques. Integr. VLSI J. 2018, 60, 232–239. [Google Scholar] [CrossRef]

- Chen, J.-D. A Low-Power Ultrawideband Low-Noise Amplifier in 0.18 μm CMOS Technology. Active Passive Electron. Compon. 2013, 2013, 953498. [Google Scholar] [CrossRef]

- Sapone, G. A 3–10-GHz low-power CMOS low-noise amplifier for ultra-wideband communication. IEEE Trans. Microw. Theory Tech. 2011, 59, 678–686. [Google Scholar] [CrossRef]

- Rastegar, H.; Saryazdi, S.; Hakimi, A. A low power and high linearity UWB low noise amplifier (LNA) for 3.1–10.6 GHZ wireless applications in 0.13 µm CMOS process. Microelectron. J. 2013, 44, 201–209. [Google Scholar] [CrossRef]

- Soon, K.L.; Ramiah, H.; Tey, Y.Y. A 3.0–10.0 GHz UWB Low Noise Amplifier with Forward Body bias Technique. IETE J. Res. 2016, 62, 91–99. [Google Scholar] [CrossRef]

- Hsieh, H.H.; Wang, J.H.; Lu, L.H. Gain-enhancement techniques for CMOS folded cascode LNAs at low-voltage operations. IEEE Trans. Microw. Theory Tech. 2008, 56, 1807–1816. [Google Scholar] [CrossRef]

| Transistors W (µm) × L (µm) | Inductance (nH) | Resistance (KΩ) | Capacitance (pF) | ||||

|---|---|---|---|---|---|---|---|

| M1 | 30 × 0.09 | Ls1 | 5.5 | R1 | 0.5 | Cin | 1.0 |

| M2 | 45 × 0.09 | Ld2 | 8.5 | R2 | 5.0 | C1 | 1.0 |

| M3 | 35 × 0.09 | L1 | 5.0 | R3 | 5.0 | C2 | 1.5 |

| M4 | 18 × 0.09 | Ld3 | 10.0 | R4 | 0.5 | C3 | 1.5 |

| M5 | 21 × 0.09 | L2 | 8.5 | R5 | 5.0 | ||

| M6 | 35 × 0.09 | Ld4 | 7.1 | ||||

| Ref. & Year | Topology | Tech (nm) | Vdd (V) | BW (GHz) | S11 (dB) | S21 (dB) | S22 (dB) | NF (dB) | IIP3 (dBm) | Power (mW) | FOM1 |

|---|---|---|---|---|---|---|---|---|---|---|---|

| This work S | CG Feedback Body Bias | 90 | 0.7 | 3.3–13.0 | <−10.6 | 14.7 ± 0.5 @ 4.5–13.0 GHz | <−10.8 | 3.0 ± 0.5 | −19 @ 7.0 GHz | 5.2 | 8.54 |

| [10], 2010 m | CS-resistive feedback | 90 | 1.2 | 3.1–10.6 | <−14.1 | 10.4 ± 0.2 *, 10.68 $ | - | 3.075 ± 0.155 | +4 | 21.6 | - |

| [28], 2011 m | Current-reused | 90 | 1.2 | 2.6–10.2 | <−9 | 12.5 $ | 3–7 | - | 7.2 | - | |

| [16], 2008 m | CS-resistive feedback | 90 | 1.2 | 0.2–9 | <−10 | 10 | -- | 4.2 # | −8 | 20 | - |

| [29], 2013 S | CS Forward Body Bias | 130 | 0.6 | 3.1–10.6 | ≤−5 | 21 $ | ≤−10.6 | 1.0–3.9 | +4.56 @ 6.0 GHz | 4.1 | - |

| [30], 2015 m | CS Forward Body Bias | 130 | 1.0 | 3.0–10.0 | ≤−11.4 | 12.1 $ | ≤11.7 | 3.04–3.48 | −6.6 @ 6.0 GHz | 13.0 | - |

| [17], 2015 S | Noise cancelling | 130 | 1.3 | 2.3–9.37 a | ≤−8 | 10.3 $ | ≤−8 | 3.68–9.2 | −4 @ 4.5 GHz | 9.97 | 5.71 |

| [27], 2013 m | CS Resistive Termination | 180 | 1.0 | 3–5.6 a | ≤−9 @ 3–11 GHz | 9 a | ≤−8 @ 3–7.5 GHz | 4.6–5.3 a | +2 @ 5.3 GHz | 9.0 | - |

| [22], 2015 L | CS Forward Body Bias | 180 | 1.5 | 3.1–10.6 | <−10.6 | 14.4 ± 1.4 | <−12.1 | 2.2–3.2 | −6.0 | 9.0 | - |

| [25], 2013 S | Common Gate | 180 | 1.2 | 3.1–10.6 | <−5.5 | 12.75 ± 0.83 | <−7 | 2.5–3.7 | −8.2 @ 5 GHz | 12.14 | 12.58 |

| [26], 2018 S | Noise cancelling | 180 | 1.8 | 3–12 | <−10 | 19.24–20.24 | - | 1.72–1.99 | 23.23 | 7.1 | |

| [31], 2008 S | Forward Body Bias | 180 | 0.6 | 5 | <−8 | 14.1 | - | 3.65 | −17.1 | 1.68 | - |

© 2018 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Singh, V.; Arya, S.K.; Kumar, M. A 0.7 V, Ultra-Wideband Common Gate LNA with Feedback Body Bias Topology for Wireless Applications. J. Low Power Electron. Appl. 2018, 8, 42. https://doi.org/10.3390/jlpea8040042

Singh V, Arya SK, Kumar M. A 0.7 V, Ultra-Wideband Common Gate LNA with Feedback Body Bias Topology for Wireless Applications. Journal of Low Power Electronics and Applications. 2018; 8(4):42. https://doi.org/10.3390/jlpea8040042

Chicago/Turabian StyleSingh, Vikram, Sandeep K. Arya, and Manoj Kumar. 2018. "A 0.7 V, Ultra-Wideband Common Gate LNA with Feedback Body Bias Topology for Wireless Applications" Journal of Low Power Electronics and Applications 8, no. 4: 42. https://doi.org/10.3390/jlpea8040042

APA StyleSingh, V., Arya, S. K., & Kumar, M. (2018). A 0.7 V, Ultra-Wideband Common Gate LNA with Feedback Body Bias Topology for Wireless Applications. Journal of Low Power Electronics and Applications, 8(4), 42. https://doi.org/10.3390/jlpea8040042