Intelligent Security Monitoring System Based on RISC-V SoC

Abstract

:1. Introduction

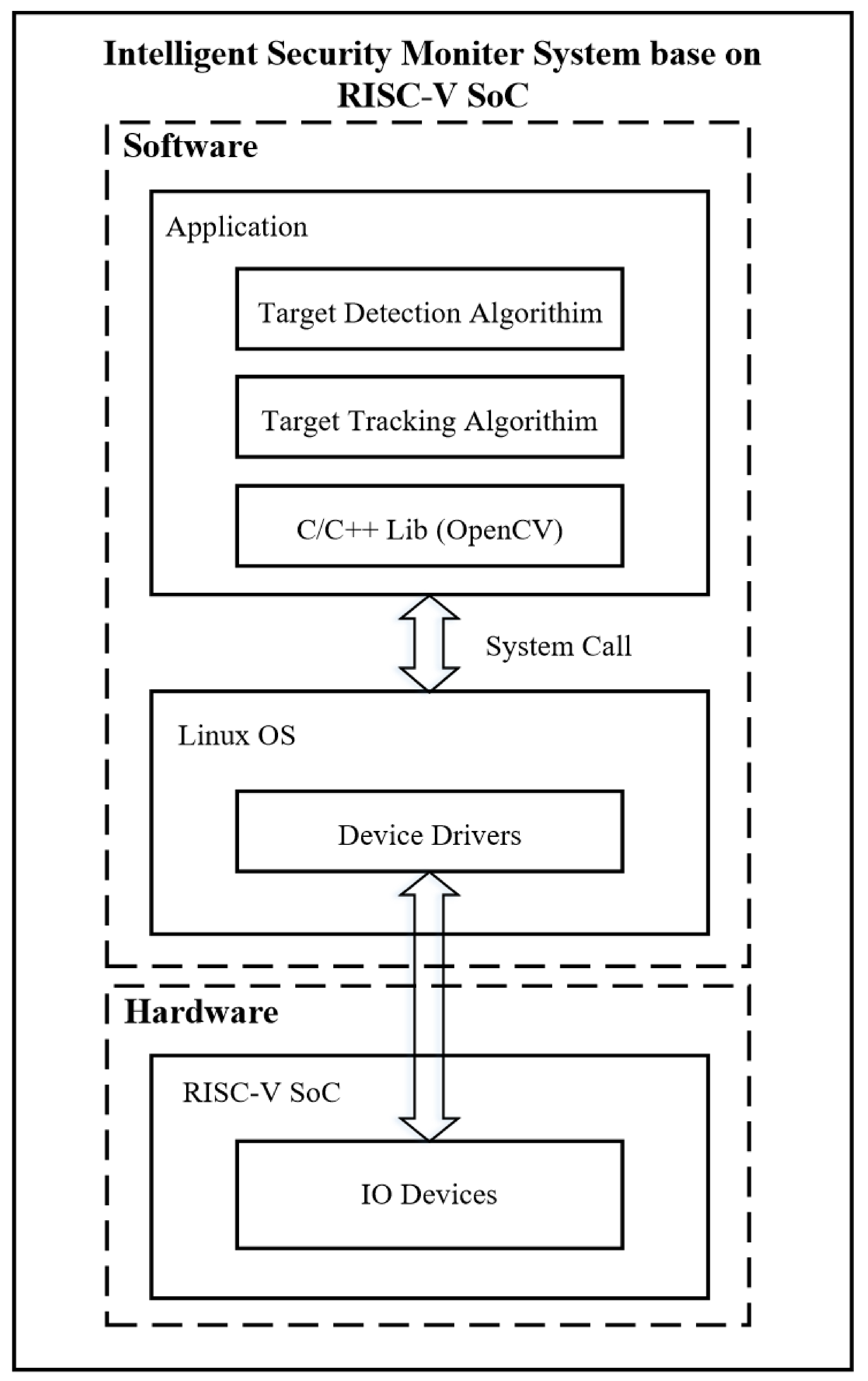

2. Overall System Design

2.1. System Composition

2.2. Introduction of the Platform and Design Tools

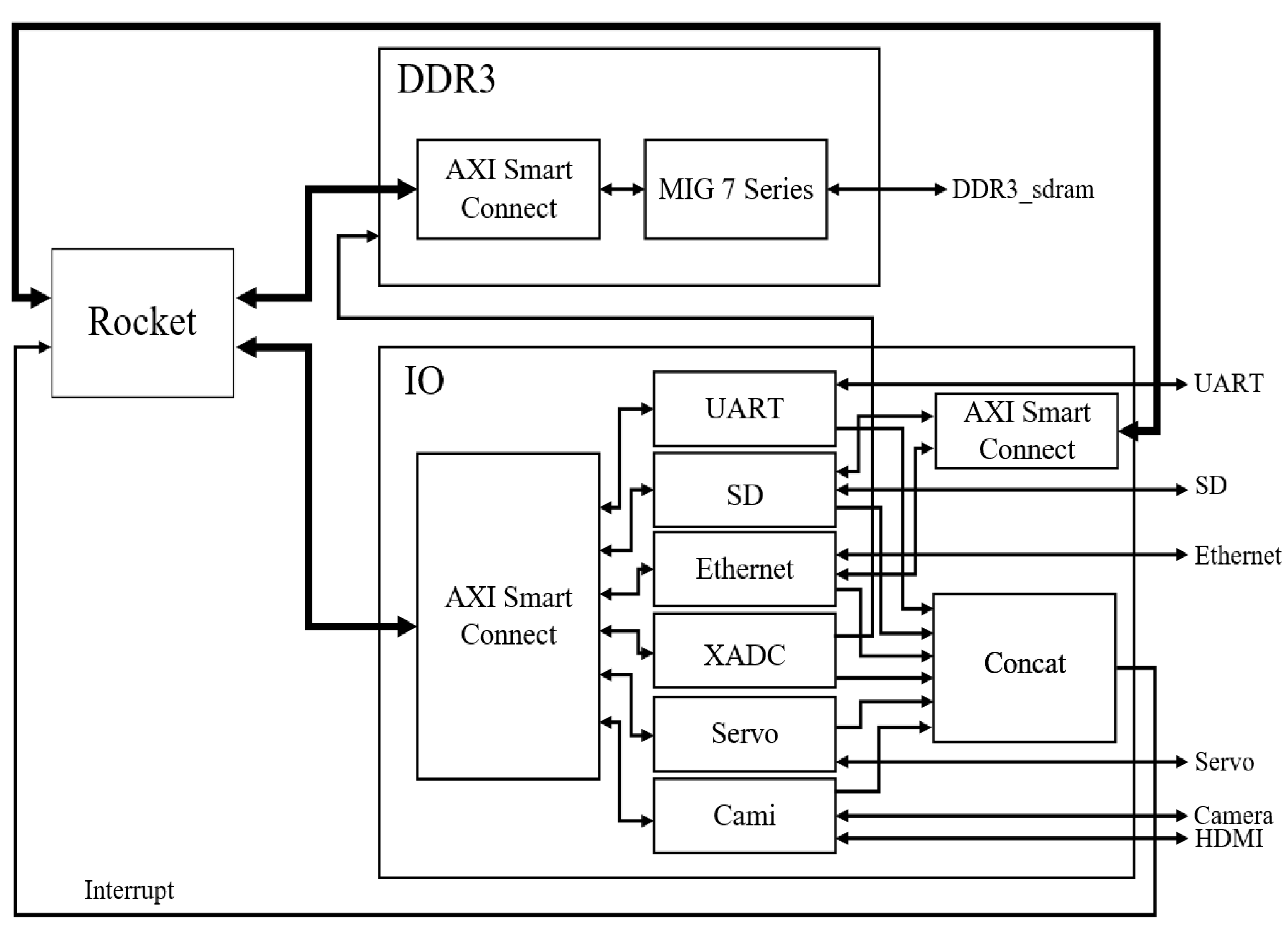

3. System Hardware Design and Implementation

4. System Software Design and Implementation

4.1. Linux Operating System Transplantation

4.2. Linux Device Driver Programming

4.3. Models and Application

4.3.1. Introduction of Models

4.3.2. Design of Application

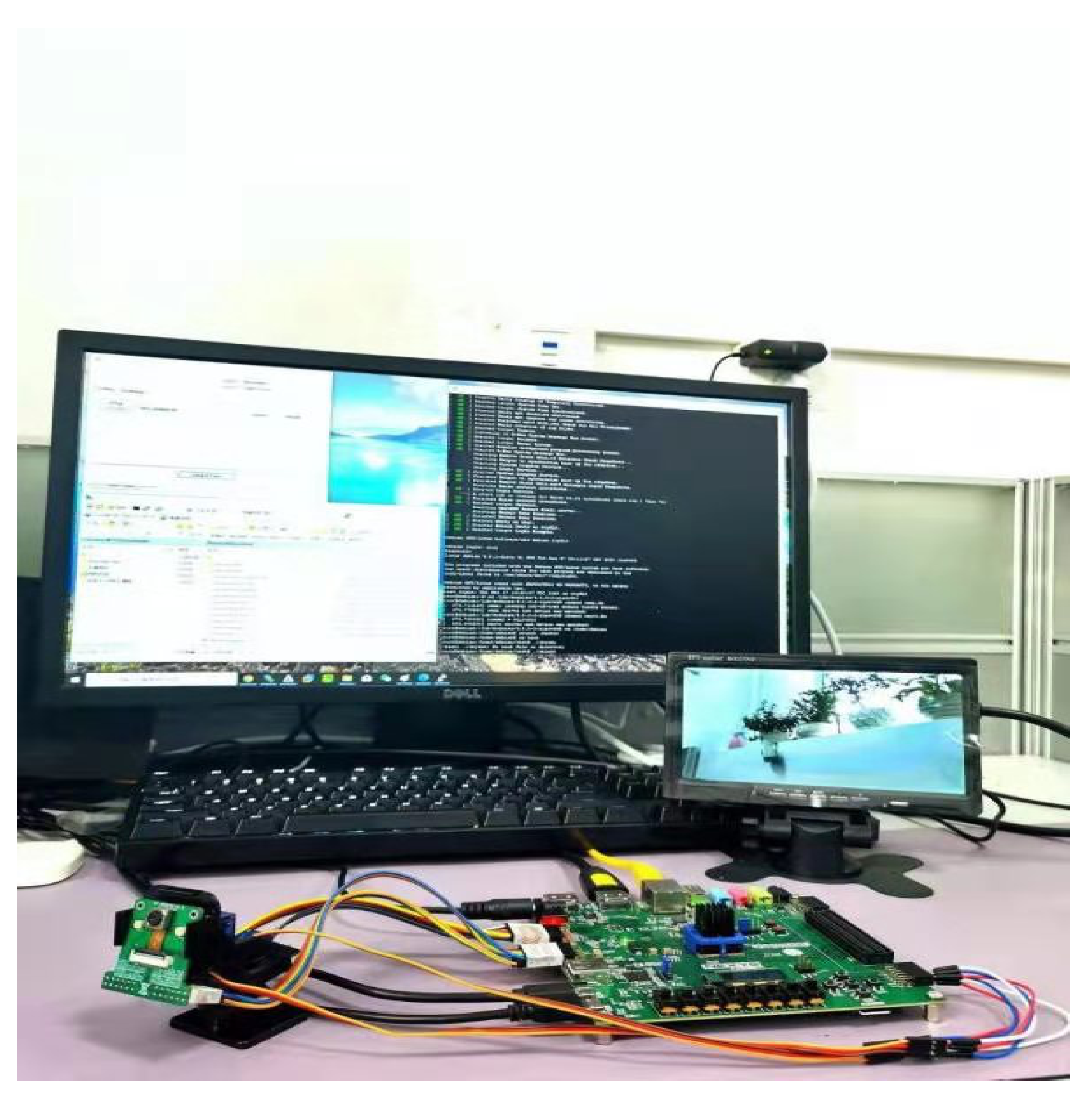

5. Experiment

5.1. Process

5.2. Results and Discussion

6. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Verma, R.K.; Singh, P.; Panigrahi, C.R.; Pati, B. ISS: Intelligent Security System Using Facial Recognition. In Progress in Advanced Computing and Intelligent Engineering; Springer: Berlin/Heidelberg, Germany, 2021; pp. 96–101. [Google Scholar]

- Alheeti, K.M.A.; McDonald-Maier, K. An Intelligent Security System for Autonomous Cars Based On Infrared sensors. In Proceedings of the 2017 23rd International Conference on Automation and Computing (ICAC), Huddersfield, UK, 7–8 September 2017; pp. 1–5. [Google Scholar]

- Yerragolla, M.; Pallela, K.; Gera, I.P. Intelligent Security System for Residential and Industrial Automation. In Proceedings of the 2016 IEEE Uttar Pradesh Section International Conference on Electrical, Computer and Electronics Engineering (UPCON), Varanasi, India, 9–11 December 2016; pp. 229–234. [Google Scholar]

- RenukaChuimurkar, M.; Bagdi, V. Smart Surveillance Security & Monitoring System Using Raspberry PI and PIR Sensor. Int. J. Sci. Eng. Appl. Sci. IJSEAS 2016, 2, 1–4. [Google Scholar]

- Menezes, V.; Patchava, V.; Gupta, M.S.D. Surveillance and Monitoring System Using Raspberry Pi and SimpleCV. In Proceedings of the 2015 international conference on green computing and internet of things (ICGCIoT), Greater Noida, India, 8–10 October 2015; pp. 1276–1278. [Google Scholar]

- Othman, N.A.; Aydin, I. A New IoT Combined Body Detection of People by Using Computer Vision for Security Application. In Proceedings of the 2017 9th International Conference on Computational Intelligence and Communication Networks (CICN), Girne, Northern Cyprus, 16–17 September 2017; pp. 108–112. [Google Scholar]

- Aydin, I.; Othman, N.A. A New IoT Combined Face Detection of People by Using Computer Vision for Security Application. In Proceedings of the 2017 International Artificial Intelligence and Data Processing Symposium (IDAP), Malatya, Turkey, 16–17 September 2017; pp. 1–6. [Google Scholar]

- Wu, L.; Liu, S. Comparative Analysis and Application of LBP Face Image Recognition Algorithms. Int. J. Commun. Syst. 2021, 34, e3977. [Google Scholar] [CrossRef]

- Othman, N.A.; Salur, M.U.; Karakose, M.; Aydin, I. An Embedded Real-Time Object Detection and Measurement of Its Size. In Proceedings of the 2018 International Conference on Artificial Intelligence and Data Processing (IDAP), Malatya, Turkey, 28–30 September 2018; pp. 1–4. [Google Scholar]

- Kanter, D. RISC-V Offers Simple, Modular ISA. In Microprocessor Report. 2016. Available online: https://riscv.org/wp-content/uploads/2016/04/RISC-V-Offers-Simple-Modular-ISA.pdf (accessed on 20 August 2020).

- Waterman, A.S. Design of the RISC-V Instruction Set Architecture. Ph.D. Thesis, UC Berkeley, Berkeley, CA, USA, 2016. [Google Scholar]

- Patterson, D.; Waterman, A. The RISC-V Reader: An Open Architecture Atlas. Strawberry Canyon LLC: San Francisco, CA, USA, 2017. [Google Scholar]

- Farshchi, F.; Huang, Q.; Yun, H. Integrating NVIDIA Deep Learning Accelerator (NVDLA) with RISC-V SoC on FireSim. In Proceedings of the 2019 2nd Workshop on Energy Efficient Machine Learning and Cognitive Computing for Embedded Applications (EMC2), Washington, DC, USA, 17 February 2019; pp. 21–25. [Google Scholar]

- Flamand, E.; Rossi, D.; Conti, F.; Loi, I.; Pullini, A.; Rotenberg, F.; Benini, L. GAP-8: A RISC-V SoC for AI at the Edge of the IoT. In Proceedings of the 2018 IEEE 29th International Conference on Application-specific Systems, Architectures and Processors (ASAP), Milan, Italy, 10–12 July 2018; pp. 1–4. [Google Scholar]

- Zhong, X.; Sham, C.W.; Ma, L. A RISC-V SoC for Mobile Payment Based on Visible Light Communication. In Proceedings of the 2020 IEEE Asia Pacific Conference on Circuits and Systems (APCCAS), Ha Long, Vietnam, 8–10 December 2020; pp. 102–105. [Google Scholar]

- Bailey, S.; Rigge, P.; Han, J.; Lin, R.; Chang, E.Y.; Mao, H.; Wang, Z.; Markley, C.; Izraelevitz, A.M.; Wang, A.; et al. A Mixed-Signal RISC-V Signal Analysis SoC Generator with a 16-nm Finfet Instance. IEEE J. Solid-State Circuits 2019, 54, 2786–2801. [Google Scholar] [CrossRef]

- Torres-Sánchez, E.; Alastruey-Benedé, J.; Torres-Moreno, E. Developing an AI IoT Application with Open Software on a RISC-V SoC. In Proceedings of the 2020 XXXV Conference on Design of Circuits and Integrated Systems (DCIS), Segovia, Spain, 18–20 November 2020; pp. 1–6. [Google Scholar]

- Höller, R.; Haselberger, D.; Ballek, D.; Rössler, P.; Krapfenbauer, M.; Linauer, M. Open-source RISC-V Processor IP Cores for FPGAs—Overview and Evaluation. In Proceedings of the 2019 8th Mediterranean Conference on Embedded Computing (MECO), Budva, Montenegro, 10–14 June 2019; pp. 1–6. [Google Scholar]

- Menon, A.; Murugan, S.; Rebeiro, C.; Gala, N.; Veezhinathan, K. Shakti-T: A RISC-V Processor with Light Weight Security Extensions. In Proceedings of the Hardware and Architectural Support for Security and Privacy, Toronto, ON, Canada, 18 June 2017; pp. 1–8. [Google Scholar]

- Matthews, E.; Shannon, L. TAIGA: A New RISC-V Soft-Processor Framework Enabling High Performance CPU Architectural Features. In Proceedings of the 2017 27th International Conference on Field Programmable Logic and Applications (FPL), Ghent, Belgium, 4–8 September 2017; pp. 1–4. [Google Scholar]

- Balkind, J.; Lim, K.; Gao, F.; Tu, J.; Wentzlaff, D.; Schaffner, M.; Zaruba, F.; Benini, L. OpenPiton+ Ariane: The First Open-Source, SMP Linux-booting RISC-V System Scaling From One to Many Cores. In Proceedings of the Workshop on Computer Architecture Research with RISC-V (CARRV), Phoenix, AZ, USA, 22 June 2019; pp. 1–6. [Google Scholar]

- Asanovic, K.; Avizienis, R.; Bachrach, J.; Beamer, S.; Biancolin, D.; Celio, C.; Cook, H.; Dabbelt, D.; Hauser, J.; Izraelevitz, A.; et al. The Rocket Chip Generator. Tech. Rep. UCB/EECS-2016-17. 2016. Available online: https://www2.eecs.berkeley.edu/Pubs/TechRpts/2016/EECS-2016-17.html (accessed on 16 August 2020).

- Chen, L.; Hu, M.; Liu, N.; Zhai, G.; Yang, S.X. Collaborative Use of RGB and Thermal Imaging for Remote Breathing Rate Measurement under Realistic Conditions. Infrared Phys. Technol. 2020, 111, 103504. [Google Scholar] [CrossRef]

- Yanzhong, Z.; Yanyan, C. Study of Some Common Technology on the Design and Transplantation of Embedded Linux Operating System. Comput. Autom. Meas. Control 2005, 2, 162–164. [Google Scholar]

- C15f44a. u-Boot. Available online: https://github.com/u-boot/u-boot (accessed on 23 December 2020).

- Mao, H. RISC-V Proxy Kernel and Boot Loader. Available online: https://github.com/riscv/riscv-pk (accessed on 27 August 2020).

- Debian Linux Package Repositories. Available online: https://wiki.debian.org/RISC-V (accessed on 10 October 2020).

- Kadav, A.; Swift, M. Understanding modern device drivers. ACM SIGPLAN Notices 2012, 47, 87–98. [Google Scholar] [CrossRef]

- Zhou, J.; Pun, C.M. Personal Privacy Protection via Irrelevant Faces Tracking and Pixelation in Video Live Streaming. IEEE Trans. Inf. Forensics Secur. 2020, 16, 1088–1103. [Google Scholar] [CrossRef]

- Xu, Z.; Baojie, X.; Guoxin, W. Canny Edge Detection based on OpenCV. In Proceedings of the 2017 13th IEEE International Conference on Electronic Measurement & Instruments (ICEMI), Yangzhou, China, 20–22 October 2017; pp. 53–56. [Google Scholar]

- Pulli, K.; Baksheev, A.; Kornyakov, K.; Eruhimov, V. Real-time Computer Vision with OpenCV. Commun. ACM 2012, 55, 61–69. [Google Scholar] [CrossRef]

- Bradski, G.; Kaehler, A. Learning OpenCV: Computer Vision with the OpenCV Library; O’Reilly Media, Inc.: Cambridge, MA, USA, 2008. [Google Scholar]

- Redmon, J.; Divvala, S.; Girshick, R.; Farhadi, A. You Only Look Once: Unified, Real-time Object Detection. In Proceedings of the IEEE Conference on Computer Vision and Pattern Recognition, Las Vegas, NV, USA, 27–30 June 2016; pp. 779–788. [Google Scholar]

- Lienhart, R.; Maydt, J. An Extended Set of Haar-like Features for Rapid Object Detection. In Proceedings of the International Conference on Image Processing, Rochester, NY, USA, 22–25 September 2002; Volume 1, p. 1. [Google Scholar]

- Team, O.D. Face Detection Using Haar Cascades. Tersedia. Available online: http://docs.opencv.org/master/d7/d8b/tutorial_py_face_detection.html (accessed on 26 May 2015).

- Zhang, G.; Huang, X.; Li, S.Z.; Wang, Y.; Wu, X. Boosting Local Binary Pattern (LBP)-based Face Recognition. In Chinese Conference on Biometric Recognition; Springer: Berlin/Heidelberg, Germany, 2004; pp. 179–186. [Google Scholar]

- do Prado, K.S. Face Recognition: Understanding LBPH Algorithm. Available online: https://towardsdatascience.com/face-recognition-how-lbph-works-90ec258c3d6b (accessed on 24 September 2020).

- Li, Y.; Ang, K.H.; Chong, G.C. PID control system analysis and design. IEEE Control Syst. Mag. 2006, 26, 32–41. [Google Scholar]

| Resource | Utilization | Available | Utilization % |

|---|---|---|---|

| LUT | 85,371 | 134,600 | 63.43 |

| LUTRAM | 5847 | 46,200 | 12.66 |

| FF | 50732 | 269,200 | 18.85 |

| BRAM | 207 | 365 | 56.71 |

| DSP | 30 | 740 | 4.05 |

| IO | 102 | 285 | 35.79 |

| MMCM | 2 | 10 | 20.00 |

| PLL | 2 | 10 | 20.00 |

| Model | Detection Time/Frame (s) |

|---|---|

| YOLO v4 tiny | 403.14 |

| Haar | 5.37 |

| LBP | 1.25 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Wu, W.; Su, D.; Yuan, B.; Li, Y. Intelligent Security Monitoring System Based on RISC-V SoC. Electronics 2021, 10, 1366. https://doi.org/10.3390/electronics10111366

Wu W, Su D, Yuan B, Li Y. Intelligent Security Monitoring System Based on RISC-V SoC. Electronics. 2021; 10(11):1366. https://doi.org/10.3390/electronics10111366

Chicago/Turabian StyleWu, Wenjuan, Dongchu Su, Bo Yuan, and Yong Li. 2021. "Intelligent Security Monitoring System Based on RISC-V SoC" Electronics 10, no. 11: 1366. https://doi.org/10.3390/electronics10111366

APA StyleWu, W., Su, D., Yuan, B., & Li, Y. (2021). Intelligent Security Monitoring System Based on RISC-V SoC. Electronics, 10(11), 1366. https://doi.org/10.3390/electronics10111366